Область техники

Изобретение относится к радиотехнике, а именно к устройствам декодирования дискретной информации, и предназначено для передачи дискретной (цифровой) информации с высокой достоверностью по каналам связи.

В области передачи дискретной (цифровой) информации неоспоримым преимуществом в защите информации от помех обладают устройства кодирования, изменяющие фазу псевдослучайных последовательностей. Задача дальнейшего повышения скорости кодирования и помехоустойчивости устройств кодирования информации на основе применения сегментов линейных рекуррентных последовательностей (РП) как кодовых слов связана с реализацией принципов мягкой обработки РП, одним из которых является пороговое декодирование [Золотарев В. В. Кодирование для цифровой связи. Справочник /Под.ред.чл-корр. РАН Ю.Б. Зубова. - М.: Горячая линия - Телеком, 2022. С. 51 - 55].

Успех порогового декодирования псевдослучайных последовательностей зависит от правильной цикловой синхронизации (ЦС) декодера, определяющего фазу обрабатываемой псевдослучайной последовательности. В основе процесса обнаружения псевдослучайной последовательности и цикловой синхронизации в приемном (декодирующем) устройстве применяется метод выделения зачетного отрезка (ЗОТ).

Уровень техники

Известно изобретение «Устройство дивергентного декодирования сегментов линейной рекуррентной последовательности» по патенту RU №2820053, H03M 13/03, опубликовано 28.05.2024, содержащее соединенные первый ключ, первую ОЛЗ на k бит (символов), второй ключ, счетчик с порогом на m подряд поступающих логических «1», первую и вторую сопровождающие матрицы, вторую ОЛЗ на k бит (символов), блок сравнения, ОЛЗ на N бит (символов), вычислитель, третий ключ, d-канальную линию задержки на N бит (символов), блок формирования частот, четвертый ключ, логический сумматор и логический инвертор. Недостатком данного аналога является необходимость применения в качестве кодовых слов только символьных псевдослучайных М-последовательностей, которые имеют дополнительные признаки обнаружения ошибок перед их декодированием. При большом количестве ошибок на псевдослучайной последовательности возникает большое количество возможных вариантов исправления ошибок, при дополнительном декодировании которых в целом снижается скорость корректирующего кода.

Наиболее близким к изобретению является «Устройство синхронизации на основе матричной обработки рекуррентной последовательности» по патенту RU №2803318, H04L 7/02, опубликовано 12.09.2023, содержащее соединенные первый и второй ключи, первую и вторую одноканальные линии задержки на k бит (символов), первую и вторую сопровождающие матрицы, дешифратор, счетчик с порогом на m подряд поступающих логических «1» и блок сравнения.

Принцип работы устройства-прототипа заключается в следующем. Изначально устройство синхронизации работает в последовательно- параллельном режиме. Первый ключ замкнут, второй - разомкнут. Входной сигнал (комбинация двоичных единичных символов) на текущем такте работы устройства синхронизации (t) последовательно через первый ключ поступает на первую ОЛЗ и записывается в ее регистры, далее, значения с k регистров первой ОЛЗ двоичные символы поступают в первую сопровождающую матрицу, где вычисляются значения регистров первой ОЛЗ на следующем такте работы (t + 1), которые затем поступают на вход блока сравнения и вход второй сопровождающей матрицы, где вычисляется значение регистров первой ОЛЗ на (t + 2) такте работы устройства синхронизации. Значения, вычисленные во второй сопровождающей матрице, поступают на вход второй ОЛЗ, где они сохраняются на один такт. На следующем такте работы (t + 1) на вход блока сравнения поступят цифровые символы с регистров первой ОЛЗ с выхода второй ОЛЗ и выхода первой сопровождающей матрицы, которые совпадут в случае, если во входном сигнале нет ошибок. При совпадении входных сигналов на выходе схемы сравнения появится логический сигнал «1», подающийся на вход счетчика с порогом на m подряд поступающих логических «1», который в случае накопления m подряд логических «1» размыкает первый ключ и замыкает второй ключ. Таким образом устройство переходит в параллельно-параллельный режим работы, а именно цифровые символы с регистров первой ОЛЗ поступают на первую сопровождающую матрицу, где вычисляются состояния регистров первой ОЛЗ на следующем такте, которые затем через второй ключ записываются в соответствующие регистры первой ОЛЗ и также поступают на вход дешифратора. В случае совпадения поступившей на вход дешифратора кодовой комбинации с комбинацией дешифратора выделяется сигнал цикловой синхронизации, являющийся результатом работы устройства и переводящий устройство в исходное состояние (замыкает первый ключ и размыкает второй ключ).

Устройство-прототип может использоваться для декодирования принятого кодового слова методом «скользящего окна» (выделения ЗОТ). Для этого дешифратор необходимо дополнить саморазмыкаемым ключом, формирующим информационное слово на приеме по сигналу цикловой синхронизации. Однако, существенным недостатком применения устройства-прототипа в декодировании является сравнительно низкая скорость корректирующего кода, невозможность автономного применения в асинхронной системе передачи информации и применения составных псевдослучайных последовательностей в качестве кодовых слов.

Технической проблемой является отсутствие возможности декодирования сегментов псевдослучайных последовательностей Голда, позволяющих повысить скорость и помехоустойчивость корректирующего кода в асинхронной системе передачи.

Техническим результатом является возможность порогового декодирования сегментов последовательности Голда методом ЗОТ, обеспечивающего повышение скорости и помехоустойчивости корректирующего кода в асинхронной системе передачи информации за счет применения механизма обнаружения и защиты от ошибок не только информационной части блока, но и сведений о цикле его обработки без внесения дополнительной избыточности.

Техническая проблема решается за счет введения ОЛЗ на 2k бит (символов), первой преобразующей матрицы, второй преобразующей матрицы, третьего ключа, четвертого ключа, пятого ключа, третьей ОЛЗ на k бит (символов) и анализатора состояния «Покой», соединения выхода ОЛЗ на 2k бит (символов) со входом анализатора состояния «Покой», входом первой преобразующей матрицы и входом второй преобразующей матрицы, выхода анализатора состояния «Покой» со вторым входом счетчика с порогом на m подряд поступающих логических «1», выхода первой преобразующей матрицы с первым информационным входом первого ключа, выхода второй преобразующей матрицы с первым информационным входом третьего ключа, выхода первого ключа с первым информационным входом блока сравнения и входом первой сопровождающей матрицы, выхода счетчика с порогом на m подряд поступающих логических «1» со вторым управляющим входом третьего ключа и вторым управляющим входом четвертого ключа, выхода третьего ключа со входом второй сопровождающей матрицы, выхода первой сопровождающей матрицы со входом первой ОЛЗ на k бит (символов), выхода первой ОЛЗ на k бит (символов) с информационным входом второго ключа и информационным входом пятого ключа, первого выхода второго ключа со вторым информационным входом блока сравнения, второго выхода второго ключа со вторым информационным входом первого ключа, выхода второй ОЛЗ на k бит (символов) с информационным входом четвертого ключа, выхода дешифратора сигналов с первым управляющим входом третьего ключа, первым управляющим входом четвертого ключа и управляющим входом пятого ключа, выхода четвертого ключа со вторым информационным входом третьего ключа и входом дешифратора сигналов, выхода пятого ключа со входом третьей ОЛЗ на k бит (символов).

Раскрытие изобретения

Задачей изобретения является создание устройства порогового декодирования сегментов последовательностей Голда, позволяющих повысить скорость и помехоустойчивость корректирующего кода в асинхронной системе передачи информации.

Эта задача решается тем, что «Устройство синхронизации на основе матричной обработки рекуррентной последовательности», содержащее соединенные первую одноканальную линию задержки (ОЛЗ) на k бит (символов), первый ключ, блок сравнения, второй ключ, вторую ОЛЗ на k бит (символов), первую сопровождающую матрицу, вторую сопровождающую матрицу, счетчик с порогом на m подряд поступающих логических «1» и дешифратор сигналов дополнено введением ОЛЗ на 2k бит (символов), первой преобразующей матрицы, второй преобразующей матрицы, третьего ключа, четвертого ключа, пятого ключа, третьей ОЛЗ на k бит (символов) и анализатора состояния «Покой», соединения выхода ОЛЗ на 2k бит (символов) со входом анализатора состояния «Покой», входом первой преобразующей матрицы и входом второй преобразующей матрицы, выхода анализатора состояния «Покой» со вторым входом счетчика с порогом на m подряд поступающих логических «1», выхода первой преобразующей матрицы с первым информационным входом первого ключа, выхода второй преобразующей матрицы с первым информационным входом третьего ключа, выхода первого ключа с первым информационным входом блока сравнения и входом первой сопровождающей матрицы, выхода счетчика с порогом на m подряд поступающих логических «1» со вторым управляющим входом третьего ключа и вторым управляющим входом четвертого ключа, выхода третьего ключа со входом второй сопровождающей матрицы, выхода первой сопровождающей матрицы со входом первой ОЛЗ на k бит (символов), выхода первой ОЛЗ на k бит (символов) с информационным входом второго ключа и информационным входом пятого ключа, первого выхода второго ключа со вторым информационным входом блока сравнения, второго выхода второго ключа со вторым информационным входом первого ключа, выхода второй ОЛЗ на k бит (символов) с информационным входом четвертого ключа, выхода дешифратора сигналов с первым управляющим входом третьего ключа, первым управляющим входом четвертого ключа и управляющим входом пятого ключа, выхода четвертого ключа со вторым информационным входом третьего ключа и входом дешифратора сигналов, выхода пятого ключа со входом третьей ОЛЗ на k бит (символов).

Первый, второй, третий и четвертый ключи представляют собой k двувходовых двунаправленных ключей, выполненных на МОП транзисторах р-типа, управляемых сигналами, поступающими на вход С ключа (Цифровые и аналоговые интегральные микросхемы: справочник / С.В. Якубовский, Л.И. Ниссельсон, В.И. Кулешова и др.; Под ред. С.В. Якубовского. - М.: Радио и связь, 1990. - 496 с.: ил.) (тип ИМС: 564КТ3).

Пятый ключ представляет собой k двухвходовых логических элементов, реализующие функцию «И»( Цифровые и аналоговые интегральные микросхемы: справочник / С.В. Якубовский, Л.И. Ниссельсон, В.И. Кулешова и др.; Под ред. С.В. Якубовского. - М.: Радио и связь, 1990. - 496 с.: ил.) (тип ИМС: 133ЛИ1).

Первая, вторая и третья ОЛЗ на k бит выполнены на универсальных регистрах сдвига с последовательным вводом с последовательной или параллельной записью и последовательным или параллельным выводом считыванием, первый разряд которого является JK-триггером, а остальные разряды построены на D-триггерах, равной времени прохождения k бит с тактовой частотой (Цифровые и аналоговые интегральные микросхемы: справочник / С.В. Якубовский, Л.И. Ниссельсон, В.И. Кулешова и др.; Под ред. С.В. Якубовского. - М.: Радио и связь, 1990. - 496 с.: ил.) (тип ИМС: 564ИР9).

ОЛЗ на 2k бит выполнен на универсальных регистрах сдвига с последовательным вводом с последовательной или параллельной записью и последовательным или параллельным выводом считыванием, первый разряд которого является JK-триггером, а остальные разряды построены на D-триггерах, равной времени прохождения 2k бит с тактовой частотой1 (тип ИМС: 564ИР9).

Дешифратор сигналов представляет собой логические двухвходовые элементы, реализующие функцию «ИЛИ-НЕ»1 (тип ИМС: 564ЛЕ5), логические двухвходовые элементы, реализующие функцию «И-НЕ»1 (тип ИМС: 564ЛА7) и двухступенчатый синхронный D-триггер1 (тип ИМС: 564ТМ2).

Счетчик с порогом на m подряд поступающих логических «1» представляет собой логические двухвходовые элементы, реализующие функцию «ИЛИ-НЕ»1 (тип ИМС: 564ЛЕ5), логические двухвходовые элементы, реализующие функцию «И-НЕ»1 (тип ИМС: 564ЛА7) и четырехразрядный двоичный счетчик1 (тип ИМС: 564ИЕ10).

Первая и вторая сопровождающие матрицы представляют собой совокупность двухвходовых схем сложения по mod 21 (тип ИМС: 564ЛП2) в соответствии с обратными связями заданного характеристического многочлена.

Первая и вторая преобразующие матрицы представляют собой совокупность двухвходовых схем сложения по mod 21 (тип ИМС: 564ЛП2) в соответствии с вычисленными корнями заданного характеристического многочлена.

Блок сравнения представляет собой k двухвходовых схем сложения по mod 21 (тип ИМС: 564ЛП2) и логические двухвходовые элементы, реализующие функцию «ИЛИ-НЕ»1 (тип ИМС: 564ЛЕ5).

Анализатор состояния «Покой» представляет собой логические двухвходовые элементы, реализующие функцию «И-НЕ»1 (тип ИМС: 564ЛА7).

Перечисленная новая совокупность существенных признаков обеспечивает пороговое декодирование сегментов последовательностей Голда методом ЗОТ и как следствие повышение скорости и помехоустойчивости корректирующего кода в асинхронной системе передачи информации за счет применения механизма обнаружения и защиты от ошибок не только информационной части блока, но и сведений о цикле его обработки без внесения дополнительной избыточности.

Проведенный анализ уровня техники позволил установить, что аналоги, характеризующиеся совокупностью признаков, тождественных всем признакам заявленного технического решения, отсутствуют, что указывает на соответствие условию патентоспособности «новизна».

Результаты поиска известных решений в данной и смежных областях техники с целью выявления признаков, совпадающих с отличительными от прототипа признаками заявленного объекта, показали, что они не следуют явным образом из уровня техники. Из уровня техники также не выявлена известность влияния предусматриваемых существенными признаками заявленного изобретения преобразований на достижение указанного технического результата. Следовательно, заявленное изобретение соответствует условию патентоспособности «изобретательский уровень».

Описание чертежей

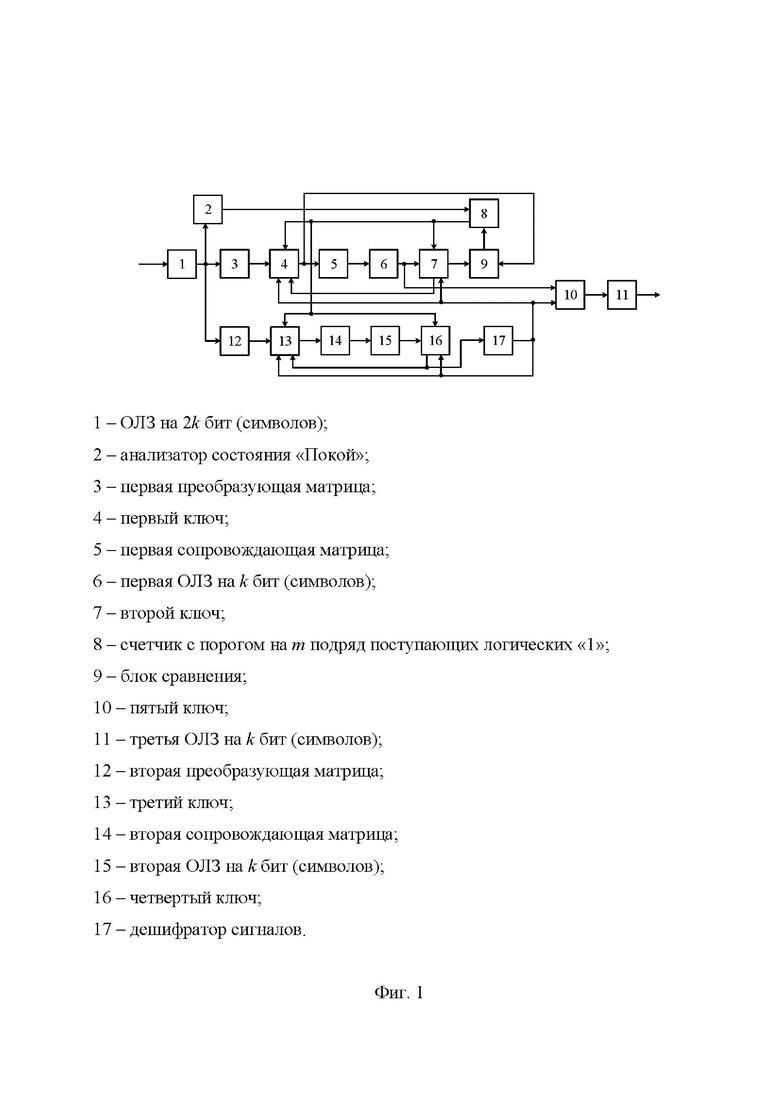

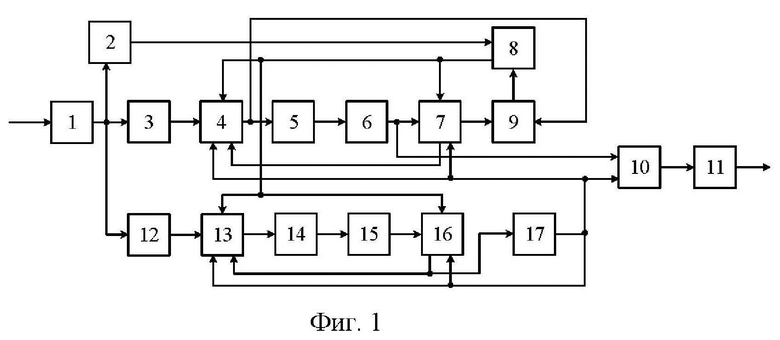

Заявляемое устройство поясняется чертежами:

фиг. 1 - структурная схема приемной стороны устройства порогового декодирования последовательности Голда.

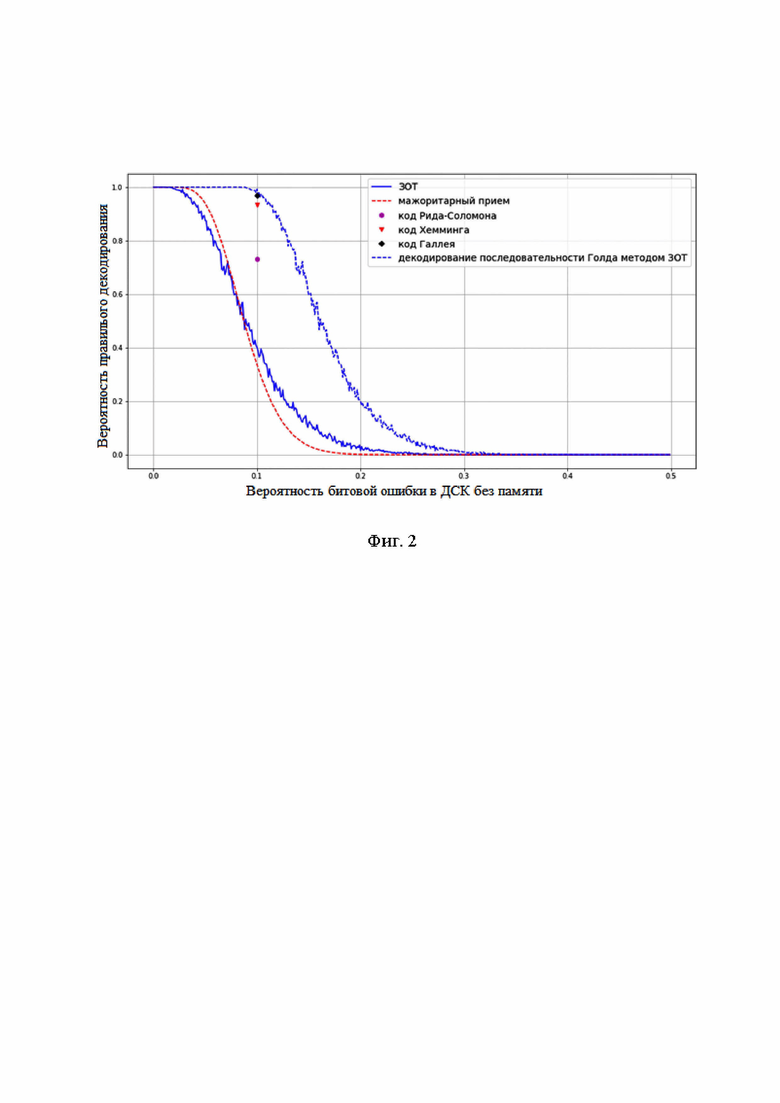

фиг. 2 - графики и точечные значения зависимостей вероятности правильного декодирования кодового слова от вероятности битовой ошибки в двоичном симметричном канале (ДСК) без памяти для различных способов помехоустойчивого кодирования.

Предложенное устройство содержит: первый ключ (4), первую ОЛЗ на k бит (символов) (6), второй ключ (7), дешифратор сигналов (17), счетчик с порогом на m подряд поступающих логических «1» (8), первую сопровождающую матрицу (5), вторую сопровождающую матрицу (14), вторую ОЛЗ на k бит (символов) (15), блок сравнения (9), первую преобразующую матрицу (3), вторую преобразующую матрицу (12), третий ключ (13), ОЛЗ на 2k бит (символов) (1), четвертый ключ (16), пятый ключ (10), третью ОЛЗ на k бит (символов) (11), анализатор состояния «Покой» (2). К выходу из канала связи своим входом подключена ОЛЗ на 2k бит (символов) (1), выход которой соединен со входом первой преобразующей матрицы (3), входом второй преобразующей матрицы (12) и входом анализатора состояния «Покой» (2), выход которого соединен со вторым входом счетчика с порогом на m подряд поступающих логических «1» (8), выход первой преобразующей матрицы (3) соединен с первым информационным входом первого ключа (4), выход которого соединен с первым информационным входом блока сравнения (9) и входом первой сопровождающей матрицы (5), выход которой соединен со входом первой ОЛЗ на k бит (символов) (6), выход которой соединен с информационным входом пятого ключа (10) и информационным входом второго ключа (7), второй выход которого соединен со вторым информационным входом первого ключа (4), а первый выход со вторым информационным входом блока сравнения (9), с выхода которого поступает сигнал на первый вход счетчика с порогом на m подряд поступающих логических «1» (8), выход которого соединен со вторым управляющим входом первого ключа (4), второго ключа (7), третьего ключа (13) и четвертого ключа (16), выход второй преобразующей матрицы (12) соединен с первым информационным входом третьего ключа (13), выход которого соединен со входом второй сопровождающей матрицы (14), выход которой соединен со входом второй ОЛЗ на k бит (символов) (15), выход которой соединен с информационным входом четвертого ключа (16), выход которого соединен со вторым информационным входом третьего ключа (13) и входом дешифратора сигналов (17), выход которого соединен с первым управляющим входом первого ключа (4), второго ключа (7), третьего ключа (13), четвертого ключа (16) и управляющим входом пятого ключа (10), выход которого соединен со входом третьей ОЛЗ на k бит (символов) (11).

Величина m счетчика с порогом на m подряд поступающих логических «1» выбирается в соответствии с требованиями, предъявляемыми к величине  (вероятности правильного выделения зачетного отрезка) в условиях помеховой обстановки в канале связи, но не менее, чем 1. В большинстве случаев величину m устанавливают сопоставимой с размером ОЛЗ (k) на k бит (символов).

(вероятности правильного выделения зачетного отрезка) в условиях помеховой обстановки в канале связи, но не менее, чем 1. В большинстве случаев величину m устанавливают сопоставимой с размером ОЛЗ (k) на k бит (символов).

Размер ОЛЗ (k) на k бит (символов) устанавливают равным размеру линейного рекуррентного регистра (ЛРР), формирующему информационный блок на передаче.

Размер квадратной (сопровождающей) матрицы k × k бит, выполняющей функцию ЛРР, определяется по размеру принимаемого информационного блока (k).

Структурная схема сопровождающей матрицы соответствует вектору обратных связей выбранного характеристического многочлена (полинома).

Структурная схема преобразующей (прямоугольной) матрицы 2k × k бит соответствует корням выбранного характеристического многочлена (полинома), которые вычисляются перед синтезом устройства [Когновицкий О.С. Теория, методы и алгоритмы решения задач в телекоммуникациях на основе двойственного базиса и рекуррентных последовательностей: дис. д-ра техн. наук: 05.12.13. - СПбГУТ, 2011. - 427 с. , С. 39-54].

Промышленное применение изобретения обусловлено тем, что оно может быть осуществлено с помощью современной элементной базы с достижением указанного в изобретении назначения.

Экспериментальная проверка характеристик устройства порогового декодирования последовательности Голда, была выполнена на ЭВМ в среде объектно-ориентированного программирования Anaconda 3 на языке программирования Python 3.7 и дала положительный результат.

Определены экспериментальные зависимости значений вероятности правильного декодирования кодового слова от вероятности битовой ошибки в ДСК без памяти для (фиг. 2):

- способа прямого применения метода ЗОТ, разработанного на основе устройства-прототипа;

- мажоритарного приема;

- декодирования последовательности Голда методом ЗОТ.

Также определены точечные значения правильного декодирования кодового слова от вероятности битовой ошибки в ДСК без памяти (для значения 0,1) для различных способов помехоустойчивого кодирования (код Рида-Соломона, код Хемминга и код Галлея).

Выявлено, что при использовании порогового декодирования последовательности Голда обеспечивается достаточный уровень вероятности правильного декодирования в асинхронном режиме передачи информации по каналам связи с ошибками, что позволяет использовать предложенный подход для повышения скорости корректирующего кода.

Принцип работы предложенного устройства заключается в использовании двух преобразующих матриц, позволяющих выделить два сегмента М-последовательностей, формирующих сегмент принимаемой последовательности Голда, а также двух регистров сдвига, работающих в последовательно-параллельном режиме, с подключенными к ним сопровождающими матрицами, что позволяет выделить рекуррентную зависимость и информационное слово из сегмента первой М-последовательности, а сигнал ЦС - из сегмента второй М-последовательности.

Технический результат по повышению скорости и помехоустойчивости корректирующего кода в асинхронной системе передачи информации достигнут за счет применения в механизме порогового декодирования сегментов последовательности Голда метода ЗОТ, обеспечивающего обнаружение и защиту от ошибок не только информационной части блока, но и сведений о цикле его обработки без внесения дополнительной избыточности.

Изначально устройство декодирования работает в последовательно-параллельном режиме. На выход первого ключа (4) поступает сигнал с его первого информационного входа, на выход третьего ключа (13) поступает сигнал с его первого информационного входа, сигнал со входа второго ключа (7) поступает на его первый выход, четвертый (16) и пятый ключи (10) - разомкнуты. Входной сигнал (комбинация двоичных единичных символов) на текущем такте работы устройства декодирования (t) поступает на вход ОЛЗ на 2k бит (символов) (1) и записывается в ее регистры и, далее, значения с 2k регистров ОЛЗ на 2k бит (символов) (1) поступают на вход первой преобразующей матрицы (3) и вход второй преобразующей матрицы (12) где вычисляются соответствующие значения элементов поля Галуа. Далее через первый ключ (4) значения, вычисленные в первой преобразующей матрице (3) поступают с ее выхода на первый информационный вход блока сравнения (9) и на вход первой сопровождающей матрицы (5), где вычисляется значение элемента поля Галуа на следующем (t + 1) такте работы устройства, которое затем поступает на вход первой ОЛЗ на k бит (символов) (6), где оно сохраняется на один такт. Через третий ключ (13) значения, вычисленные во второй преобразующей матрице (12) поступают с ее выхода на вход второй сопровождающей матрицы (14), где вычисляется значение элемента поля Галуа на следующем (t + 1) такте работы устройства, которое затем поступает на вход второй ОЛЗ на k бит (символов) (15), где оно сохраняется на один такт. На следующем такте работы устройства (t + 1) на второй информационный вход блока сравнения (9) поступят цифровые символы с регистров ОЛЗ на 2k бит (символов) (1) через первую преобразующую матрицу (3) и первый ключ (4), а также через второй ключ (7) с выхода первой ОЛЗ на k бит (символов) (6), сохраненные там ранее на один такт, которые совпадут в случае, если во входном сигнале нет ошибок. При совпадении входных сигналов на выходе блока сравнения (9) появится логический сигнал «1», подающийся на вход счетчика с порогом на m подряд поступающих логических «1» (8), который в случае накопления m подряд логических «1» проключает выход первого ключа (4) с его вторым информационным входом, выход третьего ключа (13) с его вторым информационным входом, вход второго ключа (7) с его вторым выходом и замыкает четвертый ключ (16). Таким образом устройство переходит в параллельно-параллельный режим работы, а именно цифровые символы с регистров первой ОЛЗ на k бит (символов) (6) через второй ключ (7) поступают на первый ключ (4) с выхода которого поступают на первую сопровождающую матрицу (5), где вычисляются состояния регистров первой ОЛЗ на k бит (символов) (6) на следующем такте работы устройства и записываются в регистры первой ОЛЗ на k бит (символов) (6), а цифровые символы с регистров второй ОЛЗ на k бит (символов) (15) через четвертый ключ (16) поступают на вход дешифратора сигналов (17) и на третий ключ (13) с выхода которого поступают на вторую сопровождающую матрицу (14), где вычисляются состояния регистров второй ОЛЗ на k бит (символов) (15) на следующем такте работы устройства и записываются в регистры второй ОЛЗ на k бит (символов) (15). Кроме этого, цифровые символы с регистров первой ОЛЗ на k бит (символов) (6) постоянно поступают на вход пятого ключа (10). В случае совпадения поступившей на вход дешифратора сигналов (17) кодовой комбинации с его комбинацией выделяется сигнал цикловой синхронизации замыкающий пятый ключ (10), после чего кодовая комбинация, находящаяся в регистрах первой ОЛЗ на k бит (символов) (6) синфазно через пятый ключ (10) параллельным кодом поступает на вход третьей ОЛЗ на k бит (символов) (11) и записывается в ее регистры, что является результатом работы устройства. Кроме этого, сигнал цикловой синхронизации переводит устройство в исходное состояние (проключает выход первого ключа (4) с его первым информационным входом, выход третьего ключа (13) с его первым информационным входом, вход второго ключа (7) с его первым выходом, размыкает четвертый ключ (16). Пятый ключ (10) размыкается самостоятельно после окончания поступления сигнала цикловой синхронизации. В случае поступления с выхода ОЛЗ на 2k бит (символов) (1) на вход анализатора состояния «Покой» (2) нулевой комбинации, с выхода анализатора состояния «Покой» (2) на вход счетчика с порогом на m подряд поступающих логических «1» (8) поступает сигнал сброса состояния счетчика на любом такте работы устройства.

Изобретение за счет применения механизма порогового декодирования сегментов последовательностей Голда на основе двухкаскадной матричной обработки и выделения зачетного отрезка позволяет повысить скорость и помехоустойчивость корректирующего кода в асинхронном режиме передачи информации.

Графики и точечные значения, представленные на фиг. 2, подтверждают достаточный уровень вероятности правильного декодирования в каналах связи с ошибками, что позволяет использовать предлагаемое устройство для повышения скорости корректирующего кода.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДИВЕРГЕНТНОГО ДЕКОДИРОВАНИЯ СЕГМЕНТОВ ЛИНЕЙНОЙ РЕКУРРЕНТНОЙ ПОСЛЕДОВАТЕЛЬНОСТИ | 2023 |

|

RU2820053C1 |

| УСТРОЙСТВО СИНХРОНИЗАЦИИ НА ОСНОВЕ МАТРИЧНОЙ ОБРАБОТКИ КАНОНИЧЕСКОЙ РЕКУРРЕНТНОЙ ПОСЛЕДОВАТЕЛЬНОСТИ, СФОРМИРОВАННОЙ МОДУЛЬНЫМ ГЕНЕРАТОРОМ | 2024 |

|

RU2831303C1 |

| УСТРОЙСТВО СИНХРОНИЗАЦИИ НА ОСНОВЕ МАТРИЧНОЙ ОБРАБОТКИ РЕКУРРЕНТНОЙ ПОСЛЕДОВАТЕЛЬНОСТИ | 2023 |

|

RU2803318C1 |

| УСТРОЙСТВО СИНХРОНИЗАЦИИ НА ОСНОВЕ МАТРИЧНОЙ ОБРАБОТКИ И ДЕЦИМАЦИИ РЕКУРРЕНТНОЙ ПОСЛЕДОВАТЕЛЬНОСТИ | 2023 |

|

RU2820337C1 |

| УСТРОЙСТВО СИНХРОНИЗАЦИИ РЕКУРРЕНТНОЙ ПОСЛЕДОВАТЕЛЬНОСТЬЮ С ФУНКЦИЕЙ ВЫДЕЛЕНИЯ ЗАЧЕТНЫХ ИМПУЛЬСОВ В СКОЛЬЗЯЩЕМ ОКНЕ | 2013 |

|

RU2553089C2 |

| УСТРОЙСТВО СИНХРОНИЗАЦИИ ПСЕВДОСЛУЧАЙНОЙ ПОСЛЕДОВАТЕЛЬНОСТИ С ФУНКЦИЕЙ ИСПРАВЛЕНИЯ ОШИБОК | 2011 |

|

RU2486682C2 |

| УСТРОЙСТВО СИНХРОНИЗАЦИИ НА ОСНОВЕ КОМБИНИРОВАННОГО ПРИМЕНЕНИЯ ДВОЙСТВЕННОГО БАЗИСА ПОЛЯ GF(2) И ВЫДЕЛЕНИЯ "СКОЛЬЗЯЩЕГО ОКНА" С ОШИБКАМИ | 2014 |

|

RU2580806C2 |

| УСТРОЙСТВО КОДИРОВАНИЯ-ДЕКОДИРОВАНИЯ ИНФОРМАЦИИ | 1994 |

|

RU2115231C1 |

| Способ цикловой синхронизации с динамической адресацией получателя | 2016 |

|

RU2621181C1 |

| УСТРОЙСТВО ДЛЯ ДЕКОДИРОВАНИЯ ДВОИЧНЫХ КОДОВ ХЕММИНГА | 1999 |

|

RU2161369C1 |

Изобретение относится к радиотехнике, а именно к устройствам декодирования дискретной информации, и предназначено для передачи дискретной (цифровой) информации с высокой достоверностью по каналам связи. Техническим результатом изобретения является возможность порогового декодирования сегментов последовательности Голда методом выделения зачетного отрезка (ЗОТ), обеспечивающего повышение скорости и помехоустойчивости корректирующего кода в асинхронной системе передачи информации за счет применения механизма обнаружения и защиты от ошибок не только информационной части блока, но и сведений о цикле его обработки без внесения дополнительной избыточности. Устройство порогового декодирования последовательности Голда дополнительно содержит соединенные одноканальную линию задержки (ОЛЗ) на 2k бит (символов), первую и вторую преобразующие матрицы, третий, четвертый и пятый ключи, третью ОЛЗ на k бит (символов) и анализатор состояния «Покой». 2 ил.

Устройство порогового декодирования последовательности Голда, содержащее первую одноканальную линию задержки (ОЛЗ) на k бит (символов), первый ключ, блок сравнения, второй ключ, вторую ОЛЗ на k бит (символов), первую сопровождающую матрицу, вторую сопровождающую матрицу, счетчик с порогом на m подряд поступающих логических «1» и дешифратор сигналов, соединения выхода дешифратора сигналов с первым управляющим входом второго ключа и первым управляющим входом первого ключа, выхода второй сопровождающей матрицы со входом второй ОЛЗ на k бит (символов), первого входа счетчика с порогом на m подряд поступающих логических «1» с выходом блока сравнения, выхода счетчика с порогом на m подряд поступающих логических «1» со вторым управляющим входом первого ключа и вторым управляющим входом второго ключа, для реализации порогового декодирования сегментов последовательности Голда с целью повышения скорости и помехоустойчивости корректирующего кода в асинхронной системе передачи информации, отличающееся тем, что дополнено введением ОЛЗ на 2k бит (символов), первой преобразующей матрицы, второй преобразующей матрицы, третьего ключа, четвертого ключа, пятого ключа, третьей ОЛЗ на k бит (символов) и анализатора состояния «Покой», соединения выхода ОЛЗ на 2k бит (символов) со входом анализатора состояния «Покой», входом первой преобразующей матрицы и входом второй преобразующей матрицы, выхода анализатора состояния «Покой» со вторым входом счетчика с порогом на m подряд поступающих логических «1», выхода первой преобразующей матрицы с первым информационным входом первого ключа, выхода второй преобразующей матрицы с первым информационным входом третьего ключа, выхода первого ключа с первым информационным входом блока сравнения и входом первой сопровождающей матрицы, выхода счетчика с порогом на m подряд поступающих логических «1» со вторым управляющим входом третьего ключа и вторым управляющим входом четвертого ключа, выхода третьего ключа со входом второй сопровождающей матрицы, выхода первой сопровождающей матрицы со входом первой ОЛЗ на k бит (символов), выхода первой ОЛЗ на k бит (символов) с информационным входом второго ключа и информационным входом пятого ключа, первого выхода второго ключа со вторым информационным входом блока сравнения, второго выхода второго ключа со вторым информационным входом первого ключа, выхода второй ОЛЗ на k бит (символов) с информационным входом четвертого ключа, выхода дешифратора сигналов с первым управляющим входом третьего ключа, первым управляющим входом четвертого ключа и управляющим входом пятого ключа, выхода четвертого ключа со вторым информационным входом третьего ключа и входом дешифратора сигналов, выхода пятого ключа со входом третьей ОЛЗ на k бит (символов).

| УСТРОЙСТВО СИНХРОНИЗАЦИИ НА ОСНОВЕ МАТРИЧНОЙ ОБРАБОТКИ РЕКУРРЕНТНОЙ ПОСЛЕДОВАТЕЛЬНОСТИ | 2023 |

|

RU2803318C1 |

| Устройство мажоритарного декодирования кода Рида-Соломона по k-элементным участкам кодовой комбинации с порогом определения неисправляемой ошибки | 2015 |

|

RU2610684C1 |

| Устройство мажоритарного декодирования кода Рида-Соломона по k-элементным участкам кодовой комбинации | 2015 |

|

RU2613760C2 |

| Регулятор давления | 1983 |

|

SU1166073A1 |

| CN 107094063 A, 25.08.2017 | |||

| US 4651327 A, 17.03.1987. | |||

Авторы

Даты

2024-12-24—Публикация

2024-07-02—Подача