Предлагаемое изобретение относится к автоматике и вычислительной технике и может быть использовано в аппаратуре передачи данных по каналу с помехами.

Известно устройство (АС СССР N 1150771, МКИ H 03 M 7/00, приоритет от 30.06.83), содержащее группу первых элементов И, группу триггеров, первый и второй счетчики импульсов, основной регистр сдвига, второй элемент И, элемент ИЛИ и сумматор, элемент ИЛИ, дополнительный регистр сдвига, ключи, блок сравнения кодов, постоянное запоминающее устройство, счетчик адреса, два дополнительных триггера, шесть дополнительных элементов И и решающий блок.

Недостатком этого устройства является низкая скорость передачи информации при изменении интенсивности помех.

Наиболее близким по технической сущности является устройство (АС СССР N 1307593, МКИ H 03 M 7/04, приоритет от 04.01.85), выбранное в качестве прототипа предлагаемого изобретения и содержащее группу элементов И, выходы которых соединены с соответствующими триггерами группы триггеров, первый и второй счетчики импульсов, счетные входы которых соединены с тактовой шиной, первый и второй регистры сдвига, прямые выходы разрядов второго регистра сдвига через соответствующие ключи соединены с соответствующими установочными входами первого регистра сдвига, решающий блок, элемент ИЛИ, первый, второй, третий, четвертый, пятый и шестой элементы И, первый и второй регистры и сумматор, выход которого соединен с первым входом элемента ИЛИ, второй вход которого подключен к первому выходу решающего блока, а выход подключен к информационному входу первого регистра сдвига, тактовый вход которого объединен с тактовым входом второго регистра сдвига и подключен к выходу первого элемента И, первый вход которого соединен с тактовой шиной, а второй - с инверсным выходом первого триггера, второй выход решающего блока соединен с информационным входом второго регистра сдвига, а вход решающего блока является входом устройства, выход первого регистра сдвига соединен с первым входом сумматора и первыми входами элементов И группы, вторые входы которых объединены с соответствующими входами второго элемента И и подключены к соответствующим прямым выходам второго счетчика импульсов, инверсные выходы которого соединены с соответствующими входами третьего элемента И, выход которого подключен к установочному входу первого счетчика импульсов, информационные входы которого подключены к соответствующим инверсным выходам триггеров группы триггеров, S-вход первого триггера соединен с выходом второго элемента И, входы четвертого элемента И соединены с соответствующими выходами первого счетчика импульсов, а выход - с вторым входом сумматора, первый вход пятого элемента И подключен к тактовой шине, отличающееся тем, что, с целью повышения надежности и быстродействия, выход элемента ИЛИ соединен с вторым входом пятого элемента И, выход которого подключен к счетному входу второго триггера, инверсный выход которого соединен с первым входом шестого элемента И, второй вход которого соединен с выходом третьего элемента И, а выход - с управляющими входами ключей, выход третьего элемента И соединен со счетным входом первого триггера, первый выход второго регистра сдвига подключен к управляющему входу решающего блока, а информационные выходы первого регистра сдвига являются выходами устройства.

Недостатком этого устройства также является низкая скорость передачи информации за счет невозможности адаптировать параметры зоны стирания при изменении интенсивности помех, что приводит к уменьшению числа декодируемых разрешенных комбинаций в единицу времени.

Задачей изобретения является создание устройства для передачи информации с более высокой скоростью за счет увеличения числа декодируемых разрешенных комбинаций в единицу времени.

Поставленная задача решается за счет того, что в устройство для декодирования двоичных кодов Хемминга, содержащее первый и второй регистры, первый и второй счетчики импульсов, группу элементов И, группу триггеров, элемент ИЛИ, триггер, тактовую шину, решающий блок, первый вход которого является входом устройства, второй выход которого соединен с информационным входом второго регистра, тактовый вход которого соединен с тактовой шиной, счетный вход первого счетчика импульсов соединен с тактовой шиной, а первый - третий выходы соединены со вторыми входами соответствующих элементов И группы элементов И, выходы которых соединены с входами соответствующих триггеров группы триггеров, введены дополнительная группа элементов И, дополнительная группа триггеров, первый и второй дешифраторы, первая и вторая группы сумматоров по модулю два, мультиплексор, сумматор по модулю два, решающее устройство и формирователь параметров зоны стирания, первый выход решающего блока соединен с первыми входами элементов И первой группы элементов И, вторым входом сумматора по модулю два и информационным входом первого регистра, второй выход решающего блока соединен со вторыми входами элементов И дополнительной группы элементов И, со счетным входом триггера и с первым входом сумматора по модулю два, выход которого соединен со счетным входом второго счетчика, а первый - третий выходы первого счетчика соединены с первыми входами соответствующих элементов И дополнительной группы элементов И, тактовый вход первого регистра соединен с тактовой шиной, выходы элементов И дополнительной группы элементов И соединены с соответствующими счетными входами триггеров дополнительной группы триггеров, выходы триггеров обеих групп соединены соответственно с входами соответствующих дешифраторов, выходы триггеров дополнительной группы триггеров соединены с входами элемента ИЛИ, выходы первого и второго дешифраторов соединены соответственно с первыми и вторыми входами соответствующих сумматоров по модулю два соответственно первой и второй групп сумматоров по модулю два, соответствующие вторые и первые входы которых связаны соответственно с выходами первого и второго регистров, выходы сумматоров по модулю два первой и второй групп сумматоров по модулю два подключены соответственно к соответствующим входам первой и второй групп входов мультиплексора, выходы которого являются информационными выходами устройства, а выходы второго счетчика импульсов, выход триггера, выход элемента ИЛИ и четвертый выход первого счетчика импульсов соединены с соответствующими входами решающего устройства, первый выход которого соединен с управляющим входом мультиплексора, второй является управляющим выходом, а остальные выходы соединены с соответствующими входами формирователя параметров зоны стирания, один выход которого соединен со вторым, а другой - с третьим входом решающего блока.

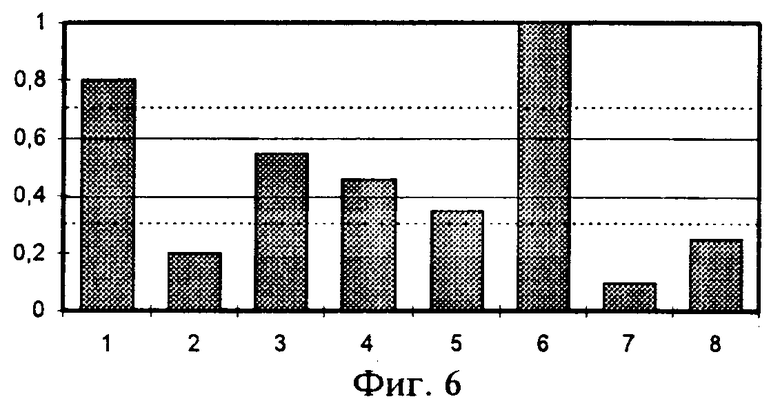

На фиг. 1 представлена структурная схема предлагаемого устройства.

На фиг. 2 представлен пример организации решающего блока.

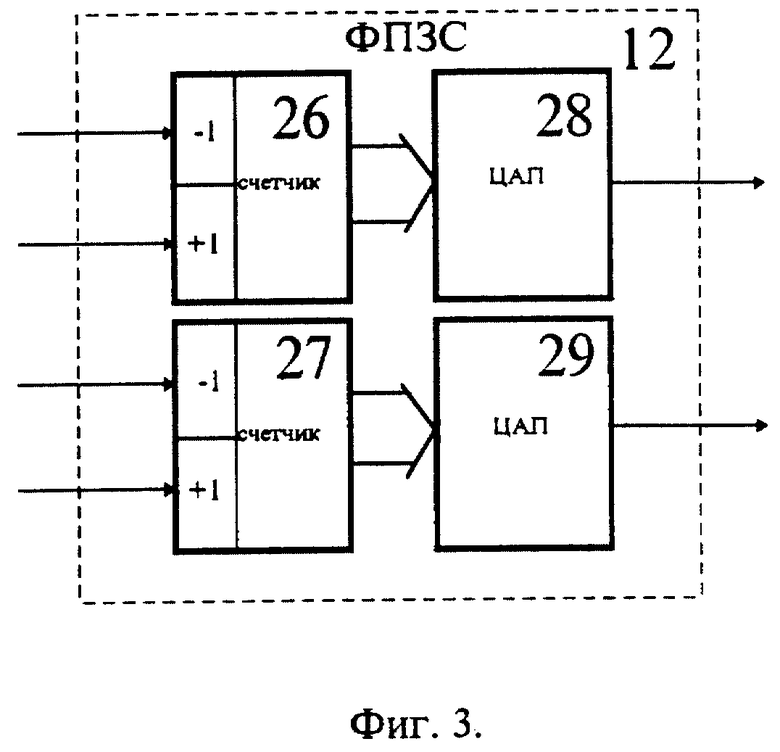

На фиг. 3 представлен пример организации формирователя параметров зоны стирания.

Предлагаемое устройство (фиг. 1) для декодирования двоичных кодов Хемминга содержит вход (ВХ) 1, тактовую шину (ТШ) 2, решающий блок (РБ) 3, первый регистр (РГ) 4, второй регистр (РГ) 5, первый счетчик импульсов (СЧ) 6, второй счетчик импульсов (СЧ) 7, элемент ИЛИ (ИЛИ) 8, триггер (Т) 9, сумматор по модулю два (М2) 10, решающее устройство (РУ) 11, формирователь параметров зоны стирания (ФПЗС) 12, первый дешифратор (ДШ) 13, второй дешифратор (ДШ) 14, мультиплексор (МП) 15, группу элементов И (И) 16, дополнительную группу элементов И (И) 17, группу триггеров (ГТ) 18, дополнительную группу триггеров (ГТ) 19, первую группу сумматоров по модулю два (М2) 20, вторую группу сумматоров по модулю два (М2) 21, информационные выходы устройства (ИВ) 22 и управляющий выход (УВ) 23. Первый вход решающего блока 3 является входом 1 устройства. Второй выход решающего блока 3 соединен с информационным входом второго регистра 5, тактовый вход которого соединен с тактовой шиной 2. Счетный вход первого счетчика решающего блока 3 соединен с информационным входом второго регистра 5, тактовый вход которого соединен с тактовой шиной 2. Счетный вход первого счетчика импульсов 6 соединен с тактовой шиной 2, а первый - третий выходы соединены со вторыми входами соответствующих элементов И группы элементов И 16, выходы которых соединены с входами соответствующих триггеров группы триггеров 18. Первый выход решающего блока 3 соединен с первыми входами элементов И группы элементов И 16, вторым входом сумматора по модулю два 10 и информационным входом первого регистра 4. Второй выход решающего блока 3 соединен со вторыми входами элементов И дополнительной группы элементов И 17, со счетным входом триггера 9 и с первым входом сумматора по модулю два 10, выход которого соединен со счетным входом второго счетчика импульсов 7. Первый - третий выходы первого счетчика импульсов 6 соединены с первыми входами элементов И дополнительной группы элементов И 17. Тактовый вход первого регистра 4 соединен с тактовой шиной 2. Выходы элементов И дополнительной группы элементов И 17 соединены с соответствующими счетными входами триггеров дополнительной группы триггеров 19. Выходы группы триггеров 18 соединены с входами первого дешифратора 13. Выходы дополнительной группы триггеров 19 соединены с входами второго дешифратора 14 и с входами элемента ИЛИ 8. Выходы дешифратора 13 соединены с первыми входами соответствующих сумматоров по модулю два первой группы сумматоров по модулю два 20. Выходы дешифратора 14 соединены со вторыми входами соответствующих сумматоров по модулю два второй группы сумматоров по модулю два 21. Вторые входы сумматоров по модулю два первой группы сумматоров по модулю два 20 связаны соответственно с выходами регистра 4. Первые входы сумматоров по модулю два второй группы сумматоров по модулю два 21 связаны соответственно с выходами регистра 5. Выходы сумматоров по модулю два первой группы сумматоров по модулю два 20 подключены к соответствующим первым входам мультиплексора 15. Выходы сумматоров второй группы сумматоров по модулю два 21 подключены к соответствующим вторым входам мультиплексора 15, выходы которого являются информационными выходами устройства 22. Выходы второго счетчика импульсов 7, выход триггера 9, выход элемента ИЛИ 8 и четвертый выход первого счетчика импульсов 6 соединены с соответствующими входами решающего устройства 11, первый выход которого соединен с управляющим входом мультиплексора 15, второй выход является управляющим выходом 23, а остальные выходы соединены с соответствующими входами формирователя параметров зоны стирания 12, один выход которого соединен со вторым, а другой - с третьим входом решающего блока 3.

Решающий блок 3 (фиг. 2) состоит из компараторов напряжений 24 и 25, осуществляющих сравнение входных сигналов (например, интегральные компараторы напряжений на ИМС 521СА2), [Л.1, c.408- 416]. Первый регистр 4 и второй регистр 5 осуществляют хранение кодовых комбинаций (например, регистры сдвига с параллельным выходом на ИМС 555ИР8), [Л.3, с. 170-182]. Первый счетчик импульсов 6 и второй счетчик импульсов 7 производят подсчет числа импульсов и представляют результат в двоичном коде (например, двоичные асинхронные счетчики на ИМС 555ИЕ19), [Л.3, с. 190-200]. Элемент ИЛИ 8 реализует операцию логического сложения (например, логический элемент ИЛИ-НЕ на ИМС 555ЛЕ4 с инвертированным с помощью логического элемента НЕ на ИМС 555ЛН1 выходом), [Л.3, c. 86-87]. Триггер 9, триггеры группы триггеров 18 и триггеры дополнительной группы триггеров 19 с появлением на входе импульса изменяют свое состояние и фиксируют его (например, D-триггеры на ИМС 555ТМ2, у которых инверсный выход соединен со входом данных), [Л.3, с. 160-165]. Сумматор по модулю два 10, элементы первой группы сумматоров по модулю два 20 и элементы второй группы сумматоров по модулю два 21 осуществляют операцию сложения по модулю два (например, сумматоры по модулю два на ИМС 555ЛП5), [Л. 3, с. 94]. Первый дешифратор 13 и второй дешифратор 14 преобразуют двоичный код в позиционный (например, дешифраторы/демультиплексоры на ИМС 155ИД3), [Л. 3, с. 107-122]. Мультиплексор 15 коммутирует определенную группу входов с выходами в зависимости от состояния управляющего входа (например, два мультиплексора на ИМС 555КП11), [Л. 3, с. 125-130]. Элементы группы элементов И 16 и элементы дополнительной группы элементов И 17 реализуют операцию логического умножения (например, логические элементы И на ИМС 555ЛИ1), [Л. 3, c. 78-80]. Решающее устройство 11 реализовано на постоянном запоминающем устройстве, осуществляющем хранение и выдачу информации в зависимости от сигналов, поступающих на его адресные входы (например, на программируемом ПЗУ на ИМС КР556РТ17), [Л. 2, с. 119-125]. Формирователь параметров зоны стирания 12 (фиг. 3) состоит из счетчиков 26 и 27, производящих подсчет числа импульсов и представляющих результат двоичном коде (например, реверсивные счетчики на ИМС 555ИЕ7), [Л. 3, с. 190-200], и цифроаналоговых преобразователей 28 и 29, преобразующих двоичную кодовую комбинацию в аналоговый сигнал (например, ЦАП на ИМС КМ 1118ПА2), [Л. 2, c. 170-171, 195-205].

Устройство работает следующим образом.

В исходном состоянии триггер 9 и счетчики импульсов 6 и 7 находятся в нулевом состоянии, в счетчики 26 и 27 записаны начальные среднестатистические значения параметров зоны стирания.

Посылка двоичных символов, закодированная в двоичном модифицированном коде Хемминга, поступает с входа 1 устройства на вход решающего блока 3. При помощи решающего блока 3 осуществляется разделение приходящей из линии связи комбинации на две: принятую комбинацию, у которой стертые позиции заменены единицами, и принятую комбинацию, у которой стертые позиции заменены нулями. Первая комбинация поступает на входы элементов И группы элементов И 16, на вход сумматора по модулю два 10 и одновременно записывается в регистр 4, на тактовый вход которого поступают тактовые импульсы с тактовой шины 2. Вторая комбинация поступает на входы элементов И дополнительной группы элементов И 17, на вход триггера 9, на вход сумматора по модулю два 10 и одновременно записывается в регистр 5, на тактовый вход которого поступают тактовые импульсы с тактовой шины 2. На счетный вход первого счетчика импульсов 6 поступают тактовые импульсы с тактовой шины 2. В зависимости от состояния первого счетчика импульсов 6 изменяются режимы работы группы элементов И 16 и дополнительной группы элементов И 17, которые осуществляют разделение символов двоичного кода Хемминга. Разделенные символы поступают соответственно на счетные входы триггеров группы триггеров 18 и на счетные входы триггеров группы триггеров 19, которые позволяют осуществить операцию сложения по модулю два и запомнить результат сложения. Каждому сочетанию состояний триггеров групп триггеров 18 и 19 соответствует синдром ошибки, который указывает номер искаженного разряда в двоичном коде. С выходов триггеров групп триггеров 18 и 19 синдромы ошибки поступают на входы дешифраторов 13 и 14, формирующих векторы ошибки, в которых на позиции искаженного символа фиксируется уровень "1", на остальных позициях - уровень "0". Полученные векторы ошибки суммируются по модулю два с соответствующими принятыми комбинациями, записанными в регистры 4 и 5, при помощи групп сумматоров по модулю два 20 и 21. Исправленные комбинации поступают соответственно на первые и вторые входы мультиплексора 15.

Синдром ошибки с выходов триггеров группы триггеров 19 поступает также на входы элемента ИЛИ 8. Если синдром ошибки нулевой, то на выходе элемента ИЛИ 8 устанавливается уровень "0", если ненулевой - уровень "1". Триггер 9 производит подсчет числа единиц в принятой комбинации, у которой стертые позиции заменены нулями, осуществляя тем самым ее проверку на четность. Сумматор по модулю два 10 осуществляет сложение по модулю два принятой комбинации, у которой стертые позиции заменены нулями и принятой комбинации, у которой стертые позиции заменены единицами. Результат сложения поступает на счетный вход счетчика импульсов 7, на выходах которого по окончании цикла приема формируется двоичная комбинация, соответствующая числу стертых символов в принятой комбинации. В зависимости от сигналов, поступающих с выходов второго счетчика импульсов 7, элемента ИЛИ 8, триггера 9, а также с четвертого выхода первого счетчика импульсов 6 на соответствующие входы решающего устройства 11, в конце цикла приема на его первом выходе устанавливается уровень "0", разрешающий мультиплексору 15 выдачу на информационные выходы устройства 22 сигналов с первой группы входов, или уровень "1", разрешающий мультиплексору 15 выдачу на информационные выходы устройства 22 сигналов со второй группы входов. Уровень "1" на втором выходе решающего устройства 11, являющемся управляющим выходом 23, разрешает чтение информации с информационных выходов устройства 22, уровень "0" - запрещает. Сигналы с остальных выходов поступают на формирователь параметров зоны стирания 12 и управляют величиной порогов зоны стирания. На выходах формирователя параметров зоны стирания 12 формируются верхний и нижний пороги зоны стирания, поступающие на соответствующие входы решающего блока 3. Цикл декодирования завершен.

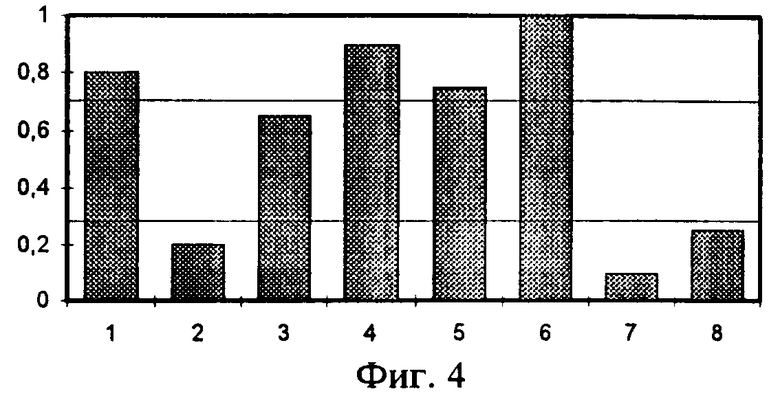

Пусть, например, передается двоичная комбинация МКХ, соответствующая десятичному числу 10, которая имеет вид: 10110100. Допустим, при передаче третий символ оказался стертым, а пятый - трансформированным (cм. фиг. 4, где на оси абсцисс указан порядковый номер двоичных сигналов в кодовой комбинации, на оси ординат - амплитуда принятых сигналов в условных единицах. Пороги зоны стирания в текущий момент показаны сплошными линиями, в предыдущий - пунктирными. В приведенных примерах передача ведется с амплитудной модуляцией и с разделительными паузами). Принятая комбинация, поступившая на вход 1 решающего блока 3, будет следующей: 10Х11100. При помощи решающего блока 3 осуществляется ее разделение на принятую комбинацию, у которой стертые позиции заменены единицами - 10111100, и принятую комбинацию, у которой стертые позиции заменены нулями - 10011100. Последний, восьмой разряд проверки на четность используется только триггером 9, поэтому в остальной части схемы используются лишь семь первых разрядов кодовой посылки. Первая комбинация поступает на входы элементов И группы элементов И 16, на вход сумматора по модулю два 10 и одновременно записывается в регистр 4, на тактовый вход которого поступают тактовые импульсы с тактовой шины 2. Вторая комбинация поступает на входы элементов И дополнительной группы элементов И 17, на вход триггера 9, на вход сумматора по модулю два 10 и одновременно записывается в регистр 5, на тактовый вход которого поступают тактовые импульсы с тактовой шины 2. На счетный вход первого счетчика импульсов 6 поступают тактовые импульсы с тактовой шины 2. В зависимости от состояния первого счетчика импульсов 6 изменяются режимы работы группы элементов И 16 и дополнительной группы элементов И 17, которые осуществляют разделение символов двоичного кода Хемминга. Разделенные символы поступают соответственно на счетные входы триггеров группы триггеров 18 и на счетные входы триггеров группы триггеров 19, которые позволяют осуществить операцию сложения по модулю два и запомнить результат сложения. Таким образом, по окончании цикла приема в триггерах группы триггеров 18 будет записан синдром ошибки 101 (снизу вверх), в триггерах группы триггеров 19 - синдром ошибки 011 (снизу вверх). С выходов триггеров групп триггеров 18 и 19 синдромы ошибки поступают на входы дешифраторов 13 и 14, формирующих векторы ошибки, в которых на позиции искаженного символа фиксируется уровень "1", на остальных позициях - уровень "0". Векторы ошибки будут соответственно следующими: 0000100 и 0000010. Полученные векторы ошибки суммируются по модулю два с соответствующими принятыми комбинациями, записанными в регистры 4 и 5, при помощи групп сумматоров по модулю два 20 и 21. Соответствующие исправленные комбинации 1011010 и 1001100 поступают соответственно на первые и вторые группы входов мультиплексора 15.

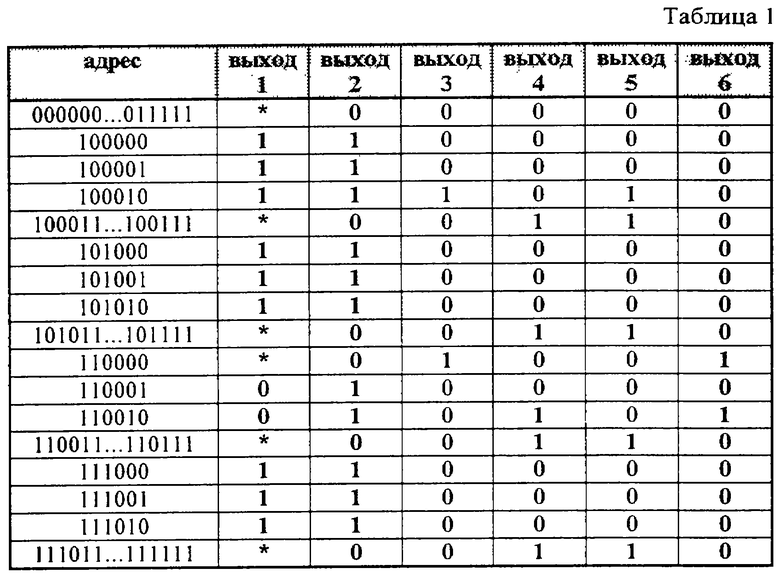

Синдром ошибки с выходов триггеров группы триггеров 19 поступает также на входы элемента ИЛИ 8. Синдром ошибки ненулевой, на выходе элемента ИЛИ 8 устанавливается уровень "1". Триггер 9 производит подсчет числа единиц в принятой комбинации, у которой стертые позиции заменены нулями, осуществляя тем самым ее проверку на четность. Таким образом, по окончании цикла приема в триггере 9 будет записан "0". Сумматор по модулю два 10 осуществляет сложение по модулю два принятой комбинации, у которой стертые позиции заменены нулями, и принятой комбинации, у которой стертые позиции заменены единицами. Результат сложения поступает на счетный вход счетчика импульсов 7, на выходах которого по окончании цикла приема формируется двоичная комбинация 001, соответствующая числу стертых символов в принятой комбинации. В зависимости от сигналов, поступающих с выходов элемента ИЛИ 8, триггера 9, второго счетчика импульсов 7, а также с четвертого выхода первого счетчика импульсов 6 на соответствующие входы решающего устройства 11, которое может быть реализовано на ПЗУ, прошитом как показано в таблице 1, в конце цикла приема на его первом выходе устанавливается уровень "0", разрешающий мультиплексору 15 выдачу на информационные выходы устройства 22 сигналов с первых входов: 1011010. Уровень "1" на втором выходе решающего устройства 11, являющемся управляющим выходом 23, разрешает чтение информации с информационных выходов устройства 22. Сигналы с остальных выходов, поступающие на формирователь параметров зоны стирания 12 и управляющие величиной порогов зоны стирания, будут соответственно прошивке ПЗУ нулевыми, т.к. менять параметры зоны стирания не требуется. Верхний и нижний пороги зоны стирания на выходах формирователя параметров зоны стирания 12, поступающие на соответствующие входы решающего блока 3, остаются прежними. Цикл декодирования завершен.

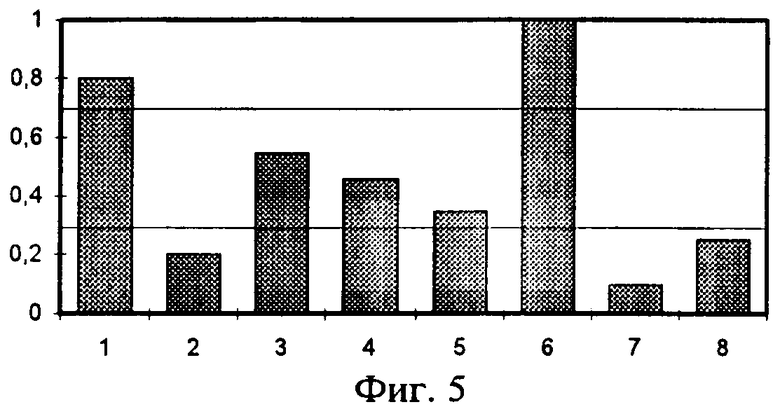

Пусть снова передается та же двоичная комбинация МКХ: 10110100. Допустим, что при передаче третий, четвертый и пятый символы оказались стертыми (фиг. 5). Принятая комбинация, поступившая на вход 1 решающего блока 3, будет следующей: 10ХХХ100. При помощи решающего блока 3 осуществляется ее разделение на принятую комбинацию, у которой стертые позиции заменены единицами - 10111100, и принятую комбинацию, у которой стертые позиции заменены нулями - 10000100. Первая комбинация поступает на входы элементов И группы элементов И 16, на вход сумматора по модулю два 10 и одновременно записывается в регистр 4, на тактовый вход которого поступают тактовые импульсы с тактовой шины 2. Вторая комбинация поступает на входы элементов И дополнительной группы элементов И 17, на вход триггера 9, на вход сумматора по модулю два 10 и одновременно записывается в регистр 5, на тактовый вход которого поступают тактовые импульсы с тактовой шины 2. На счетный вход первого счетчика импульсов 6 поступают тактовые импульсы с тактовой шины 2. В зависимости от состояния первого счетчика импульсов 6 изменяются режимы работы группы элементов И 16 и дополнительной группы элементов И 17, которые осуществляют разделение символов двоичного кода Хемминга. Разделенные символы поступают соответственно на счетные входы триггеров группы триггеров 18 и на счетные входы триггеров группы триггеров 19, которые позволяют осуществить операцию сложения по модулю два и запомнить результат сложения. Таким образом, по окончании цикла приема в триггерах группы триггеров 18 будет записан синдром ошибки 101, а в триггерах группы триггеров группы триггеров 19 будет записан синдром ошибки 111.

Синдром ошибки с выходов триггеров группы триггеров 19 поступает также на входы элемента ИЛИ 8. Синдром ошибки ненулевой, на выходе элемента ИЛИ 8 устанавливается уровень "1". Триггер 9 производит подсчет числа единиц в принятой комбинации, у которой стертые позиции заменены нулями, осуществляя тем самым ее проверку на четность. Таким образом, по окончании цикла приема в триггере 9 будет записан "0". Сумматор по модулю два 10 осуществляет сложение по модулю два принятой комбинации, у которой стертые позиции заменены нулями и принятой комбинации, у которой стертые позиции заменены единицами. Результат сложения поступает на счетный вход счетчика импульсов 7, на выходах которого по окончании цикла приема формируется двоичная комбинация 011, соответствующая числу стертых символов в принятой комбинации. В зависимости от сигналов, поступающих с выходов элемента ИЛИ 8, триггера 9, второго счетчика импульсов 7, а также с четвертого выхода первого счетчика импульсов 6 на соответствующие входы решающего устройства 11, в конце цикла приема на его втором выходе, являющемся управляющим выходом 23, устанавливается уровень "0", что запрещает чтение информации с информационных выходов устройства 22. Сигналы с остальных выходов, поступающие на формирователь параметров зоны стирания 12 и управляющие величиной порогов зоны стирания, будут соответственно прошивке ПЗУ следующими (сверху вниз): 0110, что соответствует сужению зоны стирания. Верхний порог смещается на одну ступень вниз, нижний порог смещается на одну ступень вверх. Цикл декодирования завершен.

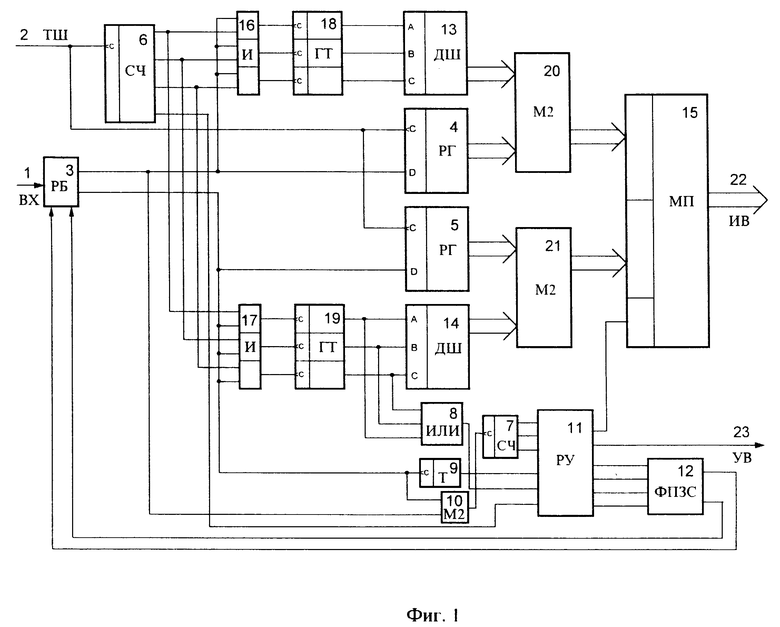

Пусть снова передается та же двоичная комбинация МКХ: 10110100. Допустим, что на вход 1 она поступила в точно таком же виде, как и в предыдущем случае. Однако теперь при новых значениях параметров зоны стирания принятая комбинация будет следующей: 10ХХ0100 (фиг. 6). При помощи решающего блока 3 осуществляется ее разделение на принятую комбинацию, у которой стертые позиции заменены единицами - 10110100, и принятую комбинацию, у которой стертые позиции заменены нулями - 10000100. Первая комбинация поступает на входы элементов И группы элементов И 16, на вход сумматора по модулю два 10 и одновременно записывается в регистр 4, на тактовый вход которого поступают тактовые импульсы с тактовой шины 2. Вторая комбинация поступает на входы элементов И дополнительной группы элементов И 17, на вход триггера 9, на вход сумматора по модулю два 10 и одновременно записывается в регистр 5, на тактовый вход которого поступают тактовые импульсы с тактовой шины 2. На счетный вход первого счетчика импульсов 6 поступают тактовые импульсы с тактовой шины 2. В зависимости от состояния первого счетчика импульсов 6 изменяются режимы работы группы элементов И 16 и дополнительной группы элементов И 17, которые осуществляют разделение символов двоичного кода Хемминга. Разделенные символы поступают соответственно на счетные входы триггеров группы триггеров 18 и на счетные входы триггеров группы триггеров 19, которые позволяют осуществить операцию сложения по модулю два и запомнить результат сложения. Таким образом, по окончании цикла приема в триггерах группы триггеров 18 будет записан синдром ошибки 000, а в триггерах группы триггеров 19 - 111. С выходов триггеров групп триггеров 18 и 19 синдромы ошибки поступают на входы дешифраторов 13 и 14, формирующих векторы ошибки соответственно 0000000 и 0000001. Полученные векторы ошибки суммируются по модулю два с соответствующими принятыми комбинациями, записанными в регистры 4 и 5, при помощи групп сумматоров по модулю два 20 и 21. Соответствующие исправленные комбинации 1011010 и 1000011 поступают соответственно на первые и вторые входы мультиплексора 15.

Синдром ошибки с выходов триггеров группы триггеров 19 поступает также на входы элемента ИЛИ 8. Синдром ошибки ненулевой, на выходе элемента ИЛИ 8 устанавливается уровень "1". Триггер 9 производит подсчет числа единиц в принятой комбинации, у которой стертые позиции заменены нулями, осуществляя тем самым ее проверку на четность. Таким образом, по окончании цикла приема в триггере 9 будет записан "0". Сумматор по модулю два 10 осуществляет сложение по модулю два принятой комбинации, у которой стертые позиции заменены нулями, и принятой комбинации, у которой стертые позиции заменены единицами. Результат сложения поступает на счетный вход счетчика импульсов 7, на выходах которого по окончании цикла приема формируется двоичная комбинация 010, соответствующая числу стертых символов в принятой комбинации. В зависимости от сигналов, поступающих с выходов элемента ИЛИ 8, триггера 9, второго счетчика импульсов 7, а также с четвертого выхода первого счетчика импульсов 6 на соответствующие входы решающего устройства 11, в конце цикла приема на его первом выходе устанавливается уровень "0", разрешающий мультиплексору 15 выдачу на информационные выходы устройства 22 сигналов с первой группы входов: 1011010. Уровень "1" на втором выходе решающего устройства 11, являющемся управляющим выходом 23, разрешает чтение информации с информационных выходов устройства 22. Сигналы с остальных выходов, поступающие на формирователь параметров зоны стирания 12 и управляющие величиной порогов зоны стирания, будут соответственно прошивке ПЗУ следующими (сверху вниз): 0101, что соответствует смещению зоны стирания вниз. Верхний и нижний пороги смещаются на одну ступень вниз. Цикл декодирования завершен.

Очевидно, что без предыдущего изменения параметров зоны стирания эта поврежденная комбинация не могла быть успешно декодирована.

Пусть снова передается та же двоичная комбинация МКХ: 10110100. Допустим, что на вход 1 она поступила в точно таком же виде, как и в предыдущих случаях. Однако теперь при новых значениях параметров зоны стирания принятая комбинация будет следующей: 101XX100 (фиг. 7). При помощи решающего блока 3 осуществляется ее разделение на принятую комбинацию, у которой стертые позиции заменены единицами - 10111100, и принятую комбинацию, у которой стертые позиции заменены нулями - 10100100. Первая комбинация поступает на входы элементов И группы элементов И 16, на вход сумматора по модулю два 10 и одновременно записывается в регистр 4, на тактовый вход которого поступают тактовые импульсы с тактовой шины 2. Вторая комбинация поступает на входы элементов И дополнительной группы элементов И 17, на вход триггера 9, на вход сумматора по модулю два 10 и одновременно записывается в регистр 5, на тактовый вход которого поступают тактовые импульсы с тактовой шины 2. На счетный вход первого счетчика импульсов 6 поступают тактовые импульсы с тактовой шины 2. В зависимости от состояния первого счетчика импульсов 6 изменяются режимы работы группы элементов И 16 и дополнительной группы элементов И 17, которые осуществляют разделение символов двоичного кода Хемминга. Разделенные символы поступают соответственно на счетные входы триггеров группы триггеров 18 и на счетные входы триггеров группы триггеров 19, которые позволяют осуществить операцию сложения по модулю два и запомнить результат сложения. Таким образом, по окончании цикла приема в триггерах группы триггеров 18 будет записан синдром ошибки 101, а в триггерах группы триггеров 19 - 100. С выходов триггеров групп триггеров 18 и 19 синдромы ошибки поступают на входы дешифраторов 13 и 14, формирующих векторы ошибки соответственно 0000100 и 0001000. Полученные векторы ошибки суммируются по модулю два с соответствующими принятыми комбинациями, записанными в регистры 4 и 5, при помощи групп сумматоров по модулю два 20 и 21. Соответствующие исправленные комбинации 1011010 и 1011010 поступают соответственно на первые и вторые входы мультиплексора 15.

Синдром ошибки с выходов триггеров группы триггеров 19 поступает также на входы элемента ИЛИ 8. Синдром ошибки ненулевой, на выходе элемента ИЛИ 8 устанавливается уровень "1". Триггер 9 производит подсчет числа единиц в принятой комбинации, у которой стертые позиции заменены нулями, осуществляя тем самым ее проверку на четность. Таким образом, по окончании цикла приема в триггере 9 будет записана "1". Сумматор по модулю два 10 осуществляет сложение по модулю два принятой комбинации, у которой стертые позиции заменены нулями, и принятой комбинации, у которой стертые позиции заменены единицами. Результат сложения поступает на счетный вход счетчика импульсов 7, на выходах которого по окончании цикла приема формируется двоичная комбинация 010, соответствующая числу стертых символов в принятой комбинации. В зависимости от сигналов, поступающих с выходов элемента ИЛИ 8, триггера 9, второго счетчика импульсов 7, а также с четвертого выхода первого счетчика импульсов 6 на соответствующие входы решающего устройства 11, в конце цикла приема на его первом выходе устанавливается уровень "1", разрешающая мультиплексору 15 выдачу на информационные выходы устройства 22 сигналов со вторых входов: 1011010. Уровень "1" на втором выходе решающего устройства 11, являющемся управляющим выходом 23, разрешает чтение информации с информационных выходов устройства 22. Сигналы с остальных выходов, поступающие на формирователь параметров зоны стирания 12 и управляющие величиной порогов зоны стирания, будут соответственно прошивке ПЗУ нулевыми. Параметры зоны стирания не изменятся. Цикл декодирования завершен.

Последнее изменение параметров зоны стирания потребовалось для создания "запаса", позволяющего отслеживать определенные изменения помех и при этом успешно декодировать принятые комбинации, ведь большее число переходов из этого состояния в ближайшее все еще позволяет осуществлять успешное декодирование, чего нельзя сказать о предыдущем состоянии.

Алгоритм декодирования, используемый в предлагаемом устройстве, универсален, т. е. его сложность не зависит от длины используемой кодовой комбинации. Иными словами, содержимое ПЗУ всегда будет таким, как показано в таблице 1.

Область применения предлагаемого устройства весьма широка. Например, оно может применяться в различных системах передачи информации, использующих разнообразные каналы связи, в том числе и такие перспективные, как оптические, позволяя повысить скорость передачи информации за счет увеличения числа декодируемых разрешенных комбинаций в единицу времени. По той же причине эффективно использование устройства в системах с обратными связями. Весьма часто используется модифицированный код Хемминга в устройствах хранения информации. Здесь есть возможность подбора приемлемых параметров зоны стирания при многократном считывании поврежденной комбинации. К тому же предлагаемое устройство полностью совместимо с известными системами, использующими модифицированный код Хемминга, что допускает их усовершенствование путем доработки только декодирующего устройства при минимальных затратах и также способствует повышению скорости передачи информации.

Литература

1. Агаханян Т.М. Интегральные микросхемы: Учеб. пособие для вузов. - М.: Энергоатомиздат, 1983. - 464 с., ил.

2. Микросхемы памяти, ЦАП, АЦП: Справочник. 2-е изд., стереотип./О.Н. Лебедев, А-Й.К. Марцинкявичюс, Э.-А.К. Багданскис и др.; - М.: КУбК-а, 1996. - 384 с.: ил.

3. Аванесян Г.Р., Левшин В.П. Интегральные микросхемы ТТЛ, ТТЛШ: Справочник. - М.: Машиностроение, 1993. - 256 с.: ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для декодирования двоичных кодов Хэмминга | 1985 |

|

SU1307593A1 |

| УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ ПО ЦИКЛАМ | 2003 |

|

RU2231228C1 |

| МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ | 1997 |

|

RU2111528C1 |

| Многоканальный аналого-цифровой преобразователь | 1985 |

|

SU1339890A1 |

| УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ ВЕНТИЛЬНЫМ ПРЕОБРАЗОВАТЕЛЕМ | 1991 |

|

RU2064730C1 |

| УСТРОЙСТВО ИЗМЕРЕНИЯ ПАРАМЕТРОВ ОШИБОК В КАНАЛЕ | 2001 |

|

RU2192038C1 |

| Устройство для декодирования двоичных кодов Хемминга | 1982 |

|

SU1051709A1 |

| МОДУЛЬ СИСТЕМЫ МИКРОПРОГРАММНОГО УПРАВЛЕНИЯ | 1999 |

|

RU2152071C1 |

| УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ ПО ЦИКЛАМ | 2002 |

|

RU2239953C2 |

| Устройство для декодирования двоичных кодов Хемминга | 1980 |

|

SU940299A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано в аппаратуре передачи данных по каналу с помехами. Техническим результатом является обеспечение более высокой скорости передачи информации. Устройство содержит регистры, счетчики импульсов, группы триггеров, сумматоры по модулю два, дешифраторы, мультиплексор, формирователь параметров зоны стирания, решающий блок, предназначенный для разделения принятой комбинации с замененными стертыми позициями на единицы или нули соответственно, и решающее устройство, реализованное на ПЗУ для хранения управляющих величин порогов зон стирания, соответствующих прошивке ПЗУ. 1 табл., 7 ил.

Устройство для декодирования двоичных кодов Хемминга, содержащее первый и второй регистры, первый и второй счетчики импульсов, группу элементов И, группу триггеров, элемент ИЛИ, триггер, тактовую шину, решающий блок, первый вход которого является входом устройства, второй выход которого соединен с информационным входом второго регистра, тактовый вход которого соединен с тактовой шиной, счетный вход первого счетчика импульсов соединен с тактовой шиной, а первый - третий выходы соединены со вторыми входами соответствующих элементов И группы элементов И, выходы которых соединены с входами соответствующих триггеров группы триггеров, отличающееся тем, что в него введены дополнительная группа элементов И, дополнительная группа триггеров, первый и второй дешифраторы, первая и вторая группы сумматоров по модулю два, мультиплексор, сумматор по модулю два, решающее устройство и формирователь параметров зоны стирания, первый выход решающего блока соединен с первыми входами элементов И первой группы элементов И, вторым входом сумматора по модулю два и информационным входом первого регистра, второй выход решающего блока соединен со вторыми входами элементов И дополнительной группы элементов И, со счетным входом триггера и с первым входом сумматора по модулю два, выход которого соединен со счетным входом второго счетчика, а первый - третий выходы первого счетчика соединены с первыми входами элементов И дополнительной группы элементов И, тактовый вход первого регистра соединен с тактовой шиной, выходы элементов И дополнительной группы элементов И соединены с соответствующими счетными входами триггеров дополнительной группы триггеров, выходы триггеров обеих групп соединены соответственно с входами соответствующих дешифраторов, выходы триггеров дополнительной группы триггеров соединены с входами элемента ИЛИ, выходы первого и второго дешифраторов соединены соответственно с первыми и вторыми входами соответствующих сумматоров по модулю два соответственно первой и второй групп сумматоров по модулю два, соответствующие вторые и первые входы которых связаны соответственно с выходами первого и второго регистров, выходы сумматоров по модулю два первой и второй групп сумматоров по модулю два подключены соответственно к соответствующим входам первой и второй групп входов мультиплексора, выходы которого являются информационными выходами устройства, а выходы второго счетчика импульсов, выход триггера, выход элемента ИЛИ и четвертый выход первого счетчика импульсов соединены с соответствующими входами решающего устройства, первый выход которого соединен с управляющим входом мультиплексора, второй выход является управляющим выходом, а остальные выходы соединены с соответствующими входами формирователя параметров зоны стирания, один выход которого соединен со вторым, а другой - с третьим входом решающего блока.

| Устройство для декодирования двоичных кодов Хэмминга | 1985 |

|

SU1307593A1 |

| SU 1150771 А, 15.04.1984 | |||

| ПЕТЕРСОН У | |||

| Коды, исправляющие ошибки | |||

| - М.: Мир, 1964, с.89 - 91 | |||

| Дорожная спиртовая кухня | 1918 |

|

SU98A1 |

| Устройство для защиты земляногоСООРужЕНия OT эРОзии | 1979 |

|

SU800279A1 |

Авторы

Даты

2000-12-27—Публикация

1999-05-28—Подача