ОБЛАСТЬ ТЕХНИКИ

Изобретение относится к области вычислительной техники, в частности к устройствам обработки данных, и может быть использовано для построения функциональных узлов для анализа свойств генераторов псевдослучайных последовательностей двоичных чисел, фильтрации событий, обработки сигналов, изображений и результатов физических экспериментов.

ПРЕДШЕСТВУЮЩИЙ УРОВЕНЬ ТЕХНИКИ

Известно устройство для детектирования единичных групп бит в бинарной последовательности RU №2763859 МПК G06F 7/74, Н03К 21/00 заявлено 29.04.2021, опубликовано 11.01.2022, Бюл. №2) содержащее внешний вход данных DI, группу внешних выходов данных QB, группу внешних выходов количества групп QG, первый RS-триггер пуска-останова TSS 1, первый счетчик бит СТВ 2, регистр номера первого бита группы RGB 3, первый элемент И 4, первый элемент ИЛИ 5 с одним инверсным входом, второй триггер единичных бит TR1 6, второй элемент И 7 с одним инверсным входом, второй счетчик единиц CTU 8, блок равенства нижней границе 9, блок равенства верхней границе 10, третий триггер нижней границы TRL 11, четвертый триггер верхней границы TRM 12, третий 13 и четвертый 14 элементы И с двумя инверсными входами, второй элемент ИЛИ 15, выходной буфер ОВ 16 и третий счетчик количества групп CTG 17, а также введены внешние входы асинхронной установки в нулевое состояние CLR, пуска устройства START, остановки устройства STOP и тактовый С, внешние входные шины нижней границы GL и верхней границы GM диапазона единичных бит, внешняя шина управления обменом ЕО, внешние флаг «Буфер заполнен» FF и флаг «Буфер пуст» FZ.

В данном устройстве осуществляется выявление единичных групп заданной размерности, определение количества групп и их расположение во входной последовательности данных. Недостатком данного устройства является отсутствие средств для детектирования заданных шаблонов содержащих совокупность групп (рядов) как нулевых, так и единичных бит.

Известно устройство для детектирования перекрывающихся шаблонов бит в двоичной последовательности RU №2787294 МПК G06F 7/74, Н03К 21/00 заявлено 31.03.2022, опубликовано 09.01.2023, Бюл. №1) содержит внешний вход данных ID, группу внешних входов шаблона IS, содержащую К разрядов, группу внешних входов IК задания разрядности входного шаблона IS, содержащую m разрядов (где m=]log2(К+1)[большее целое), группу внешних выходов данных QB, группу внешних выходов количества шаблонов OS, а также содержит RS-триггер пуска-останова TSS 1, первый счетчик бит СТВ 2, выходной буфер ОВ 3, второй вычитающий счетчик разрядов шаблона СТК 4, элемент И 5, регистр сдвига входных данных RD 6, дешифратор DC 7, группу из (К-1) элементов ИЛИ 81, 82,…, 8(К-1), первую группу из К элементов И 91, 92,…, 9К, вторую группу из К элементов И 101, 102,…, 10К, компаратор СОМР 11 и третий счетчик количества шаблонов CTS 12, а также введены внешние входы тактового сигнала 1С, пуска устройства START, остановки устройства STOP и внутренние шина дешифрации разрядов BDC, шина первого операнда сравнения ВА, шина второго операнда сравнения ВВ, внутренний флаг равенства FEQ и внутренний флаг записи FW, внешняя шина управления обменом ЕО, внешние флаг «Буфер заполнен» FF и флаг «Буфер пуст» FZ.

В данном устройстве осуществляется выявление перекрывающихся шаблонов, содержащих совокупность групп (рядов) как нулевых, так и единичных бит, задание значений шаблонов и их разрядности, определение количества выявленных шаблонов и их расположение во входной последовательности данных. Недостатком данного устройства является отсутствие средств для выявления неперекрывающихся шаблонов и определение числа бит между заданными шаблонами.

Наиболее близким устройством того же назначения к заявленному изобретению по совокупности признаков является, принятое за прототип, устройство для детектирования перекрывающихся и неперекрывающихся шаблонов бит в двоичной последовательности RU №2807299 МПК G06F 7/74, Н03К 21/00 заявлено 11.04.2023, опубликовано 13.11.2023, Бюл. №32) содержит внешний вход данных ID, группу внешних входов шаблона IS, содержащую К разрядов, группу внешних входов IК задания разрядности входного шаблона IS, содержащую m разрядов (где m=]log2(К+1)[большее целое), группу внешних выходов данных QB, группу внешних выходов количества перекрывающихся шаблонов OS, группу внешних выходов количества неперекрывающихся шаблонов QN, а также содержит первый RS-триггер пуска-останова TSS 1, второй триггер задержки TZ 2, первый счетчик бит СТВ 3, выходной буфер ОВ 4, первый элемент И с инверсным входом 5, первый элемент ИЛИ 6, третий триггер записи TW 7, второй элемент ИЛИ 8, второй вычитающий счетчик разрядов шаблона СТК 9, второй элемент И 10, третий элемент И 11, третий счетчик количества перекрывающихся шаблонов CTS 12, четвертый счетчик количества неперекрывающихся шаблонов CTN 13, регистр сдвига входных данных RD 14, дешифратор DC 15, группу из (К-1) элементов ИЛИ 161, 162,…, 16(К-1), первую группу из К элементов И 171, 172,…, 17К, вторую группу из К элементов И 181, 182,…, 18К и компаратор СОМР 19, а также в него введены внешние входы тактового сигнала 1С, пуска устройства START, остановки устройства STOP и внутренние шина дешифрации разрядов BDC, шина первого операнда сравнения ВА, шина второго операнда сравнения ВВ, внутренние флаг равенства FEQ, флаг загрузки счетчика СТК FL, флаг неперекрывающихся шаблонов FN, флаг разрешения шаблонов FS, флаг первого состояния счетчика СТК FS1, флаг задержки старта FZS и флаг записи FW, внешняя шина управления обменом ЕО, внешние флаг «Буфер заполнен» FF и флаг «Буфер пуст» FZ.

В данном устройстве осуществляется выявление перекрывающихся и неперекрывающихся шаблонов, содержащих совокупность групп (рядов) как нулевых, так и единичных бит, задание значений шаблонов и их разрядности, определение количества выявленных шаблонов и их расположение во входной последовательности данных. Недостатком данного устройства является отсутствие средств для определения интервалов между заданными шаблонами.

ЗАДАЧА ИЗОБРЕТЕНИЯ

Задачей изобретения является разработка аппаратных средств для исследования свойств генераторов псевдослучайных последовательностей двоичных чисел, а также для фильтрации событий, обработки сигналов, обработки результатов физических экспериментов и изображений.

При анализе генераторов псевдослучайных последовательностей двоичных чисел устройство предназначено для выявления и разделения перекрывающихся и неперекрывающихся групп, соответствующих заданным шаблонам из совокупности групп (рядов) нулевых и единичных бит, и определение числа бит между шаблонами.

При обработке результатов физических экспериментов устройство предназначено для выявления непериодических событий (областей) - заданных длительностей событий и интервалов между ними, а также наличие других единичных событий между детектируемыми шаблонами.

Техническим результатом изобретения расширение арсенала средств того же назначения, в части возможности детектирования и разделения перекрывающихся и неперекрывающихся шаблонов заданной разрядности, определении их количества, а также подсчет числа бит в интервалах между шаблонами и выявление единичных бит между шаблонами.

КРАТКОЕ ОПИСАНИЕ СУЩНОСТИ ИЗОБРЕТЕНИЯ

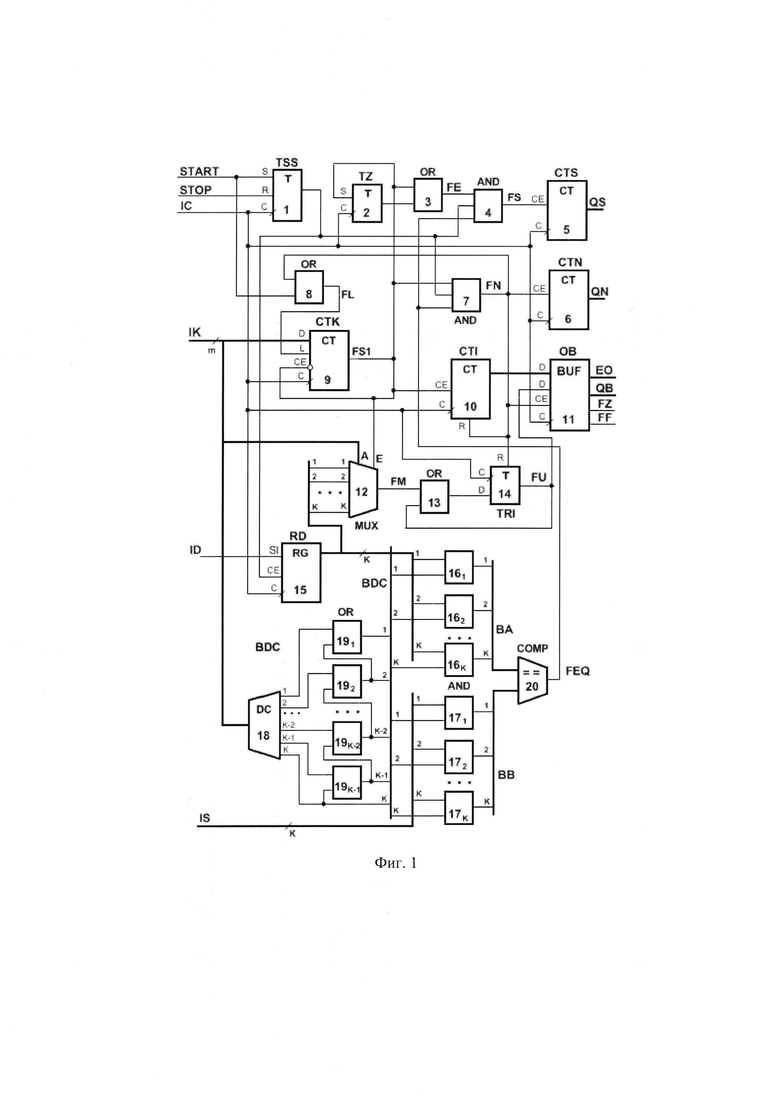

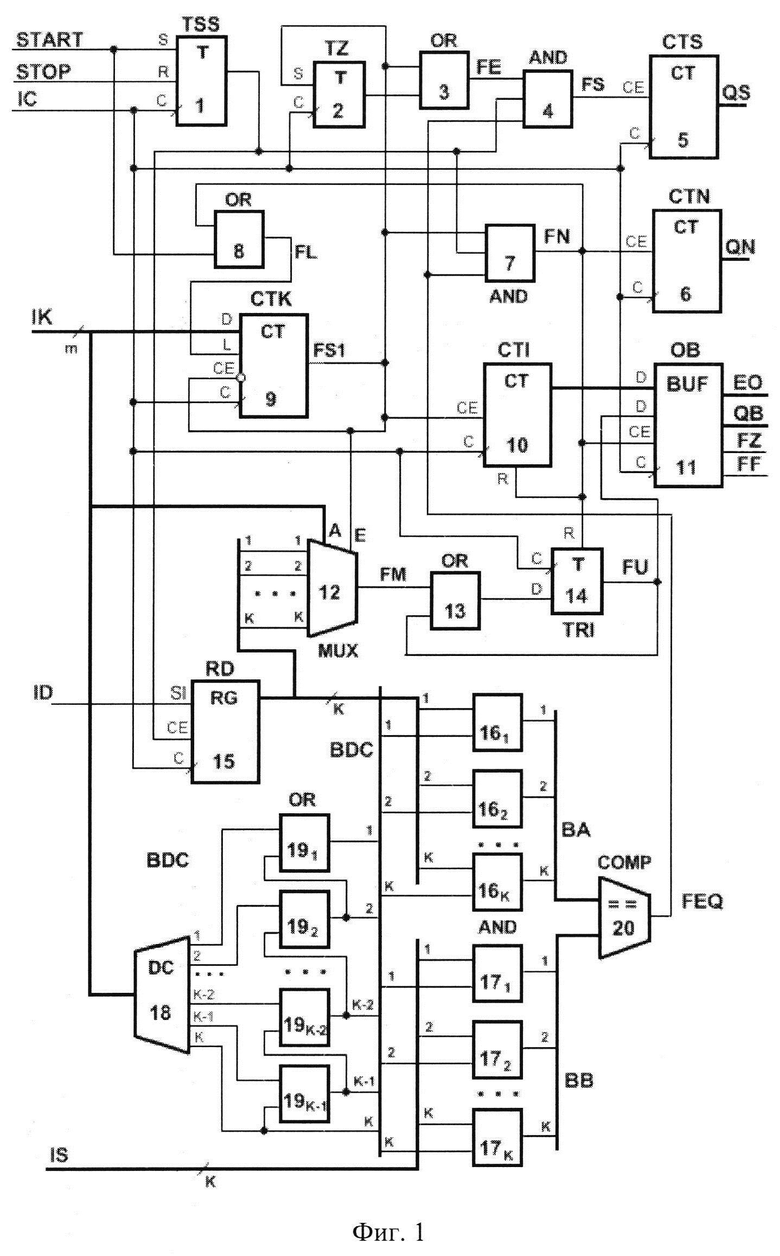

Указанный технический результат при осуществлении изобретения достигается тем, что устройство для детектирования шаблонов бит и определение числа бит между шаблонами содержит внешний вход данных ID, группу внешних входов шаблона IS, содержащую К разрядов, группу внешних входов IК задания разрядности входного шаблона IS, содержащую m разрядов (где m=]log2(К+1)[большее целое), группу внешних выходов данных ОВ, группу внешних выходов количества перекрывающихся шаблонов QS, группу внешних выходов количества неперекрывающихся шаблонов QN,

а также содержит первый RS-триггер пуска-останова TSS 1, второй триггер задержки TZ 2, первый элемент ИЛИ 3, первый элемент И 4, первый счетчик количества перекрывающихся шаблонов CTS 5, второй счетчик количества неперекрывающихся шаблонов CTN 6, второй элемент И 7, второй элемент ИЛИ 8, третий вычитающий счетчик разрядов шаблона СТК 9, четвертый счетчик интервалов CTI 10, выходной буфер ОВ 11, мультиплексор MUX 12, третий элемент ИЛИ 13, третий триггер единичных бит интервала TRI 14, регистр сдвига входных данных RD 15, первую группу из К элементов И 161, 162,…, 16К, вторую группу из К элементов И 171, 172,…, 17К, дешифратор DC 18, группу из (К-1) элементов ИЛИ 191, 192,…,19(К-1), компаратор СОМР 20,

а также введены внешние входы тактового сигнала IC, пуска устройства START, остановки устройства STOP и внутренние шина дешифрации разрядов BDC, шина первого операнда сравнения ВА и шина второго операнда сравнения ВВ, внутренние флаг разрешения шаблонов FE, флаг равенства FEQ, флаг FL загрузки счетчика СТК, флаг бита интервала FM, флаг неперекрывающихся шаблонов FN, флаг перекрывающихся шаблонов FS, флаг FS1 первого состояния счетчика СТК и флаг единичного интервала FU, внешняя шина управления обменом ЕО, внешние флаг «Буфер заполнен» FF и флаг «Буфер пуст» FZ,

причем внешний тактовый вход устройства IC соединен с входами синхронизации С первого RS-триггера пуска-останова TSS 1, второго триггера задержки TZ 2, первого счетчика количества перекрывающихся шаблонов CTS 5, второго счетчика количества неперекрывающихся шаблонов CTN 6, третьего вычитающего счетчика разрядов шаблона СТК 9, четвертого счетчика интервалов CTI 10, выходного буфера ОВ 11, третьего триггера единичных бит интервала TRI 14 и регистра сдвига входных данных RD 15,

внешний вход пуска устройства START соединен с входом S синхронной установки в единичное состояние первого RS-триггера пуска-останова TSS 1 и вторым входом второго элемента ИЛИ 8,

внешний вход остановки устройства STOP соединен с входом R синхронной установки в нулевое состояние первого RS-триггера пуска-останова TSS 1,

причем прямой выход первого RS-триггера пуска-останова TSS 1 соединен со вторыми входами первого 4 и второго 7 элементов И, с входом СЕ разрешения работы регистра сдвига входных данных RD 15, а выход второго триггера задержки TZ 2 соединен со вторым входом первого элемента ИЛИ 3,

внешний вход данных ID соединен с входом SI последовательного ввода регистра сдвига входных данных RD 15, группа К выходов которого соединена с одноименными информационными входами мультиплексора 12 и соединена с первыми входами соответствующих одноименных элементов первой группы из К элементов И 161, 162,…. 16К, выходы которых являются соответствующими одноименными разрядами внутренней шины первого операнда сравнения ВА, которая соединена с первой группой входов компаратора СОМР 20,

К разрядов группы внешних входов шаблона IS соединены с первыми входами соответствующих одноименных элементов второй группы из К элементов И 171, 172,…. 17К, выходы которых являются соответствующими одноименными разрядами внутренней шины второго операнда сравнения ВВ, которая соединена со второй группой входов компаратора СОМР 20, выход которого является внутренним флагом равенства FEQ и соединен со третьими входами первого 4 и второго 7 элементов И,

причем группа внешних входов IK задания разрядности входного шаблона IS соединена с соответствующей группой D-входов третьего счетчика разрядов шаблона СТК 9, с адресными входами мультиплексора 12 и с адресными входами дешифратора DC 18, у которого выходы, с первого выхода до (К-1)-го выхода, соединены с первыми входами соответствующих одноименных элементов И группы из (К-1) элементов 191, 192,…, 19(К-1), выходы которых являются соответствующими одноименными разрядами, с первого разряда до (К-1)-го разряда, внутренней шины дешифрации разрядов BDC, у которой К-й разряд соединен с К-м выходом дешифратора DC 18, а К разрядов внутренней шины дешифрации разрядов BDC соединены со вторыми входами соответствующих одноименных элементов первой группы из К элементов И 161, 162,…, 16К и второй группы из К элементов И 171, 172,…, 17К,

кроме того выходы элементов группы 192, 193,…, 19(К-1) из (К-1) элементов ИЛИ, начиная с выхода (К-1)-го элемента 19(К-1) до второго элемента 192, соединены со вторыми входами соответствующих предыдущих элементов ИЛИ группы 191, 192,…, 19(К-2), начиная с (К-2)-го элемента 19(К-2) до первого элемента 191, а второй вход (К-1)-го элемента 19(К-1) соединен с К-м выходом дешифратора DC 18,

причем выход мультиплексора 12 является внутренним флагом бита интервала FM и соединен с первым входом третьего элемента ИЛИ 13, выход которого соединен с информационным D-входом третьего триггера единичных бит интервала TRI 14, выход которого является внутренним флагом единичного интервала FU и соединен со вторым входом третьего элемента ИЛИ 13 и со вторым D-входом выходного буфера ОВ 11,

кроме того выход первого состояния третьего вычитающего счетчика разрядов шаблона СТК 9 является внутренним флагом FS1 первого состояния и соединен с инверсным входом разрешения работы СЕ счетчика разрядов шаблона СТК 9, с входом S синхронной установки в единичное состояние второго триггера задержки TZ 2, с первым входом первого элемента ИЛИ 3, с первым входом второго элемента И 7, с входом разрешения Е мультиплексора 12 и с входом СЕ разрешения работы четвертого счетчика интервалов CTI 10, выходы которого соединены с первой группой D-входов выходного буфера ОВ 11, который также подключен к внешней шине ЕО управления обменом, а соответствующие выходы выходного буфера ОВ 4 являются группой внешних выходов данных QB и внешними флагами «Буфер заполнен» FF и «Буфер пуст» FZ,

причем выход первого элемента ИЛИ 3 является внутренним флагом разрешения шаблонов FE и соединен с первым входом первого элемента И 4, выход которого является внутренним флагом перекрывающихся шаблонов FS и соединен с входом разрешения работы СЕ первого счетчика количества перекрывающихся шаблонов CTS 5, выходы которого являются группой внешних выходов количества перекрывающихся шаблонов QS,

кроме того выход второго элемента ИЛИ 8 является внутренним флагом FL загрузки счетчика СТК 9 и соединен с входом разрешения загрузки L третьего вычитающего счетчика разрядов шаблона СТК 9, а выход второго элемента И 7 является внутренним флагом FN неперекрывающихся шаблонов и соединен с первым входом второго элемента ИЛИ 8, входами R синхронной установки в нулевое состояние четвертого счетчика интервалов CTI 10 и третьего триггера единичных бит интервала TRI 14, а также соединен с входами разрешения работы СЕ выходного буфера ОВ 11 и второго счетчика количества неперекрывающихся шаблонов CTN 6, выходы которого являются группой внешних выходов количества неперекрывающихся шаблонов QN.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

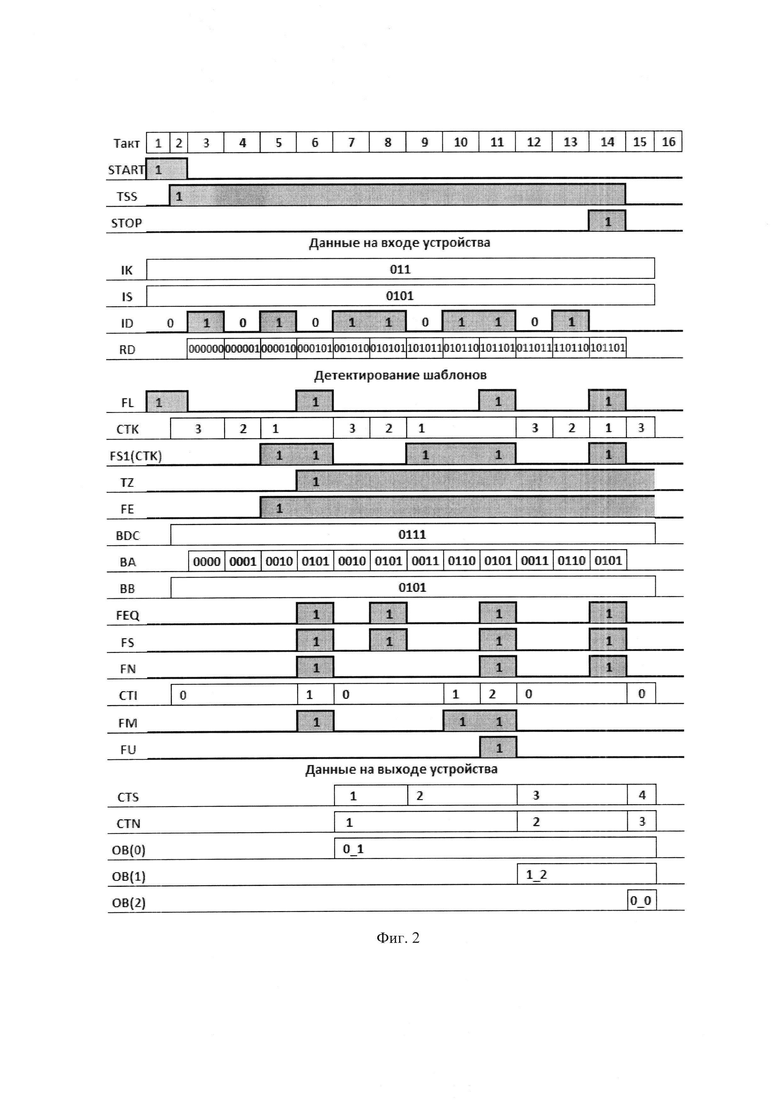

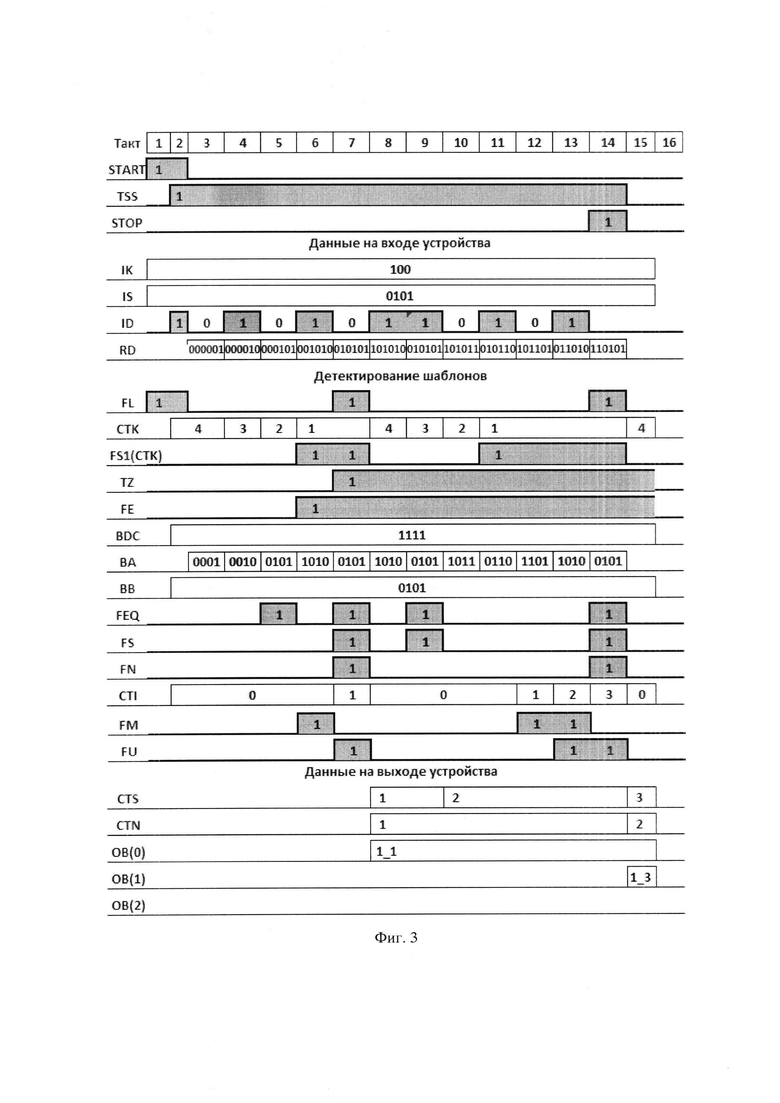

На фиг. 1 представлена схема предлагаемого устройства. На фиг. 2 и фиг. 3 приведены временные диаграммы работы устройства.

На фиг. 1-3 и в тексте приняты следующие обозначения:

А - адресные входы,

BUF - буфер с дисциплиной обслуживания FIFO,

ВА - внутренняя шина первого операнда сравнения,

ВВ - внутренняя шина второго операнда сравнения,

BDC - внутренняя шина дешифрации разрядов,

С - тактовый вход,

СЕ - вход разрешения работы,

СОМР - схема сравнения (компаратор),

СТ - счетчик,

CTI - счетчик интервалов,

СТК - вычитающий счетчик разрядов шаблона,

CTS - счетчик количества перекрывающихся шаблонов,

CTN - счетчик количества неперекрывающихся шаблонов,

D - информационные входы,

DC - дешифратор,

IC - внешний тактовый вход,

ID - внешний вход данных,

IК - группа внешних входов задания разрядности входного шаблона IS, содержащая m разрядов (где m=]log2(К+1)[большее целое),

IS - группа внешних входов задания шаблона, содержащая К разрядов,

Е - вход разрешения,

ЕО - внешняя шина управления обменом с выходным буфером ОВ,

FE - внутренний флаг разрешения шаблонов,

FEQ - внутренний флаг равенства,

FL - внутренний флаг загрузки счетчика СТК,

FM - внутренний флаг бита интервала,

FN - внутренний флаг неперекрывающихся шаблонов,

FS - внутренний флаг перекрывающихся шаблонов,

FS1 - внутренний флаг первого состояния счетчика СТК,

FU - внутренний флаг единичного интервала,

FF - внешний флаг «Буфер заполнен»,

FZ - внешний флаг «Буфер пуст»,

К - разрядность шаблона,

L - вход разрешения записи,

MUX - мультиплексор,

N - размерность (длина) входной последовательности данных,

ОВ - выходной буфер,

QB - группа внешних выходов данных,

ON - группа внешних выходов количества неперекрывающихся шаблонов,

QS - группа внешних выходов количества перекрывающихся шаблонов,

RD - регистр сдвига входных данных,

RG - регистр,

R - вход синхронной установки в нулевое состояние,

S - вход синхронной установки в единичное состояние,

SI - вход последовательного ввода регистра RD,

START - внешний вход пуска,

STOP - внешний вход останова,

Т - триггер,

TRI - триггер единичных бит интервала,

TSS - триггер пуска-останова,

TZ - триггер задержки,

1 - первый RS-триггер пуска-останова TSS,

2 - второй триггер задержки TZ,

3 - первый элемент ИЛИ (OR),

4 - первый элемент И (AND),

5 - первый счетчик количества перекрывающихся шаблонов CTS,

6 - второй счетчик количества неперекрывающихся шаблонов CTN,

7 - второй элемент И (AND),

8 - второй элемент ИЛИ (OR),

9 - третий вычитающий счетчик разрядов шаблона СТК,

10 - четвертый счетчик интервалов CTI,

11 - выходной буфер ОВ,

12 - мультиплексор MUX,

13 - третий элемент ИЛИ (OR),

14 - третий триггер единичных бит интервала TRI,

15 - регистр сдвига входных данных RD,

161, 162,…, 16К - первая группа из К элементов И (AND),

171, 172,…, 17К - вторая группа из К элементов И (AND),

18 - дешифратор DC,

191, 192,…, 19(К-1) - группа из (К-1) элементов ИЛИ (OR),

20 - компаратор (СОМР).

Предлагаемое устройство содержит внешний вход данных ID, группу внешних входов шаблона IS, содержащую К разрядов, группу внешних входов IК задания разрядности входного шаблона IS, содержащую m разрядов (где m=]log2(К+1)[большее целое), группу внешних выходов данных QB, группу внешних выходов количества перекрывающихся шаблонов OS, группу внешних выходов количества неперекрывающихся шаблонов QN, а также содержит первый RS-триггер пуска-останова TSS 1, второй триггер задержки TZ 2, первый элемент ИЛИ 3, первый элемент И 4, первый счетчик количества перекрывающихся шаблонов CTS 5, второй счетчик количества неперекрывающихся шаблонов CTN 6, второй элемент И 7, второй элемент ИЛИ 8, третий вычитающий счетчик разрядов шаблона СТК 9, четвертый счетчик интервалов CTI 10, выходной буфер ОВ 11, мультиплексор MUX 12, третий элемент ИЛИ 13, третий триггер единичных бит интервала TRI 14, регистр сдвига входных данных RD 15, первую группу из К элементов И 161, 162,…, 16К, вторую группу из К элементов И 171, 172,…, 17К, дешифратор DC 18, группу из (К-1) элементов ИЛИ 191, 192,…, 19(К-1), компаратор СОМР 20.

В предлагаемое устройство также введены внешние входы тактового сигнала IC, пуска устройства START, остановки устройства STOP и внутренние шина дешифрации разрядов BDC, шина первого операнда сравнения ВА и шина второго операнда сравнения ВВ, внутренние флаг разрешения шаблонов FE, флаг равенства FEQ, флаг FL загрузки счетчика СТК, флаг бита интервала FM, флаг неперекрывающихся шаблонов FN, флаг перекрывающихся шаблонов FS, флаг FS1 первого состояния счетчика СТК и флаг единичного интервала FU, внешняя шина управления обменом ЕО, внешние флаг «Буфер заполнен» FF и флаг «Буфер пуст» FZ.

Второй регистр сдвига входных данных RD 18 предназначен для преобразования входной последовательности данных ID в параллельные К-разрядные группы. Третий вычитающий счетчик разрядов шаблона СТК 9 предназначен для подсчета IК бит (разрядов) текущей группы входной последовательности данных ID и формировании единичного значения флага FS1=1 первого состояния при установке в счетчике кода СТК=1. Последующий счет начинается после выявления группы соответствующей заданному неперекрывающемуся шаблону и после загрузки в счетчик СТК 9 разрядности шаблона IК при единичном значении флага загрузки FL=1 (после загрузки в счетчик формируется нулевое значение флага FS1=0). Третий триггер единичных бит интервала TRI 14 предназначен для фиксации единичного флага бита интервала FM=1. Четвертый счетчик интервалов CTI 10 осуществляет счет бит после выявленной группы соответствующей заданному неперекрывающемуся шаблону. Выходной буфер ОВ 11 предназначен для записи значений интервалов (число бит) между неперекрывающимися шаблонами и флага единичного интервала FU, который принимает единичное значение FU=1 если в интервале между неперекрывающимися шаблонами выявлены единичные биты.

Внешний тактовый вход устройства IC соединен с входами синхронизации С первого RS-триггера пуска-останова TSS 1, второго триггера задержки TZ 2, первого счетчика количества перекрывающихся шаблонов CTS 5, второго счетчика количества неперекрывающихся шаблонов CTN 6, третьего вычитающего счетчика разрядов шаблона СТК 9, четвертого счетчика интервалов CTI 10, выходного буфера ОВ 11, третьего триггера единичных бит интервала TRI14 и регистра сдвига входных данных RD 15.

Внешний вход пуска устройства START соединен с входом S синхронной установки в единичное состояние первого RS-триггера пуска-останова TSS 1 и вторым входом второго элемента ИЛИ 8.

Внешний вход остановки устройства STOP соединен с входом R синхронной установки в нулевое состояние первого RS-триггера пуска-останова TSS 1.

Первый RS-триггер пуска-останова TSS 1 предназначен для выделения цикла работы предлагаемого устройства, между сигналами START и STOP, для входной последовательности данных ID размерности N. Причем прямой выход первого RS-триггера пуска-останова TSS 1 соединен со вторыми входами первого 4 и второго 7 элементов И, с входом СЕ разрешения работы регистра сдвига входных данных RD 15, а выход второго триггера задержки TZ 2 соединен со вторым входом первого элемента ИЛИ 3.

Внешний вход данных ID соединен с входом SI последовательного ввода регистра сдвига входных данных RD 15, группа К выходов которого соединена с одноименными информационными входами мультиплексора 12 и соединена с первыми входами соответствующих одноименных элементов первой группы из К элементов И 161, 162,…. 16К, выходы которых являются соответствующими одноименными разрядами внутренней шины первого операнда сравнения ВА, которая соединена с первой группой входов компаратора СОМР 20.

К разрядов группы внешних входов шаблона IS соединены с первыми входами соответствующих одноименных элементов второй группы из К элементов И 171, 172,…. 17К, выходы которых являются соответствующими одноименными разрядами внутренней шины второго операнда сравнения ВВ, которая соединена со второй группой входов компаратора СОМР 20, выход которого является внутренним флагом равенства FEQ и соединен со третьими входами первого 4 и второго 7 элементов И.

Группа внешних входов IK задания разрядности входного шаблона IS соединена с соответствующей группой D-входов третьего счетчика разрядов шаблона СТК 9, с адресными входами мультиплексора 12 и с адресными входами дешифратора DC 18, у которого выходы, с первого выхода до (К-1)-го выхода, соединены с первыми входами соответствующих одноименных элементов И группы из (К-1) элементов 191, 192,…, 19(К-1), выходы которых являются соответствующими одноименными разрядами, с первого разряда до (К-1)-го разряда, внутренней шины дешифрации разрядов BDC, у которой К-й разряд соединен с К-м выходом дешифратора DC 18.

К разрядов внутренней шины дешифрации разрядов BDC соединены со вторыми входами соответствующих одноименных элементов первой группы из К элементов И 161, 162,…,16К и второй группы из К элементов И 171, 172,…,17К.

Кроме того, выходы элементов группы 192, 193,…, 19(К-1) из (К-1) элементов ИЛИ, начиная с выхода (К-1)-го элемента 19(К-1) до второго элемента 192, соединены со вторыми входами соответствующих предыдущих элементов ИЛИ группы 191, 192,…, 19(К-2), начиная с (К-2)-го элемента 19(К-2) до первого элемента 191, а второй вход (К-1)-го элемента 19(К-1) соединен с К-м выходом дешифратора DC 18.

Выход мультиплексора 12 является внутренним флагом бита интервала FM и соединен с первым входом третьего элемента ИЛИ 13, выход которого соединен с информационным D-входом третьего триггера единичных бит интервала TRI 14, выход которого является внутренним флагом единичного интервала FU и соединен со вторым входом третьего элемента ИЛИ 13 и со вторым D-входом выходного буфера ОВ 11.

Выход первого состояния третьего вычитающего счетчика разрядов шаблона СТК 9 является внутренним флагом FS1 первого состояния и соединен с инверсным входом разрешения работы СЕ счетчика разрядов шаблона СТК 9, с входом S синхронной установки в единичное состояние второго триггера задержки TZ 2, с первым входом первого элемента ИЛИ 3, с первым входом второго элемента И 7, с входом разрешения Е мультиплексора 12 и с входом СЕ разрешения работы четвертого счетчика интервалов CTI 10, выходы которого соединены с первой группой D-входов выходного буфера ОВ 11, который также подключен к внешней шине ЕО управления обменом.

Соответствующие выходы выходного буфера ОВ 4 являются группой внешних выходов данных QB и внешними флагами «Буфер заполнен» FF и «Буфер пуст» FZ.

Причем выход первого элемента ИЛИ 3 является внутренним флагом разрешения шаблонов FE и соединен с первым входом первого элемента И 4, выход которого является внутренним флагом перекрывающихся шаблонов FS и соединен с входом разрешения работы СЕ первого счетчика количества перекрывающихся шаблонов CTS 5, выходы которого являются группой внешних выходов количества перекрывающихся шаблонов QS.

Выход второго элемента ИЛИ 8 является внутренним флагом FL загрузки счетчика СТК 9 и соединен с входом разрешения загрузки L третьего вычитающего счетчика разрядов шаблона СТК 9.

Выход второго элемента И 7 является внутренним флагом FN неперекрывающихся шаблонов и соединен с первым входом второго элемента ИЛИ 8, входами R синхронной установки в нулевое состояние четвертого счетчика интервалов CTI 10 и третьего триггера единичных бит интервала TRI 14, а также соединен с входами разрешения работы СЕ выходного буфера ОВ 11 и второго счетчика количества неперекрывающихся шаблонов CTN 6, выходы которого являются группой внешних выходов количества неперекрывающихся шаблонов QN.

ПОДРОБНОЕ ОПИСАНИЕ СУЩНОСТИ ИЗОБРЕТЕНИЯ

Принцип работы предлагаемого устройства состоит в следующем.

Предлагаемое устройство позволяет детектировать IK-разрядные группы во входном N-разрядном двоичном числе, соответствующие IK разрядному заданному шаблону групп IS, который содержит заданную последовательность единичных и нулевых бит, определять интервалы между неперекрывающимися шаблонами, число бит в интервалах и регистрировать наличие единичных бит в данных интервалах (диапазонах).

Устройство позволяет оперативно изменять (задавать) разрядность IK≤K и значения разрядов шаблона IS. В устройстве подсчитывается количество групп соответствующих заданному коду шаблону IS. При этом разряды выявленных соседних входных групп, совпадающих с заданным шаблоном IS, могут перекрываться или не перекрываться. В устройстве отдельно ведется подсчет на счетчиках перекрывающихся CTS и неперекрывающихся CTN групп, соответствующих заданному шаблону.

На внешний вход данных ID последовательно разряд за разрядом поступают биты входной последовательности данных размерностью N, которые далее передаются на вход последовательного ввода SI сдвига К разрядного второго регистра данных RD 15. На регистре сдвига RD 15 осуществляется сдвиг на один разряд в сторону старших разрядов от первого разряда к К-му разряду. При этом разряды кода входной двоичной последовательности ID преобразуются в параллельные коды на выходах регистра RD 15.

Перед началом работы в начальное нулевое состояние устанавливаются - триггеры TSS 1, TZ 2 и TRI 14, счетчики CTS 5, CTN 6, СТК 9 и CTI 10, регистр RI 15, а также устанавливается начальный нулевой адрес в выходном буфере ОВ 11.

Устройство начинает работать после подачи единичного сигнала START=1, по которому в единичное состояние устанавливается первый RS-триггер 1 пуска-останова TSS=1, а также формируется единичное значение флага FL=1 загрузки счетчика СТК 9 и в вычитающий счетчик разрядов шаблона СТК 9 загружается код «IK» текущей разрядности заданного шаблона IS, значение которого устанавливается на внешней входной К разрядной шине IS. Значения кода «IK» и кода шаблона «IS» должны поддерживаться на входах в течение всего времени работы устройства.

На внешний вход данных ID биты начинают поступать на втором такте сигнала START=1 и далее поступают в каждом такте IC.Далее на следующих IK тактовых сигналах IC осуществляется сдвиг в регистре RD 15 и вычитание в третьем счетчике разрядов шаблона СТК 9, пока не установится единичное значение флага FS1=1 первого состояния на выходе счетчика СТК 9. После ввода последнего N-го разряда входного двоичного числа задается единичный сигнал остановки STOP=1.

Одновременно код «IK» текущей разрядности заданного шаблона IS передается на входы дешифратора DC 18. На выходах дешифратора DC 18 формируются унитарные коды «1 из К», которые передаются на соответствующие входы группы 191, 192,…, 19(К-1) из (К-1) элементов ИЛИ. Единичное значение, установленное на одном из выходов дешифратора DC 18, соответствующем двоичному коду IK, последовательно передается по цепочке элементов ИЛИ 191, 192,…, 19(К-1) в сторону младших разрядов. При этом на внутренней шине дешифрации разрядов BDC устанавливается упорядоченная последовательность единичных значений, начиная с первого разряда до IK-го разряда (при IK≤K) и нулевые значения с (IK+1)-го разряда до старшего К-го разряда (например, унитарный позиционный ряд 00…011…1).

Далее значения разрядов с внутренней шины BDC поступают на вторые входы соответствующих одноименных элементов И первой группы 161, 162,… 16К и второй группы 171, 172,…. 17К. При этом, при единичных значениях разрядов в первой группе 161, 162,…. 16К, на внутреннюю шину первого операнда сравнения ВА передаются IK разрядов входной последовательности данных ID с выходов регистра RD 15, а во второй группе 171, 172,…. 17К на внутреннюю шину второго операнда сравнения ВВ передаются IK разрядов заданного шаблона IS. При этом на шинах ВА и ВВ с (IK+1)-го разряда до старшего К-го разряда формируются нулевые значения.

Далее на компараторе СОМР 20 осуществляется сравнение кодов с внутренних шин первого ВА и второго ВВ операндов и при совпадении формируется единичное значение внутреннего флага равенства FEQ=1. Далее формируется единичное значение внутреннего флага перекрывающихся шаблонов FS=1 на выходе первого элемента И 4, по которому осуществляется увеличение первого счетчика количества выявленных перекрывающихся шаблонов CTS 5.

Одновременно, при единичном значении внутреннего флага равенства FEQ=1, формируется значение флага неперекрывающихся шаблонов FN, в зависимости от значения флага FS1 первого состояния на выходе третьего вычитающего счетчика разрядов шаблона СТК 9. При единичном значении флага FS 1=1 первого состояния счетчика разрядов шаблона СТК 9, когда после предыдущего шаблона поступило «IK» разрядов, формируется единичное значение внутреннего флага неперекрывающихся шаблонов FN=1 на выходе второго элемента И 7, а также осуществляется подсчет нулевых и единичных бит интервала до следующего непересекающегося шаблона на четвертом счетчике интервалов CTI 10. При единичном значении внутреннего флага неперекрывающихся шаблонов FN=1 увеличивается значение второго счетчика количества выявленных неперекрывающихся шаблонов CTN 6.

Кроме того, при выявлении неперекрывающихся шаблонов, при единичном значении флага FN=1, на выходе второго элемента ИЛИ 8 формируется единичное значение внутреннего флага FL=1 загрузки счетчика СТК 9, по которому в вычитающий счетчик разрядов шаблона СТК 9 вновь загружается код «IK» текущей разрядности заданного шаблона IS.

Одновременно, при единичном значении флага FS1=1 первого состояния счетчика разрядов шаблона СТК 9, через мультиплексор 12 разрешается передача IK-го разряда с регистра данных RD 15, формируется внутренний флаг бита интервала FM, значение которого далее через третий элемент ИЛИ 13 передается на D-вход третьего триггера единичных бит интервала TRI 14. Когда поступает первый единичный бит, значение флага FM=1, то триггер TRI 14 устанавливается в единичное состояние, которое далее поддерживается до синхронного сброса по единичному флагу FN=1. При этом на выходе триггера TRI 14 формируется единичное значение внутреннего флага единичного интервала FU=1.

Одновременно при установке единичного значения флага неперекрывающихся шаблонов FN=1 осуществляется запись значений флага единичного интервала FU и с выходов счетчик интервалов CTI 10 в выходной буфер ОВ 11.

Кроме того, при выявлении неперекрывающихся шаблонов, при единичном значении флага FN=1, на выходе второго элемента ИЛИ 8 формируется единичное значение внутреннего флага FL=1 загрузки счетчика СТК 9, по которому в вычитающий счетчик разрядов шаблона СТК 9 вновь загружается код «IK» текущей разрядности заданного шаблона IS.

Далее по следующим тактовым сигналам IC в регистр данных RD 15 при сдвиге записывается один следующий бит входной последовательности данных ID и вновь осуществляется сравнение разрешенных разрядов регистра данных RD 15 с шаблоном IS на компараторе СОМР 20, а также выявление и анализ разрядов интервалов между неперекрывающимися группами, по которым формируются единичные или нулевые значения внутренних флагов равенства FEQ, неперекрывающихся шаблонов FN, перекрывающихся шаблонов FS, загрузки счетчика FL, первого состояния счетчика FS1 и единичного интервала FU.

Предлагаемое устройство работает следующим образом.

На фиг. 2 и фиг. 3 приведены временные диаграммы работы устройства для поиска групп во входных N=12 разрядных двоичных числах соответствующих К=4 разрядным шаблонам IS и кодом m=]log2(4+1)[=3 для разрядности шаблона IK. На фиг. 2 заданный шаблон содержит IK=3 (011) разрядов и значения разрядов шаблона IS=0101, при этом значимыми являются три младших (правых) разряда. На фиг. 3 заданный шаблон содержит IK=4 (100) разряда и значения разрядов шаблона IS=0101, при этом значимыми являются все четыре разряда.

Перед началом работы соответствующие заданные значения для шаблонов задаются на группе внешних входов шаблона IS, содержащей К=4 разряда, и на группе внешних входов задания разрядности входного шаблона IK, содержащей m=3 разряда, которые сохраняются на внешних входах в течении всего времени работы устройства - задания входного N=12 разрядного двоичного числа.

Перед началом работы в начальное нулевое состояние устанавливаются - триггеры TSS 1, TZ 2 и TRI 14, счетчики CTS 5, CTN 6, СТК 9 и CTI 10, регистр RD 15, а также устанавливается начальный нулевой адрес в выходном буфере ОВ 11.

Работа устройства для каждой входной последовательности начинается после подачи единичного сигнала START=1. При этом по фронту тактового сигнала IC (такт 2 на фиг. 2-3) в единичное состояние устанавливается первый RS-триггер 1 пуска-останова TSS=1.

Кроме того, при сигнале START=1 на выходе второго элемента ИЛИ 8 формируется единичное значение флага FL=1 загрузки счетчика СТК 9 и в такте 2 в вычитающий счетчик разрядов шаблона СТК 9 загружается код «IK» текущей разрядности заданного шаблона IS (на фиг. 2 IK=3 (011), на фиг. 3 IK=4 (100)). При этом формируется нулевое значение флага первого состояния счетчика FS1=0 на выходе счетчика разрядов шаблона СТК 9.

Одновременно код IK=3 (011) (фиг. 2) текущей разрядности заданного шаблона IS передается на входы дешифратора DC 18. На выходах дешифратора DC 18 формируются унитарные коды «1 из К», которые передаются на соответствующие первые входы группы 191, 192,…, 19(К-1) из (К-1) элементов ИЛИ, вторые входы которых соединены по цепочке с выходами последующих элементов. Далее сформированный код передается на внутреннюю шину дешифрации разрядов BDC. Для кода IK=3 (011) на шине BDC будет установлено значение унитарного позиционного ряда BDC=0111, по которому на следующих тактах разрешается передача только трех младших разрядов на внутреннюю шину первого операнда сравнения ВА с выходов регистра RD 15 и на внутреннюю шину второго операнда сравнения ВВ с внешних входов заданного шаблона IS. При этом на шине второго операнда сравнения ВВ устанавливается код ВВ=0101.

Единичное значение с выхода первого RS-триггера 1 пуска-останова TSS=1 поступает на вход разрешения работы СЕ регистра данных RD 15, в котором далее на следующих тактах осуществляется последовательный ввод входных данных ID, а также передается на входы первого 4 и второго 7 элементов И, разрешая формировать на них флаги перекрывающихся FS и неперекрывающихся FN шаблонов.

В такте 3 нулевое значение ID=0, первого разряда входной последовательности, (фиг. 2) с входа данных, заданное в такте 2, записывается в регистр сдвига входных данных RD 15, на выходах которых устанавливаются (сохраняются) нулевые значения.

В такте 4 единичное значение ID=1 с входа данных, заданное в такте 3, записывается в регистр сдвига входных данных RD 15, на выходах которого устанавливается код RD=000001, который далее передается на внутреннюю шину первого операнда сравнения ВА=0001, сравнивается с кодом на внутренней шине второго операнда ВВ=0101 и устанавливается нулевое значение внутреннего флага равенства FEQ=0 на выходе компаратора СОМР 20. Одновременно уменьшается на единицу значение третьего вычитающего счетчика 9 разрядов шаблона СТК=2. Также в такте 4 задается нулевое значение следующего третьего бита на входе данных ID=0.

В такте 5 аналогично работают элементы устройства и устанавливаются следующие коды: в регистре RD 15 данных RD=000010, уменьшенное на единицу значение второго вычитающего счетчика 9 разрядов шаблона СТК=1, по которому устанавливается единичное значение внутреннего флага первого состояния счетчика FS 1=1, внутренней шины первого операнда сравнения ВА=0010, внутренней шины бит интервала BU=000000 и внутреннего флага равенства FEQ=0. Кроме того, по единичному флагу первого состояния FS1=1 формируется единичное значение флага разрешения шаблонов FE=1 на выходе первого элемента ИЛИ 3. Также в такте 5 задается единичное значение следующего четвертого бита на входе данных ID=1.

В такте 6 аналогично работают элементы устройства и устанавливаются следующие коды: в регистре RD 15 данных RD=000101, внутренних шинах первого операнда сравнения ВА=0101 и второго операнда сравнения ВВ=0101. Кроме того, по единичному значению флага первого состояния счетчика FS1=1 разрешается работа четвертого 10 счетчика интервалов и устанавливается код CTI=1, а также разрешается передача с третьего разряда (IK=3) регистра данных RD 15 четвертого входного бита через мультиплексор MUX 12 и формирование единичного флага бита интервала FM=1, которое на такте 7 не записывается в третий триггер единичных бит интервала TRI 14, так как на синхронном входе R установки в нулевое состояние установлено единичное значение, поэтому сохраняется нулевое значение флага единичного интервала FU=0. При этом также в третьем вычитающем счетчике 9 разрядов шаблона сохраняется единичное значение СТК=1, так как установлено единичное значение флага первого состояния счетчика FS1=1, по которому запрещается счет в счетчике СТК 9 (в счетчике СЕ=0). Одновременно по единичному значению флага первого состояния счетчика FS1=1 устанавливается в единичное состояние триггер 2 задержки TZ=1, по которому на следующих тактах устанавливается флаг FE=1 и разрешается формирование флага перекрывающихся шаблонов FS.

Одновременно так как совпадают значения кода первого операнда сравнения ВА=0101 и второго операнда ВВ=0101, т.е. выявлена первая группа во входной последовательности соответствующая заданному шаблону IS=0101, то формируется единичное значение внутреннего флага равенства FEQ=1 на выходе компаратора СОМР 20.

Далее, при единичных значениях флага первого состояния FS1=1 третьего счетчика разрядов шаблона СТК 9 и флага равенства FEQ=1, формируется единичное значение внутренних флагов перекрывающихся шаблонов FS=1 на выходе первого элемента И 4 и неперекрывающихся шаблонов FN=1 на выходе второго элемента И 7, по которым разрешается счет (увеличение на единицу) в первом счетчике 5 количества перекрывающихся шаблонов CTS=1 и во втором счетчике 6 количества неперекрывающихся шаблонов CTN=1. Одновременно по единичному флагу FN=1 формируется единичное значение внутреннего флага загрузки счетчика FL=1 на выходе второго элемента ИЛИ 8, по которому в такте 7 в вычитающий третий счетчик 9 разрядов шаблона загружается код «IK» СТК=3.

Кроме того, в такте 7 по единичному флагу FN=1 разрешается работа выходного буфера ОВ 11, в который по нулевому адресу записывается код ОВ(0)=0_1 - нулевое значение флага единичного интервала FU=0 и значение кода с выхода четвертого счетчика интервалов CTI=1, которые соответствуют одному нулевому биту до первого выявленного шаблона.

В тактах 6 и 7 следующие два бита входной последовательности поступают на вход данных ID=01, осуществляется сдвиг на два разряда в регистрах сдвига и в такте 8 устанавливается в регистре 15 данных код RD=010 101, для которого на шине первого операнда сравнения устанавливается код ВА=0101, который совпадает с заданным шаблоном IS=0101. Поэтому в такте 8 формируются единичные значения внутреннего флага равенства FEQ=1 на выходе компаратора СОМР 20 и далее флаг перекрывающихся шаблонов FS=1, по которому разрешается счет (увеличение на единицу) в первом счетчике 5 количества перекрывающихся шаблонов CTS=2. Но при этом установлено нулевое значение флага состояния FS1=0 счетчика СТК 9, так как на вход данных ID поступило только два бита после первого выявленного шаблона и в счетчике 9 разрядов шаблона установлено значение СТК=2. Поэтому формируется нулевое значение внутреннего флага неперекрывающихся шаблонов FN=0 на выходе второго элемента И 7 и запрещена запись в выходной буфер ОВ 11 и счет групп во втором счетчике 6 количества неперекрывающихся шаблонов CTN (сохраняется значение CTN=1).

В тактах 8, 9 и 10 следующие три бита входной последовательности поступают на вход данных ID=101, осуществляется сдвиг на три разряда в регистрах сдвига и в такте 11 устанавливается в регистре 15 данных код RD=101101, для которого на шине первого операнда сравнения устанавливается код ВА=0101 (передаются только три младших разряда), который совпадает с заданным шаблоном IS=0101. Поэтому в такте 11 формируются единичные значения внутреннего флага равенства FEQ=1 на выходе компаратора СОМР 20.

Кроме того, в такте 9 во втором вычитающем счетчике 9 разрядов шаблона устанавливается код СТК=1 и формируется единичное значение внутреннего флага первого состояния счетчика FS1=1, которое сохраняется на тактах 10 и 11. При этом осуществляется счет в четвертом 10 счетчике интервалов и в такте 11 устанавливается код CTI=2. Одновременно разрешается передача значений с третьего разряда (IK=3) регистра данных RD 15 через мультиплексор MUX 12 и формирование единичного флага бита интервала FM=1, значение которого на такте 11 записывается в третий триггер единичных бит интервала TRI 14 и формируется единичное значение флага единичного интервала FU=1.

Далее, в такте 11 при единичных значениях флага первого состояния FS1=1 третьего счетчика разрядов шаблона СТК 9 и флага равенства FEQ=1, формируется единичное значение внутренних флагов перекрывающихся шаблонов FS=1 на выходе первого элемента И 4 и неперекрывающихся шаблонов FN=1 на выходе второго элемента И 7, по которым в такте 12 разрешается счет (увеличение на единицу) в первом счетчике 5 количества перекрывающихся шаблонов CTS=3 и во втором счетчике 6 количества неперекрывающихся шаблонов CTN=2. Одновременно по единичному флагу FN=1 формируется единичное значение внутреннего флага загрузки счетчика FL=1 на выходе второго элемента ИЛИ 8, по которому в такте 12 в вычитающий третий счетчик 9 разрядов шаблона загружается код «IK» СТК=3.

Кроме того, в такте 12 по единичному флагу FN=1 разрешается работа выходного буфера ОВ 11, в который по первому адресу записывается код ОВ(1)=1_2 - единичное значение флага единичного интервала FU=1 и значение кода с выхода четвертого счетчика интервалов CTI=2, которые соответствуют двум битам интервала между первым и вторым выявленными неперекрывающимися шаблонами, при этом один из бит интервала единичный. Также по единичному флагу FN=1 в нулевое состояние устанавливается третий триггер единичных бит интервала TRI 14, так как на синхронном входе R установки в нулевое состояние установлено единичное значение, и флаг единичного интервала FU=0.

Аналогично осуществляется поиск групп на трех следующих тактах. В тактах 11, 12 и 13 следующие три бита входной последовательности поступают на вход данных ID=101, который также совпадает с заданным шаблоном IS=0101. Поэтому в такте 14 формируются единичные значения внутреннего флага равенства FEQ=1 на выходе компаратора СОМР 20. Кроме того, так как были приняты три бита входной последовательности, то формируется единичное значение флага первого состояния FS1=1 третьего счетчика 9 разрядов шаблона при СТК=1 и далее формируется единичное значение внутренних флагов перекрывающихся шаблонов FS=1 и неперекрывающихся шаблонов FN=1, по которым разрешается счет (увеличение на единицу) в первом счетчике 5 количества перекрывающихся шаблонов CTS=4 и во втором счетчике 6 количества неперекрывающихся шаблонов CTN=3.

Далее в такте 15 по единичному флагу FN=1 разрешается работа выходного буфера ОВ 11, в который по второму адресу записывается код ОВ(1)=0_0 - нулевое значение флага единичного интервала FU=0 и значение кода с выхода четвертого счетчика интервалов CTI=0, которые соответствуют нулевому интервалу между выявленными вторым и третьим непересекающимися шаблонами.

Одновременно в такте 14 поступает единичный сигнал STOP=1 по которому в нулевое состояние переключается RS-триггер 1 пуска-останова TSS=0.

Таким образом, для входного N=12 разрядного двоичного числа приведенного на фиг. 2 выявлено четыре группы соответствующие заданному трехразрядному 1IK3 шаблону IS=101 - три группы неперекрывающихся шаблонов CTN=3 и четыре группы перекрывающихся шаблонов CTS=4, значения которых передаются на группы внешних выходов количества неперекрывающихся шаблонов QN=3 и перекрывающихся шаблонов QS=4. Кроме того, определены интервалы между неперекрывающимися шаблонами и наличие единичных бит в данных диапазонах, которые записаны в выходной буфер ОВ 11 по трем адресам ОВ(0), ОВ(1), В(2).

Для последовательности входных данных ID приведенных на фиг. 3 осуществляется поиск групп для IK=(4) 100 разрядов заданного шаблона IS=0101. Одновременно для кода IK=100 на шине BDC будет установлено значение унитарного позиционного ряда BDC=1111, по которому на следующих тактах разрешается передача четырех младших разрядов на внутреннюю шину первого операнда сравнения ВА с выходов регистра RD 15 и на внутреннюю шину второго операнда сравнения ВВ с внешних входов заданного шаблона IS. При этом на шине второго операнда сравнения ВВ устанавливается код ВВ=0101. В такте 2 при единичном значении флага загрузки счетчика FL=1 значение кода IK=4 текущей разрядности заданного шаблона IS загружается в третий вычитающий счетчик 9 разрядов шаблона СТК=4.

Первое единичное значение внутреннего флага равенства FEQ=1 на выходе компаратора СОМР 20 формируется на такте 5, так как после передачи трех первых бит входной последовательности на шине первого операнда сравнения ВА с выходов регистра RD 15 установлен код ВА=0101 соответствующий четырем разрядам заданного шаблона IS=0101. Но при этом установлено нулевое значение флага первого состояния счетчика СТК FS1=0, так как на вход данных ID поступило только три бита и в третьем счетчике 9 разрядов шаблона установлено значение СТК=2, и также нулевое значение установлено во втором 2 триггере задержки TZ=0, поэтому установлено нулевое значение флага разрешения шаблонов FE=0. Поэтому далее установлены нулевые значения внутренних флагов перекрывающихся шаблонов FS=0 и неперекрывающихся шаблонов FN=0, по которым запрещена запись в выходной буфер ОВ 11 и счет групп в первом счетчике 5 количества шаблонов CTS=0 и втором счетчике 6 количества неперекрывающихся шаблонов CTN=0.

В тактах 5 и 6 на вход данных ID поступают значении четвертого (0) и пятого (1) бит ID=01, для которых, с учетом значений предыдущих второго (0) и третьего бит (1), на такте 7 формируется четырехразрядной код группы на шине первого операнда сравнения ВА=0101, с выходов четырех младших разрядов регистра 15 данных RD=010101, соответствующий заданному шаблону IS=0101. При этом формируется единичное значение внутреннего флага равенства FEQ=1. Кроме того, в такте 6 уже было установлено значение счетчика разрядов шаблона СТК=1 (принято четыре бита входных данных) и сформировано единичное значение флага первого состояния счетчика FS1=1, поэтому формируется единичное значение флага разрешения шаблонов FE=1 на выходе первого элемента ИЛИ 3. Также в такте 7 по единичному значению флага FS1=1 устанавливается в единичное состояние триггер 2 задержки TZ=1, по которому на следующих тактах устанавливается флаг FE=1 и разрешается формирование флагов перекрывающихся шаблонов FS. Кроме того, при FS1=1 в такте 7 осуществляется счет бит в четвертом 10 счетчике интервалов и устанавливается код CTI=1.

Одновременно в такте 7 формируются единичные значения внутренних флагов перекрывающихся шаблонов FS=1 и неперекрывающихся шаблонов FN=1 по которым разрешается счет в первом счетчике 5 количества перекрывающихся шаблонов CTS=1 и во втором счетчике 6 количества неперекрывающихся шаблонов CTN=1. Также одновременно по единичному флагу FN=1 формируется единичное значение внутреннего флага загрузки счетчика FL=1 на выходе второго элемента ИЛИ 8, по которому в такте 8 в вычитающий третий счетчик 9 разрядов шаблона загружается код «IK» СТК=4. Одновременно, так как установлено единичное значение флага первого состояния FS1=1, разрешается передача значений с третьего разряда (IK=3) регистра данных RD 15 через мультиплексор MUX 12 и формирование единичного флага бита интервала FM=1, значение которого на такте 7 записывается в третий триггер единичных бит интервала TRI 14 и формируется единичное значение флага единичного интервала FU=1.

В такте 8 осуществляется запись по нулевому адресу выходного буфера кода ОВ(0)=1_1 - значение флага единичного интервала FU=1 и значение кода с выхода четвертого счетчика интервалов CTI=1, которые соответствуют одному единичному биту до первого выявленного шаблона (первый бит во входной последовательности).

Следующая группа, соответствующая заданному шаблону IS=0101, выявлена для 4-7 разрядов входной последовательности, для которой формируются в такте 9 единичное значение флага равенства FEQ=1, но с учетом перекрытия 4 и 5 разрядов из выявленной первой группы, далее формируется только единичный флаг перекрывающихся шаблонов FS=1, по которому осуществляется счет перекрывающихся шаблонов CTS=2, и нулевой флаг неперекрывающихся шаблонов FN=0.

Следующая группа, соответствующая заданному шаблону IS=0101, выявлена для 9-12 разрядов входной последовательности, для которой формируются в такте 14 единичные значения флагов равенства FEQ=1 и далее флагов перекрывающихся шаблонов FS=1 и неперекрывающихся шаблонов FN=1, по которым разрешается счет в первом счетчике 5 количества перекрывающихся шаблонов CTS=3 и во втором счетчике 6 количества неперекрывающихся шаблонов CTN=2. Кроме того, на такте 14 формируется единичное значение флага единичного интервала FU=1 на выходе третьего триггера единичных бит интервала TRI 14. Кроме того, при FS1=1 в тактах 12-14 осуществляется счет бит в четвертом 10 счетчике интервалов и устанавливается код CTI=3.

В такте 15, по единичному флагу FN=1 осуществляется запись кода по первому адресу выходного буфера кода ОВ(1)=1_3 -значение флага единичного интервала FU=1 и значение кода с выхода четвертого счетчика интервалов CTI=3, которые соответствуют трем битам интервала между первым и вторым выявленными неперекрывающимися шаблонами, при этом один из бит единичный.

Считывание результатов на группу внешних выходов данных QB из выходного буфера ВО 11 выполняется под управлением по внешней шине управления ЕО. При реализации выходного буфера ВО 11 в виде двухпортовой памяти FIFO, обмен можно выполнять в процессе детектирования групп с учетом значений флагов «Буфер пуст» FZ и «Буфер заполнен» FF. Значение кода на группу внешних выходов количества перекрывающихся шаблонов QS передается с выходов первого счетчика количества шаблонов CTS 5 и на группу внешних выходов количества неперекрывающихся шаблонов QN с выхода второго счетчика количества шаблонов CTN 6.

Предлагаемое устройство может быть применено для аппаратной реализации статистических тестов разработанных лабораторией информационных технологий Национального института стандартов и технологий (NIST, США), целью которых является определение меры случайности двоичных последовательностей порожденных генераторами случайных чисел. В частности предлагаемое устройство реализует тесты на совпадение заданных шаблонов размерностью К бит с группами из входных данных также размерностью К бит, как перекрывающихся, так и неперекрывающихся групп и подсчитывает количество выявленных в исходной последовательности перекрывающихся и неперекрывающихся групп При этом независимо от совпадения или не совпадения шаблону анализируемые соседние группы из входных данных сдвигаются на один бит вперед. Цель - выявить генераторы случайных или псевдослучайных чисел, формирующие слишком часто заданные непериодические шаблоны. Кроме того, в устройстве определяется число бит (интервал) между соседними неперекрывающимися шаблонами и выявление единичных бит в интервале между шаблонами. Тест оценивает насколько «далеко» друг от друга отстоят шаблоны внутри последовательности (универсальный статистический тест Маурера). Цель теста - выяснить может ли данная последовательность быть значительно сжата без потерь информации. Чем более сжимаема последовательность, тем она менее случайна.

При обработке результатов физических экспериментов предлагаемое устройство обеспечивает выявление непериодических событий (шаблонов - заданной группы из последовательностей единичных бит (длительности событий) и нулевых бит (интервалов между ними)) и интервалов между событиями, а также наличие других единичных событий между детектируемыми шаблонами.

Вышеизложенные сведения позволяют сделать вывод, что предлагаемое устройство решает поставленную задачу и соответствует заявляемому техническому результату -реализация возможности задания значений шаблонов и их разрядности, разделение выявленных перекрывающихся и неперекрывающихся шаблонов, определение их количества, а также подсчет числа бит в интервалах между шаблонами и выявление единичных бит между шаблонами.

Изобретение относится к средствам детектирования шаблона бит. Технический результат - детектирование перекрывающихся и неперекрывающихся шаблонов заданной разрядности, определении их количества, а также подсчет числа бит в интервалах между шаблонами и выявление единичных бит между шаблонами. Указанный технический результат при осуществлении изобретения достигается тем, что устройство содержит первый RS-триггер, второй триггер задержки, первый элемент ИЛИ, первый элемент И, первый счетчик количества перекрывающихся шаблонов CTS второй счетчик количества неперекрывающихся шаблонов CTN, второй элемент И, второй элемент ИЛИ, третий вычитающий счетчик разрядов шаблона СТК, четвертый счетчик интервалов CTI, выходной буфер ОВ, мультиплексор MUX, третий элемент, третий триггер единичных бит интервала TRI, регистр сдвига входных данных RD, первую и вторую И группы элементов И, дешифратор DC, группу элементов ИЛИ, компаратор СОМР. 3 ил.

Устройство для детектирования шаблонов бит и определение числа бит между шаблонами содержит внешний вход данных ID, группу внешних входов шаблона IS, содержащую К разрядов, группу внешних входов IК задания разрядности входного шаблона IS, содержащую m разрядов (где m=]log2(К+1)[большее целое), группу внешних выходов данных QB, группу внешних выходов количества перекрывающихся шаблонов QS, группу внешних выходов количества неперекрывающихся шаблонов QN,

а также содержит первый RS-триггер пуска-останова TSS 1, второй триггер задержки TZ 2, первый элемент ИЛИ 3, первый элемент И 4, первый счетчик количества перекрывающихся шаблонов CTS 5, второй счетчик количества неперекрывающихся шаблонов CTN 6, второй элемент И 7, второй элемент ИЛИ 8, третий вычитающий счетчик разрядов шаблона СТК 9, четвертый счетчик интервалов CTI 10, выходной буфер ОВ 11, мультиплексор MUX 12, третий элемент ИЛИ 13, третий триггер единичных бит интервала TRI 14, регистр сдвига входных данных RD 15, первую группу из К элементов И 161, 162, …, 16К, вторую группу из К элементов И 171, 172, …, 17К, дешифратор DC 18, группу из (К-1) элементов ИЛИ 191, 192, …, 19(К-1), компаратор СОМР 20,

а также введены внешние входы тактового сигнала IC, пуска устройства START, остановки устройства STOP и внутренние шина дешифрации разрядов BDC, шина первого операнда сравнения ВА и шина второго операнда сравнения ВВ, внутренние флаг разрешения шаблонов FE, флаг равенства FEQ, флаг FL загрузки счетчика СТК, флаг бита интервала FM, флаг неперекрывающихся шаблонов FN, флаг перекрывающихся шаблонов FS, флаг FS1 первого состояния счетчика СТК и флаг единичного интервала FU, внешняя шина управления обменом ЕО, внешние флаг «Буфер заполнен» FF и флаг «Буфер пуст» FZ,

причем внешний тактовый вход устройства IC соединен с входами синхронизации С первого RS-триггера пуска-останова TSS 1, второго триггера задержки TZ 2, первого счетчика количества перекрывающихся шаблонов CTS 5, второго счетчика количества неперекрывающихся шаблонов CTN 6, третьего вычитающего счетчика разрядов шаблона СТК 9, четвертого счетчика интервалов CTI 10, выходного буфера ОВ 11, третьего триггера единичных бит интервала TRI 14 и регистра сдвига входных данных RD 15,

внешний вход пуска устройства START соединен с входом S синхронной установки в единичное состояние первого RS-триггера пуска-останова TSS 1 и вторым входом второго элемента ИЛИ 8,

внешний вход остановки устройства STOP соединен с входом R синхронной установки в нулевое состояние первого RS-триггера пуска-останова TSS 1,

причем прямой выход первого RS-триггера пуска-останова TSS 1 соединен со вторыми входами первого 4 и второго 7 элементов И, с входом СЕ разрешения работы регистра сдвига входных данных RD 15, а выход второго триггера задержки TZ 2 соединен со вторым входом первого элемента ИЛИ 3,

внешний вход данных ID соединен с входом SI последовательного ввода регистра сдвига входных данных RD 15, группа К выходов которого соединена с одноименными информационными входами мультиплексора 12 и соединена с первыми входами соответствующих одноименных элементов первой группы из К элементов И 161, 162, …, 16К, выходы которых являются соответствующими одноименными разрядами внутренней шины первого операнда сравнения ВА, которая соединена с первой группой входов компаратора СОМР 20,

К разрядов группы внешних входов шаблона IS соединены с первыми входами соответствующих одноименных элементов второй группы из К элементов И 171, 172, …, 17К, выходы которых являются соответствующими одноименными разрядами внутренней шины второго операнда сравнения ВВ, которая соединена со второй группой входов компаратора СОМР 20, выход которого является внутренним флагом равенства FEQ и соединен со третьими входами первого 4 и второго 7 элементов И,

причем группа внешних входов IK задания разрядности входного шаблона IS соединена с соответствующей группой D-входов третьего счетчика разрядов шаблона СТК 9, с адресными входами мультиплексора 12 и с адресными входами дешифратора DC 18, у которого выходы, с первого выхода до (К-1)-го выхода, соединены с первыми входами соответствующих одноименных элементов И группы из (К-1) элементов 191, 192, …, 19(К-1), выходы которых являются соответствующими одноименными разрядами, с первого разряда до (К-1)-го разряда, внутренней шины дешифрации разрядов BDC, у которой К-й разряд соединен с К-м выходом дешифратора DC 18, а К разрядов внутренней шины дешифрации разрядов BDC соединены со вторыми входами соответствующих одноименных элементов первой группы из К элементов И 161, 162, …, 16К и второй группы из К элементов И 171, 172, …, 17К,

кроме того, выходы элементов группы 192, 193, …, 19(К-1) из (К-1) элементов ИЛИ, начиная с выхода (К-1)-го элемента 19(К-1) до второго элемента 192, соединены со вторыми входами соответствующих предыдущих элементов ИЛИ группы 191, 192, …, 19(К-2), начиная с (К-2)-го элемента 19(К-2) до первого элемента 191, а второй вход (К-1)-го элемента 19(К-1) соединен с К-м выходом дешифратора DC 18,

причем выход мультиплексора 12 является внутренним флагом бита интервала FM и соединен с первым входом третьего элемента ИЛИ 13, выход которого соединен с информационным D-входом третьего триггера единичных бит интервала TRI 14, выход которого является внутренним флагом единичного интервала FTJ и соединен со вторым входом третьего элемента ИЛИ 13 и со вторым D-входом выходного буфера ОВ 11,

кроме того, выход первого состояния третьего вычитающего счетчика разрядов шаблона СТК 9 является внутренним флагом FS1 первого состояния и соединен с инверсным входом разрешения работы СЕ счетчика разрядов шаблона СТК 9, с входом S синхронной установки в единичное состояние второго триггера задержки TZ 2, с первым входом первого элемента ИЛИ 3, с первым входом второго элемента И 7, с входом разрешения Е мультиплексора 12 и с входом СЕ разрешения работы четвертого счетчика интервалов CTI 10, выходы которого соединены с первой группой D-входов выходного буфера ОВ 11, который также подключен к внешней шине ЕО управления обменом, а соответствующие выходы выходного буфера ОВ 4 являются группой внешних выходов данных ОВ и внешними флагами «Буфер заполнен» FF и «Буфер пуст» FZ,

причем выход первого элемента ИЛИ 3 является внутренним флагом разрешения шаблонов FE и соединен с первым входом первого элемента И 4, выход которого является внутренним флагом перекрывающихся шаблонов FS и соединен с входом разрешения работы СЕ первого счетчика количества перекрывающихся шаблонов CTS 5, выходы которого являются группой внешних выходов количества перекрывающихся шаблонов QS,

кроме того, выход второго элемента ИЛИ 8 является внутренним флагом FL загрузки счетчика СТК 9 и соединен с входом разрешения загрузки L третьего вычитающего счетчика разрядов шаблона СТК 9, а выход второго элемента И 7 является внутренним флагом FN неперекрывающихся шаблонов и соединен с первым входом второго элемента ИЛИ 8, входами R синхронной установки в нулевое состояние четвертого счетчика интервалов CTI 10 и третьего триггера единичных бит интервала TRI 14, а также соединен с входами разрешения работы СЕ выходного буфера ОВ 11 и второго счетчика количества неперекрывающихся шаблонов CTN 6, выходы которого являются группой внешних выходов количества неперекрывающихся шаблонов QN.

| УСТРОЙСТВО ДЛЯ ДЕТЕКТИРОВАНИЯ ПЕРЕКРЫВАЮЩИХСЯ И НЕПЕРЕКРЫВАЮЩИХСЯ ШАБЛОНОВ БИТ В ДВОИЧНОЙ ПОСЛЕДОВАТЕЛЬНОСТИ | 2023 |

|

RU2807299C1 |

| УСТРОЙСТВО ДЛЯ ДЕТЕКТИРОВАНИЯ ПЕРЕКРЫВАЮЩИХСЯ ШАБЛОНОВ БИТ В ДВОИЧНОЙ ПОСЛЕДОВАТЕЛЬНОСТИ | 2022 |

|

RU2787294C1 |

| УСТРОЙСТВО ДЛЯ ДЕТЕКТИРОВАНИЯ ПЕРЕКРЫВАЮЩИХСЯ ШАБЛОНОВ БИТ В ДВОИЧНОЙ ПОСЛЕДОВАТЕЛЬНОСТИ | 2022 |

|

RU2787294C1 |

| US 9582664 B2, 28.02.2017 | |||

| US 7295674 B2, 13.11.2007. | |||

Авторы

Даты

2025-02-03—Публикация

2024-05-08—Подача