ОБЛАСТЬ ТЕХНИКИ

Изобретение относится к области вычислительной техники, в частности к устройствам обработки данных, и может быть использовано для построения функциональных узлов для анализа свойств генераторов псевдослучайных последовательностей двоичных чисел, фильтрации событий, обработки сигналов и результатов физических экспериментов.

Известно устройство сортировки информации методом преобразования данных в адрес (RU №2382396 С2, МПК G06F 7/08, G06F 17/30, заявлено 31.03.2008, опубликовано 20.02.2010, Бюл. №5) содержащее блок ввода данных, блок сортировки положительных чисел, блок хранения результатов, блок сортировки отрицательных чисел, блок управления, оперативные запоминающие устройства, двоичные счетчики, пороговые элементы.

В данном устройстве решается задача сортировки входной числовой и символьной информации по возрастанию и убыванию. Сортировка осуществляется как положительных, так и отрицательных чисел, и символов. Выполняется подсчет количества одинаковых чисел и символов. Недостатком данного устройства являются большие аппаратные затраты и осуществление поисковых операций по указанному интервалу или по конкретному заданному символу или числу.

Известно устройство для детектирования групп единичных бит в блоках двоичной последовательности (RU №2809743 С1, МПК G06F 7/74, заявлено 07.08.2023, опубликовано 15.12.2023, Бюл. №35) содержащее внешний вход данных ID последовательного ввода К-разрядных блоков данных ВВ из входной N-разрядной бинарной последовательности данных, группу внешних выходов групп QB, группу внешних выходов максимальных групп QH, группу внешних шин количества единичных групп Q1, Q2, …, Q(M+1) (где М - разрядности детектируемых единичных групп, 1≤М≤К), счетчик тактов СТС 1, счетчик единичных бит СТВ 2, дешифратор 3, инвертор 4, выходной буфер групп ОВ 5, группу из (М+1) счетчиков единичных групп 61, 62, …, 6(M+1), группу из (М+1) сумматоров 71, 72, …, 7(M+1), группу из (М+1) регистров 81, 82, …, 8(M+1), первый элемент ИЛИ 9, группу из (К-1) элементов ИЛИ 101, 102, …, 10(К-1), группу из (К-1) элементов И с инверсным входом 111, 112, …, H(К-1), второй элемент ИЛИ 12, регистр максимальной группы RH 13, регистр приоритета RPR 14 и выходной буфер максимальных групп ОН 15, а также введены внешние входы тактовый IC, синхронной установки в нулевое состояние IR и разрешения работы ICE, внутренние шины количества единичных бит в группе BD, унитарного кода BDC, старшей группы BS и приоритета BPR, внутренние флаги начала блока F0, разрешения счета FE и максимума FH, внешние шины управления обменом ЕО, внешние флаги «Буфер заполнен» FF и «Буфер пуст» FZ.

Данное устройство выявляет группы единичных бит заданной разрядности и максимальные группы в двоичных блоках, а также осуществляет подсчет единичных групп во входной последовательности. Недостатком данного устройства является побитовое поступление входных данных и детектирование только единичных групп.

Наиболее близким устройством того же назначения к заявленному изобретению по совокупности признаков является, принятое за прототип, устройство групповой структуры для детектирования шаблонов бит переменной разрядности (RU №2809741 С1, МПК G06F 7/74, заявлено 15.06.2023, опубликовано 15.12.2023, Бюл. №35) содержащее внешние m разрядный вход данных ID, (m+1) разрядный вход заданного шаблона IG, v разрядный вход разрядности шаблона IK, где v=]log2(m+1)[(большее целое), группы внешних выходов данных QB, количества перекрывающихся шаблонов QS, количества неперекрывающихся шаблонов QN, первый RS-триггер пуска-останова TSS 1, второй D-триггер TR2 задержки 2, счетчик CTG групп 3, выходной буфер ОВ 4, дешифратор 5, группу из m элементов ИЛИ 61, 62, …, 6m, первую группу из (m+1) элементов И 71, 72, …, 7m+1, элемент И 8, первый элемент ИЛИ 9, второй элемент ИЛИ 10, первый блок счета единиц 11, первый сумматор 12, регистр неперекрывающихся шаблонов RN 13, первый R1 регистр данных 14, второй R2 регистр данных 15, группу из m блоков разрешения 161, …, 162, 16m, каждый из которых содержит по (m+1) элементов И, группу из m компараторов 171, …, 172, 17m, группу из т блоков запрета 181, …, 182, 18m, каждый из которых содержит по m элементов И-НЕ, вторую группу из 2m элементов И 191, …, 192, 192m, регистр маски RM 20, второй блок счета единиц 21, второй сумматор 22, регистр перекрывающихся шаблонов RS 23, а также введены внешние входы асинхронной установки в нулевое состояние CLR, пуска устройства START, остановки устройства STOP и тактовый вход С, внутренние шины данных BD, запрета ВВ, дешифрации разрядов BDC, совпадения BE, шаблона BG, маски ВМ, неперекрывающихся шаблонов BN и группа из М шин данных D1, DM, внутренние флаги шаблонов FS, неперекрывающихся шаблонов FN, записи FW, внешняя шина управления обменом ЕО, внешние флаги «Буфер заполнен» FF и «Буфер пуст» FZ.

Данное устройство позволяет детектировать в соседних m-разрядных группах входного N-разрядного двоичного числа группы, соответствующие заданному шаблону групп IG, который содержит заданную последовательность единичных и нулевых бит, и осуществляет подсчет выявленных групп. Недостатком данного устройства является выявление групп, соответствующих только одному заданному шаблону.

ЗАДАЧА ИЗОБРЕТЕНИЯ

Задачей изобретения является разработка аппаратных средств для исследования свойств генераторов псевдослучайных последовательностей двоичных чисел, а также для фильтрации событий, обработки сигналов и результатов физических экспериментов.

При анализе генераторов псевдослучайных последовательностей двоичных чисел устройство предназначено для реализации теста на произвольные отклонения, в котором определяются циклы кумулятивных сумм, и осуществляется подсчет отклонений кумулятивных сумм в состояниях циклов.

В задачах обработки событий и результатов физических экспериментов осуществляется выявление одинаковых событий и подсчет их количества.

Техническим результатом изобретения является обеспечение возможности детектирования одинаковых групп числовой и символьной информации и подсчет количества таких групп в блоках входных данных входной двоичной последовательности.

КРАТКОЕ ОПИСАНИЕ СУЩНОСТИ ИЗОБРЕТЕНИЯ

Указанный технический результат при осуществлении изобретения достигается тем, что устройство для подсчета одинаковых групп бит в блоках двоичной последовательности содержит внешние группу входных данных IBD, вход конца блока IEB и вход выдачи количества одинаковых групп IES, группы внешних выходов количества одинаковых групп в блоках QB и количества одинаковых групп в последовательности QS, RS-триггер пуска-останова TSS 1, элемент И с инверсным входом 2, регистр входных данных RD 3, дешифратор групп DCG 4, группу элементов И 50, …, 5к, группу триггеров 60, …, 6к, группу счетчиков 70, …, 7к, группу дешифраторов 80, …, 8к, матрицу счетчиков 9[0:М, 0:К], содержащую (М+1) строк и (К+1) столбцов (где К - количество различных групп в блоках данных, М - максимальное количество одинаковых групп в блоке данных) и выходной буфер ОВ 10,

а также введены внешние входы тактового сигнала 1С, пуска устройства START и остановки устройства STOP, внутренний флаг разрешения работы FE, внешняя шина управления обменом ЕО, внешние флаги FF «Буфер заполнен», FZ «Буфер пуст»,

причем внешний тактовый вход устройства 1С соединен с входами синхронизации С RS-триггера пуска-останова TSS 1, регистра входных данных RD 3, триггеров группы 60, …, 6к, счетчиков группы 70, …, 7к, счетчиков матрицы 9[0:М, 0:К] и выходного буфера ОВ 10,

внешний вход пуска устройства START соединен с входом S синхронной установки в единичное состояние RS-триггера пуска-останова TSS 1,

внешний вход остановки устройства STOP соединен с входом R синхронной установки в нулевое состояние RS-триггера пуска-останова TSS 1, а также соединен со вторым инверсивным входом элемента И 2,

причем прямой выход RS-триггера пуска-останова TSS 1 соединен с первым прямым входом элемента И 2 с инверсивным входом, выход которого является внутренним флагом разрешения работы FE и соединен с входом разрешения работы Е дешифратора групп DCG 4,

группа входных данных IBD соединена с группой D-входов регистра входных данных RD 3, выходы которого соединены с адресными входами дешифратора групп DCG 4, у которого (К+1) выходов соединены с Т-входами одноименных триггеров группы 60, …, 6к, с входами разрешения работы СЕ одноименных счетчиков группы 70, …, 7к и со вторыми входами одноименных элементов И группы 50, …, 5к, выходы которых соединены с D-входами одноименных триггеров группы 60, …, 6к, выходы которых соединены с Т-входами одноименных счетчиков группы 70, …, 7к, с соответствующими D-входами выходного буфера ОВ 10 и с младшими адресными входами одноименных дешифраторов группы 80, …, 8к, у которых старшие разряды адресов соединены с выходами одноименных счетчиков группы 70, …, 7к, выходы которых также соединены с соответствующими группами D-входов выходного буфера ОВ 10, который также подключен к внешней шине ЕО управления обменом, а соответствующие выходы выходного буфера ОВ 10 являются группой внешних выходов количества одинаковых групп в блоках QB и соответствующими внешними флагами «Буфер заполнен» FF и «Буфер пуст» FZ,

кроме того внешний вход конца блока IEB соединен с первыми входами элементов И группы 50, …, 5к, с входами разрешения записи L триггеров группы 60, …, 6к, с входами R синхронной установки в нулевое состояние счетчиков группы 70, …, 7к, с входом разрешения работы СЕ выходного буфера ОВ 10 и с входами разрешения работы Е дешифраторов группы 80, …, 8к, у каждого из которых (М+1) выходов, начиная с нулевого выхода до М-го выхода, соединены с входами СЕ разрешения работы счетчиков соответствующих строк, начиная с нулевой строки до М-ой строки, одноименных столбцов матрицы счетчиков 9[0:М, 0:К], у которых входы L разрешения записи счетчиков соединены с внешним входом выдачи количества одинаковых групп IES,

причем в К-ой строке матрицы счетчиков матрицы 9[0:М, 0:К] на группы D-входов счетчиков заданы нулевые коды «О», а группы D-входов счетчиков матрицы 9[0:М, 0:К], начиная с (К-1)-ой строки до нулевой строки, подключены к выходам счетчиков следующих строк матрицы, начиная с К-ой строки до первой строки, а выходы счетчиков нулевой строки матрицы являются соответствующими группами внешних выходов количества одинаковых групп в последовательности QS.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

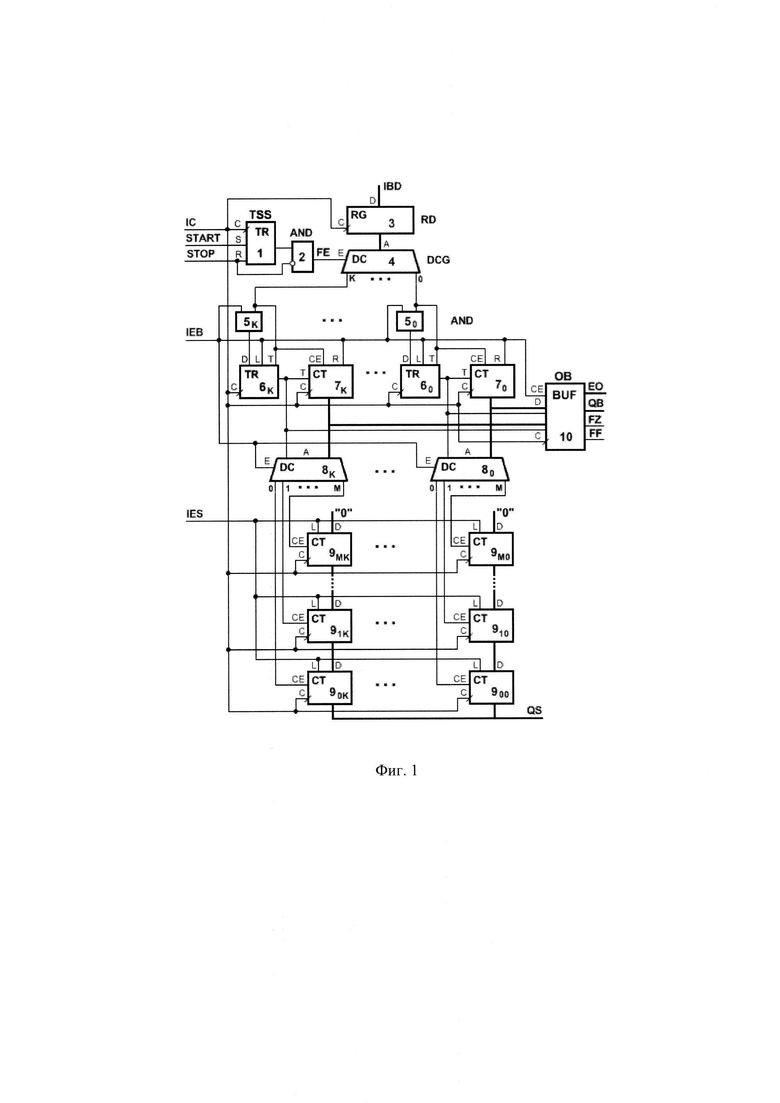

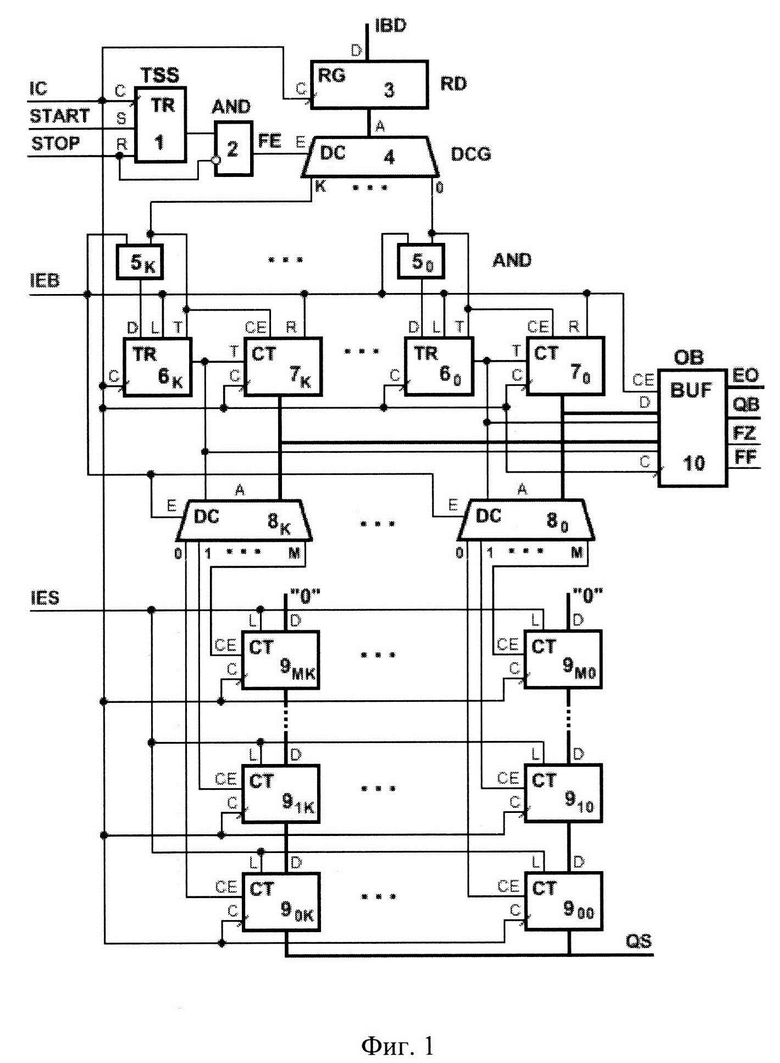

На фиг.1 приведена схема предлагаемого устройства.

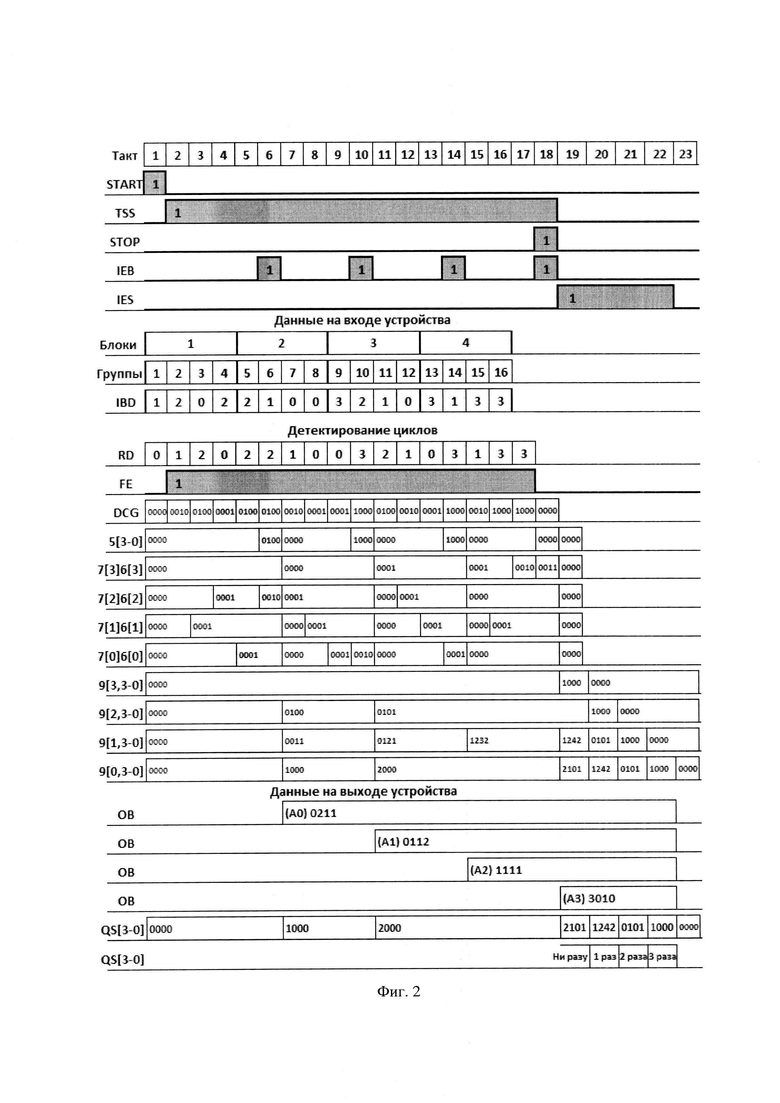

На фиг.2 приведена временная диаграмма работы устройства.

На фиг.1 - 2 и в тексте приняты следующие обозначения:

А - адресные входы,

AND - элемент И,

BUF - буфер с дисциплиной обслуживания FIFO,

С - тактовый вход,

СЕ - вход разрешения работы,

СТ - счетчик,

D - информационные входы,

DC - дешифратор,

DCG - дешифратор групп,

ЕО - внешняя шина управления обменом,

Е - вход разрешения работы дешифраторов,

FE - внутренний флаг разрешения работы,

FF -внешний флаг «Буфер заполнен»,

FZ -внешний флаг «Буфер пуст»,

IBD - внешняя группа входных данных,

1С - внешний тактовый вход,

IEB - внешний вход конца блока,

IES - внешний вход выдачи количества одинаковых групп,

k - разрядность входных данных,

К - количество различных групп в блоках данных, где К=2k-1,

L - вход разрешения записи,

М - максимальное количество одинаковых групп в блоке,

ОВ -выходной буфер,

QB - группа внешних выходов количества одинаковых групп в блоках,

QS - группы внешних выходов количества одинаковых групп в последовательности,

RG - регистр,

RD - регистр входных данных,

R - вход синхронной установки в нулевое состояние,

S - вход синхронной установки в единичное состояние,

START - внешний вход пуска,

STOP - внешний вход останова,

TR - триггер,

Т - счетный вход,

TSS - триггер пуска-останова,

W - количество блоков в двоичной последовательности,,

1 - RS-триггер пуска-останова TSS,

2 - элемент И с инверсным входом (AND),

3 - регистр входных данных RD,

4 - дешифратор групп DCG,

50, …, 5к - группа элементов И (AND),

60, …, 6к - группа триггеров (TR),

70, …, 7к - группа счетчиков (СТ),

80, …, 8к - группа дешифраторов (DC),

9[0:М, 0:К] - матрица счетчиков, содержащая (М+1) строк и (К+1) столбцов,

10 - выходной буфер ОВ.

Предлагаемое устройство содержит внешние группу входных данных IBD, вход конца блока IEB и вход выдачи количества одинаковых групп IES, группы внешних выходов количества одинаковых групп в блоках QB и количества одинаковых групп в последовательности QS, RS-триггер пуска-останова TSS 1, элемент И с инверсным входом 2, регистр входных данных RD 3, дешифратор групп DCG 4, группу элементов И 50, …, 5к, группу триггеров 60, …, 6к, группу счетчиков 70, …, 7к, группу дешифраторов 80, …, 8к, матрицу счетчиков 9[0:М, 0:К], содержащую (М+1) строк и (К+1) столбцов (где К - количество различных групп в блоках данных, М - максимальное количество одинаковых групп в блоке данных) и выходной буфер ОВ 10.

В предлагаемое устройство также введены внешние входы тактового сигнала IC, пуска устройства START и остановки устройства STOP, внутренний флаг разрешения работы FE, внешняя шина управления обменом ЕО, внешние флаги FF «Буфер заполнен», FZ «Буфер пуст».

Регистр входных данных RD 3 предназначен для приема и хранения текущих входных групп с внешний группы входных данных IBD. Дешифратор групп DCG 4 преобразует двоичный код входной группы в унитарный код «1 из К». Пары одноименных триггера из группы 60, …, 6к и счетчика из группы 70, …, 7к образуют счетчики и предназначены для подсчета одинаковых групп во входных группах. Дешифраторы из группы 80, …, 8к осуществляют преобразование двоичных кодов количества одинаковых групп в унитарные коды «1 из М». Счетчики из матрицы 9[0:М, 0:К] предназначены для подсчета количества блоков в которых одноименные входные группы 0, К встречаются от 0 до М раз.

Внешний тактовый вход устройства 1С соединен с входами синхронизации С RS-триггера пуска-останова TSS 1, регистра входных данных RD 3, триггеров группы 60, …, 6к, счетчиков группы 70, …, 7к, счетчиков матрицы 9[0:М, 0:К] и выходного буфера ОВ 10.

Внешний вход пуска устройства START соединен с входом S синхронной установки в единичное состояние RS-триггера пуска-останова TSS 1.

Внешний вход остановки устройства STOP соединен с входом R синхронной установки в нулевое состояние RS-триггера пуска-останова TSS 1, а также соединен со вторым инверсивным входом элемента И 2.

Триггер пуска-останова TSS 1 предназначен для выделения цикла работы предлагаемого устройства, между сигналами START и STOP. Причем прямой выход RS-триггера пуска-останова TSS 1 соединен с первым прямым входом элемента И 2 с инверсивным входом, выход которого является внутренним флагом разрешения работы FE и соединен с входом разрешения работы Е дешифратора групп DCG 4.

Группа входных данных IBD соединена с группой D-входов регистра входных данных RD 3, выходы которого соединены с адресными входами дешифратора групп DCG 4, у которого (К+1) выходов соединены с Т-входами одноименных триггеров группы 60, …, 6к, с входами разрешения работы СЕ одноименных счетчиков группы 70, …, 7к и со вторыми входами одноименных элементов И группы 50, …, 5к, выходы которых соединены с D-входами одноименных триггеров группы 60, …, 6к, выходы которых соединены с Т-входами одноименных счетчиков группы 70, …, 7к, с соответствующими D-входами выходного буфера ОВ 10 и с младшими адресными входами одноименных дешифраторов группы 80, …, 8к, у которых старшие разряды адресов соединены с выходами одноименных счетчиков группы 70, …, 7к.

Выходы счетчиков группы 70, …, 7к также соединены с соответствующими группами D-входов выходного буфера ОВ 10, который также подключен к внешней шине ЕО управления обменом, а соответствующие выходы выходного буфера ОВ 10 являются группой внешних выходов количества одинаковых групп в блоках QB и соответствующими внешними флагами «Буфер заполнен» FF и «Буфер пуст» FZ.

Кроме того внешний вход конца блока IEB соединен с первыми входами элементов И группы 50, …, 5к, с входами разрешения записи L триггеров группы 6о,..., 6к, с входами R синхронной установки в нулевое состояние счетчиков группы 70, …, 7к, с входом разрешения работы СЕ выходного буфера ОВ 10 и с входами разрешения работы Е дешифраторов группы 80, …, 8к, у каждого из которых (М+1) выходов, начиная с нулевого выхода до М-го выхода, соединены с входами СЕ разрешения работы счетчиков соответствующих строк, начиная с нулевой строки до М-ой строки, одноименных столбцов матрицы счетчиков 9[0:М, 0:К], у которых входы L разрешения записи счетчиков соединены с внешним входом выдачи количества одинаковых групп IES.

Причем в К-ой строке матрицы счетчиков матрицы 9[0:М, 0:К] на группы D-входов счетчиков заданы нулевые коды «0», а группы D-входов счетчиков матрицы 9[0:М, 0:К], начиная с (К-1)-ой строки до нулевой строки, подключены к выходам счетчиков следующих строк матрицы, начиная с К-ой строки до первой строки. Выходы счетчиков нулевой строки матрицы являются соответствующими группами внешних выходов количества одинаковых групп в последовательности QS.

ПОДРОБНОЕ ОПИСАНИЕ СУЩНОСТИ ИЗОБРЕТЕНИЯ

Принцип работы предлагаемого устройства состоит в следующем.

Входная двоичная последовательность разбивается на W блоков данных, которые содержат k-разрядные группы, состоящие из нулевых и единичных бит, соответствующие числовой и символьной информации.. Предлагаемое устройство осуществляет детектирование и подсчет одинаковых k-разрядных групп в каждом из W блоков входных данных и общее количество во всех W блоках входной двоичной последовательности.

Входные k-разрядные группы данных в каждом такте 1С поступают на внешнюю группу входных данных IBD, записываются в регистр входных данных RD 3 и далее на дешифраторе групп DCG 4 преобразуются в унитарный код «1 из К» (где К - количество различных групп в блоках данных, К=2k-1). При единичном значении флага разрешения работы FE=1, формируется единичное значение на одном из выходов дешифратора групп DCG 4 и далее разрешается счет на соответствующем одноименном триггере из группы 60, …, 6к, а также при единичном значении триггера разрешается счет в соответствующем одноименном счетчике из группы 70, …, 7к. При этом на парах одноименных триггера из группы 60, …, 6к и счетчика из группы 70, …, 7к осуществляется счет одинаковых групп бит для каждого входного блока (значения с триггеров являются младшими разрядами), а далее значения с триггеров и счетчиков поступают на адресные входы соответствующих одноименных дешифраторов DC из группы 80, …, 8к.

При единичном значении на внешнем входе конца блока IEB=1 осуществляется запись в выходной буфер ОВ 10 значений сумм по одинаковым группам бит с выходов триггеров из группы 60, …, 6к и счетчиков из группы 70, …, 7к.

Единичное значение с внешнего входа конца блока IEB=1 также поступает на входы Е разрешения работы дешифраторов DC из группы 80, …, 8к, на которых формируются унитарные коды «1 из М», где М - максимальное количество одинаковых групп в блоке. При этом единичные значения устанавливаются на одном из выходов дешифраторов DC из группы 80, …, 8к, по которым осуществляется счет в соответствующих счетчиках одноименных строк из матрицы 9[0:М, 0:К], на которых осуществляется подсчет количества блоков в которых одноименные входные группы 0, К встречаются от 0 до М раз. Например, в первой строке счетчиков матрицы 9[1, 0:К] осуществляется счет блоков, в которых одноименные группы встречаются один раз, а в нулевых строках матрицы 9[0, 0:К] - в которых одноименные группы не встречаются ни разу.

Кроме того, единичное значение с внешнего входа конца блока IEB=1 также поступает на первые входы элементов И из группы 50, …, 5к, на входы L разрешения записи триггеров из группы 60, …, 6к и на входы R синхронной установки в нулевое состояние счетчиков из группы 70, …, 7к. При этом счетчики 70, …, 7к устанавливаются в нулевое состояние. Одновременно на выходе только одного элемента И из группы 50, …, 5к будет установлено единичное значение соответствующее первой входной группе следующего входного блока с входного регистра данных RD 3, по которому в единичное состояние устанавливается соответствующий одноименный триггер из группы 6о,..., 6к, так как вход L имеет высший приоритет, а другие триггеры устанавливаются в нулевое состояние.

Кроме того, после сигнала остановки STOP=l, после передачи W блоков входной двоичной последовательности, при единичном значении на внешнем входе выдачи количества одинаковых групп IES=1, на группу внешних выходов OS выдаются в течение М тактов количества одинаковых групп в последовательности в зависимости от количества раз выявленных в последовательности, начиная с отсутствия в последовательности (0 раз или ни разу) до М раз.

Предлагаемое устройство работает следующим образом.

На фиг.2 приведена временная диаграмма работы предлагаемого устройства для детектирования W=4 блоков, содержащих по четыре k=2 разрядные группы входных данных и максимальном количестве одинаковых групп в блоке М=3.

Перед началом работы в начальное нулевое состояние устанавливаются - триггер пуска-останова TSS 1, регистр входных данных RD 3, группа триггеров 60, …, 6к, группа счетчиков 70, …, 7к и счетчики в матрице 9[0:М, 1:К], а также устанавливается начальный нулевой адрес в выходном буфере ОВ 10.

Работа устройства для каждой входной последовательности начинается после подачи единичного сигнала START=1. При этом по фронту тактового сигнала IC (такт 2 на фиг.2) в единичное состояние устанавливается RS-триггер 1 пуска-останова TSS=1, по которому формируется единичное значение флага разрешения работы FE=1 на выходе элемента И с инверсным входом 2, и далее на следующих тактах 1С разрешается работа дешифратора групп DCG 4.

Одновременно с сигналом START=1 в такте 1 на внешнюю группу входных данных IBD поступает первая входная группа IBD=1, которая в такте 2 принимается в регистр входных данных RD 3. Далее унитарный код «1 из К» устанавливается на дешифраторе групп DCG 4 и соответствующее единичное значение устанавливается на первом выходе DCG=0010. Поэтому в такте 3 осуществляется счет в первом триггере 6[1] из группы 60, …, 6к и устанавливается единичное значение 6[1]=1.

Кроме того в такте 2 на внешнюю группу входных данных IBD поступает вторая входная группа IBD=2 и в такте 3 последовательно поступает третья входная группа IBD=0 первого блока входных данных, которые последовательно принимаются в регистр входных данных RD 3. Далее последовательно формируются соответствующие унитарные коды «1 из К» на дешифраторе групп DCG 4 - соответственно DCG=0100 (такт 3) и DCG=0001 (такт 4), по которым осуществляется счет соответственно во втором триггере 6[2]=1 (такт 4) и нулевом триггере 6[0]=1 (такт 5) из группы триггеров 60, …, 6к.

В такте 4 также поступает четвертая входная группа IBD=2 первого блока входных данных, для которой устанавливается унитарный код на дешифраторе групп DCG=0100 (такт 5) и осуществляется счет во втором счетчике 7[2]=1 (такт 6), так как в такте 4 было установлено единичное значение во втором триггере 6[2]=1, а также одновременно счет во втором триггере - установка в нулевое состояние 6[2]=0 (такт 6).

В такте 6 поступает единичный сигнал конца блока 1ЕВ=1, по которому разрешается работа выходного буфера ОВ 10, в который в такте 7, для первого входного блока IBD=1202, с выходов триггеров группы 60, …, 6к и счетчиков группы 70, …, 7к по нулевому адресу записывается код ОВ (А0)=0211 - отсутствие групп соответствующих коду 3, две группы соответствующие коду 2, одна группа соответствующая коду 1 и одна группа соответствующая коду 0.

Одновременно в такте 6 по единичному сигналу конца блока IEB=1 разрешается работа группы дешифраторов DC 80, …, 8к, на соответствующих выходах которых формируются единичные значения, по которым в такте 7 осуществляется счет в матрице счетчиков 9[0:М, 0:К]: в нулевой строке только в третьем столбце - отсутствие групп с кодом 3 в первом блоке входных данных и устанавливается код 9[0, 3-0]=1000; в первой строке в первом и нулевом столбцах - по одному разу встречаются группы с кодами 1 и 0 и устанавливается код 9[1, 3-0]=0011; во второй строке только во втором столбце - два раза встречаются группы с кодом 2 и устанавливается код 9[2, 3-0]=0100; в третьей строке отсутствует счет так как нет кодов групп которые встречаются три раза.

Кроме того, в такте 5 на внешнюю группу входных данных IBD поступает пятая входная группа IBD=2 (первая группа для второго входного блока), которая в такте 6 принимается в регистр входных данных RD 3 и на дешифраторе групп DCG 4 соответствующее единичное значение устанавливается на втором выходе DCG=0100. Далее при единичном значении с внешнего входа конца блока IEB=1 единичное значение устанавливается только на выходе второго элемента И 52=1 и так как одновременно установлено единичное значение на входах L разрешения записи триггеров из группы 60, …, 6к, то второй триггер устанавливается в единичное состояние 62=1, а другие триггера в группе триггеров 60, …, 6к устанавливаются в нулевое состояние 6[3-0]=0100 (такт 7). Одновременно в такте 7 в нулевое состояние устанавливаются счетчики в группе 70, …, 7к, так как единичное значение установлено на входах R синхронной установки в нулевое состояние счетчиков.

Далее в тактах 6-8 на внешнюю группу входных данных IBD последовательно поступают коды IBD=1, 0, 0 шестой-восьмой входных групп для второго входного блока, которые принимаются в регистр входных данных RD 3 (такты 7-9), по которым устанавливаются соответствующие унитарные коды «1 из К» на выходах дешифратора групп DCG 4 и далее осуществляется счет в соответствующих триггерах из группы 60, …, 6к и счетчиках из группы 70, …, 7к.

В такте 10 поступает единичный сигнал конца блока 1ЕВ=1 для второго входного блока, по которому разрешается работа выходного буфера ОВ 10, в который в такте 11 для второго блока IBD=2100, с выходов триггеров группы 60, …, 6к и счетчиков группы 70, …, 7к по первому адресу записывается код ОВ (А1)=0112 - отсутствие групп соответствующих коду 3, одна группа соответствующая коду 2, одна группа соответствующая коду 1 и две группы соответствующие коду 0.

Одновременно в такте 10 по единичному сигналу конца блока IEB=1 разрешается работа группы дешифраторов DC 80, 8к, на соответствующих выходах которых формируются единичные значения, по которым в такте 11 осуществляется счет в матрице счетчиков 9[0:М, 0:К]: в нулевой строке только в третьем столбце - отсутствие групп с кодом 3 во втором блоке входных данных и устанавливается код 9[0, 3-0]=2000; в первой строке во втором и первом столбцах - по одному разу встречаются группы с кодами 2 и 1 и устанавливается код 9[1, 3-0]=0121; во второй строке только в нулевом столбце - два раза встречаются группы с кодом 0 и устанавливается код 9[2, 3-0]=0101; в третьей строке отсутствует счет так как нет кодов групп которые встречаются три раза.

Для третьего входного блока на внешнюю группу входных данных IBD последовательно поступают коды IBD=3, 2, 1,0 девятой-двенадцатой входных групп (такты 9-12), по которым формируются соответствующие унитарные коды «1 из К» на выходах дешифратора групп DCG 4, по которым далее осуществляется счет в соответствующих триггерах из группы 60, …, 6к и счетчиках из группы 70, …, 7к.

В такте 14 поступает единичный сигнал конца блока IEB=1 для третьего входного блока, по которому разрешается работа выходного буфера ОВ 10, в который в такте 15 для третьего блока IBD=3210, с выходов триггеров группы 60, …, 6к и счетчиков группы 70, …, 7к по второму адресу записывается код ОВ (А2)=1111 - в третьем блоке встречаются по одной группе соответствующей всем кодам 3, 2,1, 0.

Одновременно в такте 15 по единичному сигналу конца блока IEB=1 осуществляется счет в матрице счетчиков 9[0:М, 0:К] - только в первой строке, так как все коды в третьем блоке встречаются по одному разу и устанавливается код 9[1, 3-0]=1232.

Для четвертого входного блока на внешнюю группу входных данных IBD последовательно поступают коды IBD=3, 1, 3, 3 тринадцатой-шестнадцатой входных групп (такты 13-16), для которых выполняется выше рассмотренный алгоритм.

В такте 18 поступает единичный сигнал конца блока IEB=1 для четвертого входного блока, по которому разрешается работа выходного буфера ОВ 10, в который в такте 19 для четвертого блока IBD=3133, с выходов триггеров группы 60, …, 6к и счетчиков группы 70, …, 7к по третьему адресу записывается код ОВ (А3)=3010 - три группы соответствующие коду 3, нет групп соответствующих коду 2, одна группа соответствующая коду 1 и нет групп соответствующих коду 0.

Одновременно в такте 19 по единичному сигналу конца блока IEB=1 осуществляется счет в матрице счетчиков 9[0:М, 0:К]: в первой строке в первом столбце - один раз встречается группа с кодом 1 и устанавливается код 9[1, 3-0]=1242; в третьей строке в третьем столбце - три раза встречаются группы с кодом 3 и устанавливается код 9[3, 3-0]=1000.

Кроме того, одновременно в такте 18 по единичному сигналу остановки STOP=l устанавливается нулевое значение флага разрешения работы FE=0 на выходе элемента И с инверсным входом 2, и далее на следующих тактах IC запрещается работа дешифратора групп DCG 4 - на всех выходах устанавливаются нулевые значения. При этом также сигналу остановки STOP=l в нулевое состояние переключается RS-триггер 1 пуска-останова TSS=0.

Кроме того во время работы предлагаемого устройства на группы внешних выходов количества одинаковых групп в последовательности OS передаются значения счетчиков нулевой строки матрицы 9[0, 3-0] и последовательно устанавливаются коды: QS[3-0]=1000 (такт 7); QS[3-0]=2000 (такт 11); QS[3-0]=2101 (такт 19) - соответствующие количества блоков в которых отсутствуют группы соответственно с кодами 3,2, 1,0.

Далее после сигнала остановки STOP=1 в тактах 19-22 задается единичное значение на внешнем входе выдачи количества одинаковых групп IES=1. При этом осуществляется последовательная передача между строками матрицы счетчиков 9[0:М, 0:К] в направлении от К-ой строки к 0-ой строке и запись нулевых кодов, а также осуществляется последовательная выдача с выходов нулевой строки матрицы счетчиков на группу внешних выходов QS: в такте 20 устанавливается код OS [3-0]=1242 -количество блоков в которых входных коды групп встречаются один раз - в одном блоке код 3, в двух блоках код 2, в четырех блоках код 1 и в двух блоках код 0; в такте 21 устанавливается код QS[3-0]=0101 - количество блоков в которых входных коды групп встречаются два раза - в одном блоке код 2 и в одном блоке код 0; в такте 22 устанавливается код QS[3-0]=1000 - количество блоков в которых входных коды групп встречаются три раза - в одном блоке код 3.

Таким образом для входной последовательности данных, содержащей W=4 блока по четыре k=2 разрядных группы входных данных, выявлены и проведен подсчет одинаковых групп бит с кодами 3, 2, 1, 0 в каждом блоке для которых соответствующие значения записаны в выходной буфер ОВ 10 по четырем адресам ОВ(А0), ОВ(А3), а также в счетчиках матрицы 9[0:М, 0:К] проведен подсчет блоков последовательности в которых соответственно коды 3, 2, 1, 0 встречаются три раза, два раза, один раз или ни разу (отсутствуют в блоке)

Считывание результатов на группу внешних выходов количества одинаковых групп в блоках QB из выходного буфера ОВ 10 выполняется под управлением по внешней шине управления обменом ЕО. При реализации выходного буфера ОВ в виде двухпортовой памяти FIFO, обмен можно выполнять в процессе детектирования входных групп с учетом значений соответствующих флагов «Буфер пуст» FZ и «Буфер заполнен» FF.

Предлагаемое устройство может быть применено для аппаратной реализации статистических тестов, разработанных лабораторией информационных технологий Национального института стандартов и технологий (NIST, США), целью которых является определение меры случайности двоичных последовательностей, порожденных генераторами случайных чисел. В частности, предлагаемое устройство реализует тест на произвольные отклонения, в котором осуществляется подсчет отклонений кумулятивных сумм в состояниях циклов. В задачах обработки событий и результатов физических экспериментов осуществляется выявление одинаковых событий и подсчет их количества.

Вышеизложенные сведения позволяют сделать вывод, что предлагаемое устройство решает поставленную задачу и соответствует заявляемому техническому результату -реализация возможности детектирования одинаковых групп числовой и символьной информации и подсчет количества таких групп в блоках входных данных входной двоичной последовательности.

Изобретение относится к устройствам обработки данных и может быть использовано для построения функциональных узлов для анализа свойств генераторов псевдослучайных последовательностей двоичных чисел. Технический результат - обеспечение возможности детектирования одинаковых групп числовой и символьной информации и подсчет количества таких групп в блоках входных данных входной двоичной последовательности. Устройство содержит внешние группу входных данных IBD, вход конца блока IEB и вход выдачи количества одинаковых групп IES, группы внешних выходов количества одинаковых групп в блоках QB и количества одинаковых групп в последовательности QS, RS-триггер пуска-останова TSS 1, элемент И с инверсным входом 2, регистр входных данных RD 3, дешифратор групп DCG 4, группу элементов И 50, …, 5к, группу триггеров 60, …, 6к, группу счетчиков 70, …, 7к, группу дешифраторов 80, …, 8к, матрицу счетчиков 9[0:М, 0:К], выходной буфер ОВ 10, внешние входы тактового сигнала 1С, пуска устройства START и остановки устройства STOP, внутренний флаг разрешения работы FE, внешняя шина управления обменом ЕО, внешние флаги FF «Буфер заполнен», FZ «Буфер пуст». 2 ил.

Устройство для подсчета одинаковых групп бит в блоках двоичной последовательности содержит внешние группу входных данных IBD, вход конца блока IEB и вход выдачи количества одинаковых групп IES, группы внешних выходов количества одинаковых групп в блоках QB и количества одинаковых групп в последовательности QS, RS-триггер пуска-останова TSS 1, элемент И с инверсным входом 2, регистр входных данных RD 3, дешифратор групп DCG 4, группу элементов И 50, …, 5к, группу триггеров 60, …, 6к, группу счетчиков 70, …, 7к, группу дешифраторов 80, …, 8к, матрицу счетчиков 9[0:М, 0:К], содержащую (М+1) строк и (К+1) столбцов (где К - количество различных групп в блоках данных, М - максимальное количество одинаковых групп в блоке данных) и выходной буфер ОВ 10,

а также введены внешние входы тактового сигнала IC, пуска устройства START и остановки устройства STOP, внутренний флаг разрешения работы FE, внешняя шина управления обменом ЕО, внешние флаги FF «Буфер заполнен», FZ «Буфер пуст»,

причем внешний тактовый вход устройства IC соединен с входами синхронизации С RS-триггера пуска-останова TSS 1, регистра входных данных RD 3, триггеров группы 60, …, 6к, счетчиков группы 70, …, 7к, счетчиков матрицы 9[0:М, 0:К] и выходного буфера ОВ 10,

внешний вход пуска устройства START соединен с входом S синхронной установки в единичное состояние RS-триггера пуска-останова TSS 1,

внешний вход остановки устройства STOP соединен с входом R синхронной установки в нулевое состояние RS-триггера пуска-останова TSS 1, а также соединен со вторым инверсивным входом элемента И 2,

причем прямой выход RS-триггера пуска-останова TSS 1 соединен с первым прямым входом элемента И 2 с инверсивным входом, выход которого является внутренним флагом разрешения работы FE и соединен с входом разрешения работы Е дешифратора групп DCG 4,

группа входных данных IBD соединена с группой D-входов регистра входных данных RD 3, выходы которого соединены с адресными входами дешифратора групп DCG 4, у которого (К+1) выходов соединены с Т-входами одноименных триггеров группы 60, …, 6к, с входами разрешения работы СЕ одноименных счетчиков группы 70, …, 7к и со вторыми входами одноименных элементов И группы 50, …, 5к, выходы которых соединены с D-входами одноименных триггеров группы 60, …, 6к, выходы которых соединены с Т-входами одноименных счетчиков группы 70, …, 7к, с соответствующими D-входами выходного буфера ОВ 10 и с младшими адресными входами одноименных дешифраторов группы 80, …, 8к, у которых старшие разряды адресов соединены с выходами одноименных счетчиков группы 70, …, 7к, выходы которых также соединены с соответствующими группами D-входов выходного буфера ОВ 10, который также подключен к внешней шине ЕО управления обменом, а соответствующие выходы выходного буфера ОВ 10 являются группой внешних выходов количества одинаковых групп в блоках QB и соответствующими внешними флагами «Буфер заполнен» FF и «Буфер пуст» FZ,

кроме того, внешний вход конца блока IEB соединен с первыми входами элементов И группы 50, …, 5к, с входами разрешения записи L триггеров группы 60, …, 6к, с входами R синхронной установки в нулевое состояние счетчиков группы 70, …, 7к, с входом разрешения работы СЕ выходного буфера ОВ 10 и с входами разрешения работы Е дешифраторов группы 80, …, 8к, у каждого из которых (М+1) выходов, начиная с нулевого выхода до М-го выхода, соединены с входами СЕ разрешения работы счетчиков соответствующих строк, начиная с нулевой строки до М-й строки, одноименных столбцов матрицы счетчиков 9[0:М, 0:К], у которых входы L разрешения записи счетчиков соединены с внешним входом выдачи количества одинаковых групп IES,

причем в К-й строке матрицы счетчиков матрицы 9[0:М, 0:К] на группы D-входов счетчиков заданы нулевые коды «0», а группы D-входов счетчиков матрицы 9[0:М, 0:К], начиная с (К-1)-й строки до нулевой строки, подключены к выходам счетчиков следующих строк матрицы, начиная с К-й строки до первой строки, а выходы счетчиков нулевой строки матрицы являются соответствующими группами внешних выходов количества одинаковых групп в последовательности QS.

| УСТРОЙСТВО ДЛЯ ДЕТЕКТИРОВАНИЯ ГРУПП ЕДИНИЧНЫХ БИТ И МАКСИМАЛЬНОЙ ГРУППЫ В БЛОКАХ ДАННЫХ | 2023 |

|

RU2800039C1 |

| УСТРОЙСТВО ГРУППОВОЙ СТРУКТУРЫ ДЛЯ ДЕТЕКТИРОВАНИЯ ШАБЛОНОВ БИТ ПЕРЕМЕННОЙ РАЗРЯДНОСТИ | 2023 |

|

RU2809741C1 |

| УСТРОЙСТВО ПОСЛЕДОВАТЕЛЬНОГО ТИПА ДЛЯ ДЕТЕКТИРОВАНИЯ ГРАНИЦ ДИАПАЗОНА ЕДИНИЧНЫХ БИТ В БИНАРНОЙ ПОСЛЕДОВАТЕЛЬНОСТИ | 2020 |

|

RU2749150C1 |

| УСТРОЙСТВО ДЛЯ ДЕТЕКТИРОВАНИЯ ГРУПП ЕДИНИЧНЫХ БИТ В БЛОКАХ ДВОИЧНОЙ ПОСЛЕДОВАТЕЛЬНОСТИ | 2023 |

|

RU2809743C1 |

| US 6513053 B1, 28.01.2003 | |||

| US 20210224042 A1, 22.07.2021 | |||

| US 6904114 B2, 07.06.2005. | |||

Авторы

Даты

2024-10-08—Публикация

2024-03-04—Подача