Предлагаемое изобретение относится к области радиоэлектронной техники, в частности к схемотехническому исполнению обратной связи микросхем понижающих регуляторов (стабилизаторов) напряжения, обеспечивающих формирование выходного стабилизированного напряжения в диапазоне от около нулевых значений до уровня источника опорного напряжения стабилизатора.

В настоящее время большинство подсистем электропитания вычислительных ядер процессорных компонентов и микроконтроллеров, характеризующихся низким уровнем выходного стабилизированного напряжения, строится на электронной компонентной базе иностранного производства. Основанием для создания настоящего технического решения является необходимость создания источников низкого (менее 0,8 В) стабилизированного выходного напряжения на базе отечественных микросхем регуляторов напряжения с целью замены иностранных функциональных аналогов.

Подходящие по выходному напряжению микросхемы стабилизаторов выпускаются несколькими иностранными предприятиями [1-4]. Отечественные микросхемы стабилизаторов с низким выходным напряжением и подходящими характеристиками по входному напряжению и выходной мощности российские предприятия серийно не выпускают.

На техническом уровне проблема заключается в ограничениях способа контроля и управления выходным напряжением микросхемы стабилизатора с помощью сравнения уровней выходного напряжения, поданного на встроенный в микросхему стабилизатора усилитель ошибки через цепь обратной связи (далее - ОС), собранной по классической схеме на основе резистивного делителя напряжения, которую используют в схемах включения микросхем стабилизаторов иностранного производства [1-4], и напряжения, вырабатываемого источником опорного напряжения (далее - ИОН).

В зависимости от уровня и знака результирующего сигнала ошибки, срабатывает регулирующая ток нагрузки часть схемы, и выходное напряжение микросхемы стабилизатора стремится к заданному значению, которое достигается при условии равенства выходного напряжения цепи ОС и напряжения ИОН и характеризуется отсутствием сигнала ошибки.

В случае использования классической ОС, минимальный уровень выходного напряжения, при котором сигнал ошибки может принять нулевое значение, соответствует уровню ИОН.

В теории обеспечить стабилизацию выходного напряжения на низких (меньше ИОН) уровнях можно за счет подачи усиленного выходного напряжения на нагрузке на микросхему стабилизатора для сравнения с ИОН. В этом случае необходимо применение дополнительного усилителя в цепи ОС, который будет вносить временную задержку и способствовать возникновению самовозбуждения микросхемы стабилизатора. На практике данный вариант не применяется в силу высокой стоимости и сложности настройки.

Другой, также теоретический вариант, заключается в применении компенсирующего источника электропитания, включенного последовательно с нагрузкой в противофазе к основному. Напряжение на компенсирующем источнике подбирается из расчета разности напряжений обоих источников равной требуемому напряжению. Недостатками является стоимость реализации и требования к мощности компенсирующего источника, которая должна быть эквивалентной мощности основного источника.

Наиболее реалистичный вариант базируется на передаче напряжения с нагрузки на микросхему стабилизатора с положительным постоянным смещением, которое не должно вносить временных искажений и влиять на регулировочную характеристику микросхемы стабилизатора за исключением абсолютного уровня напряжения, передаваемого по цепи ОС, для сравнения с ИОН.

Задача, решаемая предлагаемым изобретением, заключается в расширении функциональных возможностей и рабочих режимов микросхем стабилизаторов. При этом указанным решением достигается технический результат, заключающийся в расширении диапазона формирования стабилизированного выходного напряжения в сторону от около нулевых значений до уровня напряжения ИОН микросхемы стабилизатора.

Вышеуказанная задача достигается благодаря применению схемотехнического исполнения обратной связи микросхемы стабилизатора, включающего помимо нагрузочного резистора генератор стабильного тока (ГСТ), источник постоянного напряжения смещения и балансировочный резистор. Причем вход ГСТ подключен к источнику напряжения электропитания, а выход подключен к положительному выводу источника постоянного напряжения смещения с возможностью формирования в точке их соединения выходного напряжения обратной связи, превышающего выходное напряжение микросхемы стабилизатора на нагрузочном резисторе на постоянную величину напряжения смещения, поступающего на микросхему стабилизатора для сравнения с опорным напряжением, при этом отрицательный вывод источника постоянного напряжения смещения подключен к балансировочному и нагрузочному резисторам, включенным в схему параллельно друг другу так, что в точку их соединения подается выходное напряжение микросхемы стабилизатора, при этом нагрузочный и балансировочный резисторы подключены между выходом микросхемы стабилизатора и нулевым потенциалом электропитания.

Протекающий через источник постоянного напряжения смещения выходной ток ГСТ обеспечивает его рабочий режим. В точке соединения ГСТ и источника постоянного напряжения формируется выходное напряжение обратной связи, превышающее выходное напряжение микросхемы стабилизатора на нагрузочном резисторе на постоянную величину напряжения смещения, которое поступает на микросхему стабилизатора и используется для сравнения с опорным напряжением. Балансировочный резистор обеспечивает балансировку и стабильность работы цепи обратной связи при токах нагрузки, проходящих через нагрузочный резистор, не превышающих по амплитуде выходной ток ГСТ. Нагрузочный резистор выполняет функцию эквивалента электрической нагрузки микросхемы стабилизатора.

В результате применения предложенной электрической схемы обратной связи, выходное напряжение которой в итоге представляет сумму напряжения источника напряжения смещения и выходного напряжения микросхемы стабилизатора на нагрузочном резисторе, условие равенства выходного напряжения обратной связи и напряжения ИОН, при котором микросхема стабилизатора вырабатывает постоянное напряжение, наступает для диапазона малых выходных напряжений, не превышающих напряжения ИОН стабилизатора.

В отличие от классической схемы обратной связи на основе делителей выходного напряжения данное решение реализуется на основе ГСТ, который обеспечивает рабочий режим источника постоянного напряжения смещения и не может вносить временных искажений в сигнал обратной связи, передаваемый с нагрузки на микросхему стабилизатора.

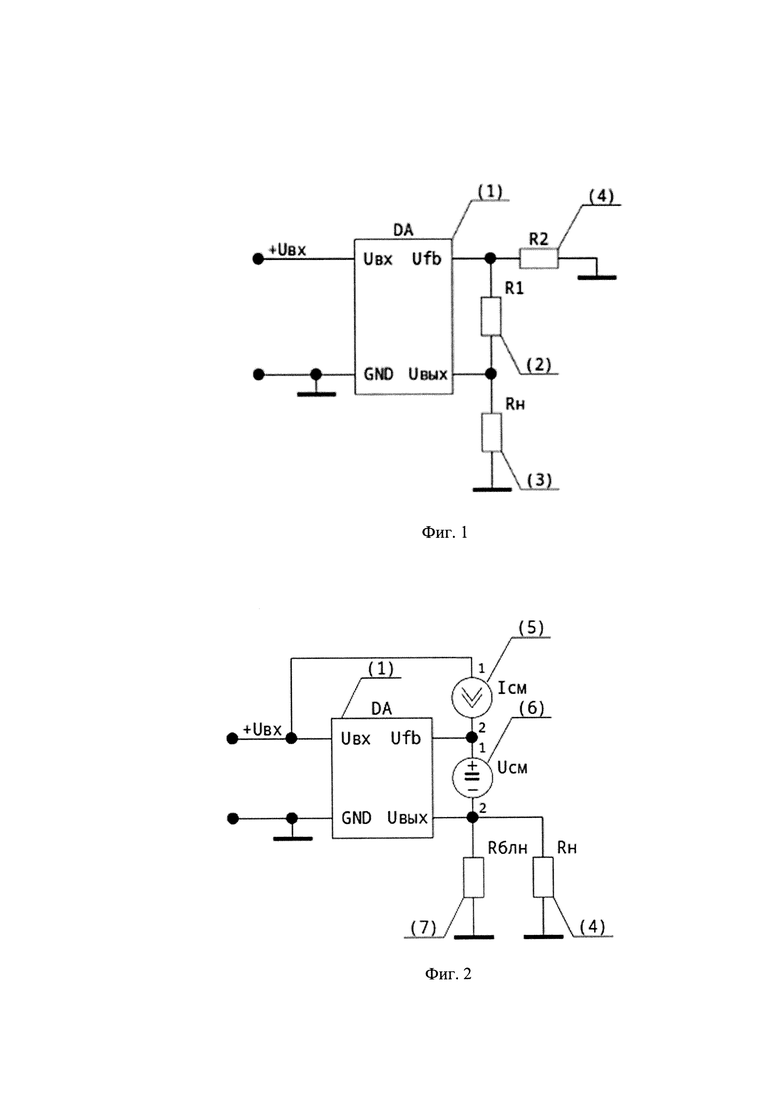

На фиг. 1 приведена схема подключения к микросхеме стабилизатора классической обратной связи, известная из уровня техники, где обозначены:

1 - микросхема стабилизатора;

2 - первый резистор делителя выходного напряжения микросхемы стабилизатора;

3 - второй резистор делителя выходного напряжения микросхемы стабилизатора;

4 - нагрузочный резистор.

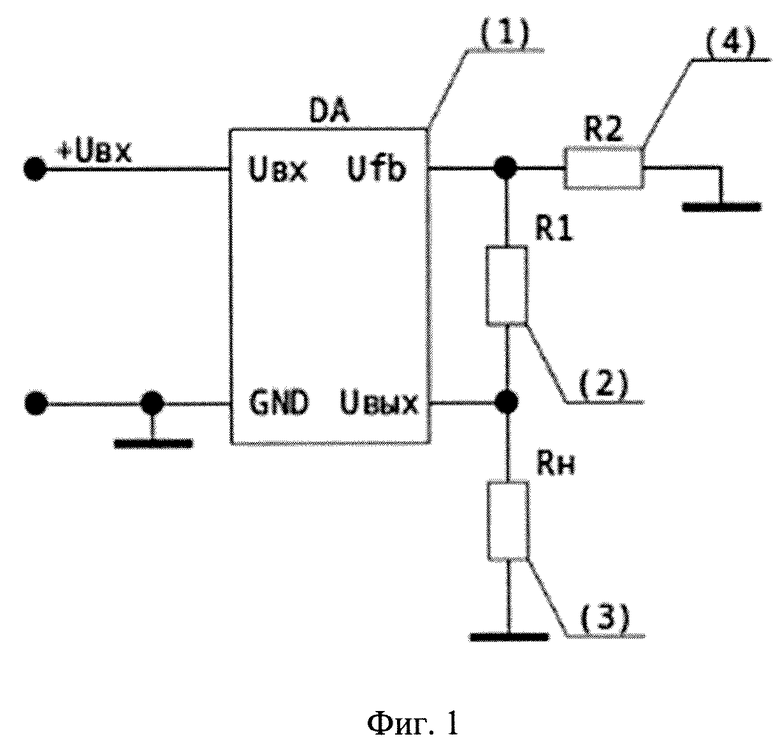

На фиг. 2 приведена схема подключения к микросхеме стабилизатора обратной связи согласно предлагаемому решению, где обозначены:

1 - микросхема стабилизатора;

4 - нагрузочный резистор (далее - нагрузка);

5 - генератор стабильного тока (ГСТ);

6 - источник постоянного напряжения смещения;

7 - резистор балансировочный.

В электрической схеме высокий потенциал напряжения электропитания + Uвх подается на вход Uвх микросхемы стабилизатора 1 и вывод 1 (втекающего тока) ГСТ 5. Нулевой потенциал электропитания («земля») подается на вывод GND микросхемы стабилизатора 1, нагрузку 4 Rн и резистор 7 балансировочный Rблн. Вывод 2 (вытекающего тока) ГСТ 5 соединен с положительным выводом 1 источника 6 постоянного напряжения смещения Uсм и входом измерения напряжения, передаваемого цепью обратной связи, выводом Ufb микросхемы стабилизатора 1. Отрицательный вывод 2 источника 6 постоянного напряжения смещения Uсм соединен с нагрузочным резистором 4 Rн, резистором 7 балансировочным Rблн, который обеспечивает балансировку и стабильность работы цепи ОС при токах, проходящих через нагрузку 4 Rн, не превышающих по амплитуде выходной ток ГСТ 5, и выводом Uвых микросхемы стабилизатора. В соответствии с принципом работы стабилизатора напряжения 1, выходное напряжение которого на выводе Uвых поддерживается на постоянном (заданном расчетном) уровне при условии равенства напряжения, поданного через цепь обратной связи с вывода Uвых на вывод Ufb, напряжению Uион микросхемы стабилизатора 1. Оригинальная электрическая схема обратной связи микросхемы стабилизатора 1, реализованная как источник Uсм 6, подключенный между выводом Uвых и выводом Ufb микросхемы стабилизатора 1 последовательно с нагрузочным резистором 4 Rн относительно «земли», обеспечивает подачу на вывод Ufb суммы напряжений Uсм и Uвых, и за счет дополнительного постоянного напряжения смещения в цепи обратной связи напряжение на выводе Ufb достигнет равного с напряжением Uион значения при меньшем на величину Uсм напряжении на выводе Uвых микросхемы стабилизатора 1.

Представленная электронная схема цепи обратной связи обеспечивает подачу на вход Ufb микросхемы стабилизатора суммы двух напряжений:

Микросхема стабилизатора в рабочем режиме вырабатывает постоянное стабилизированное напряжение на нагрузке Rн расчетного уровня, значение которого соответствует условию равенства напряжения на входе Ufb и Uион микросхемы стабилизатора. В соответствии с формулой (1) указанное равенство в зависимости от величины Uсм достигается при выходных напряжениях микросхемы стабилизатора от нулевого значения до напряжения Uион.

Схемотехническая реализация цепи обратной связи может быть выполнена исключительно на пассивных электронных компонентах без ухудшения амплитудно-временных параметров микросхемы стабилизатора. В качестве источника Uсм может использоваться резистор Rсм, на котором образуется падение напряжения, и значение которого определяется номинальным сопротивлением резистора Rсм и протекающим через него током 1 см в соответствии с формулой:

Ток Iсм вырабатывается ГСТ. Дополнительный балансировочный резистор Rблн обеспечивает балансировку и стабильность работы цепи ОС при отсутствии или малой величине тока нагрузки Iн в соответствии с формулой:

Таким образом, предложенное техническое решение позволяет стабилизировать выходное напряжение микросхемы в диапазоне от около нулевых значений до уровня напряжения ИОН, таким образом, расширяя ее функциональные возможности и рабочие режимы, при этом оно применимо ко всем типам отечественных микросхем стабилизаторов и может заменить функциональные аналоги иностранного производства.

Список источников информации:

[1] ST Microelectronics (EU), Data Sheet L6982 (L6982CDR, L6982NDR) «38 V, 2 А synchronous step-down converter with low quiescent current», DS13683 - Rev 1 - April 2021, сайт: www.st.com

[2] Texas Instruments (USA), Data Sheet TPS54202 «4.5-V to 28-V Input, 2-A Output, EMI Friendly Synchronous Step Down Converter», SLVSD26B - April 2016 - revised April 2021, сайт: www.ti.com

[3] Analog Devices (USA), Data Sheet ADP2384 «20 V, 4 A, Synchronous, Step-Down DC-to-DC Regulator», One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, сайт: www.analog.com

[4] Global Mixed-mode Technology (Taiwan), Data Sheet G973 «4A Low Dropout Regulator with Enable», Ver. 04, Oct. 25, 2011, сайт: www.gmt.com.tw

| название | год | авторы | номер документа |

|---|---|---|---|

| Способ построения стабилизатора постоянного напряжения | 2021 |

|

RU2775059C1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ТОКА | 1991 |

|

RU2047181C1 |

| Стабилизатор напряжения питания часовой интегральной схемы | 1987 |

|

SU1453378A1 |

| СПОСОБ ИЗМЕРЕНИЯ ДИНАМИЧЕСКИХ ХАРАКТЕРИСТИК КВАРЦЕВОГО МАЯТНИКОВОГО АКСЕЛЕРОМЕТРА (ВАРИАНТЫ) | 2013 |

|

RU2533750C1 |

| СПОСОБ ЗАЩИТЫ ЛИНЕЙНОГО СТАБИЛИЗАТОРА НАПРЯЖЕНИЯ ПОСТОЯННОГО ТОКА ОТ КОРОТКОГО ЗАМЫКАНИЯ С МАЛЫМИ ТЕПЛОВЫМИ ПОТЕРЯМИ | 2022 |

|

RU2786935C1 |

| КОРРЕКТОР КОЭФФИЦИЕНТА МОЩНОСТИ | 2014 |

|

RU2560103C1 |

| ФОРМИРОВАТЕЛЬ ИМПУЛЬСОВ ЛИНЕЙНО ИЗМЕНЯЮЩЕГОСЯ НАПРЯЖЕНИЯ | 2002 |

|

RU2239280C2 |

| ГЕНЕРАТОР ПЕРЕМЕННОГО ТОКА | 2003 |

|

RU2235415C1 |

| СПОСОБ УПРАВЛЕНИЯ УРОВНЕМ СВЕТООТДАЧИ СВЕТОДИОДОВ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2018 |

|

RU2693844C1 |

| СПОСОБ ОПРЕДЕЛЕНИЯ НАПРЯЖЕНИЯ ПЛОСКИХ ЗОН ПОЛУПРОВОДНИКА В МЕТАЛЛ-ДИЭЛЕКТРИК-ПОЛУПРОВОДНИК-СТРУКТУРАХ | 2000 |

|

RU2212078C2 |

Изобретение относится к области радиоэлектронной техники, в частности к схемотехническому исполнению обратной связи микросхем понижающих регуляторов (стабилизаторов) напряжения, обеспечивающих формирование выходного стабилизированного напряжения в диапазоне от около нулевых значений до уровня источника опорного напряжения стабилизатора. Технический результат - расширение диапазона формирования стабилизированного выходного напряжения в сторону от около нулевых значений до уровня источника опорного напряжения микросхемы стабилизатора. Вышеуказанная задача достигается благодаря применению схемотехнического исполнения обратной связи микросхемы стабилизатора, включающего помимо нагрузочного резистора генератор стабильного тока (ГСТ), источник постоянного напряжения смещения и балансировочный резистор. Причем вход ГСТ подключен к источнику напряжения электропитания, а выход подключен к положительному выводу источника постоянного напряжения смещения с возможностью формирования в точке их соединения выходного напряжения обратной связи, превышающего выходное напряжение микросхемы стабилизатора на нагрузочном резисторе на постоянную величину напряжения смещения, поступающего на микросхему стабилизатора для сравнения с опорным напряжением, при этом отрицательный вывод источника постоянного напряжения смещения подключен к балансировочному и нагрузочному резисторам, включенным в схему параллельно друг другу так, что в точку их соединения подается выходное напряжение микросхемы стабилизатора, при этом нагрузочный и балансировочный резисторы подключены между выходом микросхемы стабилизатора и нулевым потенциалом электропитания. 2 ил.

Электронная схема обратной связи микросхемы понижающего стабилизатора напряжения, содержащая нагрузочный резистор, отличающаяся тем, что содержит генератор стабильного тока, источник постоянного напряжения смещения и балансировочный резистор, причем вход генератора стабильного тока подключен к источнику напряжения электропитания, а выход подключен к положительному выводу источника постоянного напряжения смещения с возможностью формирования в точке их соединения выходного напряжения обратной связи, превышающего выходное напряжение микросхемы стабилизатора на нагрузочном резисторе на постоянную величину напряжения смещения, поступающего на микросхему стабилизатора для сравнения с опорным напряжением, при этом отрицательный вывод источника постоянного напряжения смещения подключен к балансировочному и нагрузочному резисторам, включенным в схему параллельно друг другу так, что в точку их соединения подается выходное напряжение микросхемы стабилизатора, при этом нагрузочный и балансировочный резисторы подключены между выходом микросхемы стабилизатора и нулевым потенциалом электропитания.

| СТАБИЛИЗАТОР ПОСТОЯННОГО НАПРЯЖЕНИЯ С ИМПУЛЬСНЫМ РЕГУЛИРОВАНИЕМ | 1991 |

|

RU2014646C1 |

| Источник вторичного электропитания для сети постоянного напряжения | 1990 |

|

SU1786476A1 |

| ПОНИЖАЮЩИЙ СТАБИЛИЗАТОР | 2007 |

|

RU2339072C1 |

| Импульсный понижающий стабилизатор постоянного напряжения | 1990 |

|

SU1786477A1 |

| 0 |

|

SU158718A1 | |

| JP 7281772 А, 27.10.1995. | |||

Авторы

Даты

2025-02-07—Публикация

2024-07-11—Подача