Область техники

Изобретение относится к области проектирования и конструирования микросхем (топологии интегральной микросхемы), в частности предназначено для создания микросхем, которые имеют специальный режим с низким потреблением мощности.

Уровень техники

Каскодные ячейки ввода-вывода (I/O) используются в системах на кристалле для поддержки уровней напряжений превышающие максимально допустимые напряжения для одиночных транзисторов. Например, используя 3V транзисторы, можно добиться работы I/O ячейки до напряжений 6V. Такие ячейки требуют нескольких аналоговых блоков, такие как генератор опорного напряжения, источники тока, операционные усилители для поддержания необходимых уровней для защиты 3V транзисторов от напряжения 6V. Эти схемы даже в спящем режиме потребляют значительное количество тока (вызвано необходимостью поддерживать опорные уровни и следить за уровнем I/O питания), что сказывается на их применении в системах с низким потреблением мощности.

Из уровня техники известен способ реализации режима с низким потреблением тока в спящем режиме для цифровых блоков по патенту WO 2010088155 (РФ №2486574) заключающийся в запуске логического перехода, посредством модуля измерений, в первый вентиль последовательного соединения множества вентилей и которые физически распределены по участку интегральной микросхемы, который занят логической схемой, которая реализует работу интегральной микросхемы, при этом число вентилей во множестве логических вентилей больше, чем число вентилей, которые срабатывают за такт генератора тактовых импульсов, обеспеченного для интегральной микросхемы, при этом генератор тактовых импульсов задает рабочую частоту интегральной микросхемы; и измерения времени, посредством модуля измерений, до обнаружения соответствующего перехода из последнего вентиля последовательного соединения множества вентилей, при этом измеренное время сравнивается с заранее заданным временем для регулировки напряжения питания интегральной микросхемы.

Недостатком способа является неприменимость данного метода для цифро-аналоговых схем и необходимость использования двух источников напряжения питания, один из которых основной с большой нагрузочной способностью, а другой маломощный. В момент перехода в спящий режим основной источник питания отключается и блоки, которые к нему подключены, оказываются обесточенными. Маломощный источник не отключается и запитывает только необходимые блоки. Также недостатком является изменение функционала микросхемы, так как основные блоки оказываются неработоспособными.

Другой патент с реализацией режима с низким потреблением WO 2016014197. Суть изобретения в использовании внешней микросхемы управления уровнем напряжения с целью понижения напряжения питания схемы и тем самым понижение мощности.

Недостатком является использования источника питания с регулируемым уровнем выходного напряжения, а также сложного блока самокалибровки.

Раскрытие изобретения

Техническим результатом изобретения является снижение потребления тока каскодной ячейки ввода-вывода в микросхеме.

Технический результат достигает тем, что предложен способ реализации режима с низким потреблением тока в спящем режиме для каскодной ячейки ввода-вывода, содержащей детектор питания, генератор опорных уровней, служебные ячейки ввода-вывода, повторитель опорных уровней, в котором в момент перехода в режим с низким потреблением мощности активируется инициализирующий сигнал SLEEP, одновременно транзистор Р1 отключает служебные ячейки от основного источника питания, транзистор Р2 подключает служебные ячейки к дополнительному источнику питания, детектор питания фиксирует режим дополнительного источника питания и переводит служебные ячейки в режим минимального токопотребления, при этом дополнительный источник питания имеет напряжение по меньшей мере 40%, и не превышающее 60% от напряжения основного источника, состояние выходных уровней генератора и повторителя уровней фиксируется и остается неизменным, I/O ячейки продолжают принимать опорные уровни соответствующие режиму основного источника питания, и ячейка продолжает корректную работу в режиме минимального токопотребления и может принимать входной инициализирующий сигнал низкой частоты, до 1MHz.

Совокупность приведенных выше существенных признаков приводит к тому, что:

Ячейки ввода-вывода, построенные по каскодной архитектуре, могут поддерживать напряжение питания в 2 раза больше, чем может выдержать одиночный МОП транзистор (максимально допустимое напряжение затвор-исток, затвор-сток, сток-исток) тем самым, при максимальном напряжении 3 В, используя каскодную структуру, можно создать ячейку, поддерживающую напряжения до 6 В. Такое решение требует использования дополнительных служебных подсхем, которые размещаются в I/O сегменте.

Краткое описание чертежей

Предлагаемое изобретение поясняется фиг. 1-3, на которых:

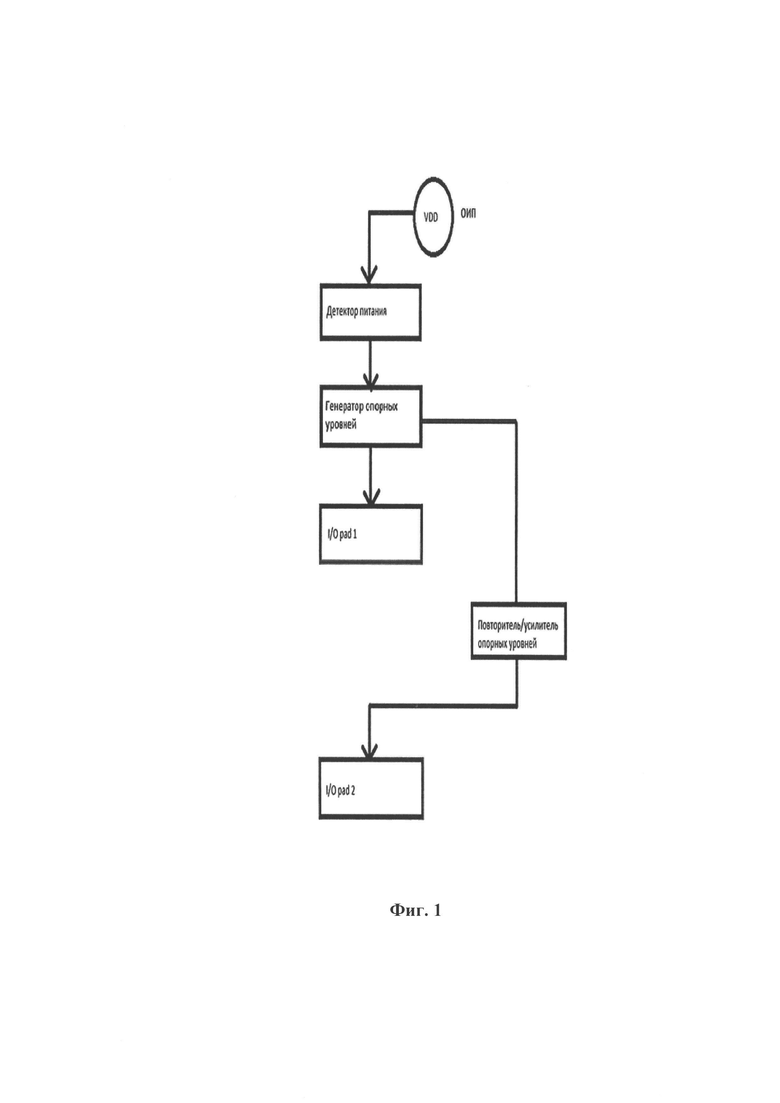

Фиг. 1 Состав I/O сегмента на кристалле;

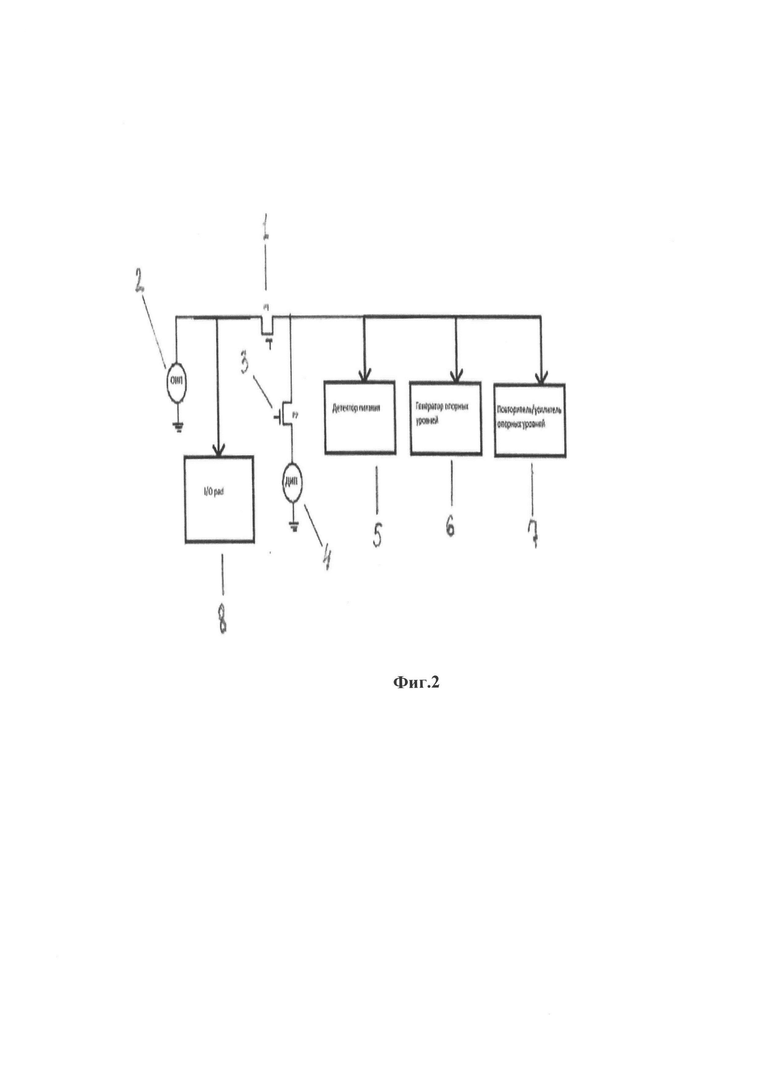

Фиг. 2 Реализации режима с низким потреблением мощности;

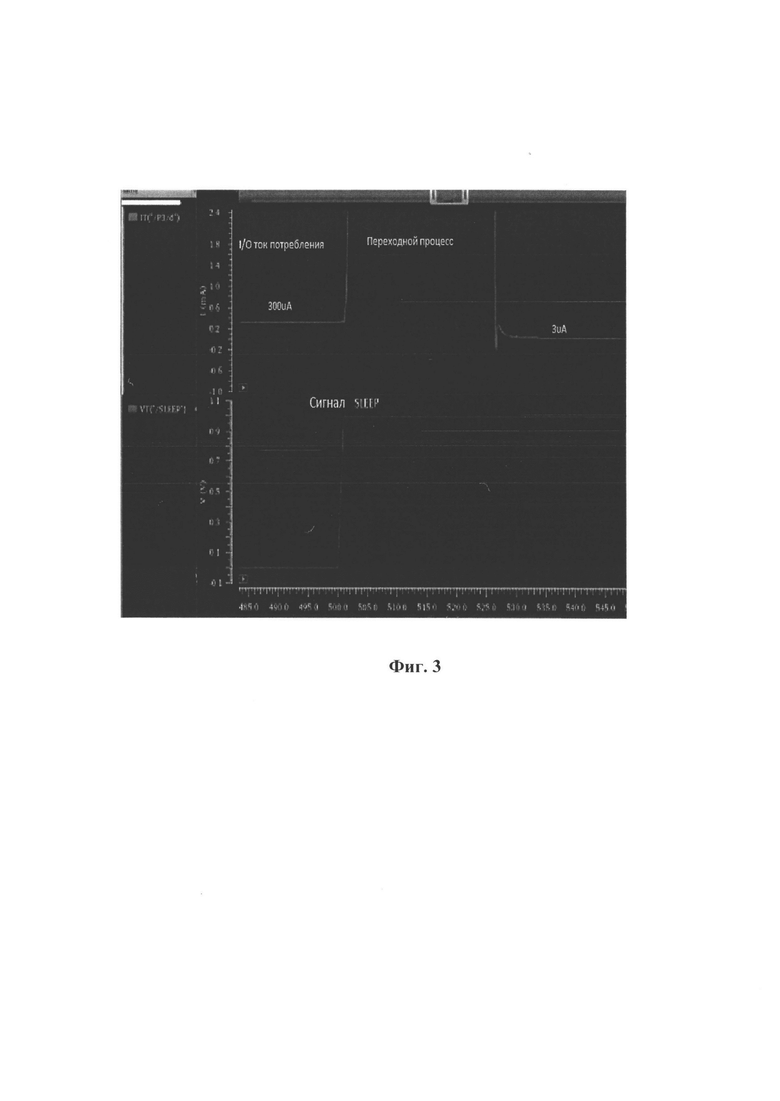

Фиг. 3 Результаты моделирования перехода в режим ультранизкого тока потребления.

Позициями на фигурах обозначены:

1 - транзистор Р1;

2 - основной источник питания (ОИП);

3 - транзистор Р2;

4 - дополнительный источник питания (ДИП);

5 - детектор питания;

6 - генератор;

7 - повторитель уровней;

8 - I/O ячейки.

Осуществление изобретения

Каскодная ячейка сегмента питания I/O на кристалле по фиг. 1 включает детектор питания, генератор опорных уровней, ячейки ввода-вывода (I/O pad 1 и I/O pad 2), повторитель/усилитель опорных уровней, в момент перехода в режим с низким потреблением мощности схема приведена на фиг. 2 активируется сигнал SLEEP, транзистор P1 1 отключает служебные ячейки от основного источника питания (ОИП) 2, транзистор Р2 3 подключает служебные ячейки к дополнительному источнику питания (ДИП) 4, детектор питания 5 фиксирует режим ДИП и переводит служебные ячейки в режим, при котором ток потребления минимален т.е. основные токопотребляющие блоки оказываются подключенными к ДИП и переведены в режим с низким потреблением электроэнергии, в момент инициализации сигнала SLEEP, состояние выходных уровней генератора 6 и повторителя уровней 7 фиксируется и остается неизменным несмотря на подключение блоков к ДИП. Таким образом, несмотря на то что на служебные ячейки подключены к ДИП и они переключены в режим с низким потреблением, сами I/O ячейки 8 продолжают принимать опорные уровни, соответствующие режиму основного источника питания (ОИП). В данном режиме I/O ячейка может принимать входной сигнал только низкой частоты, не более чем 1 Mhz для обеспечения корректной работы ячейки ввода-вывода в режиме пониженной мощности. При превышении частоты в 1MHz корректная работа ячейки не гарантируется. После деактивации сигнала SLEEP ячейка переходит в режим полной функциональности. Результаты моделирования перехода в режим ультранизкого тока потребления визуализированы на фиг. 3.

Дополнительный источник питания должен иметь напряжение должен иметь напряжение по меньшей мере 40%, и не превышающее 60% от напряжения основного источника в оптимальных условиях реализации вполовину меньшее, чем основной источник питания для защиты компонентов ячейки (МОП транзисторы) от перенапряжения и как следствие быстрой деградации характеристик транзисторов при превышении или понижении указанных диапазонов проявятся проблемы с деградацией характеристик транзисторов.

Пример осуществления

Приведенный ниже пример иллюстрирует вариант заявленного изобретения, но не ограничивает его.

1. Контроллер вырабатывает сигнал SLEEP, активируя режим с низким потреблением тока.

2. Транзистор Р1 отключает основные токопотребляющие схемы от источника ОИП.

3. Транзистор Р2 подключает токопотребляющие блоки к источнику ДИП, тем самым минимизируя потребляемую мощность, так как в конфигурации с ДИП упомянутые блоки находятся в режиме низкого потребления тока.

4. Основная ячейка ввода-вывода остается подключенной к ОИП и продолжает выдавать корректный сигнал, с частотой до 1 MHz.

| название | год | авторы | номер документа |

|---|---|---|---|

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2008 |

|

RU2390912C2 |

| СИСТЕМА ЭЛЕКТРЕТНОГО КОНДЕНСАТОРНОГО МИКРОФОНА | 2005 |

|

RU2310294C2 |

| МУЛЬТИДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2008 |

|

RU2374756C1 |

| Источник опорного напряжения | 1986 |

|

SU1374200A1 |

| КАСКОДНЫЙ ШИРОКОПОЛОСНЫЙ УСИЛИТЕЛЬ | 2010 |

|

RU2421878C1 |

| УСТРОЙСТВО для ДЕТЕКТИРОВАНИЯ АМПЛИТУДНО- МОДУЛИРОВАННЫХ СИГНАЛОВ | 1973 |

|

SU365794A1 |

| ГЕНЕРАТОР ОПОРНОГО НАПРЯЖЕНИЯ С НИЗКИМ ИМПЕДАНСОМ | 2012 |

|

RU2592719C2 |

| Способ выявления контрафактных микросхем, бывших в употреблении на основе свойств деградации СОЗУ | 2020 |

|

RU2757977C1 |

| СХЕМА СЧИТЫВАНИЯ СИГНАЛОВ ИЗ ЯЧЕЕК МАТРИЦЫ ФОТОДЕТЕКТОРОВ | 2008 |

|

RU2356177C1 |

| Усилитель мощности | 2023 |

|

RU2796545C1 |

Изобретение относится к области электронной техники. Техническим результатом является снижение потребления тока каскодной ячейки ввода-вывода в микросхеме. Для достижения указанного результата в способе реализации режима с низким потреблением тока в спящем режиме для каскодной ячейки ввода-вывода, содержащей детектор питания, генератор опорных уровней, служебные ячейки ввода-вывода, повторитель опорных уровней, в момент перехода в режим с низким потреблением мощности активируется инициализирующий сигнал SLEEP, одновременно транзистор Р1 отключает служебные ячейки от основного источника питания, транзистор Р2 подключает служебные ячейки к дополнительному источнику питания, детектор питания фиксирует режим дополнительного источника питания и переводит служебные ячейки в режим минимального токопотребления, при этом дополнительный источник питания имеет напряжение по меньшей мере 40%, и не превышающее 60% от напряжения основного источника, состояние выходных уровней генератора и повторителя уровней фиксируется и остается неизменным, I/O ячейки продолжают принимать опорные уровни, соответствующие режиму основного источника питания, и ячейка продолжает корректную работу в режиме минимального токопотребления и может принимать входной инициализирующий сигнал низкой частоты, до 1 MHz. 3 ил.

Способ реализации режима с низким потреблением тока в спящем режиме для каскодной ячейки ввода-вывода, содержащей детектор питания, генератор опорных уровней, служебные ячейки ввода-вывода, повторитель опорных уровней, отличающийся тем, что в момент перехода в режим с низким потреблением мощности активируется инициализирующий сигнал SLEEP, одновременно транзистор Р1 отключает служебные ячейки от основного источника питания, транзистор Р2 подключает служебные ячейки к дополнительному источнику питания, детектор питания фиксирует режим дополнительного источника питания и переводит служебные ячейки в режим минимального токопотребления, при этом дополнительный источник питания имеет напряжение по меньшей мере 40%, и не превышающее 60% от напряжения основного источника, состояние выходных уровней генератора и повторителя уровней фиксируется и остается неизменным, I/O ячейки продолжают принимать опорные уровни, соответствующие режиму основного источника питания, и ячейка продолжает корректную работу в режиме минимального токопотребления и может принимать входной инициализирующий сигнал низкой частоты, до 1 MHz.

| Токарный резец | 1924 |

|

SU2016A1 |

| Забойный гидравлический домкрат | 1981 |

|

SU976021A1 |

| Колосоуборка | 1923 |

|

SU2009A1 |

| ДИНАМИЧЕСКОЕ УПРАВЛЕНИЕ НАПРЯЖЕНИЕМ И ЧАСТОТОЙ | 2010 |

|

RU2488875C2 |

| ЭЛЕКТРОННАЯ СХЕМА С КОНТРОЛЛЕРОМ И СПОСОБ УПРАВЛЕНИЯ ЭНЕРГИЕЙ | 2002 |

|

RU2271563C2 |

Авторы

Даты

2025-04-04—Публикация

2024-09-11—Подача