УРОВЕНЬ ТЕХНИКИ

ОБЛАСТЬ ТЕХНИКИ, К КОТОРОЙ ОТНОСИТСЯ ИЗОБРЕТЕНИЕ

Это изобретение относится к интегральными микросхемами и, более конкретно, к динамическому управлению напряжением и частотой в интегральной микросхеме.

ОПИСАНИЕ ПРЕДШЕСТВУЮЩЕГО УРОВНЯ ТЕХНИКИ

По мере роста числа транзисторов на одном "кристалле" интегральной микросхемы и по мере роста рабочей частоты интегральных микросхем продолжает расти важность управления мощностью, потребляемой интегральной микросхемой. Если потребляемая мощность не управляется, удовлетворить тепловым техническим требованиям для интегральной микросхемы (например, обеспечить компоненты, требуемые для достаточного охлаждения интегральной микросхемы во время работы, чтобы остаться в пределах рабочих температур интегральной микросхемы) может быть чрезмерно дорогостояще или даже неосуществимо. Кроме того, в некоторых применениях, таких как устройства c питанием от батарей, управление потребляемой мощностью в интегральной микросхеме может быть ключом к обеспечению приемлемого времени работы от батареи.

Потребляемая мощность в интегральной микросхеме связана с напряжением питания, обеспеченным для интегральной микросхемы. Например, многие цифровые логические схемы представляют двоичную единицу и двоичный нуль как напряжение питания и напряжение земли соответственно (или наоборот). По мере проведения вычислений дискретной логикой во время работы сигналы часто полностью переходят от одного напряжения к другому. Таким образом, мощность, потребляемая в интегральной микросхеме, зависит от величины напряжения питания относительно напряжения земли. Уменьшение напряжения питания в целом приводит к уменьшению потребляемой мощности, но также воздействует на скорость, с которой работают цифровые схемы, и таким образом может быть причиной неправильной работы на данной рабочей частоте (то есть частоте, на которой синхронизирована дискретная логика в интегральной микросхеме) или может уменьшить производительность.

Кроме того, поскольку размеры транзисторов продолжают уменьшаться, токи утечки, которые возникают, когда транзистор не проводит активно ток, стали большим компонентом мощности, потребляемой в интегральной микросхеме. Величина тока утечки, имеющего место в данном транзисторе, как правило, увеличивается линейно с увеличением напряжения питания. Кроме того, при каждом новом полупроводниковом производстве функциональных узлов (при котором уменьшаются размеры транзисторов), ток утечки увеличивается сильнее, чем активные (в состоянии ВКЛЮЧЕНО) токи. Таким образом, по мере использования более совершенных функциональных узлов, ток утечки становится все большей и большей проблемой.

Таким образом, потребляемой мощностью в интегральной микросхеме можно управлять посредством снижения напряжения питания интегральной микросхемы, однако результатом может стать неправильная работа, если напряжение питания снижено слишком сильно. Величина напряжения питания, при которой имеет место неправильная работа для данной рабочей частоты, изменяется от экземпляра к экземпляру для данного устройства интегральной микросхемы. Например, изменения в производственном процессе, используемом для производства интегральной микросхемы, и рабочая температура интегральной микросхемы могут воздействовать на величину напряжения питания, при которой происходит неправильная работа. Соответственно, попытки управлять потребляемой мощностью через напряжение питания были ограничены величинами напряжения питания, которые гарантируют корректную работу на данной частоте для всех допустимых отклонений в производственном процессе и всех допустимых рабочих температур. Как правило, напряжение питания для данной частоты статично указано в спецификации интегральной микросхемы.

СУЩНОСТЬ ИЗОБРЕТЕНИЯ

В варианте воплощения интегральная микросхема содержит логическую схему, локальное устройство управления электропитанием, связанное с логической схемой, и модуль самокалибровки. Локальное устройство управления электропитанием выполнено с возможностью передавать указание о запрошенной величине напряжения питания внешнему источнику питания. Модуль самокалибровки выполнен с возможностью выполнять тест логической схемы и повторять тест на соответственно более низкой запрошенной величине напряжения питания до тех пор, пока тест не приведет к сбою. Самая низкая запрошенная величина напряжения питания, на которой тест проходит успешно, используется для генерации требуемой величины напряжения питания для работы интегральной микросхемы.

В варианте воплощения способ содержит повторение теста логической схемы модулем самокалибровки на соответственно более низких требуемых величинах напряжения питания для интегральной микросхемы, которая включает в себя логическую схему и модуль самокалибровки, до тех пор, пока тест не приведет к сбою. Способ дополнительно содержит модуль самокалибровки, который определяет самую низкую требуемую величину напряжения питания, на которой тест проходит успешно. Еще способ дополнительно содержит модуль самокалибровки, выбирающий самую низкую запрошенную величину напряжения питания для генерации запрошенной величины напряжения питания для работы интегральной микросхемы.

В варианте воплощения интегральная микросхема содержит множество логических вентилей, физически распределенных по участку интегральной микросхемы, который занят логической схемой, которая реализует действие интегральной микросхемы, где множество логических вентилей соединено последовательно; а модуль измерений соединен с первым вентилем в последовательном соединении и последним вентилем в последовательном соединении. Модуль измерений выполненный с возможностью запуска логического перехода в первый вентиль и измерения времени, когда соответствующий переход обнаружен в последнем вентиле. Измеренное время сравнивается с заранее заданным временем для регулировки напряжения питания интегральной микросхемы. В некоторых вариантах воплощения заранее заданное время может быть определено во время процедуры самокалибровки. В некоторых вариантах воплощения заранее заданное время может быть измерено как число тактов, которое требуется импульсу для прохождения через все последовательно включенные логические вентили.

В варианте воплощения способ содержит модуль измерений, который запускает логический переход в первый вентиль последовательного соединения множества логических вентилей, которые физически распределены по участку интегральной микросхемы, которая занята логической схемой, которая реализует действие интегральной микросхемы; и модуль измерений, который измеряет время, когда соответствующий переход обнаружен в последнем вентиле, и при этом измеренное время сравнивается с заранее заданным временем для регулировки напряжение питания интегральной микросхемы.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

Последующее подробное описание ссылается на сопроводительные чертежи, которые теперь будут кратко описаны.

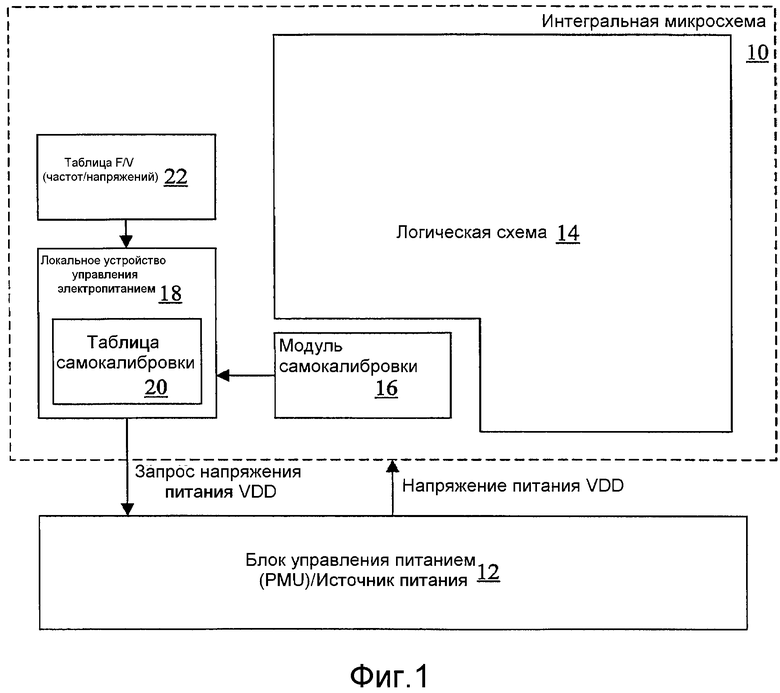

Фиг.1 является блок-схемой одного варианта воплощения интегральной микросхемы.

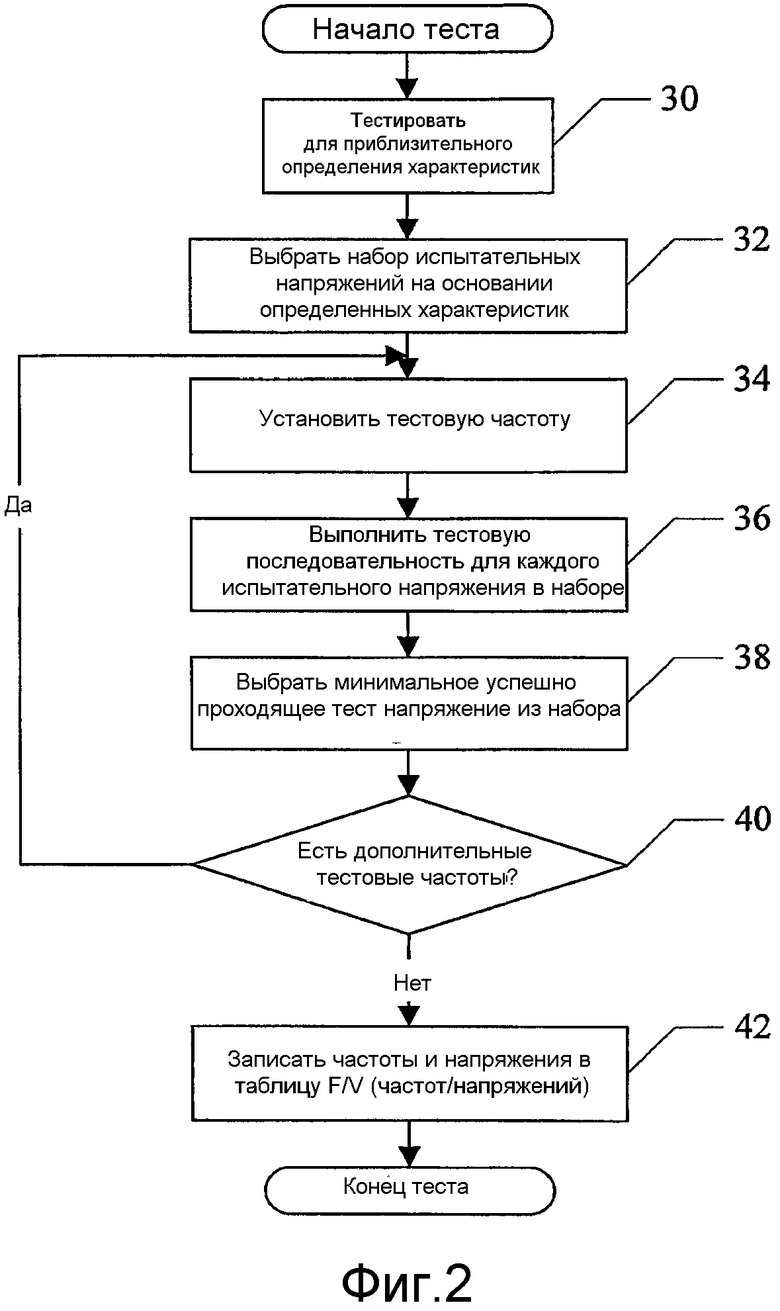

Фиг.2 является блок-схемой последовательности операций, которая изображает один вариант воплощения теста интегральной микросхемы, показанной на фиг.1.

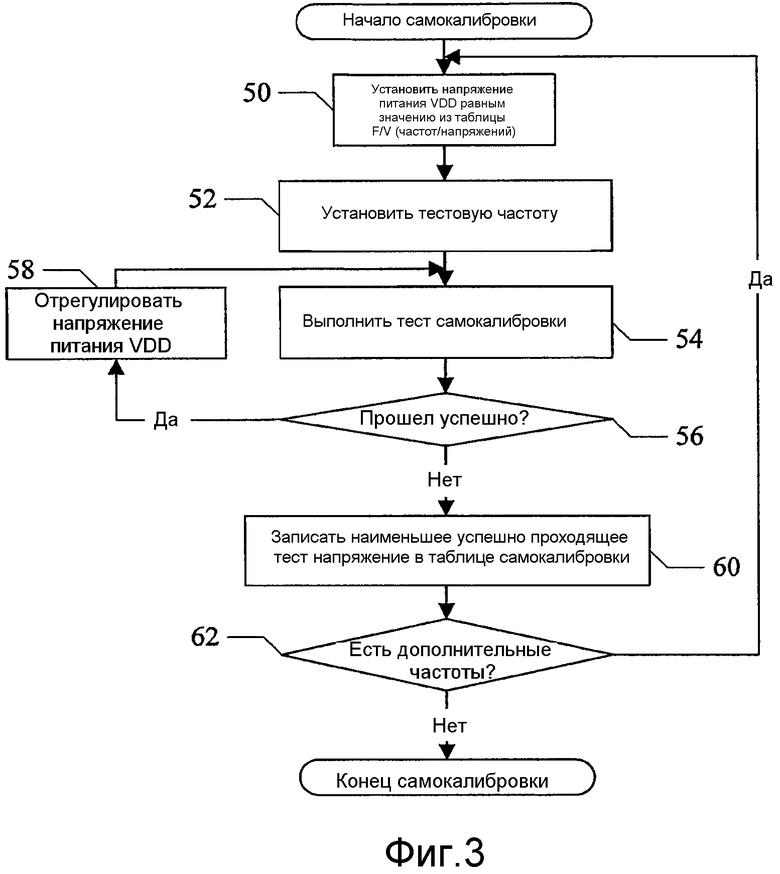

Фиг.3 является блок-схемой последовательности операций, которая изображает работу одного варианта воплощения модуля самокалибровки, показанного на фиг.1.

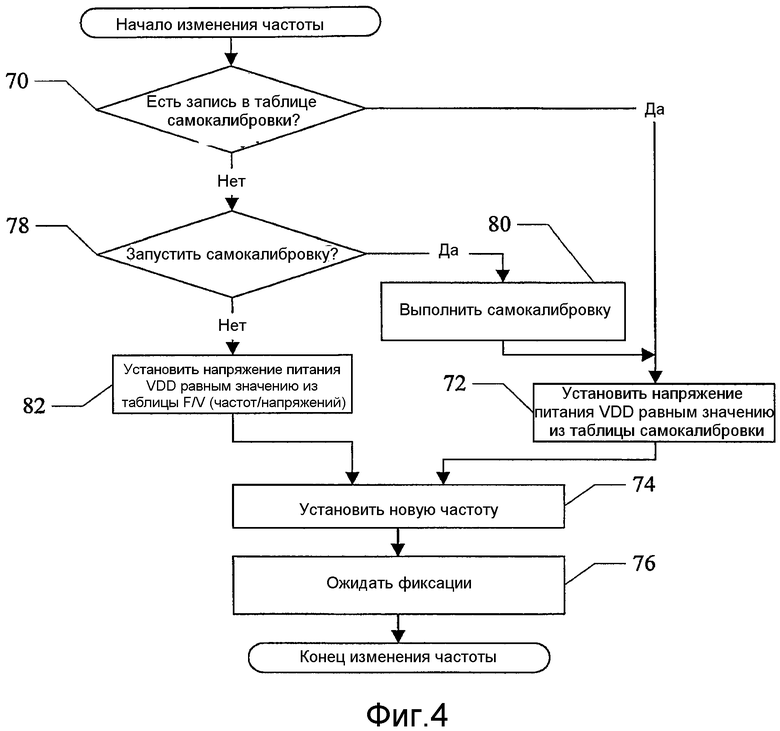

Фиг.4 является блок-схемой последовательности операций, которая изображает работу одного варианта воплощения интегральной микросхемы, показанной на фиг.1, по изменению частоты работы интегральной микросхемы.

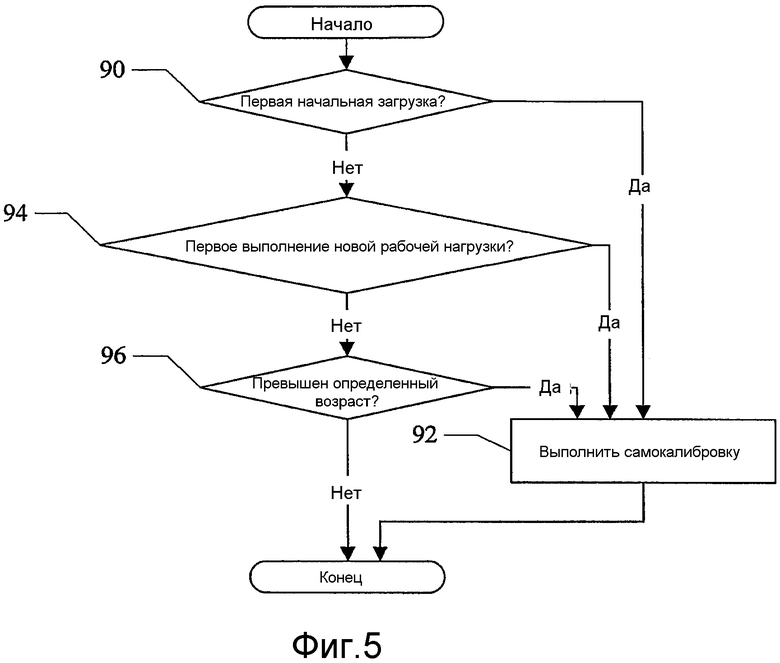

Фиг.5 является блок-схемой последовательности операций, которая изображает для одного варианта воплощения выполнение самокалибровки в ответ на различные события.

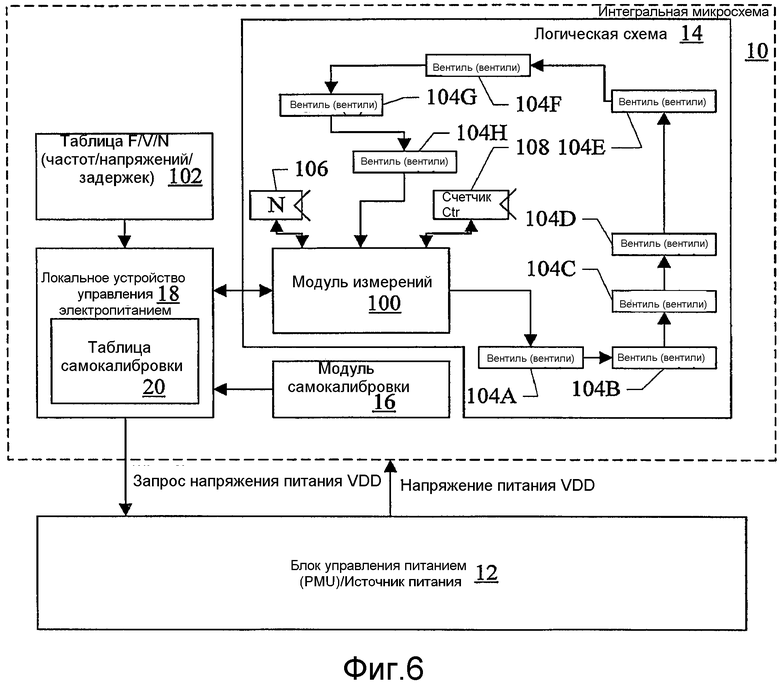

Фиг.6 является блок-схемой другого варианта воплощения интегральной микросхемы.

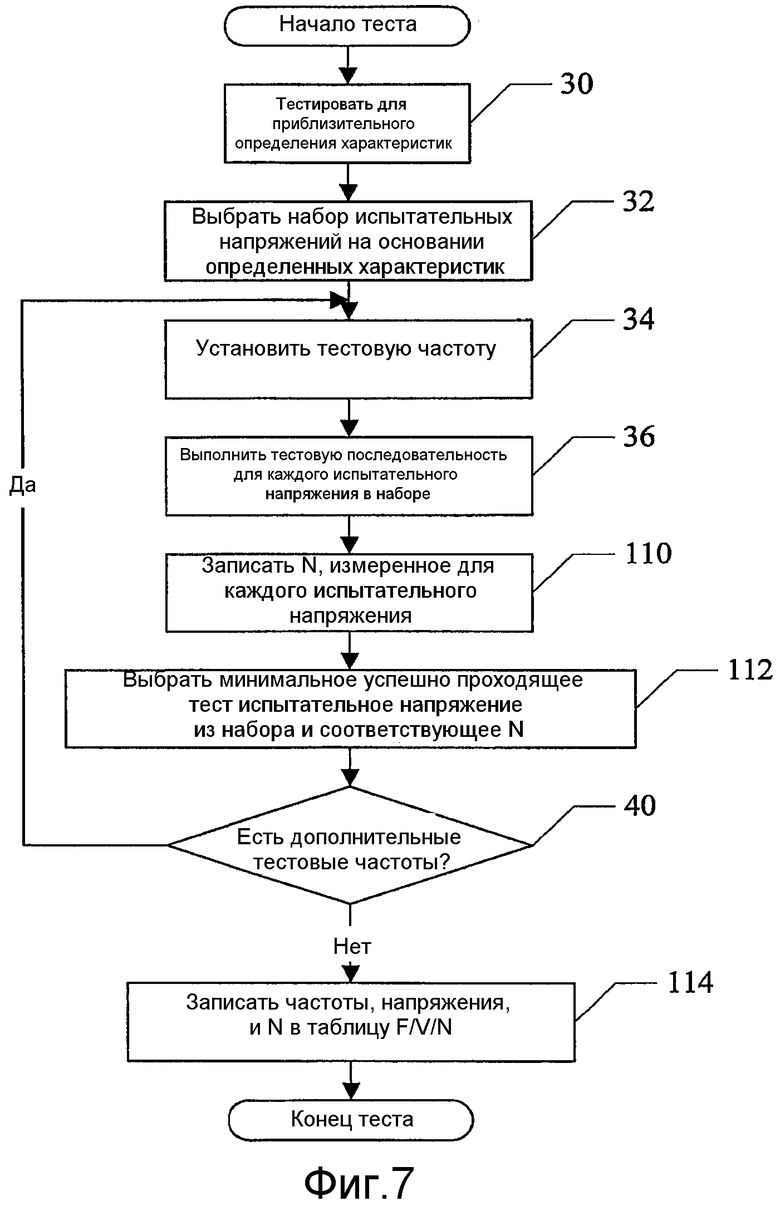

Фиг.7 является блок-схемой последовательности операций, которая изображает один вариант воплощения теста интегральной микросхемы, показанной на фиг.6.

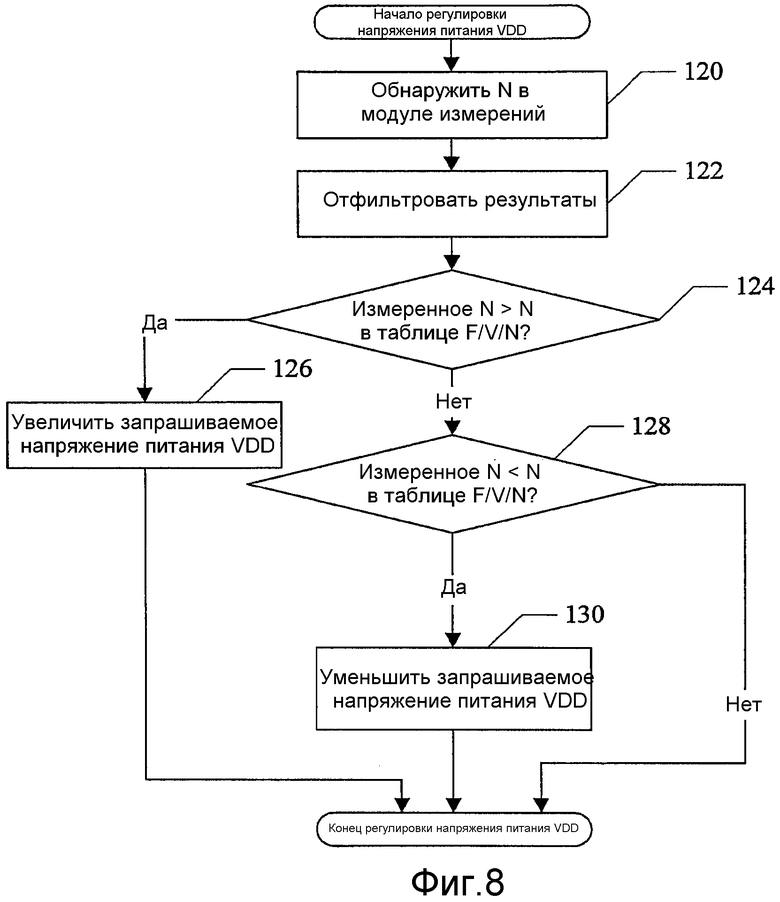

Фиг.8 является блок-схемой последовательности операций, которая изображает работу одного варианта воплощения интегральной микросхемы по запросу напряжения питания.

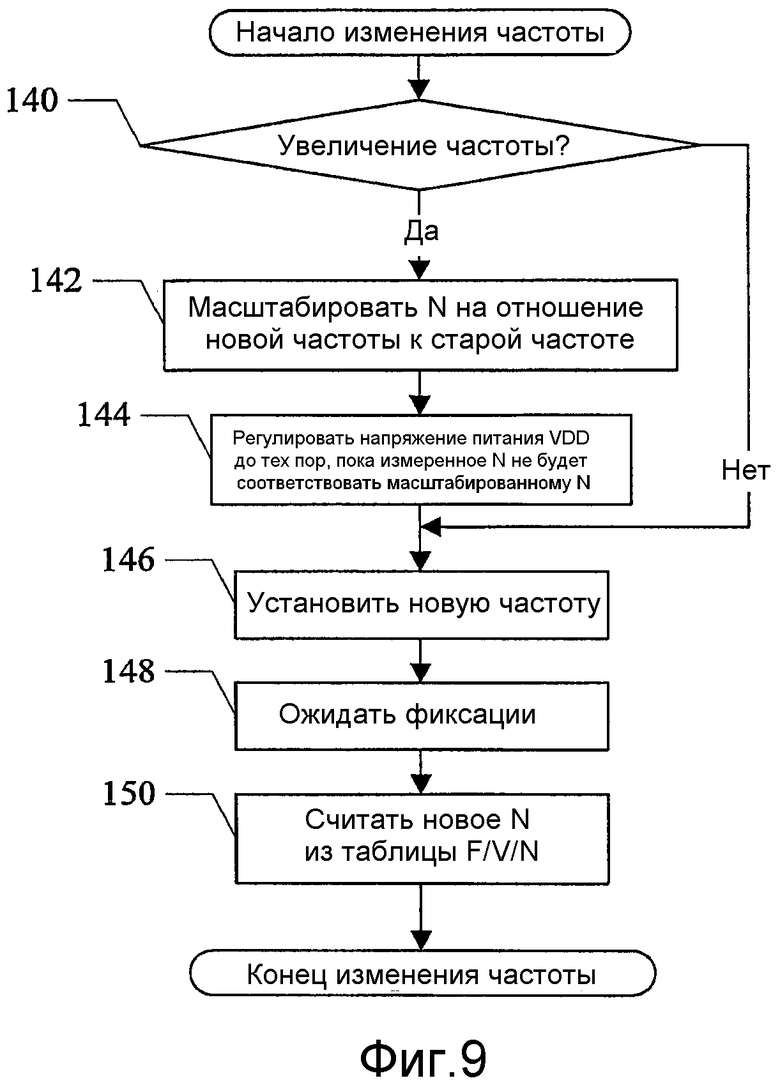

Фиг.9 является блок-схемой последовательности операций, которая изображает работу одного варианта воплощения интегральной микросхемы, показанного на фиг.6, по изменению частоты работы интегральной микросхемы.

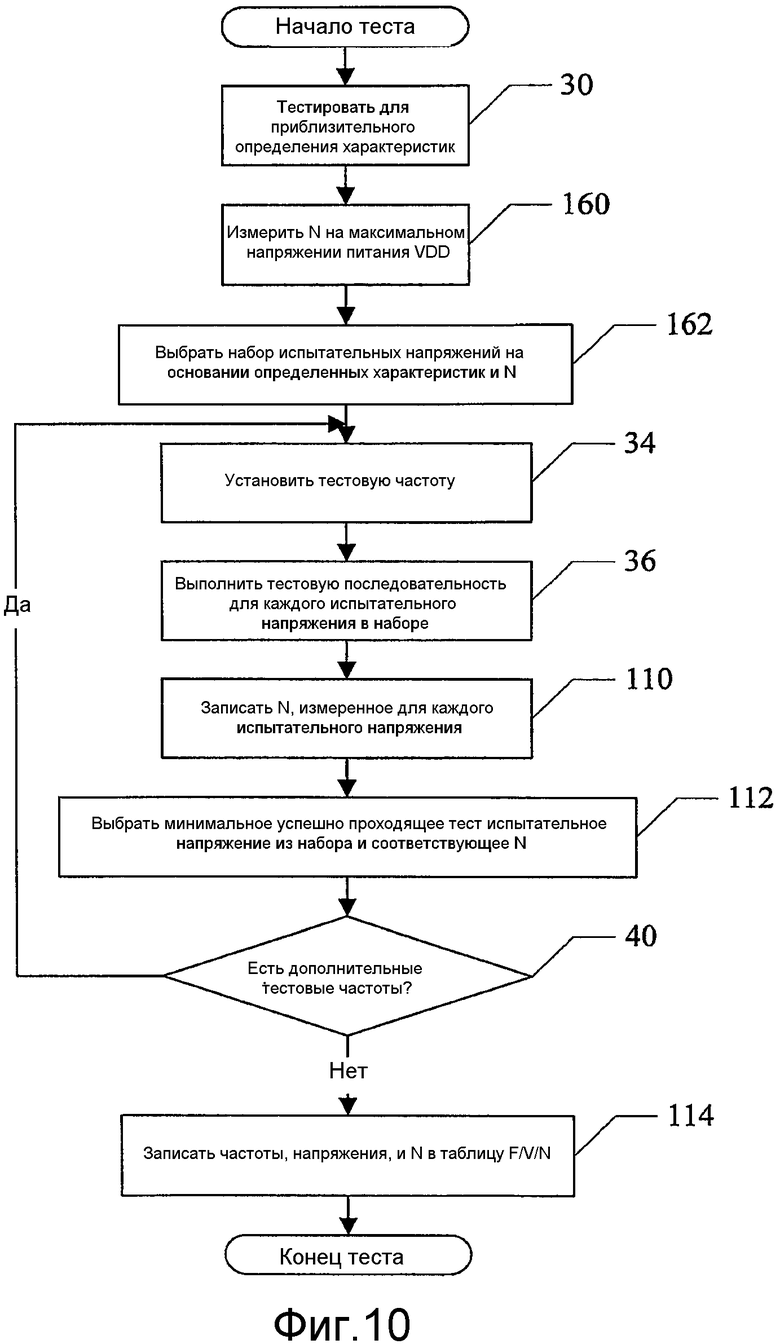

Фиг.10 является блок-схемой последовательности операций, которая изображает другой вариант воплощения теста интегральной микросхемы, показанной на фиг.6.

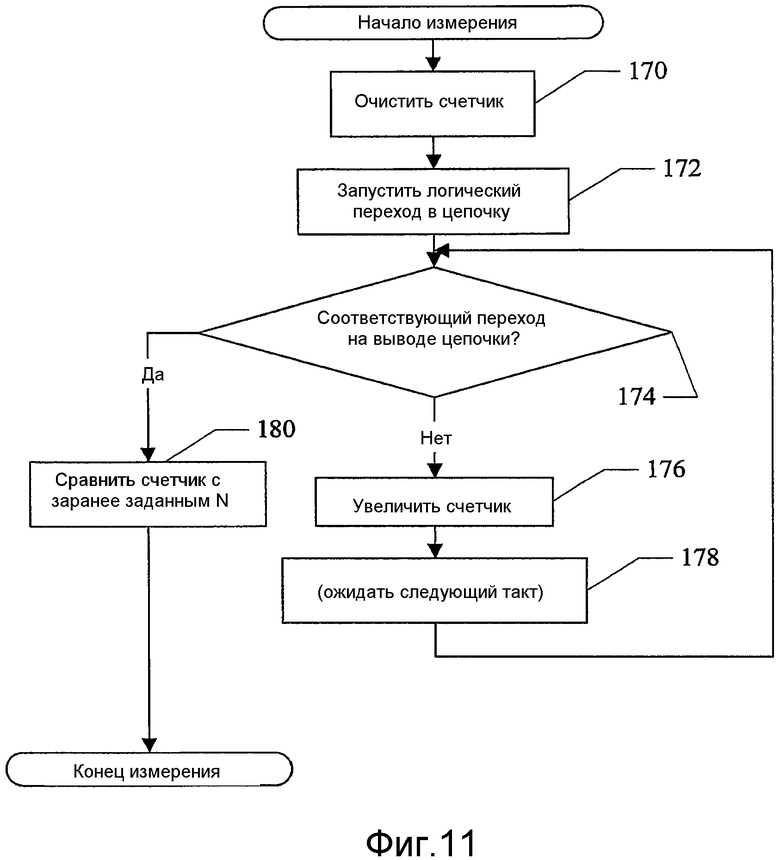

Фиг.11 является блок-схемой последовательности операций, которая изображает работу одного варианта воплощения модуля компенсации скорости/температуры, показанного на фиг.6.

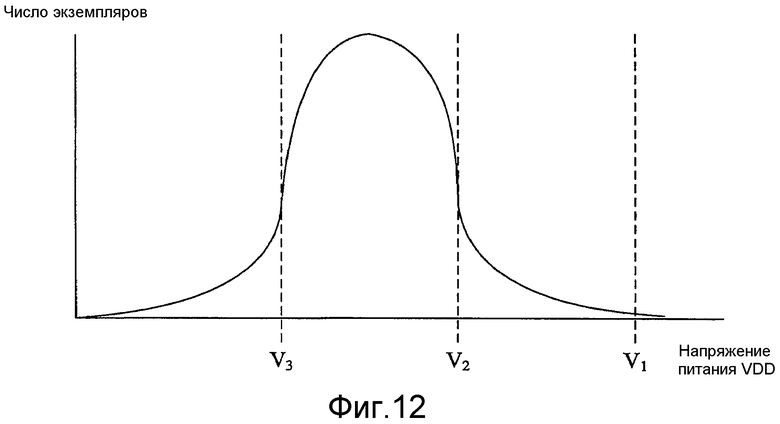

Фиг.12 является графическим изображением числа экземпляров, которые могут действовать при различных напряжениях питания, и тестовых напряжений, которые могут использоваться в одном варианте воплощения тестирования интегральной микросхемы.

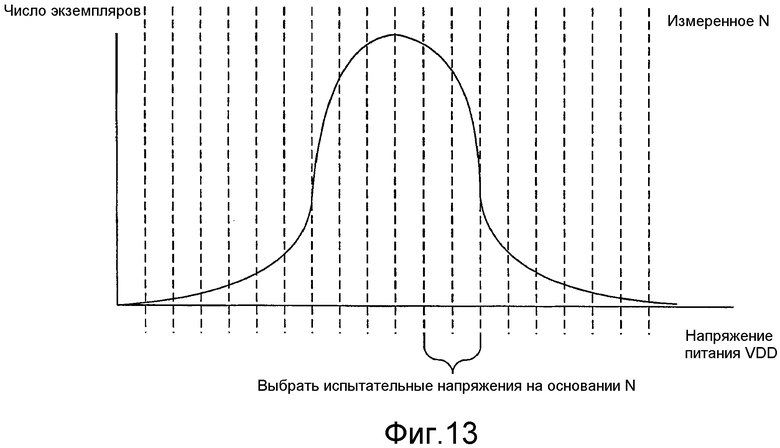

Фиг.13 является графическим изображением числа экземпляров, которые могут действовать при различных напряжениях питания, и тестовых напряжений, которые могут использоваться в другом варианте воплощения тестирования интегральной микросхемы.

Хотя изобретение допускает различные изменения и альтернативные формы, его конкретные варианты воплощения показаны в качестве примера на чертежах, и они будут подробно описаны в настоящем документе. Однако следует понимать, что чертежи и подробное описание к ним не ограничивают изобретение определенной раскрытой разновидностью, напротив, намерение состоит в том, чтобы охватить все модификации, эквиваленты и варианты, находящиеся в пределах существа и объема данного изобретения, заданными в прилагаемой формуле изобретения. Заголовки, используемые в настоящем документе, служат только для организационных целей и не предназначены для ограничения объема описания. Повсюду в настоящей заявке слово "может" используется в разрешительном смысле (то есть означающем наличие потенциала для чего-то), а не обязывающем смысле (то есть означающем необходимость). Точно так же слова "включают в себя", "включая в себя" и "включает в себя" означает включение в себя, а не ограничение чем-то.

Различные модули, схемы или другие компоненты могут быть описаны как "выполненные с возможностью" выполнять задачу или задачи. В таких контекстах "выполненный с возможностью" является широким прочтением конструкции, в целом означающей "имеет электрическую схему, которая" выполняет задачу или задачи во время работы. Таким образом, модуль/схема/компонент может быть выполненным с возможностью выполнять задачу даже когда модуль/схема/компонент в настоящий момент не включен. Вообще, электрическая схема, которая формирует структуру, соответствующую "выполненному с возможностью", может включать в себя аппаратные схемы и/или сохраненные в памяти исполняемые инструкции программы для реализации операции. Память может включать в себя кратковременную память, такую как статическая или динамическая оперативная память и/или энергонезависимую память, такую как запоминающее устройство на оптических или на магнитных дисках, флэш-память, программируемые постоянные запоминающие устройства (ПЗУ) и т.д. Аналогично различные модули/схемы/компоненты могут быть описаны как выполняющие задачу или задачи для удобства в описании. Такие описания должны интерпретироваться как включающие фразу "выполненные с возможностью". Описание модуля/схемы/компонента, который выполнен с возможностью выполнять одну или более задач, однозначно не предусматривает интерпретацию этого модуля/схемы/компонента согласно абзацу шесть 35 U.S.C. § 112 Свода законов США.

ПОДРОБНОЕ ОПИСАНИЕ ВАРИАНТОВ ВОПЛОЩЕНИЯ

Обращаясь теперь к фиг.1, показана блок-схема одного варианта воплощения интегральной микросхемы 10, связанной с внешним блоком управления питанием (PMU)/источником 12 питания. В изображенном варианте воплощения интегральная микросхема 10 включает в себя логическую схему 14, модуль 16 самокалибровки, локальное устройство 18 управления электропитанием (которое может включать в себя таблицу 20 самокалибровки) и таблицу 22 частоты/напряжения (F/V). Модуль 16 самокалибровки и таблица 22 F/V связаны с локальным устройством 18 управления электропитанием, которое связано с блоком PMU/источником 12 питания для передачи указания о запрошенной величине напряжения питания (запрос VDD). Блок PMU/источник 12 питания связан с интегральной микросхемой 10 для обеспечения напряжения питания (VDD) требуемой величины. Компоненты, изображенные в пределах интегральной микросхемы 10, интегрированы на одной полупроводниковой подложке или кристалле.

Обычно модуль 16 самокалибровки содержит электрическую схему управления наряду с тестом, который должен быть выполнен логической схемой 14. Тест может быть предназначен для отработки известных "критических" хронометражных маршрутов в логической схеме 14. Критический хронометражный маршрут может быть маршрутом через электрическую схему, которая, как ожидается, покажет самую высокую задержку (по сравнению с другими хронометражными маршрутами) от входного перехода до соответствующего выходного перехода, и таким образом будет маршрутом, который ограничивает рабочую частоту, на которой логическая схема 14 будет работать правильно. Природа теста может меняться в зависимости от определения логической схемы 14. Например, если логическая схема 14 включает в себя одно или более ядер процессора, тест может содержать программу, которая должна быть выполнена ядром (ядрами) процессора, наряду с ожидаемым результатом программы (например, подпись). Если логическая схема 14 включает в себя электрическую схему стандартной функции, тест может содержать значения входного сигнала и ожидаемые значения выходного сигнала. В различных вариантах воплощения может быть включена комбинация значений сигнала и инструкций программы.

Электрическая схема в модуле 16 самокалибровки может быть выполнена с возможностью выполнения теста на логической схеме 14 (например, предоставляя инструкции ядру (ядрам) процессора для выполнения и/или управляя сигналами с помощью значений входного сигнала). Электрическая схема в модуле самокалибровки может также быть выполнена с возможностью проверки результата посредством сравнения с ожидаемым значением. Модуль 16 самокалибровки может быть выполнен с возможностью повторения теста и обмена информацией с локальным устройством 18 управления электропитанием для запроса более низких величин напряжения питания для каждого повтора, пока не будет обнаружен неверный результат для повтора. Самая низкая величина напряжения питания, для которой обнаружен корректный результат теста, может быть обеспечена в качестве запрашиваемой величины напряжения питания (или может быть прибавлен некоторый припуск к самой низкой величине напряжения питания, чтобы получить величину, которая будет запрашиваться). Модуль 16 самокалибровки может повторять тест для каждой возможной рабочей частоты или может выполнять тест для данной рабочей частоты в ответ на первый фактический запрос данной рабочей частоты для интегральной микросхемы 10 (например, программным обеспечением).

При использовании модуля 20 самокалибровки в некоторых вариантах воплощения может использоваться меньший припуск, так как самокалибровка происходит с интегральной микросхемой 10, установленной в конкретное устройство, в котором оно будет использоваться (и таким образом некоторые факторы, которые учитываются с помощью припуска, такие как вариации в источнике 12 питания, конструкции платы, монтаже интегральной микросхемы 10 в корпусе, и т.д. в общем и целом устраняются). Кроме того, в некоторых вариантах воплощения вместо того, чтобы тестировать на самое низкое напряжение питания на этапе заводской проверки, в это время могут тестироваться меньшие величины напряжения питания, и таким образом время заводской проверки может быть уменьшено. Кроме того, в некоторых вариантах воплощения модуль 16 самокалибровки может быть активирован в любое время, таким образом автоматически проводя регулировки для учета эффекта старения в интегральной микросхеме 10.

В одном варианте воплощения локальное устройство 18 управления электропитанием может сохранять получающиеся величины напряжения питания, предоставленные модулем 16 самокалибровки, в таблице 20 самокалибровки. Таблица 20 самокалибровки может быть оперативной памятью, синхронными запоминающими устройствами, такими как регистры, или любой другой кратковременной памятью. В соответствии с другим вариантом воплощения может использоваться долговременная память, такая как программируемое ПЗУ, флэш-память, и т.д. После этого, если в таблице 20 самокалибровки обнаруживается запись для данной рабочей частоты, величина напряжения питания, записанная в записи, может быть затребована локальным устройством 18 управления электропитанием.

Таблица 22 F/V может содержать множество записей, в каждой содержится соответствующая рабочая частота для интегральной микросхемы 10 и соответствующая величина напряжения питания для этой частоты. Частота работы может быть частотой генератора тактовых импульсов, которым снабжены синхронные запоминающие устройства в логической схеме 14. Может иметься ряд частот, на которых интегральная микросхема 10 может работать (а переключение между частотами в этом ряду может поддерживаться интегральной микросхемой 10, например, чтобы позволить управление питанием, управление температурой и т.д.). Таблица 22 F/V может быть статической таблицей, записанной во время заводской проверки интегральной микросхемы 10 (например, до монтажа интегральной микросхемы в корпусе, например, во время теста полупроводниковой пластины). В других вариантах воплощения тест может быть выполнен в любой момент до продажи интегральной микросхемы 10 для установки в устройство, или до установки интегральной микросхемы 10 в таком устройстве, в других вариантах воплощения, таблица 22 F/V может быть записана во время самокалибровки, которая может быть выполнена до первого использования устройства, в том числе интегральной микросхемы 10. Таким образом, величина напряжения питания, определенная для каждой частоты в таблице 22 F/V, может иметь соответствующий значительный предохранительный интервал напряжения, чтобы гарантировать корректную работу в случае, когда электрические характеристики корпуса изменяют величину напряжения, чтобы учесть изменение температур (например, тест может быть выполнен при регулируемой температуре, а рабочая температура может быть более высокой или низкой, чем эта температура), чтобы учесть эффекты старения в интегральной микросхеме в течение ее предполагаемого срока эксплуатации и т.д.

Локальное устройство 18 управления электропитанием содержит электрическую схему, которая выполнена с возможностью запрашивать величину напряжения питания от внешнего источника питания (например, блока PMU/источника 12 питания). Как упоминалось ранее, если в таблице 20 самокалибровки обнаружена запись для данной рабочей частоты, локальное устройство 18 управления электропитанием может запросить величину напряжения питания, записанную в той записи. Если никакая запись не найдена в таблице 20 самокалибровки, локальное устройство 18 управления электропитанием может прочитать таблицу 22 F/V для данной рабочей частоты и может запросить эту величину напряжения питания от блока PMU/источника 12 питания (запрос VDD на фиг.1). Запрос может быть представлен в любой желаемой форме. Например, запрос может содержать множество бит, а различным величинам напряжения питания в пределах диапазона поддерживаемых величин присвоен различный код из множества бит.

Локальное устройство 18 управления электропитанием может также быть выполнено с возможностью управления сменой рабочих частот. Например, локальное устройство 18 управления электропитанием может содержать регистр или другое средство, в которое программное обеспечение может делать записи для выбора новой рабочей частоты. Локальное устройство 18 управления электропитанием может обнаружить факт записи и может управлять переходом с текущей рабочей частоты на вновь запрошенную рабочую частоту. Переход может включать в себя изменение запрашиваемого напряжения питания, изменение работы электрической схемы синхронизации (например, повторную синхронизацию системы фазовой автоподстройки частоты (PLL), которая генерирует тактовые импульсы в интегральной микросхеме 10, и т.д.), и т.д. Таким образом, в одном варианте воплощения подробности перехода могут быть отделены от программного обеспечения, которое может просто запросить новую частоту и продолжить работу (например, даже без проверки факта завершения перехода).

Таблица 22 F/V может быть записана в любой желаемой форме. Например, каждая запись в таблице может содержать плавкие предохранители, которые могут быть выборочно расплавлены, чтобы постоянным образом сохранить в записи показание требуемой величины напряжения (например, закодированное как множество бит в записи). В других вариантах воплощения может использоваться любое другое энергонезависимое запоминающее устройство. Таблица 22 F/V может содержать энергонезависимую память, в которую можно записывать посредством обновления встроенного микропрограммного обеспечения устройства, которое включает в себя интегральную микросхему 10.

В некоторых вариантах воплощения тест, который выполняется модулем 16 самокалибровки, может быть программируемым и обновляемым. Такие варианты воплощения могут позволять изменение теста по мере того, как становится доступно больше данных. Например, маршрут, отличный от ранее идентифицированных критических маршрутов, может доминировать или сильно влиять на напряжение питания, на котором интегральная микросхема 10 работает правильно. Тест может быть обновлен для учета недавно обнаруженного критического маршрута. Более того, в некоторых вариантах воплощения тест может быть обновлен для включения в него более подходящей программы для выполнения во время теста.

Обычно логическая схема 14 может включать в себя электрическую схему, которая реализует действие, для которого предназначена интегральная микросхема 10. Например, если конструкция включает в себя один или более процессоров, логическая схема 14 может включать в себя электрическую схему, которая реализует действия процессора (например, вызов команды, декодирование, выполнение и запись результата). Процессоры могут содержать универсальные процессоры и/или графические процессоры в различных вариантах воплощения. Если конструкция включает в себя устройство сопряжения с периферийным интерфейсом, то логическая схема 14 может включать в себя электрическую схему, которая реализует действия устройства сопряжения. Если конструкция содержит другие коммуникационные возможности, такие как пакетные интерфейсы, сетевые интерфейсы и т.д., логическая схема 14 может содержать электрическую схему, реализующую соответствующие возможности. Вообще интегральная микросхема 10 может предназначаться для обеспечения любого набора действий. Обычно логическая схема 14 может содержать любую комбинацию одного или более элементов из следующих: массив памяти, комбинаторная логика, конечные автоматы, триггеры, регистры, другие синхронные запоминающие устройства, специализированные логические схемы, и т.д.

Обычно блок PMU/источник 12 питания может содержать любую электрическую схему, которая способна генерировать величину напряжение питания, указанную в запросе входного напряжения. Например, электрическая схема может содержать один или более стабилизаторов напряжения или другие источники энергии. Блок PMU/источник 12 питания может также содержать электрическую схему управления питанием для системы (которая содержит интегральную микросхему 10) как целого.

Хотя в обсуждении выше упоминалось о запросе величины напряжения питания и о предоставлении блоком PMU/источником 12 питания напряжения запрошенной величины, в обсуждении не подразумевалось, что есть только одно запрашиваемое/подаваемое напряжение. Может иметься множество напряжений питания, которые запрашиваются и подаются в любой данный момент времени. Например, могут иметься отдельные напряжения питания для комбинаторной логической электрической схемы и для электрической схемы памяти в логической схеме 14. Может иметься множество областей напряжения в пределах интегральной микросхемы 10, которые могут включаться и выключаться по отдельности, и каждая область может включать в себя отдельный запрос. Локальное устройство 18 управления электропитанием может питаться отдельно от логической схемы 14. Любое множество из одного или более напряжений питания может запрашиваться и подаваться.

Величина напряжения питания упоминалась выше как запрашиваемая, а напряжение питания запрашиваемой величины как подаваемое. Величина напряжения питания может измеряться относительно опорного напряжения (например, напряжения земли интегральной микросхемы 10, иногда именуемого как VSS). Для удобства нижеследующего описания напряжения могут упоминаться как являющиеся большими или меньшими, чем другие напряжения. Аналогично в настоящем документе может упоминаться измерение напряжения, в таких случаях имеется в виду, что это величина напряжения больше чем (или меньше чем) другое напряжение или то, что измерено.

Обращаясь теперь к фиг.2, показана блок-схема последовательности операций, которая изображает один вариант воплощения тестирования интегральной микросхемы 10, показанной на фиг.1, до монтажа интегральной микросхемы в корпусе. Блоки, показанные на фиг.2, могут выполняться на установке для испытаний (например, приборе для проверки полупроводниковой пластины) во время производства интегральной микросхемы 10.

Тест может начинаться с тестирования для приблизительного определения характеристик интегральной микросхемы 10 (блок 30), используя различные измерения для оценки, является ли интегральная микросхема относительно быстрой, относительно медленной, и т.д. Например, в одном варианте воплощения приблизительное определение характеристик может включать в себя тестирование входного тока интегральной микросхемы 10, в то время как интегральная микросхема 10 находится в установившемся режиме (часто называемое тестированием на отклонения тока в установившемся режиме ("Iddq" тестированием)). Более высокие результаты измерений Iddq могут указывать на более высокую утечку (например, "более быстрый" процесс). Более низкие результаты измерений Iddq могут указывать на более низкую утечку (например, "более медленный" процесс). Iddq тестирование может быть выполнено, например, с максимальным напряжением питания, допустимому для интегральной микросхемы 10. Из приблизительного определения характеристик (и из предыдущих результатов тестирования экземпляров интегральной микросхемы 10), может быть выбран относительно небольшой набор тестовых напряжений питания. То есть на основании напряжений питания, которые обеспечивают надежную работу на предыдущих экземплярах, имеющих похожие приблизительные характеристики, может быть выбрано лишь небольшое количество испытательных напряжений (блок 32). Например, в одном варианте воплощения может быть выбран набор из трех испытательных напряжений. Фиг.12 является графическим изображением распределения экземпляров от быстрого процесса (левая сторона фиг.12) до медленного процесса (правая сторона фиг.12). Как изображено на фиг.12, испытательные напряжения для одного примера могут быть V1, V2 и V3.

Установка для испытаний может включить питание интегральной микросхемы 10 (например, с самым высоким из испытательных напряжений) и может установить тестовую частоту (одна из частот, на которых поддерживается работа интегральной микросхемы 10 - блок 34). Установка для испытаний может выполнять одну или более тестовых последовательностей на интегральной микросхеме 10 для каждого напряжения из множества испытательных напряжений (блок 36) и может выбрать самое низкое испытательное напряжение, для которого все тестовые последовательности проходят успешно (то есть достигнут правильный результат для каждой последовательности - блок 38). Если имеются дополнительные тестовые частоты (например, дополнительные поддерживаемые рабочие частоты для интегральной микросхемы 10, которые еще не были протестированы - блок 40 ветвления, ответвление "да"), то может выбираться и тестироваться следующая частота (блоки 34, 36 и 38). Набор испытательных напряжений может содержать различные напряжения для тестирования для каждой поддерживаемой рабочей частоты, или может выбираться так, чтобы для каждой поддерживаемой рабочей частоты ожидалось по меньшей мере одно напряжение питания, успешно проходящее тесты. Как только тестовые частоты исчерпаны (блок 40 ветвления, ответвление "нет"), установка для испытаний может записывать частоты и величины напряжения в таблицу 22 F/V (блок 42). Например, плавкие предохранители могут быть расплавлены для отображения поддерживаемых частот и соответствующих величин напряжения питания.

Так как число испытательных напряжений ограничено, процесс тестирования, возможно, не определит самое низкое напряжение питания, которое приводит к корректной работе определенного экземпляра интегральной микросхемы 10. Однако время на установке для испытаний может быть ограничено, что может быть важным вообще и особенно если ожидаются большие объемы производства интегральной микросхемы 10.

Обращаясь теперь к фиг.3, блок-схема изображает работу одного варианта воплощения модуля 16 самокалибровки (и локального устройства 18 управления электропитанием) по выполнению самокалибровки. Самокалибровка может быть выполнена неоднократно, как обсуждается более подробно ниже. Хотя блоки показаны в определенном порядке для простоты понимания, могут использоваться иные порядки расположения. Блоки могут выполняться параллельно в комбинаторной логической электрической схеме в модуле 16 самокалибровки и/или локальном устройстве 18 управления электропитанием. Блоки, комбинации блоков и/или блок-схема последовательности операций в целом могут исполняться конвейерным образом за множество тактов.

Модуль 16 самокалибровки может обмениваться информацией с локальным устройством 18 управления электропитанием для указания, что выполняется процесс самокалибровки. В соответствии с другим вариантом воплощения локальное устройство 18 управления электропитанием может инициировать процесс самокалибровки и может таким образом знать, что идет процесс самокалибровки. В любом случае локальное устройство 18 управления электропитанием может запросить величину напряжения питания, которая предоставлена в таблице 22 F/V для тестовой частоты (блок 50). Каждая рабочая частота, которая поддерживается интегральной микросхемой 10, может быть тестовой частотой, например, начиная с самой низкой частоты. Локальное устройство 18 управления электропитанием может установить тестовую частоту (блок 52) и может ожидать, пока интегральная микросхема стабилизируется на тестовой частоте (например, время синхронизации системы фазовой автоподстройки частоты (PLL) и/или время установления для напряжения от блока PMU/источника 12 питания). Модуль 16 самокалибровки может выполнить тест самокалибровки (блок 54) и определить, выдает ли логическая схема 14 верный результат (пройден) или нет (сбой) (блок ветвления 56). Если тест проходит успешно (блок ветвления 56, ответвление "да"), модуль 16 самокалибровки может сообщить это локальному устройству 18 управления электропитанием, который может запросить следующее более низкое напряжение питания (блок 58), и тест может быть выполнен снова (блоки 54 и 56). Тест может повторяться, пока для теста не обнаружен неудачный результат (блоки 54, 56 и 58). Как только обнаружен сбой (блок ветвления 56, ответвление "нет"), локальное устройство 18 управления электропитанием может записать величину самого низкого успешно проходящего напряжения питания в таблице 20 самокалибровки (блок 60). В некоторых вариантах воплощения может быть прибавлен припуск к самому низкому успешно проходящему тест напряжению питания, чтобы получить величину напряжения, которая будет записана в таблице самокалибровки. В соответствии с другим вариантом воплощения, припуск может быть прибавлен при запросе напряжения питания. Если есть дополнительные тестовые частоты, на которых необходимо провести самокалибровку (блок ветвления 62, ответвление "да"), то процесс самокалибровки возвращается к блоку 50 для следующей частоты. В противном случае (блок ветвления 62, ответвление "нет") процесс самокалибровки заканчивается.

Обращаясь теперь к фиг.4, показана блок-схема последовательности операций, которая изображает работу одного варианта воплощения локального устройства 18 управления электропитанием в ответ на запрос по изменению рабочей частоты (например, от программного обеспечения, выполняющегося на интегральной микросхеме 10 или в другом месте в системе, которая содержит интегральную микросхему 10). Хотя блоки показаны в определенном порядке для простоты понимания, могут использоваться иные порядки расположения. Блоки могут выполняться параллельно в комбинаторной логической электрической схеме в локальном устройстве 18 управления электропитанием. Блоки, комбинации блоков и/или блок-схема последовательности операций в целом могут исполняться конвейерным образом за множество тактов.

Локальное устройство 18 управления электропитанием может проверить таблицу 20 самокалибровки на наличие записи, соответствующую новой (запрошенной) рабочей частоте (блок ветвления 70). Если запись найдена (блок ветвления 70, ответвление "да") локальное устройство 18 управления электропитанием может запросить напряжение питания величины, обозначенной в таблице 20 самокалибровки (блок 72). Локальное устройство 18 управления электропитанием может установить новую рабочую частоту (блок 74) и может в некоторых случаях в зависимости от реализации ожидать, пока электрическая схема зафиксируется на новой рабочей частоте (блок 76). С другой стороны, если нет никакой записи в таблице 20 самокалибровки для запрошенной частоты (блок ветвления 70, ответвление "нет"), то локальное устройство 18 управления электропитанием может определить, должна ли быть выполнена самокалибровка для требуемой частоты (блок ветвления 78). Например, блок-схема последовательности операций фиг.3 может быть выполнена с запрошенной частотой как единственной тестовой частотой. Факторы, которые могут влиять на то, выполнять ли самокалибровку во время изменения частоты, могут включать в себя текущую рабочую нагрузку логической схемы 14, общую обстановку в системе (например, температуру, оставшееся время работы от батареи и т.д.). Например, если логическая схема 14 содержит много ядер процессора, и одно из ядер неактивно, самокалибровка может быть выполнена на неактивном ядре процессора. Если система работает на заряде батареи и оставшееся время работы от батареи невелико, выполнение самокалибровки может потратить заряда батареи больше, чем желательно.

Если локальное устройство 18 управления электропитанием решает, что самокалибровка должна быть выполнена (блок ветвления 78, ответвление "да"), то локальное устройство 18 управления электропитанием может вызвать модуль самокалибровки 16 для выполнения самокалибровки (блок 80). Локальное устройство 18 управления электропитанием может тогда запросить напряжение питания, обозначенное в таблице 20 самокалибровки (после завершения самокалибровки - блок 72), установить новую рабочую частоту (блок 74) и в некоторых случаях ожидать фиксации частоты (блок 76).

Если локальное устройство 18 управления электропитанием решает, что самокалибровка не должна быть выполнена (блок ветвления 78, ответвление "нет"), то локальное устройство 18 управления электропитанием может считать таблицу 22 F/V для получения величины напряжения питания и может запросить эту величину напряжения питания (блок 82). Локальное устройство 18 управления электропитанием может установить новую частоту, и в некоторых случаях ожидать фиксации частоты (блок 74 и 76).

В варианте воплощения фиг.4 самокалибровка может быть выполнена в ответ на запрашиваемую рабочую частоту, для которой не найдена запись в таблице 20 самокалибровки. В дополнение к или вместо этой операции самокалибровка может быть вызвана в один или более иных моментов времени (например, как показано на блок-схеме последовательности операций фиг.5 для одного варианта воплощения). Блок-схема последовательности операций, показанная на фиг.5, может быть реализована с помощью аппаратных средств, программного обеспечения и/или их комбинации.

Если система, которая содержит интегральную микросхему 10, загружается впервые (например, клиентом, который купил систему - блок ветвления 90, ответвление "да"), то интегральная микросхема 10 может выполнить самокалибровку (блок 92). Обычно начальная загрузка системы может относиться к включению системы и подготовке системы к началу работы. Определение того, что начальная загрузка является первой начальной загрузкой системы, может быть выполнено множеством способов. Например, может иметься флаг, сохраненный в энергонезависимой памяти в системе, который может указывать, загружается ли эта система впервые. Флаг может проверяться кодом начальной загрузки в системе, и состояние флага может быть изменено в конце кода начальной загрузки, если начальная загрузка является первой начальной загрузкой, так что последующие начальные загрузки не могут быть распознаны как первая начальная загрузка. Например, флаг может быть битом, который первоначально не установлен, а устанавливается после первой начальной загрузки (или наоборот). В некоторых вариантах воплощения полный системный сброс (например, "жесткий" сброс, инициируемый пользователем, активирующим один или более вводов устройства), может очистить флаг "первой начальной загрузки" и вызвать самокалибровку на следующей начальной загрузке. В некоторых вариантах воплощения такая операция может улучшить функциональность устройства. Например, если пользователь инициирует "жесткий" сброс, потому что устройство "не реагирует на запросы" или как-то иначе неправильно функционирует, самокалибровка может частично устранить ошибку, если это ошибка из-за неправильного функционирования интегральной микросхемы 10 (например, из-за того, что самокалибровочная величина напряжения питания слишком низка). Кроме того, если устройство соединено с сетью (например, с интернетом), обновленная калибровочная программа или процедура может быть автоматически загружена в устройство от производителя устройства. Самокалибровка может быть выполнена в ответ на обновление.

Как вариант или вдобавок система может решить, что данная рабочая нагрузка выполняется впервые (блок ветвления 94, ответвление "да"), и может выполнить самокалибровку в ответ (блок 92). Решение, что данная рабочая нагрузка выполняется впервые, может быть реализовано множеством способов (например, флаг для каждой рабочей нагрузки в энергонезависимом запоминающем устройстве, подобно таковому в обсуждении выше касательно первой начальной загрузки). Обнаружение различных рабочих нагрузок может использоваться, например, в системе, в которой рабочие нагрузки изменяются значительно. Например, система может быть мобильным устройством, которое может функционировать как мобильный телефон, аудиопроигрыватель, веб-браузер, и может выполнить различные другие вычислительные задачи. Рабочие нагрузки могут различаться в значительной степени и могут требовать различную величину производительности от интегральной микросхемы 10. Соответственно, самокалибровка для каждой рабочей нагрузки может приводить к дополнительной экономии электроэнергии (например, меньшая нагрузка может приводить к более низкой рабочей температуре, которая может разрешить более низкую величину напряжения питания, чем разрешили бы более высокие рабочие нагрузки).

В еще одном варианте или дополнении система может решить, что ее возраст увеличился на определенную величину (блок ветвления 96, ответвление "да"), и может выполнить самокалибровку в ответ (блок 92). Выполнение самокалибровки в ответ на старение интегральной микросхемы 10 (и/или устройства, которое содержит интегральную микросхему 10) может отрегулировать требуемые величины напряжения питания для интегральной микросхемы 10, чтобы компенсировать эффекты процесса старения кристалла или другие эффекты старения. Таким образом, не нужно прибавлять припуск к требуемой величине напряжения питания, чтобы учесть эффекты старения (так как они уже учтены при перекалибровке в процессе старения интегральной микросхемы 10). Возраст интегральной микросхемы 10 может измеряться множеством способов. Например, возраст может измеряться от даты первой начальной загрузки на основе календарного времени. Возраст может измеряться по времени работы от первой начальной загрузки. Возраст может измеряться в единицах времени или числа тактов, по желанию. В других вариантах воплощения возраст может также измеряться относительно даты производства. В любом случае самокалибровка может выполняться много раз для разного возраста (например, один раз каждые 6 месяцев, один раз в год и т.д.). В других случаях самокалибровка может выполняться динамически, когда система находится в работе, что может помочь компенсировать эффекты температуры. Любое требуемое множество вызовов самокалибровки может быть реализовано в различных вариантах воплощения.

Обращаясь теперь к фиг.6, показана блок-схема другого варианта воплощения интегральной микросхемы 10 и блока PMU/источника 12 питания. Подобно варианту воплощения фиг.1 вариант воплощения интегральной микросхемы 10 на фиг.6 содержит логическую схему 14 и локальное устройство 18 управления электропитанием. Некоторые варианты воплощения могут содержать модуль 16 самокалибровки и таблицу 20 самокалибровки, а другие варианты воплощения могут быть без этих функциональных возможностей. В варианте воплощения фиг.6 таблица 22 F/V из фиг.1 заменена таблицей 102 F/V/N, связанной с локальным устройством 18 управления электропитанием. Таблица 102 F/V/N может содержать записи, хранящие частоту и соответствующие величины напряжения питания, подобно таблице 22 F/V. Кроме того, записи могут сохранять измерение (N) задержки, описанное более подробно ниже. Как изображено далее в варианте воплощения фиг.6, интегральная микросхема 10 может содержать модуль измерений 100 и логические вентили 104A-104H, связанные в последовательном соединении. Ввод логического вентиля (вентилей) 104A связан с модулем 100 измерений, и вывод логического вентиля (вентилей) 104H также связан с модулем 100 измерений. Кроме того, триггер 106 хранит ожидаемое измерение (N) задержки, а триггер 108 хранит значение счетчика (Ctr). Оба триггера 106 и 108 связаны с модулем 100 измерений. В других вариантах воплощения триггеры 106 и 108 могут быть любыми синхронными запоминающими устройствами.

Модуль 100 измерений может быть выполнен с возможностью измерения задержки распространения логического перехода через последовательное соединение вентилей 104A-104H. Вентили 104A-104H могут иметь токую же конструкция, как различные логические вентили в логической схеме 14. Соответственно, задержка распространения через вентили 104A-104H должна быть пропорциональна логическим вентилям в логической схеме 14. Измеряя задержку распространения и сравнивая ее с заранее заданной задержкой, может быть учтено влияние различных факторов на работу логической схемы 14. Например, может быть обнаружено воздействие рабочей температуры, старения и т.д. при измерении задержки распространения и при ее сравнении с заранее заданной величиной.

Задержка распространения может быть измерена в любых требуемых единицах (например, наносекундах, тактах и т.д.). В одном варианте воплощения задержка распространения измеряется в единицах тактов текущей рабочей частоты генератора тактовых импульсов, которым снабжена логическая схема 14. Соответственно, модуль 100 измерений может запустить логический переход (например, переход нуля в единицу или единицы в ноль) во ввод последовательного соединения вентилей 104A-104H (то есть ввод вентилей 104A на фиг.6) и может считать такты до тех пор, пока соответствующий переход не обнаружен на выводе последовательного соединения (то есть вывод вентилей 104H на фиг.6). В одном варианте воплощения может передаваться импульс, содержащий два логических перехода (например, нуля в единицу и обратно в нуль). Счетчик Ctr в триггере 108 может очищаться, когда запускается логический переход, и может постепенно увеличиваться каждый такт, пока не обнаружен соответствующий переход. Триггер 106 может хранить заранее заданное число (N) тактов, которое, как ожидается, пройдет, если напряжение питания обеспечивает задержку, которая поддерживает текущую рабочую частоту. Если измеренное число тактов больше, чем заранее заданное число N, то напряжение питания может быть увеличено, чтобы понизить задержку. Если измеренное число тактов меньше, чем заранее заданное число N, то напряжение питания может быть уменьшено, чтобы увеличить задержку (и потреблять меньше мощности).

Число вентилей в последовательном соединении может быть значительно больше, чем число вентильных задержек, которые могут сработать в пределах такта генератора тактовых импульсов, которым снабжена логическая схема 14. Например, число последовательно соединенных вентилей может быть приблизительно в 100 раз больше числа вентильных задержек за такт. Таким образом, если 14 вентильных задержек доступны в такте, то приблизительно 1400 вентилей могут быть последовательно включены в вентилях 104A-104H. Использование большое количество вентилей может улучшить соответствие измеренной задержки задержке схемы, фактически происходящей в логической схеме 14. Кроме того, так как настоящий вариант воплощения считает задержку в единицах тактов, большое количество вентилей может уменьшить ошибку измерения, которая имеет место из-за гранулярности такта. Например, при числе в 100 раз большем числа вентильных задержек в такте, ошибка в задержке за один полный такт (максимально возможная ошибка) составляет только 1% измеренной величины. Хотя в этом варианте воплощения используется число 100, другие варианты воплощения могут использовать большие или меньшие числа (например, 200, 500, 100, 50, и т.д.).

Заранее заданное число N может быть измерено во время заводской проверки интегральной микросхемы. Обычно ожидается, что заранее заданное число N будет близко к кратному числу вентильных задержек, которое использовалось для создания последовательного соединения вентилей (например, 100 в вышеупомянутом примере), но может несколько отличаться от этого числа. В одном варианте воплощения заранее заданное число N может быть сохранено в таблице 102 F/V/N наряду со статической величиной напряжения питания для данной рабочей частоты. В различных вариантах воплощения может иметься одно число N, сохраненное в таблице, или может иметься одно число N для каждой рабочей частоты (в записи, соответствующей этой рабочей частоте).

Вентили 104A-104H могут быть физически распределены по участку интегральной микросхемы 10, который занят логической схемой 14. Соответственно, в задержке распространения могут быть учтены вариации в характеристиках процесса и/или рабочей температуре, которые могут иметь место в пределах поверхности кристалла интегральной микросхемы. Таким образом, на каждое множество из одного или более вентилей 104A-140H могут влиять рабочая температура и/или характеристики процесса, которые имеют локальный характер для физической области, в которой расположены эти вентили 104A-104H. В одном варианте воплощения вентили 104A-104H могут быть выбраны из "запасных вентилей", которые обычно содержатся повсюду на интегральной микросхеме 10, чтобы сделать возможным исправление логических ошибок в логической схеме 14 посредством изменения слоя межсоединений интегральной микросхемы. Таким образом, запасные вентили изначально не соединены с логической схемой 14 и не используются. Если в логике обнаружены ошибки, то запасные вентили могут быть соединены с логической схемой 14 для формирования правильной логической функции. Множество различных логических вентилей может быть включено в запасные вентили, чтобы увеличить вероятность формирования правильной логической функции. Соответственно, неиспользованные запасные вентили могут быть разнообразными и могут быть соединены вместе для создания последовательного соединения вентилей 104A-104H, которое может масштабироваться подобно логической схеме 14. При реализации вентилей 104A-104H из запасных вентилей, вентили 104A-104H могут не добавляться к полупроводниковому участку, использованному под интегральную микросхему 10.

Кроме того, использование последовательного соединения логических вентилей, 104A-104H для обнаружения задержки является главным образом цифровой схемой. Таким образом, в некоторых вариантах воплощения использование схемы может быть относительно простым и требующим небольшую мощность по сравнению с аналоговой электрической схемой.

Модуль 100 измерений содержит по меньшей мере электрическую схему, выполненную с возможностью запуска перехода и измерения задержки распространения. В некоторых вариантах воплощения модуль 100 измерений может также содержать электрическую схему, выполненную с возможностью определения того, когда провести измерение и/или электрическую схему, выполненную с возможностью сравнивать задержку распространения с ожидаемым значением.

В соответствии с другим вариантом воплощения определение может выполняться в локальном устройстве 18 управления электропитанием или в программном обеспечении.

Обычно логический вентиль содержит электрическую схему, которая получает один или более входных сигналов, и выполнен с возможностью выполнять логическую функцию на входных сигналах, чтобы обеспечить один или более выходных сигналов. Один или более таких вентилей могут быть включены в каждое множество вентилей 104A-104H. Следует отметить, что хотя вентили 104A-104H представлены около границы логической схемы 14 на фиг.6 для удобства изображения графика, вентили обычно могут быть вкраплены повсюду в участки логической схемы 14, как упоминалось выше.

Хотя в вышеупомянутом обсуждении фиг.6 упоминался запрос величины напряжения питания и подача блоком PMU/источником 12 питания напряжения запрошенной величины, обсуждение не подразумевало, что есть только одно запрашиваемое/подаваемое напряжение. Может иметься множество напряжений питания, которые запрашиваются и подаются в любой конкретный момент времени. Например, могут иметься отдельные напряжения питания для комбинаторной логической электрической схемы и для электрической схемы памяти в логической схеме 14. Может иметься множество областей напряжения в пределах интегральной микросхемы 10, которые могут включаться и выключаться отдельно, и могут иметь отдельные модули измерений и последовательные цепочки логических вентилей. Каждая такая область может содержать отдельный запрос. Локальное устройство 18 управления электропитанием может питаться отдельно от логической схемы 14. Любой набор из одного или более напряжений питания может запрашиваться и подаваться. Кроме того, в некоторых вариантах воплощения может быть реализована более чем одна цепочка вентилей в пределах области напряжения для моделирования различных типов задержек. Например, задержки логического вентиля и задержки регистрового файла могут моделироваться отдельно.

Обращаясь теперь к фиг.7, показана блок-схема последовательности операций, которая изображает один вариант воплощения тестирования интегральной микросхемы 10, как показано на фиг.6, до монтажа интегральной микросхемы в корпус. Блоки, показанные на фиг.7, могут выполняться на установке для испытаний (например, приборе для проверки полупроводниковой пластины) во время производства интегральной микросхемы 10.

Подобно варианту воплощения фиг.2 тест может начинаться с тестирования для приблизительного определения характеристик интегральной микросхемы 10 (блок 30), таких как Iddq тестирование, а также может быть выбран набор испытательных напряжений (блок 32). Испытательный прибор может установить первую тестовую частоту (блок 34), и может выполнит тестовую последовательность для каждого напряжения в наборе испытательных напряжений в качестве напряжения питания (блок 36). В этом варианте воплощения тест может содержать активацию модуля 100 измерений. Для каждого испытательного напряжения испытательный прибор может считать число тактов задержки "N", измеренное модулем 100 измерений во время теста (то есть, значение в счетчике триггера 108). Испытательный прибор может записать измеренное N для каждого испытательного напряжения (блок 110). Затем испытательный прибор может выбрать минимальную величину напряжения питания, для которой тест проходит успешно, так же как и соответствующее "N" (блок 112).

Если есть дополнительные тестовые частоты (например, дополнительные поддерживаемые рабочие частоты для интегральной микросхемы 10, которые еще не были протестированы - блок ветвления 40, ответвление "да"), то может быть выбрана и протестирована следующая частота (блоки 34, 36, 110 и 112). Набор испытательных напряжений может содержать различные напряжения, которые будут протестированы на каждой поддерживаемой рабочей частоты, или он может быть выбран так, чтобы ожидалось по меньшей мере одно напряжение питания, успешно проходящее тест, для каждой поддерживаемой рабочей частоты. Как только тестовые частоты исчерпаны (блок ветвления 40, ответвление "нет"), установка для испытаний может записать частоты, величины напряжения, и значения "N" в таблицу 102 F/V/N (блок 114).

В некоторых вариантах воплощения может быть прибавлен припуск к измеренному "N", которое будет записано в таблицу. В соответствии с другим вариантом воплощения, припуск может быть прибавлен к "N", считанному из таблицы для записи "N" в триггер 106. Точно так же припуск может быть прибавлен к величине напряжения питания, записанному в таблице, или припуск может быть прибавлен локальным устройством 18 управления электропитанием после чтения величины из таблицы.

Обращаясь теперь к фиг.8, показана блок-схема последовательности операций, которая изображает работу одного варианта воплощения интегральной микросхемы 10 как показано на фиг.6 (и в частности модуль 100 измерений и локальное устройство 18 управления электропитанием) по определению необходимости регулировки величины напряжения питания. Операция фиг.8 может выполняться периодически, пока интегральная микросхема 10 работает (например, в одном варианте воплощения в зависимости от тепловой инерции системы приблизительно один раз каждый период времени от 10 микросекунд до 1 миллисекунды). Операция фиг.8 может выполняться после изменения рабочей нагрузки (например, с работы в режиме телефона на работу в режиме аудиопроигрывателя или мобильного устройства доступа в интернет). Также операция фиг.8 может выполняться как часть изменения частоты работы. Блоки показаны в определенном порядке для простоты понимания, но могут использоваться и другие последовательности. Блоки могут выполняться параллельно комбинаторной логикой в модуле 100 измерений/локальном устройстве 18 управления электропитанием. Блоки, комбинации блоков и/или блок-схема последовательности операций в целом могут исполняться конвейерным образом за множество тактов.

Локальное устройство 18 управления электропитанием может активировать модуль 100 измерений, который может измерять текущую задержку распространения ("N") в последовательном соединении вентилей 104A-104H (блок 120). В некоторых вариантах воплощения локальное устройство 18 управления электропитанием и/или модуль 100 измерений может фильтровать результаты (блок 122). А именно, фильтрация может содержать, например, обнаружение колебаний значения N между последовательными измерениями. Колебание может иметь место, потому что задержка распространения близка к целому числу тактов (и таким образом иногда фиксируется М тактов, а иногда M+1 тактов). Колебание может также иметь место в силу того, что запрошенное напряжение питания увеличивается и уменьшается колебательным образом.

Если модуль 100 измерений обнаруживает, что измеренное "N" больше чем "N" из таблицы 102 F/V/N (блок ветвления 124, ответвление "да"), то локальное устройство 18 управления электропитанием может увеличить запрашиваемую величину напряжения питания, отправленную в блок PMU/источник 12 питания (блок 126). Например, может запрашиваться следующая более высокая величина напряжения питания. Если модуль 100 измерений обнаруживает, что измеренное "N" меньше чем "N" из таблицы 102 F/V/N (блок ветвления 128, ответвление "да"), то локальное устройство 18 управления электропитанием может уменьшить запрашиваемую величину напряжения питания, отправленную в блок PMU/источник 12 питания (блок 130). Операция фиг.8 может повторяться, пока не установится запрошенная величина напряжения питания, или может повторяться во время следующего измерения, по желанию.

Обращаясь теперь к фиг.9, показана блок-схема последовательности операций, которая изображает работу одного варианта воплощения интегральной микросхемы 10 (и в частности локальное устройство 18 управления электропитанием и модуль 100 измерений) в ответ на запрос об изменении частоты в интегральной микросхеме 10. Блоки показаны в определенном порядке для простоты понимания, однако могут использоваться иные порядки расположения. Блоки могут выполняться параллельно комбинаторной логикой в модуле 100 измерений/локальном устройстве 18 управления электропитанием. Блоки, комбинации блоков, и/или блок-схема последовательности операций в целом могут исполняться конвейерным образом за множество тактов.

Если запрос об изменении частоты является запросом на увеличение текущей рабочей частоты (блок ветвления 140, ответвление "да"), значение N в триггере 106 может масштабироваться в соответствии с отношением новой (запрошенной) частоты и старой (текущей частоты) (блок 142). Например, если текущая частота равна 1 ГГц, а новая частота 1.5 ГГц, то значение N может масштабироваться на 1.5. Локальное устройство 18 управления электропитанием и модуль 100 измерений могут повторять процесс регулировки напряжения питания фиг.8 до тех пор, пока измеренное N из модуля 100 измерений не будет соответствовать масштабированному N (блок 144). В некоторых вариантах воплощения к масштабированному N может быть прибавлен припуск, чтобы гарантировать, что увеличенная величина напряжения питания достаточна для поддержки вновь измененной частоты. Как только масштабированное N достигнуто, локальное устройство 18 управления электропитанием может установить новую частоту (блок 146) и может ожидать фиксации схемы генератора тактовых импульсов на новой частоте (блок 148). Новое N может считываться из таблицы 102 F/V/N и может записываться в триггер 106 (блок 150).

Если запрос об изменении частоты является запросом на уменьшение текущей рабочей частоты (блок ветвления 140, ответвление "нет"), локальное устройство 18 управления электропитанием может установить новую частоту (блок 146) без масштабирования N и регулировки напряжения питания (блоки 142 и 144). Так как напряжение питания уже достаточно высоко для поддержки более высокой текущей частоты, интегральная микросхема 10 будет работать на новой частоте без ошибок. Последующие периодические измерения и регулировки (например, фиг.8) могут понизить напряжение. В других вариантах воплощения N может масштабироваться, а напряжение может регулироваться (блоки 142 и 144) также и для новой более низкой частоты, в этом случае регулировки напряжения питания будут являться понижениями.

В некоторых вариантах воплощения процесс регулировки величины напряжения питания (блок 144) может начинаться с чтения величины напряжения питания из таблицы 102 F/V/N (или таблицы 22 самокалибровки) для новой частоты и инициализации процесса при запросе величины напряжения питания из таблицы.

Обращаясь теперь к фиг.10, показана блок-схема последовательности операций, которая изображает другой вариант воплощения тестирования интегральной микросхемы 10 как показано на фиг.6 до монтажа интегральной микросхемы в корпус. Блоки, показанные на фиг.10 могут выполняться на установке для испытаний (например, приборе для проверки полупроводниковой пластины) во время производства интегральной микросхемы 10.

Аналогично варианту воплощения фиг.2 тест может начинаться с тестирования для приблизительного определения характеристик интегральной микросхемы 10 (блок 30), например Iddq тестирования. Кроме того, модуль 100 измерений может быть активирован с максимально возможным установленным значением напряжения питания (в соответствии со спецификацией интегральной микросхемы 10) (блок 160). Измерение числа N при максимально возможном значении может быть показателем "скорости" интегральной микросхемы 10 и может использоваться для выбора набора испытательных напряжений (блок 162). Таким образом, выбранные испытательные напряжения могут быть ближе к оптимальному напряжению для данной частоты, что может позволить тестирование напряжения с малым шагом за небольшом количество времени тестирования и иметь результатом величину напряжения питания близкую к оптимальному значению для интегральной микросхемы 10. Соответственно, интегральная микросхема 10 может потреблять меньшую мощность на данной частоте, когда напряжение питания установлено равным напряжению в таблице (по сравнению с менее оптимальными стратегиями тестирования). Кроме того, еще может использоваться относительно небольшой набор напряжений, уменьшая время тестирования. Например, фиг.13 является графическим изображением распределения экземпляров от быстрого процесса (левая сторона фиг.13) до медленного процесса (правая сторона фиг.13). Используя максимальное напряжение (пунктирная линия дальше всего направо) может быть измерено N. На основании измеренного N может быть выбран небольшой набор испытательных напряжений около ожидаемой рабочей точки, и интегральная микросхема 10 может быть протестирована на этих напряжениях (фигурная скобка у основания фиг.13).

Впоследствии аналогично варианту воплощения фиг.7 устанавливают первую тестовую частоту (блок 34) и могут выполнять тестовую последовательность для каждого напряжения в наборе испытательных напряжений в качестве напряжение питания (блок 36). Тест может включать в себя активацию модуля 100 измерений. Для каждого испытательного напряжения испытательный прибор может считывать число тактов задержки "N", измеренных модулем 100 измерений во время теста (то есть, значение в триггере 108 счетчика). Испытательный прибор может записать измеренное N для каждого испытательного напряжения (блок 110). Затем испытательный прибор может выбрать минимальную величину напряжения питания, для которой тест проходит успешно, так же как соответствующее "N" (блок 112).

Если есть дополнительные тестовые частоты (например, дополнительные поддерживаемые рабочие частоты для интегральной микросхемы 10, которые еще не были протестированы - блок ветвления 40, ответвление "да"), то может быть выбрана и протестирована следующая частота (блоки 34, 36, 110, и 112). Набор испытательных напряжений может содержать различные напряжения для тестирования для каждой поддерживаемой рабочей частоты, или может быть выбран так, чтобы имелось по меньшей мере одно успешно проходящее тест напряжение питания для каждой поддерживаемой рабочей частоты. Как только тестовые частоты были исчерпаны (блок ветвления 40, ответвление "нет"), установка для испытаний может записать частоты, величины напряжения, и значения "N" в таблицу 102 F/V/N (блок 114).

В некоторых вариантах воплощения к измеренному "N", которое будет записано в таблицу, может быть прибавлен припуск. В соответствии с другим вариантом воплощения, припуск может быть прибавлен к "N", считанному из таблицы, для записи "N" в триггер 106. Аналогично припуск может быть прибавлен к величине напряжения питания, записанной таблице, или припуск может быть прибавлен локальным устройством 18 управления электропитанием после чтения величины из таблицы.

Обращаясь теперь к фиг.11, показана блок-схема последовательности операций, которая изображает работу одного варианта воплощения модуля 100 измерений по выполнению измерения. Модуль 100 измерений может выполнять операцию, изображенную на фиг.11, например, в ответ на инициирование измерения локальным устройством 18 управления электропитанием. Блоки показаны в определенном порядке для простоты понимания, однако могут использоваться и другие порядки расположения. Блоки могут выполняться параллельно комбинаторной логикой в модуле 100 измерений. Блоки, комбинации блоков, и/или блок-схема последовательности операций в целом могут исполняться конвейерным образом за множество тактов.

Модуль 100 измерений может очистить счетчик в триггере 108 (номер позиции 170), и может запустить логический переход в последовательное соединение (или "цепочку") вентилей 104A-104H (блок 172). Если модуль 100 измерений еще не обнаружил соответствующий логический переход на выводе цепочки (блок ветвления 174, ответвление "нет"), то модуль 100 измерений может увеличить значение счетчика (блок 176) и ожидать следующего такта, чтобы снова обнаружить переход (блок 178). Если модуль 100 измерений обнаружил соответствующий переход (блок ветвления 174, ответвление "да"), то модуль 100 измерений может сравнить счетчик с N в триггере 106 и сообщить результаты локальному устройству 18 управления электропитанием (блок 180).

Многочисленные вариации и модификации станут очевидны для специалистов в области техники, как только вышеприведенное раскрытие полностью понято. Имеется в виду, что нижеследующая формула изобретения интерпретируется так, чтобы охватить все такие вариации и модификации.

Изобретения относятся к интегральным микросхемам и могут быть использованы для динамического управления напряжением и частотой в интегральных микросхемах. Техническим результатом является обеспечение возможности корректной работы интегральной микросхемы. Устройство содержит логическую схему, локальное устройство управления электропитанием и модуль самокалибровки, выполненный с возможностью повторять тест логической схемы в интегральной микросхеме на соответственно более низких величинах напряжения питания до тех пор, пока не тест не даст сбой. Самая низкая величина напряжения питания, на которой тест проходит успешно, используется для генерации запрошенной величины напряжения питания для интегральной микросхемы. 2 н. и 12 з.п. ф-лы, 13 ил.

1. Интегральная микросхема, сконфигурированная для генерации запрошенной величины напряжения питания для интегральной микросхемы, причем интегральная микросхема содержит:

логическую схему;

локальное устройство управления электропитанием, связанное с логической схемой и выполненное с возможностью передавать указание о запрошенной величине напряжения питания внешнему источнику питания; и модуль самокалибровки в интегральной микросхеме, который выполнен с возможностью выполнять тест логической схемы, причем модуль самокалибровки выполнен с возможностью повторять тест на соответственно более низких запрошенных величинах напряжения питания до тех пор, пока тест не даст сбой, и при этом самая низкая запрошенная величина напряжения питания, на которой тест успешно проходит, используется для генерации запрошенной величины напряжения питания для работы интегральной микросхемы, и при этом модуль самокалибровки дополнительно выполнен с возможностью повторять тест и определять самую низкую запрошенную величину напряжения питания в ответ на выполнение логической схемой различной рабочей нагрузки.

2. Интегральная микросхема по п.1, дополнительно содержащая статическую таблицу величин напряжения питания, причем содержимое статической таблицы определяется во время заводской проверки интегральной микросхемы, и при этом локальное устройство управления электропитанием выполнено с возможностью считывать начальную величину напряжения питания из статической таблицы.

3. Интегральная микросхема по п.1, в которой интегральная микросхема может работать на множестве тактовых частот, и в которой модуль самокалибровки выполнен с возможностью повторять тест на соответственно более низких величинах напряжения питания для каждой из множества тактовых частот для определения самой низкой запрошенной величины напряжения питания для каждой из множества тактовых частот.

4. Интегральная микросхема по п.1, в которой модуль самокалибровки выполнен с возможностью повторять тест в ответ на начальную загрузку устройства, которое включает в себя интегральную микросхему.

5. Интегральная микросхема по п.4, в которой модуль самокалибровки выполнен с возможностью повторять тест и определять самую низкую запрошенную величину напряжения питания в ответ на превышение возрастом интегральной микросхемы определенной величины.

6. Интегральная микросхема по п.1, в которой локальное устройство управления электропитанием содержит таблицу самокалибровки, сконфигурированную для сохранения самых низких величин напряжения питания, определенных посредством модуля самокалибровки, и при этом локальное устройство управления в ответ на запрос по изменению рабочей частоты интегральной микросхемы сконфигурировано проверять таблицу самокалибровки для самой низкой величины напряжения питания, соответствующей рабочей частоте, и при этом локальное устройство управления в ответ на обнаружение того, что самая низкая величина напряжения питания, соответствующая рабочей частоте, не сохранена в таблице самокалибровки, сконфигурировано для вызова модуля самокалибровки для повторения теста на соответственно более низких запрошенных величинах напряжения питания до тех пор, пока тест не даст сбой, для определения самой низкой величины напряжения питания для рабочей частоты.

7. Интегральная микросхема по п.6, в которой локальное устройство управления электропитанием сконфигурировано для определения, вызвать ли модуль самокалибровки в ответ на обнаружение того, что самая низкая величина напряжения питания, соответствующая рабочей частоте, не сохранена в таблице самокалибровки, и при этом локальное устройство управления сконфигурировано запрашивать величину напряжения питания, определенную во время заводской проверки интегральной микросхемы, в ответ на определение не вызывать таблицу самокалибровки.

8. Способ генерации величины напряжения питания для интегральной микросхемы, при этом способ содержит этапы:

повторения теста логической схемы модулем самокалибровки при соответственно более низких запрошенных величинах напряжения питания для интегральной микросхемы, которая содержит логическую схему и модуль самокалибровки, до тех пор, пока тест не даст сбой;

определения посредством модуля самокалибровки самой низкой запрошенной величины напряжения питания, при которой тест проходит успешно;

выбора посредством модуля самокалибровки самой низкой запрошенной величины напряжения питания для генерирования запрошенной величины напряжения питания для работы интегральной микросхемы, при этом способ выполняется в ответ на выполнение логической схемой различной рабочей нагрузки.

9. Способ по п.8, дополнительно содержащий считывание начальной запрошенной величины напряжения питания из статической таблицы, причем содержание статической таблицы определяется во время заводской проверки интегральной микросхемы.

10. Способ по п.8, в котором интегральная микросхема может работать на множестве тактовых частот, а способ дополнительно содержит повторение этапов повторения, определения и выбора для каждой из множества тактовых частот.

11. Способ по п.8, выполняемый в ответ на начальную загрузку устройства, которое включает в себя интегральную микросхему.

12. Способ по п.11, выполняемый в ответ на превышение возрастом интегральной микросхемы определенной величины.

13. Способ по п.8, дополнительно содержащий этапы, на которых:

в ответ на запрос по изменению рабочей частоты интегральной микросхемы проверяют таблицу самокалибровки для самой низкой величины напряжения питания, соответствующей рабочей частоте, при этом таблица самокалибровки сконфигурирована для сохранения самых низких величин напряжения питания, определенных посредством модуля самокалибровки; и в ответ на определение того, что самая низкая величина напряжения питания, соответствующая рабочей частоте, не сохранена в таблице самокалибровки, вызывают модуль самокалибровки для повторения теста на соответственно более низких запрошенных величинах напряжения питания до тех пор, пока тест не даст сбой, для определения самой низкой величины напряжения питания для рабочей частоты.

14. Способ по п.13, дополнительно содержащий этапы, на которых:

определяют, вызывать ли модуль самокалибровки в ответ на обнаружение того, что самая низкая величина напряжения питания, соответствующая рабочей частоте, не сохранена в таблице самокалибровки, и при этом упомянутый вызов дополнительно реагирует на определение вызвать модуль самокалибровки; и

запрашивают величину напряжения питания, определенную во время заводской проверки интегральной микросхемы, в ответ на определение не вызывать модуль самокалибровки.

| US 2009016140 A1, 15.01.2009 | |||

| US 2006259840 A1, 16.11.2006 | |||

| US 2003018937 A1, 23.01.2003 | |||

| ЭЛЕКТРОННАЯ СХЕМА С КОНТРОЛЛЕРОМ И СПОСОБ УПРАВЛЕНИЯ ЭНЕРГИЕЙ | 2002 |

|

RU2271563C2 |

Авторы

Даты

2013-07-27—Публикация

2010-01-22—Подача