Настоящее изобретение относится к области тестирования электроники, в частности, определения времени эксплуатации статической оперативной памяти и выявления контрафакта.

1. Проблема контрафактной электронной компонентной базы (ЭКБ) носит глобальный характер - известно много случаев, когда в электронные системы подводных лодок, боевых самолетов США и стран НАТО, космической аппаратуры НАСА и Европейского космического агентства попадали контрафактные (поддельные, клонированные) микросхемы и модули радио электронной аппаратуры низкого качества китайского производства (Tulkoff С.Counterfeit Prevention & Detection Strategies: When To Do It, How to Do It // Symposium on Counerfeit Parts & Materials 2013. http://smta.org (дата обращения: 03.09.2016)). Контрафактные микросхемы можно категорировать на 3 вида: микросхемы, не отвечающие техническим требованиям, дефектные микросхемы и оригинальные микросхемы, бывшие в употреблении (б/у) и проданные как новые. Категория б/у микросхем составляет 80% от всей контрафактной продукции микроэлектроники, такие изделия несут в себе опасность преждевременного выхода из строя, т.е. настоящий жизненный цикл микросхемы заканчивается раньше, чем ожидаемый обманутым пользователем период гарантированной работы, что, несомненно, наносит урон надежности и безопасности функционирования комплектуемой ими аппаратуры (U. Gum, K. Huang, D DiMase, J Carulli, M Tehranipoor, et al., "Counterfeit integrated circuits: A rising threat in the global semiconductor supply chain," Proceedings of the IEEE, Vol. 102, Issue 8, pp. 1207-1228, Aug. 2014).

Из существующего уровня техники известны решения, которые позволяют определить микросхемы, бывшие в употреблении, на основе внедрения (на этапе проектирования) в кристаллы микросхем сенсоров (аппаратных одометров) [3-6], реагирующих на процессы старения полупроводников, такие как NBTI (негативное смещение температурной неустойчивости) и HCI (инжекция горячих носителей), что дает возможность установить факт и примерное время использования микросхем. Типичным представителем описанной группы решений является патент US 7,592,876 В2 [3], в котором в качестве сенсора старения выступает пара генераторов колебаний (или пара цепочек генераторов колебаний), в которой один из генераторов (все время стареющий) испытывает воздействие процесса старения с каждым тактом работы микросхемы, когда как второй генератор (опорный) остается нетронутым эффектами старения, определение времени эксплуатации микросхемы происходит за счет измерения разницы задержек сигнала или разницы частот стареющего и опорного генераторов. В источнике [4] вместо генераторов колебаний используются цепочки инверторов (все время стареющая цепочка инверторов и опорная), время эксплуатации аналогично вычисляется посредствам измерения разницы задержек прохождения сигнала через опорную и состарившуюся цепочки инверторов, в патенте US 2017/0126229 A1 [5] в качестве сенсора старения используются два внутренних проводника микросхемы, один из которых во время эксплуатации находится в условиях старения, второй опорный, на основе эффекта электромиграции, посредствам сравнительного анализа устанавливается время эксплуатации. Данные решения, помимо издержек в виде дополнительного места на кристалле под сенсоры, часто требуют привлечения точных аналоговых измерительных приборов, кроме того, на практике редко встречаются микросхемы, оборудованные такими механизмами.

Другая группа решений, определяющих микросхемы, бывшие в употреблении, основана на записи данных счетчика (или сенсора старения) микросхемы в ее нестираемую память (ПЗУ) (в частности, US, заявка 2017/0126229, опубл.). В патенте ЕР0623900 (опубл.) предлагается записывать в нестираемую память микросхемы информацию о времени ее эксплуатации, а также время и место ее производства, дополнительную информацию, считанную из различных сенсоров, обеспечивающих данными о состоянии надежности и функциональности микросхемы. Данный подход представлен в виде цифрового решения и не требует привлечения аналогового измерительного оборудования, однако по-прежнему имеют место издержки проектирования и выделения дополнительного места на кристалле для реализации такого подхода. На практике так же нечасто встречаются микросхемы с записанным временем эксплуатации в нестираемой памяти.

2. Наряду с вышеописанными также существуют решения, направленные на борьбу с контрафактом изделий микроэлектроники, к которым относятся: обязательная маркировка с серийным номером изделия, ставший нормой в современных изделиях микроэлектроники электронный идентификатор микросхемы (Electronic Chip ID)([K. Arndt, С. Narayan, A. Brintzinger, W. Guthrie, D. Lachtrupp, J. Mauger, D. Glimmer, S. Lawn, B. Dinkel, and A. Mitwalsky, "Reliability of laser activated metal fuses in drams," in Proc. of IEEE on Electronics Manufacturing Technology Symposium, 1999, pp. 389-394). набирающая популярность идентификация, использующая уникальные особенности изделий микроэлектроники («отпечатки пальцев» в области техники), по которым создаются физически неклонируемые функции [11-13], и др. Данные решения позволяют определить только подлинность изделия посредствам сличения считанной идентификационной информации микросхемы с априорной информацией в информационных источниках производителя, и не дают возможности установить факт использования оригинальных микросхем, т.е. не выявляют микросхемы, бывшие в употреблении.

Наиболее близким к заявленному решению по технической сущности является патент CN104810062A, в котором используются уникальные особенности микросхемы SRAM, связанные с разбросом технологического процесса производства, с помощью которых сконструирована физически неклонируемая функция, выражающаяся в данном решении в виде гистограммы частоты переключившихся бит предварительно записанного массива памяти микросхемы SRAM, которую в режиме эксплуатации подвергают воздействию различной высокой температуры, после чего анализируют изменения свойств выбранной физически неклонируемой функции для оценки надежности микросхемы. Преимущества подхода данного решения заключаются в том, что не требуется топологической избыточности микросхемы и осуществляется цифровым способом, без привлечения точных измерительных аналоговых приборов.

Недостатком известно технического решения следует признать тот факт, что способ, защищенный патентом CN104810062, направлен на оценку надежности микросхемы и не позволяет идентифицировать микросхему как «новую» или «бывшую в употреблении».

Техническая проблема, решаемая с использованием разработанного способа, состоит в обеспечении возможности идентифицировать микросхемы статической оперативной памяти как «новые» или «бывшие в употреблении».

Техническим результатом, обеспечиваемым приведенной совокупностью признаков, является выявление микросхем СОЗУ (статические оперативные запоминающие устройства), бывших в употреблении, простым цифровым оборудованием, без применения точных аналоговых измерительных приборов, посредствам штатного интерфейса микросхемы, без специальных требований к ее электрической и топологической схеме, без априорной первичной информации о свойствах ее физически неклонируемых функциях.

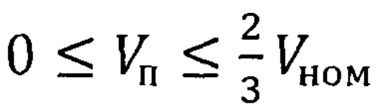

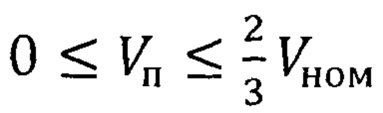

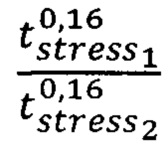

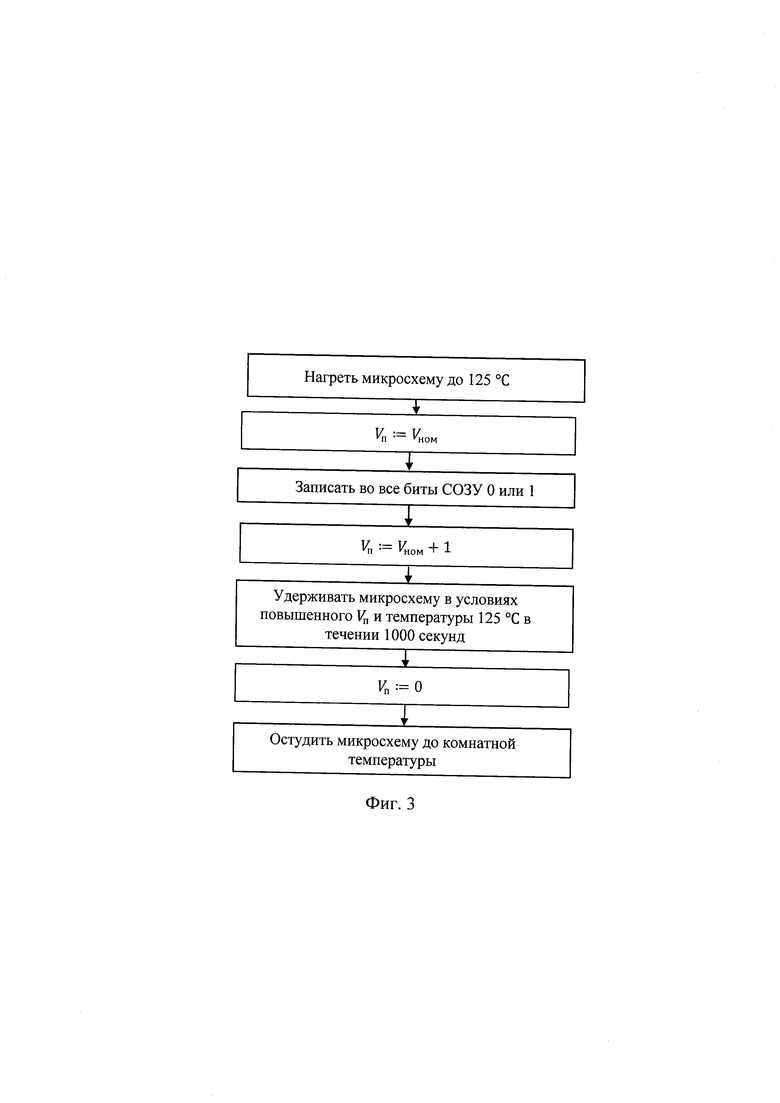

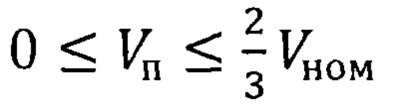

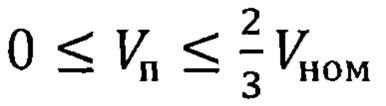

Для обеспечения достижения указанного технического результата предложено использовать разработанный способ выявления контрафактных микросхем, бывших в употреблении на основе свойств деградации СОЗУ, выполненного по КМОП технологии 65 нм - 90 нм. Согласно разработанному способу производят подсчет нестабильных бит путем записи при номинальном напряжении питания (Vп=Vном) во все биты СОЗУ значение 1 или 0, затем напряжение питания уменьшают до значения, выбранного из диапазона  , которое гарантированно ниже критического уровня удержания микросхемой информации, после чего все биты СОЗУ последовательно вдоль линии слов переводят в режим чтения на период, достаточный для разрядки RC константы электрической схемы, далее содержимое СОЗУ считывают и подсчитывают количество бит, изменивших свое значение (N), затем микросхему СОЗУ с записанным во все ячейки значением 1 или 0 подвергают стрессовому воздействию, путем воздействия повышенной температурой и напряжением (Vстресс) в течении периода времени Δt, причем способ реализуют посредством комбинации подсчета нестабильных бит и, по крайней мере, двух итераций стрессового воздействия и подсчета нестабильных бит, при этом после первого подсчета нестабильных бит инициализируют начальное количество нестабильных бит N0=N, после второго подсчета нестабильных бит считают приращенное количество нестабильных бит относительно первого подсчета первой итерации стресса ΔN1=N-N0, после третьего подсчета нестабильных бит считают общее приращенное количество нестабильных бит относительно второго подсчета после ΔN2=N-N0, затем вычисляют истинность выражения

, которое гарантированно ниже критического уровня удержания микросхемой информации, после чего все биты СОЗУ последовательно вдоль линии слов переводят в режим чтения на период, достаточный для разрядки RC константы электрической схемы, далее содержимое СОЗУ считывают и подсчитывают количество бит, изменивших свое значение (N), затем микросхему СОЗУ с записанным во все ячейки значением 1 или 0 подвергают стрессовому воздействию, путем воздействия повышенной температурой и напряжением (Vстресс) в течении периода времени Δt, причем способ реализуют посредством комбинации подсчета нестабильных бит и, по крайней мере, двух итераций стрессового воздействия и подсчета нестабильных бит, при этом после первого подсчета нестабильных бит инициализируют начальное количество нестабильных бит N0=N, после второго подсчета нестабильных бит считают приращенное количество нестабильных бит относительно первого подсчета первой итерации стресса ΔN1=N-N0, после третьего подсчета нестабильных бит считают общее приращенное количество нестабильных бит относительно второго подсчета после ΔN2=N-N0, затем вычисляют истинность выражения  истинность которого говорит о том, что микросхема СОЗУ «новая», а ложное значение - «использованная».

истинность которого говорит о том, что микросхема СОЗУ «новая», а ложное значение - «использованная».

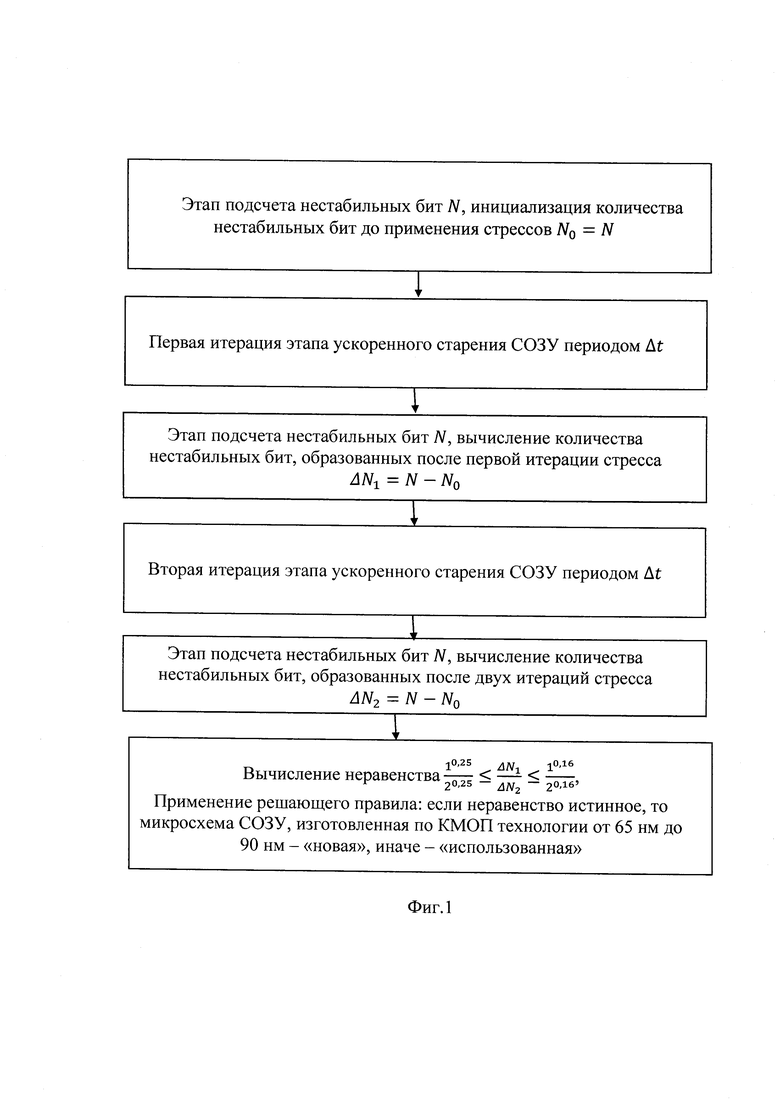

Предпочтительно период, на который все биты СОЗУ последовательно вдоль линии слов, переводят в режим чтения составляет 10 мс.

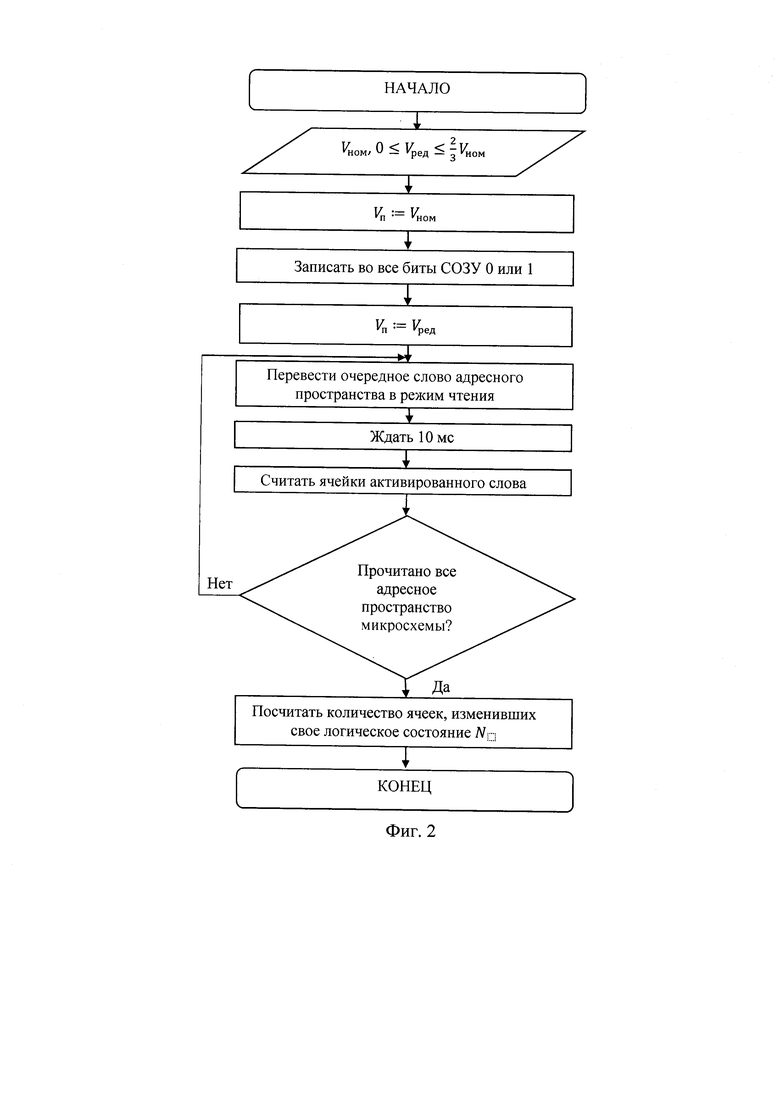

Преимущественно циклы стрессов ускоренного старения проходят при температуре 125°С. Обычно Nстресс=Vном+1В.

В некоторых вариантах реализации разработанного способа выбранное значение записи оставляют неизменным для всех итераций подсчета нестабильных бит.

Поставленную проблему решают путем применения способа выявления контрафактных микросхем, бывших в употреблении на основе свойств деградации СОЗУ, выполненного по КМОП технологии 65 нм - 90 нм, с использованием штатного интерфейса микросхемы, без специальных требований к ее электрической и топологической схеме, без априорной первичной информации о свойствах ее физически неклонируемых функциях, без сравнения с эталоном. Используемый способ включает следующие этапы:

этап подсчета нестабильных бит производится следующим образом: при номинальном напряжении питания (Vп=Vном) во все биты СОЗУ записывают значение 1 или 0 (выбранное значение остается неизменным для всех итераций подсчета нестабильных бит); затем напряжение питания сбрасывают до значения из диапазона  (значения диапазона гарантированно ниже критического уровня удержания микросхемой информации); после чего все биты СОЗУ последовательно вдоль линии слов переводят в режим чтения на период 10 мс (или другой период, достаточный для разрядки RC константы электрической схемы); далее содержимое СОЗУ считывают, и подсчитывают количество бит, изменивших свое значение (N);

(значения диапазона гарантированно ниже критического уровня удержания микросхемой информации); после чего все биты СОЗУ последовательно вдоль линии слов переводят в режим чтения на период 10 мс (или другой период, достаточный для разрядки RC константы электрической схемы); далее содержимое СОЗУ считывают, и подсчитывают количество бит, изменивших свое значение (N);

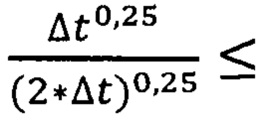

этап стресса ускоренного старения производят следующим образом: микросхему СОЗУ с записанным во все ячейки значением 1 или 0 (выбранное значение остается неизменным для всех итераций этапа стресса) подвергают воздействию повышенной температуры (125°С) и напряжения (Vстресс=Vном+1В) в течении периода времени Δt;

причем способ реализуют посредством комбинации этапа подсчета нестабильных бит и двух итераций цикла этапа стресса и подсчета нестабильных бит: после первого этапа подсчета нестабильных бит инициализируют начальное количество нестабильных бит N0=N, после второй итерации этапа подсчета нестабильных бит считают приращенное количество нестабильных бит после первой итерации стресса N1=N-N0, после третьей итерации этапа подсчета нестабильных бит считают общее приращенное количество нестабильных бит после второй итерации стресса N2=N-N0; после чего вычисляют истинность выражения  истинность которого говорит о том, что микросхема СОЗУ «новая», а ложное значение - «использованная».

истинность которого говорит о том, что микросхема СОЗУ «новая», а ложное значение - «использованная».

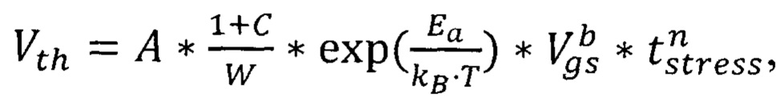

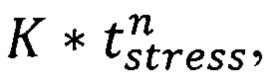

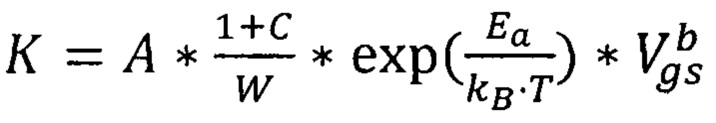

Увеличение количества нестабильных бит в СОЗУ в результате старения обусловлено увеличением разницы уровней пороговых напряжений включений инверторов (транзисторов, входящих в инверторы) каждой ячейки СОЗУ, которая ведет к нестабильности, выражаемой в самопроизвольном переключении логического состояния ячейки СОЗУ в стрессовых условиях функционирования (повышенное или пониженное напряжение питания, температура и др.). Установлено [14], что при направленном (когда все ячейки СОЗУ находятся в одинаковом логическом состоянии) ускоренном старении СОЗУ КМОП технологии технического узла 65 нм - 90 нм в режиме хранения количество нестабильных бит увеличивается пропорционально увеличению порогового напряжения подтягивающих транзисторов КМОП ячеек СОЗУ: ΔN=k*ΔVth, где ΔN - увеличившееся количество нестабильных бит, ΔVth - средний сдвиг порового напряжения подтягивающих транзисторов ячеек СОЗУ, k - коэффициент пропорциональности. При этом подтягивающие транзисторы ячеек СОЗУ в режиме хранения деградируют под действием процесса температурной нестабильности при отрицательном смещении (в иностранной литературе Negative Bias Temperature Instability (NBTI)) по закону:  где tstress - время воздействия NBTI процесса на транзистор, ассоциируемое с периодом эксплуатации, Vgs - напряжение на затворе транзистора, W - ширина транзистора, Т - среднестатистическая температура в период эксплуатации, A, Еа, kB, b, n, С - константы реакционно диффузионной модели NBTI эффекта. Как видно из закона, параметры Vgs и Т являются константами, а не функциями от времени, значения которых равно их среднестатистическим за период стресса, поэтому представленный закон старения представляет собой степенную функцию от времени стресса

где tstress - время воздействия NBTI процесса на транзистор, ассоциируемое с периодом эксплуатации, Vgs - напряжение на затворе транзистора, W - ширина транзистора, Т - среднестатистическая температура в период эксплуатации, A, Еа, kB, b, n, С - константы реакционно диффузионной модели NBTI эффекта. Как видно из закона, параметры Vgs и Т являются константами, а не функциями от времени, значения которых равно их среднестатистическим за период стресса, поэтому представленный закон старения представляет собой степенную функцию от времени стресса  степень которой меньше единицы (0<n<1), где

степень которой меньше единицы (0<n<1), где  - константа.

- константа.

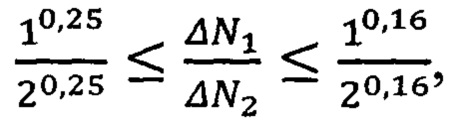

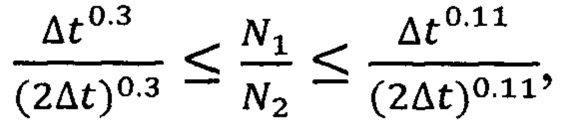

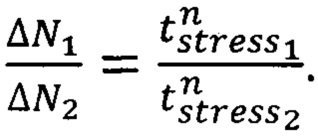

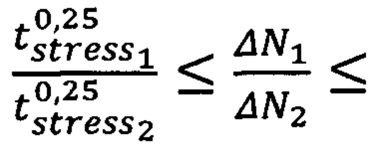

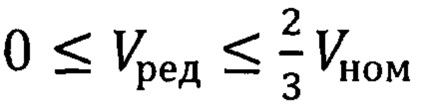

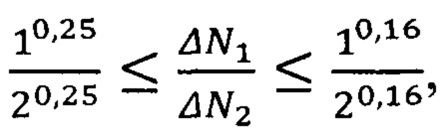

Первая производная функции нелинейно убывает на всей временной шкале, причем ее величина в начальном периоде старения (когда микросхема еще неиспользованная) значительно отличается от ее величины после продолжительной эксплуатации. Этот факт в данном способе используют для индикации «новой» или «использованной» микросхемы СОЗУ, что фиксируется посредством отношения приращений  где ΔN1, ΔN2 - приращения количества нестабильных бит после стрессов старения периодами tstress1-tstress0 и tstress2 - tstress0 соответственно, ΔVth1, ΔVth2 - сдвиги пороговых напряжений подтягивающих транзисторов, представляющие из себя разницы пороговых напряжений ΔVth1=Vth1-Vtho, ΔVth2=Vth2-Vth0, где Vth0 -пороговое напряжение подтягивающего транзистора на момент времени эксплуатации tstress0 Vth1 - значение порогового напряжения на момент времени эксплуатации tstress1, Vth2 - значение порогового напряжения на момент времени эксплуатации tstress2, K0, K1, K2 - константы соответствующих периодов стресса. Предположим, что на момент проверки микросхема СОЗУ «новая», а итерации цикла ускоренного старения проходят с фиксированными значениями напряжения и температуры (Vgs1=Vgs2 и T1=Т2), тогда tstress0=0, K1=K2, в таком случае

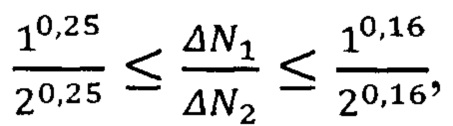

где ΔN1, ΔN2 - приращения количества нестабильных бит после стрессов старения периодами tstress1-tstress0 и tstress2 - tstress0 соответственно, ΔVth1, ΔVth2 - сдвиги пороговых напряжений подтягивающих транзисторов, представляющие из себя разницы пороговых напряжений ΔVth1=Vth1-Vtho, ΔVth2=Vth2-Vth0, где Vth0 -пороговое напряжение подтягивающего транзистора на момент времени эксплуатации tstress0 Vth1 - значение порогового напряжения на момент времени эксплуатации tstress1, Vth2 - значение порогового напряжения на момент времени эксплуатации tstress2, K0, K1, K2 - константы соответствующих периодов стресса. Предположим, что на момент проверки микросхема СОЗУ «новая», а итерации цикла ускоренного старения проходят с фиксированными значениями напряжения и температуры (Vgs1=Vgs2 и T1=Т2), тогда tstress0=0, K1=K2, в таком случае  Из источников [15-17] известно, что значение степени n лежит в границах от 0,16 до 0,25 (0,16≤n≤0,25), поэтому для новой микросхемы неравенство

Из источников [15-17] известно, что значение степени n лежит в границах от 0,16 до 0,25 (0,16≤n≤0,25), поэтому для новой микросхемы неравенство

будет истинным. Таким образом, чтобы определить микросхему СОЗУ как «новую» или «использованную» необходимо подвергнуть микросхему двум циклам ускоренного старения периодами tstress1 и Δt, зафиксировать увеличение количества нестабильных бит после каждого стресса ΔN1 и ΔN, и проверить истинность приведенного неравенства, где tstress2=tstress1+Δt, ΔN2=ΔN1+ΔN; истинное значение будет говорить о том, что микросхема новая, ложное значение - «использованная».

будет истинным. Таким образом, чтобы определить микросхему СОЗУ как «новую» или «использованную» необходимо подвергнуть микросхему двум циклам ускоренного старения периодами tstress1 и Δt, зафиксировать увеличение количества нестабильных бит после каждого стресса ΔN1 и ΔN, и проверить истинность приведенного неравенства, где tstress2=tstress1+Δt, ΔN2=ΔN1+ΔN; истинное значение будет говорить о том, что микросхема новая, ложное значение - «использованная».

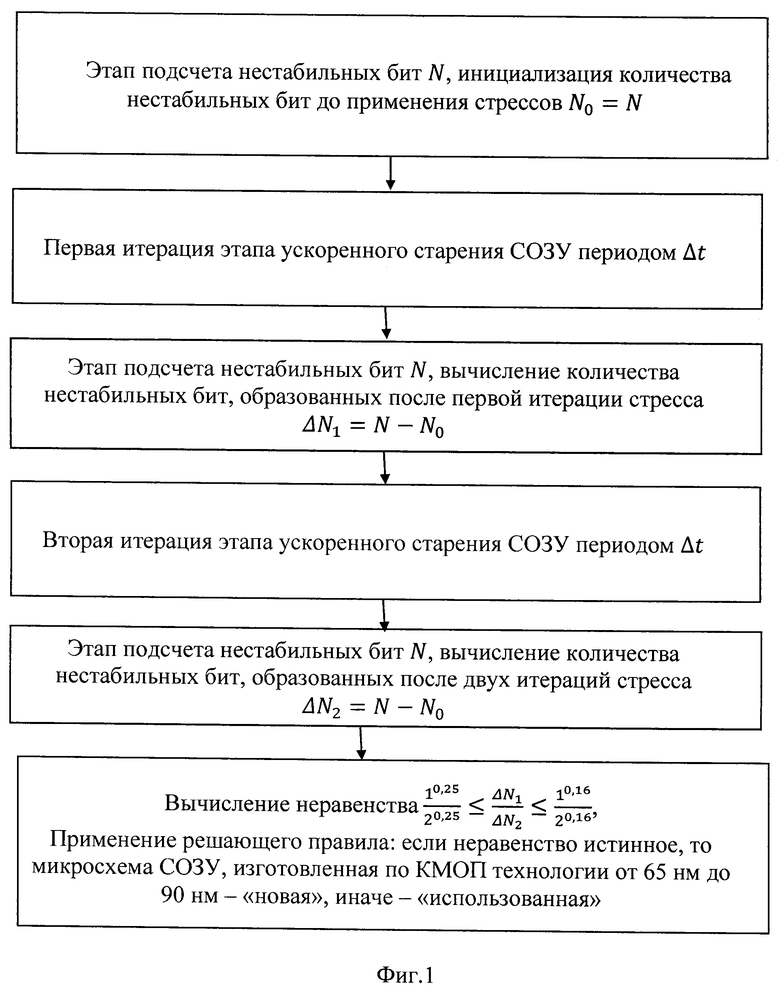

Сущность изобретения поясняется графическим материалом, на которых изображено:

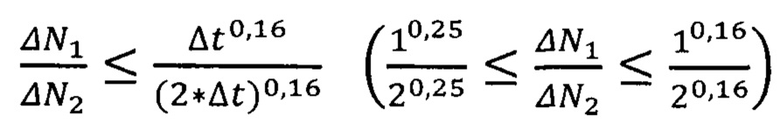

На фиг. 1 - схематично изображена последовательность этапов, реализующих изобретение;

На фиг. 2 - изображен алгоритм действий, реализующих этап подсчета нестабильных бит;

На фиг. 3 - изображен алгоритм действий, реализующих этап ускоренного старения микросхемы СОЗУ;

Разработанный способ, определяющий статические оперативные запоминающие устройства (СОЗУ) любого исполнения (от 6 транзисторов и больше) и технологии изготовления 65 нм - 90 нм, бывшие в употреблении, характеризуется тем, что его осуществляют простым цифровым оборудованием, без применения точных аналоговых приборов, посредствам штатного интерфейса микросхемы, без специальных требований к ее электрической и топологической схеме характеризуется последовательностью этапов, представленной на фиг. 1.

Осуществляют разработанный способ следующим образом, осуществляют последовательность этапов подсчета нестабильных бит и ускоренного старения СОЗУ. Этап подсчета нестабильных бит осуществляют рядом следующих действий (фиг. 2): при номинальном напряжении питания (Vп-Vном) во все биты СОЗУ записывают значение 1 или 0 (выбранное значение остается неизменным для всех итераций подсчета нестабильных бит); затем напряжение питания сбрасывают до значения Vп=Vред из диапазона  (значения ниже критического уровня удержания микросхемой информации, причем выбранное значение Vред остается неизменным для всех итераций подсчета нестабильных бит); после чего все биты СОЗУ последовательно вдоль линии слов переводят в режим чтения на период 10 мс (или другой период, достаточный для разрядки RC константы электрической схемы); далее содержимое СОЗУ считывают, и подсчитывают количество бит, изменивших свое значение (N). Этап ускоренного старения СОЗУ производят следующим образом (фиг. 3): микросхема СОЗУ с записанным во все ячейки значением 1 или 0 (выбранное значение остается неизменным для всех итераций этапа стресса) подвергают воздействию повышенной температуры (125°С) и напряжения питания (Vп=Vном+1В) в течении периода времени Δt (период стресса Δt должен продолжаться не менее 1000 секунд, что статистически достоверно изменит количество нестабильных бит новой микросхемы). Саму последовательность этапов строят следующим образом: первым производят этап подсчета нестабильных бит, в котором выявляют значение количества нестабильных бит перед стрессом ускоренного старения N0=N, после чего применяют первую итерация этапа ускоренного старения СОЗУ, затем снова этап подсчета нестабильных бит, задача которого вычислить количество нестабильных бит, образованных после стресса ΔN1=N-N0; далее выполняют вторую итерацию этапа ускоренного старения СОЗУ, вслед за ней производят заключительный этап подсчета нестабильных бит, в котором вычисляют количество нестабильных бит, образованных за обе итерации этапа ускоренного старения СОЗУ ΔN2=N-N0. Идентификацию микросхемы как «новой» или «использованной» осуществляют по решающему правилу: если неравенство

(значения ниже критического уровня удержания микросхемой информации, причем выбранное значение Vред остается неизменным для всех итераций подсчета нестабильных бит); после чего все биты СОЗУ последовательно вдоль линии слов переводят в режим чтения на период 10 мс (или другой период, достаточный для разрядки RC константы электрической схемы); далее содержимое СОЗУ считывают, и подсчитывают количество бит, изменивших свое значение (N). Этап ускоренного старения СОЗУ производят следующим образом (фиг. 3): микросхема СОЗУ с записанным во все ячейки значением 1 или 0 (выбранное значение остается неизменным для всех итераций этапа стресса) подвергают воздействию повышенной температуры (125°С) и напряжения питания (Vп=Vном+1В) в течении периода времени Δt (период стресса Δt должен продолжаться не менее 1000 секунд, что статистически достоверно изменит количество нестабильных бит новой микросхемы). Саму последовательность этапов строят следующим образом: первым производят этап подсчета нестабильных бит, в котором выявляют значение количества нестабильных бит перед стрессом ускоренного старения N0=N, после чего применяют первую итерация этапа ускоренного старения СОЗУ, затем снова этап подсчета нестабильных бит, задача которого вычислить количество нестабильных бит, образованных после стресса ΔN1=N-N0; далее выполняют вторую итерацию этапа ускоренного старения СОЗУ, вслед за ней производят заключительный этап подсчета нестабильных бит, в котором вычисляют количество нестабильных бит, образованных за обе итерации этапа ускоренного старения СОЗУ ΔN2=N-N0. Идентификацию микросхемы как «новой» или «использованной» осуществляют по решающему правилу: если неравенство

истинно, то микросхема СОЗУ, выполненная по КМОП технологии 65 нм - 90 нм, - «новая», иначе -«использованная».

истинно, то микросхема СОЗУ, выполненная по КМОП технологии 65 нм - 90 нм, - «новая», иначе -«использованная».

ИСТОЧНИКИ ИНФОРМАЦИИ

3. Tulkoff С.Counterfeit Prevention & Detection Strategies: When To Do It, How to Do It // Symposium on Counerfeit Parts & Materials 2013. http://smta.org (дата обращения: 03.09.2016)

4. U. Guin, K. Huang, D DiMase, J Carulli, M Tehranipoor, et al., "Counterfeit integrated circuits: A rising threat in the global semiconductor supply chain," Proceedings of the IEEE, Vol. 102, Issue 8, pp.1207-1228, Aug. 2014.

5. US 7,592,876 B2 [LEAKAGE OSCILLATOR BASED AGNG MONITOR]

6. Puneet Ramesh Savanur, Spyros Tragoudas. A Method to Determine the Static NBTI Stress Time of Embedded Component in an Integreted Circuit // VALID 20176: The Ninth International Conference on Advances in System Testing and Validation

7. US, заявка 2017/0126229 Al ON-CHIPAGING SENSOR AND COUNTERFET INTEGRATED CIRCUITDETECTION METHOD

8. Bhuvaneswari. M, Rajaramya. V.G, Yogananth. A3, Prabakaran. A.P, Recycled IC Detection Based on AF and RO Sensors for Security and Reliability // International Journal of Innovative Research in Science, Engineering and Technology, Vol. 4, Special Issue 6, May 2015 стр. 500-506

9. ЕР, заявка 0623900 A1 Recycable component with data storage for storing information for examining the component and product including such a component

10. X. Zhang and M. Tehranipoor, "Design of On-chip Lightweight Sensors for Effective Detection of Recycled ICs," IEEE Transactions on VLSI (TVLSI), 2013.

11. K. Arndt, С.Narayan, A. Brintzinger, W. Guthrie, D. Lachtrupp, J. Mauger, D. Glimmer, S. Lawn, B. Dinkel, and A. Mitwalsky, "Reliability of laser activated metal fuses in drams," in Proc. of IEEE on Electronics Manufacturing Technology Symposium, 1999, pp. 389- 394.

12. N. Robson, J. Safran, C. Kothandaraman, A. Cestero, X. Chen, R. Rajeevakumar, A. Leslie, D. Moy, T. Kirihata, and S. Iyer, "Electrically programmable fuse (efuse): From memory redundancy to autonomic chips," in Proc. of IEEE on Custom Integrated Circuits Conference, 2007, pp. 799-804.

13. R. Pappu, "Physical one-way functions," Ph.D. dissertation, Massachusetts Institute of Technology, 2001.

14. G. Suh and S. Devadas, "Physical unclonable functions for device authentication and secret key generation," in Proc. of ACM/IEEE on Design Automation Conference, June 2007, pp. 9-14.

15. K. Kursawe, A. -R. Sadeghi, D. Schellekens, B. Skoric, and P. Tuyls, "Reconfigurable physical unclonable functions - enabling technology for tamper-resistant storage," in Proc. of IEEE International Workshop on Hardware-Oriented Security and Trust, July 2009, pp. 22-29.

16. Drapatz S. Parametric Reliability of 6T-SRAM Core Cell Arrays: genehmigten Dissertation - Lehrstuhl fur Technische Elektronik der Technischen Universif'at M"unchen - 2012

17. Massey, J.G. NBTI: WHAT WE KNOW AND WHAT WE NEED TO KNOW A TUTORIAL ADDRESSING THE CURRENNT UNDERSTANDING AND CHALLENGES FOR THE FUTURE // IEEE International Integrated Reliability Workshop Final Report, 2004 - S. Lake Tahoe, CA, USA (Oct. 18-21, 2004)

18. Fundamentals of Bias Temperature Instability in MOS Transistors. Characterization Methods, Process and Materials Impact, DC and AC Modeling: Springer Series in Advanced Microelectronics, Volume 139 / ed. Souvik Mahapatra

19. Grasser T. et al. A Two-Stage Model for Negative Bias Temperature Instability // IEEE International Reliability Physics Symposium (IRPS) - Montreal, QC, Canada (2009.04.)

| название | год | авторы | номер документа |

|---|---|---|---|

| Способ тестирования микросхем энергонезависимой памяти и устройство для его осуществления | 2023 |

|

RU2821349C1 |

| СПОСОБ КОНТРОЛЯ ИДЕНТИЧНОСТИ ИЗДЕЛИЙ В ПАРТИИ ОДНОТИПНЫХ МИКРОСХЕМ | 2014 |

|

RU2554675C1 |

| СПОСОБ ТРЕХМЕРНОГО МНОГОКРИСТАЛЬНОГО КОРПУСИРОВАНИЯ ИНТЕГРАЛЬНЫХ МИКРОСХЕМ ПАМЯТИ | 2019 |

|

RU2705229C1 |

| СПОСОБ ВОССТАНОВЛЕНИЯ ИСХОДНОГО СИГНАЛА ПРИ ДЕЛЬТА-МОДУЛЯЦИИ И УСТРОЙСТВО ДЛЯ ДЕЛЬТА-ДЕМОДУЛЯЦИИ | 1994 |

|

RU2129333C1 |

| Способ безметочного одномолекулярного секвенирования ДНК и устройство для его реализации | 2017 |

|

RU2679494C1 |

| СПОСОБ ПРОВЕДЕНИЯ АДЕКВАТНОЙ ПЕРФУЗИИ ГОЛОВНОГО МОЗГА ПРИ ОПЕРАЦИЯХ НА ВОСХОДЯЩЕМ ОТДЕЛЕ И ЧАСТИ ДУГИ АОРТЫ БЕЗ ЦИРКУЛЯТОРНОГО АРЕСТА | 2019 |

|

RU2734466C1 |

| СПОСОБ КОРРЕКЦИИ СТРЕСС-ВЫЗВАННЫХ РАССТРОЙСТВ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2006 |

|

RU2324424C1 |

| ПОЛУПРОВОДНИКОВЫЙ ПРИБОР С ЗАЩИТОЙ ОБЛАСТЕЙ ТОПОЛОГИИ КРИСТАЛЛА, СОДЕРЖАЩИХ КОНФИДЕНЦИАЛЬНЫЕ ДАННЫЕ, ОТ ОБРАТНОГО ПРОЕКТИРОВАНИЯ | 2011 |

|

RU2455729C1 |

| УСТРОЙСТВО И СХЕМА КАЛИБРОВКИ ИЛИ НАСТРОЙКИ ВСТРОЕННЫХ В МИКРОСХЕМУ РЕГУЛЯТОРОВ БЕЗ ИСПОЛЬЗОВАНИЯ КОНТАКТОВ ВВОДА-ВЫВОДА | 2016 |

|

RU2696233C1 |

| Способ опосредованного определения полноты инактивации антигена вируса ящура в сырье для вакцины с применением обратно-транскриптазной полимеразной цепной реакции в режиме реального времени при амплификации большеразмерного фрагмента | 2021 |

|

RU2753969C1 |

Изобретение относится к области тестирования электроники, в частности, определения времени эксплуатации статической оперативной памяти и выявления контрафакта. Сущность: производят подсчет нестабильных бит путем записи при номинальном напряжении питания (Vп=Vном) во все биты СОЗУ значение 1 или 0. Затем напряжение питания уменьшают до значения, выбранного из диапазона  , которое гарантированно ниже критического уровня удержания микросхемой информации. После чего все биты СОЗУ последовательно вдоль линии слов переводят в режим чтения на период, достаточный для разрядки RC константы электрической схемы. Далее содержимое СОЗУ считывают и подсчитывают количество бит, изменивших свое значение (N). Микросхему СОЗУ с записанным во все ячейки значением 1 или 0 подвергают стрессовому воздействию путем воздействия повышенной температурой и напряжением (Vстресс) в течение периода времени Δt. Способ реализуют посредством комбинации подсчета нестабильных бит и по крайней мере двух итераций стрессового воздействия и подсчета нестабильных бит, при этом после первого подсчета нестабильных бит инициализируют начальное количество нестабильных бит N0=N, после второго подсчета нестабильных бит считают приращенное количество нестабильных бит относительно первого подсчета первой итерации стресса ΔN1=N-N0, после третьего подсчета нестабильных бит считают общее приращенное количество нестабильных бит относительно второго подсчета после ΔN2=N-N0, затем вычисляют истинность выражения

, которое гарантированно ниже критического уровня удержания микросхемой информации. После чего все биты СОЗУ последовательно вдоль линии слов переводят в режим чтения на период, достаточный для разрядки RC константы электрической схемы. Далее содержимое СОЗУ считывают и подсчитывают количество бит, изменивших свое значение (N). Микросхему СОЗУ с записанным во все ячейки значением 1 или 0 подвергают стрессовому воздействию путем воздействия повышенной температурой и напряжением (Vстресс) в течение периода времени Δt. Способ реализуют посредством комбинации подсчета нестабильных бит и по крайней мере двух итераций стрессового воздействия и подсчета нестабильных бит, при этом после первого подсчета нестабильных бит инициализируют начальное количество нестабильных бит N0=N, после второго подсчета нестабильных бит считают приращенное количество нестабильных бит относительно первого подсчета первой итерации стресса ΔN1=N-N0, после третьего подсчета нестабильных бит считают общее приращенное количество нестабильных бит относительно второго подсчета после ΔN2=N-N0, затем вычисляют истинность выражения  истинность которого говорит о том, что микросхема СОЗУ «новая», а ложное значение - «использованная». Технический результат: выявление микросхем СОЗУ (статические оперативные запоминающие устройства), бывших в употреблении, простым цифровым оборудованием без применения точных аналоговых измерительных приборов, посредством штатного интерфейса микросхемы, без специальных требований к ее электрической и топологической схеме, без априорной первичной информации о свойствах ее физически неклонируемых функциях. 4 з.п. ф-лы, 3 ил.

истинность которого говорит о том, что микросхема СОЗУ «новая», а ложное значение - «использованная». Технический результат: выявление микросхем СОЗУ (статические оперативные запоминающие устройства), бывших в употреблении, простым цифровым оборудованием без применения точных аналоговых измерительных приборов, посредством штатного интерфейса микросхемы, без специальных требований к ее электрической и топологической схеме, без априорной первичной информации о свойствах ее физически неклонируемых функциях. 4 з.п. ф-лы, 3 ил.

1. Способ выявления контрафактных микросхем, бывших в употреблении на основе свойств деградации СОЗУ, выполненного по КМОП технологии 65-90 нм, отличающийся тем, что производят подсчет нестабильных бит путем записи при номинальном напряжении питания (Vп=Vном) во все биты СОЗУ значение 1 или 0, затем напряжение питания уменьшают до значения, выбранного из диапазона  , которое гарантированно ниже критического уровня удержания микросхемой информации, после чего все биты СОЗУ последовательно вдоль линии слов переводят в режим чтения на период, достаточный для разрядки RC константы электрической схемы, далее содержимое СОЗУ считывают и подсчитывают количество бит, изменивших свое значение (N), затем микросхему СОЗУ с записанным во все ячейки значением 1 или 0 подвергают стрессовому воздействию путем воздействия повышенной температурой и напряжением (Vстресс) в течение периода времени Δt, причем способ реализуют посредством комбинации подсчета нестабильных бит и по крайней мере двух итераций стрессового воздействия и подсчета нестабильных бит, при этом после первого подсчета нестабильных бит инициализируют начальное количество нестабильных бит N0=N, после второго подсчета нестабильных бит считают приращенное количество нестабильных бит относительно первого подсчета первой итерации стресса ΔN1=N-N0, после третьего подсчета нестабильных бит считают общее приращенное количество нестабильных бит относительно второго подсчета после ΔN2=N-N0, затем вычисляют истинность выражения

, которое гарантированно ниже критического уровня удержания микросхемой информации, после чего все биты СОЗУ последовательно вдоль линии слов переводят в режим чтения на период, достаточный для разрядки RC константы электрической схемы, далее содержимое СОЗУ считывают и подсчитывают количество бит, изменивших свое значение (N), затем микросхему СОЗУ с записанным во все ячейки значением 1 или 0 подвергают стрессовому воздействию путем воздействия повышенной температурой и напряжением (Vстресс) в течение периода времени Δt, причем способ реализуют посредством комбинации подсчета нестабильных бит и по крайней мере двух итераций стрессового воздействия и подсчета нестабильных бит, при этом после первого подсчета нестабильных бит инициализируют начальное количество нестабильных бит N0=N, после второго подсчета нестабильных бит считают приращенное количество нестабильных бит относительно первого подсчета первой итерации стресса ΔN1=N-N0, после третьего подсчета нестабильных бит считают общее приращенное количество нестабильных бит относительно второго подсчета после ΔN2=N-N0, затем вычисляют истинность выражения  истинность которого говорит о том, что микросхема СОЗУ «новая», а ложное значение - «использованная».

истинность которого говорит о том, что микросхема СОЗУ «новая», а ложное значение - «использованная».

2. Способ по п. 1, отличающийся тем, что период на который все биты СОЗУ последовательно вдоль линии слов переводят в режим чтения составляет 10 мс.

3. Способ по п. 1, отличающийся тем, что циклы стрессов ускоренного старения проходят при температуре 125°С.

4. Способ по п. 1, отличающийся тем, что Vстресс=Vном+1В.

5. Способ по п. 1, отличающийся тем, что выбранное значение записи оставляют неизменным для всех итераций подсчета нестабильных бит.

| CN 104810062 А, 29.07.2015 | |||

| CN 109725248 А, 07.05.2019 | |||

| CN 109765476 A, 17.05.2019 | |||

| Сталь | 1976 |

|

SU623900A1 |

| РАСПРЕДЕЛИТЕЛЬНЫЙ КЛАПАН | 0 |

|

SU180037A1 |

Авторы

Даты

2021-10-25—Публикация

2020-08-24—Подача