Изобретение относится к области автоматики и вычислительной техники и может быть использовано для научных исследований, в которых необходимо проведение моделирования состояния дискретного симметричного двоичного канала с памятью.

Устройство предназначено для имитационного моделирования состояния дискретного симметричного двоичного канала с памятью в условиях внешних воздействий, в том числе информационно-технических воздействий (ИТВ), а также для непосредственного расчета вероятности возникновения ошибок в канале связи, вызванных внешними воздействиями или ИТВ.

Известно устройство для моделирования системы связи (Патент РФ на полезную модель №191159, опубл. 25.07.2019, бюл. №21). Данное устройство позволяет осуществлять расчет характеристик качества информационного обмена в системах связи, функционирующих в режиме незакрепленных каналов. Однако в данном устройстве не учитываются влияние внешних воздействий на параметры каналов связи.

Известно устройство для моделирования канала связи со сжатием без потерь (Патент РФ на полезную модель №78383, опубл. 20.11.2008, бюл. №32). Данное устройство позволяет моделировать состояние двоичного симметричного канала связи со сжатием и получать условные вероятности ошибки для оценки помехоустойчивости алгоритмов декомпрессии.

Однако в данном устройстве не учтены параметры описывающие память канала, а также влияние дополнительных внешних воздействий (в том числе ИТВ) в совокупности с независимыми и группирующимися ошибками в канале связи.

Наиболее близким к предлагаемой полезной модели по технической реализации и выполняемым функциям аналогом (прототипом) является устройство для моделирования состояния канала связи (Патент РФ на полезную модель №214124, опубл. 12.10.2022, бюл. №29), включающее блок ввода информации, первый, второй, третий, четвертый и пятый регистры, реверсивный счетчик, первый, второй, третий и четвертый компараторы, генератор случайных чисел, блок элементов ИЛИ, первый и второй сумматоры, первый и второй блоки умножения, элемент задержки, первый и второй блоки элементов И, первый и второй блоки деления, накапливающий сумматор, блок отображения и выдачи результата, причем выходы блока ввода информации соединены со входами первого, второго, третьего, четвертого и пятого регистров, выход первого регистра параллельно соединен со входами реверсивного счетчика и второго блока деления, выходы второго, третьего, четвертого и пятого регистров соединены со входами первого, второго, третьего и четвертого компараторов соответственно, выходы реверсивного счетчика соединены со входами генератора случайных чисел и второго блока элементов И, выходы генератора случайных чисел соединены со входами первого, второго, третьего и четвертого компараторов, выходы первого, второго, третьего и четвертого компараторов соединены со входами блока элементов ИЛИ, выход первого компаратора параллельно соединен со входами первого сумматора и второго блока умножения, выход второго компаратора параллельно соединен со входами первого сумматора и первого блока умножения, выход третьего компаратора соединен со входом первого блока умножения, выход четвертого компаратора соединен со входом второго блока умножения, выход блока элементов ИЛИ соединен со входом реверсивного счетчика, выходы первого и второго блоков умножения соединены со входами второго сумматора, выходы первого и второго сумматоров через первый блок элементов И соединены со входами первого блока деления, выход первого блока элементов И через элемент задержки соединен со входом реверсивного счетчика, выход первого блока деления соединен со входом накапливающего сумматора, выход накапливающего сумматора соединен со входом второго блока элементов И, выход второго блока элементов И соединен со входом второго блока деления, выход второго блока деления соединен со входом блока отображения и выдачи результата.

Данное устройство позволяет осуществлять моделирование параметров канала связи, описывающих его состояние в условиях внешних воздействий, а также рассчитывать коэффициент ошибок в канале связи в условиях внешних воздействий.

Однако в данном устройстве не учтены параметры, описывающие группирование ошибок в канале связи.

Цель создания изобретения - создание технического средства, позволяющего повысить достоверность моделирования состояния

дискретного симметричного двоичного канала с памятью в условиях внешних воздействий и ИТВ, за счет учета дополнительного состояния канала связи, в котором происходит группирование ошибок.

В основе работы устройства-прототипа положена модель дискретного симметричного двоичного канала с памятью с глубиной памяти l=1 и числом состояний канала R=2 (модель Гильберта-Эллиота).

Динамика смены состояния канала связи в этом случае описана цепью Маркова, имеющей два состояния канала: «хорошее состояние» (G), в котором возникают ошибки, не связанные с внешними воздействиями (ИТВ), и «плохое состояние» (В), в котором ошибки обусловлены наличием внешнего воздействия (ИТВ). Вероятность ошибки в одном разряде составляет в состоянии (G) - Pε0, а в состоянии (B) - Pε1.

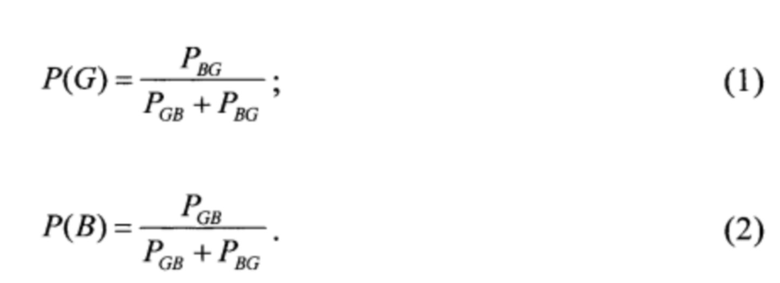

Вероятности пребывания канала в состояниях (G) и (В) представлены финальными вероятностями Марковской цепи:

Вероятность ошибки на символ в представленном канале с учетом (1) и (2) определяется по формуле:

В устройстве-прототипе реализовано имитационное моделирование параметров Pε0, Pε1, PGB, PBG, и последующий расчет вероятности возникновения ошибок в канале связи в соответствии с формулой (3).

В представленном новом устройстве использована усовершенствованная модель канала связи, характеризующаяся числом состояний канала R=3 (модель Смита-Боуэна-Джойса).

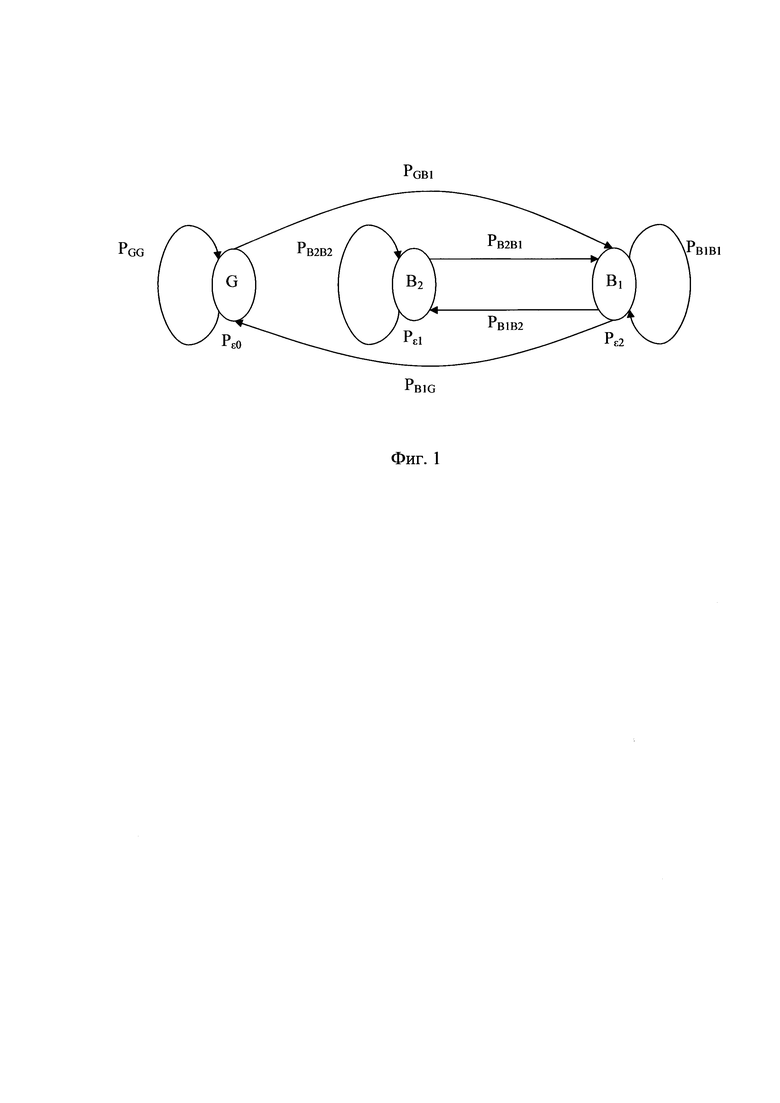

Динамика смены состояния данного канала связи описана цепью Маркова, имеющей три состояния канала: «хорошее состояние» (G), в котором возникают ошибки, не связанные с внешними воздействиями (ИТВ), «плохое состояние» (B1), в котором ошибки обусловлены наличием внешнего воздействия (ИТВ), «плохое состояние» (В2), в котором возникают группы ошибок (пакеты ошибок). Вероятности ошибок в одном разряде составляют в состоянии (G) - Pε0, в состоянии (B1) - Pε1, в состоянии (B2) - Pε2.

На рисунке фиг. 1 представлен граф переходов и состояний модели канала связи.

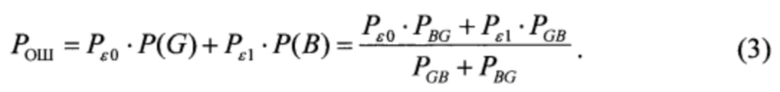

Матрица памяти (Мп) представленного графа имеет следующий вид:

Условие формирования пакетов ошибок в канале связи описывается неравенством:

PGB1<<PB2B1.

В представленном варианте состояние дискретного симметричного двоичного канала с памятью полностью описывается семью параметрами:

PGB1 - вероятность перехода канала связи из состояния возникновения ошибок, не связанных с внешними воздействиями (ИТВ), в состояние возникновения ошибок, обусловленных внешними воздействиями (ИТВ);

PB1G - вероятность перехода канала связи из состояния возникновения ошибок, обусловленных внешними воздействиями (ИТВ), в состояние возникновения ошибок, не связанных с внешними воздействиями (ИТВ);

PB1B2 - вероятность перехода канала связи из состояния возникновения ошибок, обусловленных внешними воздействиями (ИТВ), в состояние возникновения групп ошибок;

PB2B1 - вероятности перехода канала связи из состояния возникновения групп ошибок, в состояние возникновения ошибок, обусловленных внешними воздействиями (ИТВ);

Pε0 - вероятность возникновения ошибки в одном разряде сообщения в состоянии, возникновения ошибок, не связанных с внешними воздействиями (ИТВ);

Pε1 - вероятность возникновения ошибки в одном разряде сообщения в состоянии возникновения ошибок, обусловленных внешними воздействиями (ИТВ);

Pε2 - вероятность возникновения ошибки в одном разряде сообщения в состоянии, в котором возникают группы ошибок.

Эти параметры в устройстве определяются с помощью имитационного моделирования.

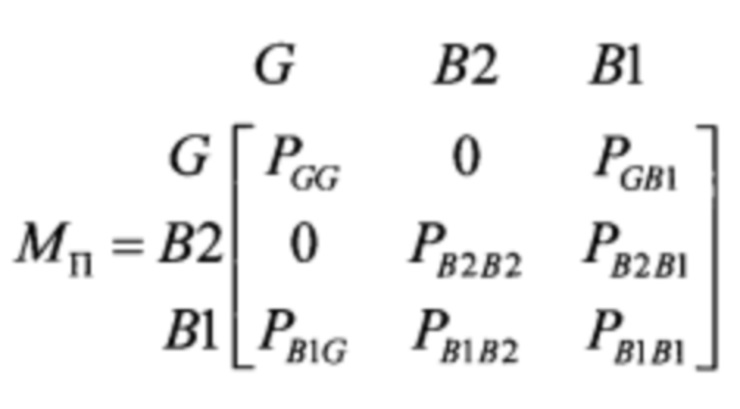

Вероятности пребывания канала в состояниях (G), (В1) и (В2) определяются как финальные вероятности Марковской цепи:

В представленном устройстве, как и в устройстве-прототипе принято допущение о том, что в различных состояниях памяти канала имеет место биномиальное распределение ошибок с соответствующей вероятностью ошибок.

Вероятность ошибки на символ в представленном канале связи с учетом (4), (5), (6) определяется по формуле:

В устройстве реализовано имитационное моделирование параметров Pε0, Pε1, Pε2, PG1B, PBG1, PG2B, PBG2, а также вычисление вероятности возникновения ошибок в канале связи в соответствии с формулой (7).

Технический результат, на достижение которого направлено изобретение заключается в расширении области применения устройства-прототипа за счет учета дополнительного состояния канала связи, описывающего группирование битовых ошибок.

Для достижения этого технического результата в известном устройстве для моделирования состояния канала связи, содержащем блок ввода информации, первый, второй, третий, четвертый и пятый регистры, реверсивный счетчик, первый, второй, третий и четвертый компараторы, генератор случайных чисел, блок элементов ИЛИ, первый и второй сумматоры, первый и второй блоки умножения, элемент задержки, первый и второй блоки элементов И, первый и второй блоки деления, накапливающий сумматор, блок отображения и выдачи результата, причем выходы блока ввода информации соединены со входами первого, второго, третьего, четвертого и пятого регистров, выход первого регистра параллельно соединен со входами реверсивного счетчика и второго блока деления, выходы второго, третьего, четвертого и пятого регистров соединены со входами первого, второго, третьего и четвертого компараторов соответственно, выходы реверсивного счетчика соединены со входами генератора случайных чисел и второго блока элементов И, выходы генератора случайных чисел соединены со входами первого, второго, третьего и четвертого компараторов, выходы первого, второго, третьего и четвертого компараторов соединены со входами блока элементов ИЛИ, выход первого компаратора параллельно соединен со входами первого сумматора и второго блока умножения, выход второго компаратора параллельно соединен со входами первого сумматора и первого блока умножения, выход третьего компаратора соединен со входом первого блока умножения, выход четвертого компаратора соединен со входом второго блока умножения, выход блока элементов ИЛИ соединен со входом реверсивного счетчика, выходы первого и второго блоков умножения соединены со входами второго сумматора, выходы первого и второго сумматоров через первый блок элементов И соединены со входами первого блока деления, выход первого блока элементов И через элемент задержки соединен со входом реверсивного счетчика, выход первого блока деления соединен со входом накапливающего сумматора, выход накапливающего сумматора соединен со входом второго блока элементов И, выход второго блока элементов И соединен со входом второго блока деления, выход второго блока деления соединен со входом блока отображения и выдачи результата дополнительно введены шестой, седьмой и восьмой регистры, пятый, шестой и седьмой компараторы, третий, четвертый и пятый сумматоры и третий блок умножения, причем шестой, седьмой и восьмой выходы блока ввода информации соединены с шестым, седьмым и восьмым регистрами соответственно, выходы генератора случайных чисел соединены со входами пятого, шестого и седьмого компараторов, выходы шестого, седьмого и восьмого регистров соединены со входами пятого, шестого и седьмого компараторов соответственно, выходы пятого, шестого и седьмого компараторов соединены со входами блока элементов ИЛИ, выход первого компаратора дополнительно соединен со входами третьего и четвертого сумматоров, выход второго компаратора дополнительно соединен со входами четвертого и пятого сумматоров, выход третьего компаратора параллельно соединен со входами первого, третьего и пятого сумматоров, выход четвертого компаратора параллельно соединен со входами первого, четвертого и пятого сумматоров, выходы пятого компаратора и пятого сумматора соединены со входами первого блока умножения, выходы шестого компаратора и четвертого сумматора соединены со входами второго блока умножения, выходы седьмого компаратора и третьего сумматора соединены со входами третьего блока умножения, выход третьего блока умножения соединен со входом второго сумматора.

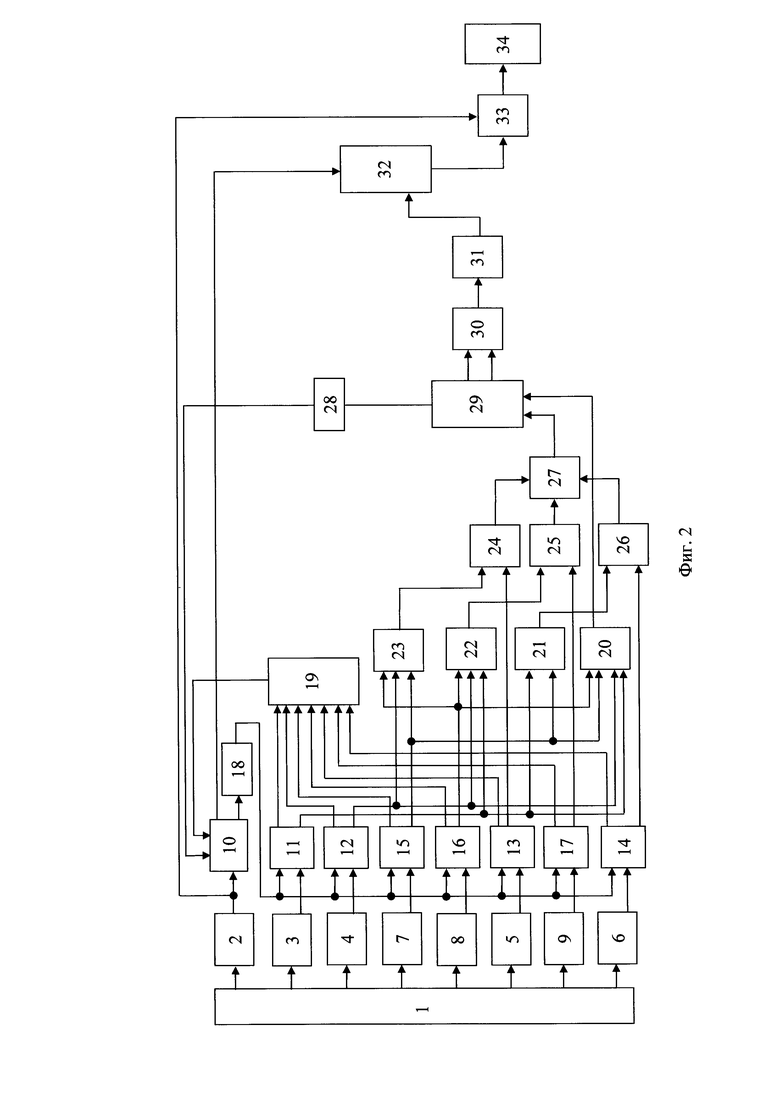

На рисунке фиг. 2 представлена структурная схема устройства.

Устройство содержит блок ввода информации 1, первый регистр 2, предназначенный для записи количества проводимых циклов моделирования, второй регистр 3, предназначенный для записи максимального значения вероятности перехода канала связи из состояния возникновения ошибок, не связанных с внешними воздействиями, в состояние возникновения ошибок, обусловленных внешними воздействиями, третий регистр 4, предназначенный для записи максимального значения вероятности перехода канала связи из состояния возникновения ошибок, обусловленных внешними воздействиями, в состояние возникновения ошибок, не связанных с внешними воздействиями, четвертый регистр 5, предназначенный для записи максимального значения вероятности возникновения ошибки в одном разряде сообщения в состоянии возникновения ошибок, не связанных с внешними воздействиями, пятый регистр 6, предназначенный для записи максимального значения вероятности возникновения ошибки в одном разряде сообщения в состоянии возникновения ошибок, обусловленных внешними воздействиями, шестой регистр 7, предназначенный для записи максимального значения вероятности перехода канала связи из состояния, возникновения групп ошибок, в состояние возникновения ошибок, обусловленных внешними воздействиями, седьмой регистр 8, предназначенный для записи максимального значения вероятности перехода канала связи из состояния возникновения ошибок, обусловленных внешними воздействиями, в состояние возникновения групп ошибок, восьмой регистр 9, предназначенный для записи максимального значения вероятности возникновения ошибки в одном разряде сообщения в состоянии возникновения групп ошибок, реверсивный счетчик количества проводимых циклов моделирования 10, первый компаратор 11, предназначенный для сравнения значения числа, поступившего с генератора случайных чисел и максимального значения вероятности перехода канала связи из состояния возникновения ошибок, не связанных с внешними воздействиями, в состояние возникновения ошибок, обусловленных внешними воздействиями, поступившего со второго регистра, второй компаратор 12, предназначенный для сравнения значения числа, поступившего с генератора случайных чисел и максимального значения вероятности перехода канала связи из состояния возникновения ошибок, обусловленных внешними воздействиями, в состояние возникновения ошибок, не связанных с внешними воздействиями, поступившего с третьего регистра, третий компаратор 13, предназначенный для сравнения значения числа, поступившего с генератора случайных чисел и максимального значения вероятности возникновения ошибки в одном разряде сообщения в состоянии возникновения ошибок, не связанных с внешними воздействиями, поступившего с четвертого регистра, четвертый компаратор 14, предназначенный для сравнения значения числа, поступившего с генератора случайных чисел и максимального значения вероятности возникновения ошибки в одном разряде сообщения в состоянии возникновения ошибок, обусловленных внешними воздействиями, поступившего с пятого регистра, пятый компаратор 15, предназначенный для сравнения значения числа, поступившего с генератора случайных чисел и максимального значения вероятности перехода канала связи из состояния, возникновения групп ошибок, в состояние возникновения ошибок, обусловленных внешними воздействиями, поступившего с шестого регистра, шестой компаратор 16, предназначенный для сравнения значения числа, поступившего с генератора случайных чисел и максимального значения вероятности перехода канала связи из состояния возникновения ошибок, обусловленных внешними воздействиями, в состояние возникновения групп ошибок, поступившего с седьмого регистра, седьмой компаратор 17, предназначенный для сравнения значения числа, поступившего с генератора случайных чисел и максимального значения вероятности возникновения ошибки в одном разряде сообщения в состоянии возникновения групп ошибок, поступившего с восьмого регистра, генератор случайных чисел 18, блок элементов ИЛИ 19, первый, второй, третий, четвертый и пятый сумматоры 20, 27, 21-23, первый, второй и третий блоки умножения 24-26, элемент задержки 28, первый и второй блоки элементов И 29, 32, первый и второй блоки деления 30, 33, накапливающий сумматор 31, блок отображения и выдачи результата 34.

Выходы блока ввода информации 1 соединены со входами первого, второго, третьего, четвертого, пятого, шестого, седьмого и восьмого регистров 2-9, выход первого регистра 2 параллельно соединен со входами реверсивного счетчика 10 и второго блока деления 33, выходы второго, третьего, четвертого и пятого регистров 3-6 соединены со входами первого, второго, третьего и четвертого компараторов 11-14 соответственно, выходы шестого, седьмого и восьмого регистров 7-9 соединены со входами пятого, шестого и седьмого компараторов 15-17 соответственно, выходы реверсивного счетчика 10 соединены со входами генератора случайных чисел 18 и второго блока элементов И 32, выходы генератора случайных чисел 18 соединены со входами первого, второго, третьего, четвертого, пятого, шестого и седьмого компараторов 11-17, выходы первого, второго, третьего, четвертого, пятого, шестого и седьмого компараторов 11-17 соединены со входами блока элементов ИЛИ 19, выход первого компаратора 11 параллельно соединен со входами первого, третьего и четвертого сумматоров 20, 21, 22, выход второго компаратора 12 параллельно соединен со входами первого, четвертого и пятого сумматоров 20, 22, 23, выход третьего компаратора 13 соединен со входом первого блока умножения 24, выход четвертого компаратора 14 соединен со входом третьего блока умножения 26, выход пятого компаратора 15 параллельно соединен со входами первого, третьего и пятого сумматоров 20, 21, 23, выход шестого компаратора 16 параллельно соединен со входами первого, четвертого и пятого сумматоров 20, 22, 23, выход пятого сумматора 23 соединен со входом первого блока умножения 24, выходы седьмого компаратора 17 и четвертого сумматора 22 соединены со входами второго блока умножения 25, выход третьего сумматора 21 соединен со входом третьего блока умножения 26, выход блока элементов ИЛИ 19 соединен со входом реверсивного счетчика 10, выходы первого, второго и третьего блоков умножения 24, 25, 26 соединены со входами второго сумматора 27, выходы первого и второго сумматоров 20, 27 через первый блок элементов И 29 соединены со входами первого блока деления 30, выход первого блока элементов И 29 через элемент задержки 28 соединен со входом реверсивного счетчика 10, выход первого блока деления 30 соединен со входом накапливающего сумматора 31, выход накапливающего сумматора 31 соединен со входом второго блока элементов И 32, выход второго блока элементов И 32 соединен со входом второго блока деления 33, выход второго блока деления 33 соединен со входом блока отображения и выдачи результата 34.

Устройство функционирует следующим образом.

С помощью блока ввода информации 1, представляющего собой наборное поле, устанавливаются значения первого, второго, третьего, четвертого, пятого, шестого, седьмого и восьмого регистров 2-9. В первый регистр 2 записывается значение количества проводимых циклов моделирования, во второй регистр 3 записывается максимальное значение вероятности PB1G, в третий регистр 4 записывается максимальное значение вероятности PBG1, в четвертый регистр 5 записывается максимальное значение вероятности Pε0, в пятый регистр 6 записывается максимальное значение вероятности Pε1, в шестой регистр 7 записывается максимальное значение вероятности PB2B1, в седьмой регистр 8 записывается максимальное значение вероятности PB1B2, в восьмой регистр 9 записывается максимальное значение вероятности Pε2. С первого регистра 2 данные о количестве проводимых циклов моделирования поступают на реверсивный счетчик 10 и на второй блок деления 33 в качестве делителя. С реверсивного счетчика 10 поступает сигнал на вход генератора случайных чисел 18, при этом значение реверсивного счетчика 10 уменьшается на единицу. С генератора случайных чисел 18 данные поступают на входы первого, второго, третьего, четвертого, пятого, шестого и седьмого компараторов 11-17. Со второго регистра 3 данные поступают на вход первого компаратора 11. В случае, когда максимальное значение вероятности PGB1, поступившее со второго регистра 3, окажется больше значения числа, поступившего с генератора случайных чисел 18, первый компаратор 11 выдает данное значение на первый, третий и четвертый сумматоры 20, 21, 22. В случае, когда максимальное значение вероятности PGB1, поступившее со второго регистра 3, окажется меньше значения числа, поступившего с генератора случайных чисел 18, первый компаратор 11 выдает сигнал на блок элементов ИЛИ 19. С третьего регистра 4 данные поступают на вход второго компаратора 12. В случае, когда максимальное значение вероятности PB1G, поступившее с третьего регистра 4, окажется больше значения числа, поступившего с генератора случайных чисел 18, второй компаратор 12 выдает данное значение на первый, четвертый и пятый сумматоры 20, 22, 23. В случае, когда максимальное значение вероятности PB1G, поступившее с третьего регистра 4, окажется меньше значения числа, поступившего с генератора случайных чисел 18, второй компаратор 12 выдает сигнал на второй блок элементов ИЛИ 19. С четвертого регистра 5 данные поступают на вход третьего компаратора 13. В случае, когда максимальное значение вероятности Pε0, поступившее с четвертого регистра 5, окажется больше значения числа, поступившего с генератора случайных чисел 18, третий компаратор 13 выдает данное значение на первый блок умножения 24. В случае, когда максимальное значение вероятности Pε0, поступившее с четвертого регистра 5, окажется меньше значения числа, поступившего с генератора случайных чисел 18, третий компаратор 13 выдает сигнал на блок элементов ИЛИ 19. С пятого регистра 6 данные поступают на вход четвертого компаратора 14. В случае, когда максимальное значение вероятности Pε1, поступившее с пятого регистра 6, окажется больше значения числа, поступившего с генератора случайных чисел 18, четвертый компаратор 14 выдает данное значение на третий блок умножения 26. В случае, когда максимальное значение вероятности Pε1, поступившее с пятого регистра 6, окажется меньше значения числа, поступившего с генератора случайных чисел 18, четвертый компаратор 14 выдает сигнал на блок элементов ИЛИ 19.

С шестого регистра 7 данные поступают на вход пятого компаратора 15. В случае, когда максимальное значение вероятности PB2B1, поступившее с шестого регистра 7, окажется больше значения числа, поступившего с генератора случайных чисел 18, пятый компаратор 15 выдает данное значение на первый, третий и пятый сумматоры 20, 21, 23. В случае, когда максимальное значение вероятности PB2B1, поступившее с шестого регистра 7, окажется меньше значения числа, поступившего с генератора случайных чисел 18, пятый компаратор 15 выдает сигнал на блок элементов ИЛИ 19. С седьмого регистра 8 данные поступают на вход шестого компаратора 16. В случае, когда максимальное значение вероятности PB1B2, поступившее с седьмого регистра 8, окажется больше значения числа, поступившего с генератора случайных чисел 18, шестой компаратор 16 выдает данное значение на первый, четвертый и пятый сумматоры 20, 22, 23. В случае, когда максимальное значение вероятности PB2B1, поступившее с седьмого регистра 8, окажется меньше значения числа, поступившего с генератора случайных чисел 18, шестой компаратор 16 выдает сигнал на блок элементов ИЛИ 19. С восьмого регистра 9 данные поступают на вход седьмого компаратора 17. В случае, когда максимальное значение вероятности Pε2, поступившее с восьмого регистра 9, окажется больше значения числа, поступившего с генератора случайных чисел 18, седьмой компаратор 17 выдает данное значение на второй блок умножения 25. В случае, когда максимальное значение вероятности, поступившее с восьмого регистра 9, окажется меньше значения числа, поступившего с генератора случайных чисел 18, седьмой компаратор 17 выдает сигнал на блок элементов ИЛИ 19.

При поступлении на блок элементов ИЛИ 19 сигналов с первого, второго, третьего, четвертого, пятого, шестого или седьмого компараторов 11-17 блок элементов ИЛИ 19 выдает сигнал на реверсивный счетчик 10, при этом значение реверсивного счетчика 10 увеличивается на единицу.

С третьего, четвертого и пятого сумматоров 21, 22, 23 данные поступают на третий, второй и первый блоки умножения 26, 25, 24 соответственно. С первого, второго и третьего блоков умножения 24, 25, 26 данные поступают на второй сумматор 27. С первого и второго сумматоров 20, 27 данные поступают через первый блок элементов И 29 на первый блок деления 30 в качестве делителя и делимого соответственно, при этом первый блок элементов И 29 выдает сигнал через элемент задержки 28 на реверсивный счетчик 10, после чего реверсивный счетчик 10 посылает сигнал на генератор случайных чисел 18 и начинается новый цикл моделирования. С первого блока деления 30 данные поступают на накапливающий сумматор 31. При возникновении ситуации, когда значение реверсивного счетчика 10 становится равным нулю реверсивный счетчик 10 посылает положительный сигнал на второй блок элементов И 32, при этом данные с накапливающего сумматора 31 через второй блок элементов И 32 поступают на второй блок деления 33 в качестве делимого. Со второго блока деления 33 данные поступают на блок отображения и выдачи результата 34.

Таким образом, в результате функционирования устройства на блоке отображения и выдачи результата имеем усредненное значение вероятности возникновения ошибки на символ в представленном канале РОШ, полученное с учетом дополнительных параметров, описывающих состояние канала связи, в котором возникают группы ошибок. Полученное вероятностное значение достаточно полно описывает состояние дискретного симметричного двоичного канала с памятью.

Следовательно, поставленная цель - создание технического средства, позволяющего повысить достоверность моделирования состояния дискретного симметричного двоичного канала с памятью в условиях внешних воздействий и ИТВ за счет учета дополнительного состояния канала связи, в котором происходит группирование ошибок, - достигнута.

Заявленное изобретение является техническим решением, относящимся к устройству, т.к. формула изобретения содержит совокупность относящихся к устройству существенных признаков (а именно, перечень используемых элементов и связей между ними) достаточную для решения указанной задачи и достижения технического результата. Приведенные признаки относятся к существенным, т.к. они влияют на возможность получения технического результата, т.е. находятся в причинно-следственной связи с указанным результатом. Отсутствие одного или нескольких признаков приведет к неработоспособности устройства и не позволит получить заявленный результат.

Реализация и использование предлагаемого изобретения позволяет проводить моделирование состояния дискретного симметричного двоичного канала с памятью на основе имитационного моделирования параметров канала связи, описывающих его состояние в условиях внешних воздействий, в том числе и ИТВ, а также проводить оценку вероятностных характеристик, характеризующих наличие ошибок в канале связи в условиях внешних воздействий и ИТВ.

Технический результат данного изобретения заключается в том, что при реализации и использовании данного устройства обеспечивается повышение достоверности моделирования состояния дискретного симметричного двоичного канала с памятью в условиях внешних воздействий и ИТВ за счет расширения технических характеристик устройства-прототипа, позволяющих учитывать ряд параметров, описывающих дополнительное состояние канала связи, в котором возникают группы ошибок в различных условиях функционирования.

Описанное устройство может быть реализовано с применением известных в области радиоэлектроники узлов и блоков, соединенных между собой, обеспечивающих конструктивное и функциональное единство.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для моделирования деятельности человека-оператора | 1990 |

|

SU1778761A1 |

| УСТРОЙСТВО ДЛЯ МОДЕЛИРОВАНИЯ СИСТЕМЫ СВЯЗИ | 2005 |

|

RU2286597C1 |

| Устройство для моделирования случайных блужданий | 1981 |

|

SU999063A1 |

| УСТРОЙСТВО ДЛЯ МОДЕЛИРОВАНИЯ СИСТЕМ ПЕРЕДАЧИ ДАННЫХ | 1991 |

|

RU2011219C1 |

| Многофункциональный цифровой коррелометр | 1986 |

|

SU1363246A1 |

| Генератор случайных чисел | 1981 |

|

SU980093A1 |

| Устройство прогнозирования работоспособности радиоэлектронной аппаратуры | 1987 |

|

SU1422196A2 |

| Устройство для определения рациональной программы технического обслуживания и эксплуатации изделия | 2019 |

|

RU2728955C1 |

| Устройство для моделирования деятельности человека-оператора | 1987 |

|

SU1432553A1 |

| Устройство для определения рациональной программы технического обслуживания и эксплуатации изделия | 2018 |

|

RU2701484C1 |

Изобретение относится к области автоматики и вычислительной техники. Технический результат данного изобретения заключается в повышении достоверности моделирования состояния канала связи в условиях внешних воздействий за счет учета дополнительного состояния канала связи. Технический результат достигается за счет того, что в устройство введены дополнительные регистры, предназначенные для записи максимального значения вероятности перехода канала связи в состояние возникновения групп ошибок, для записи максимального значения вероятности перехода канала связи в состояние возникновения групп ошибок и для записи максимального значения вероятности возникновения ошибки в одном разряде сообщения в состоянии возникновения групп ошибок; компараторы, сумматоры, связанные между собой для вычисления оценки вероятности перехода канала связи в состояние возникновения групповой ошибки. 2 ил.

Устройство для моделирования состояния канала связи, включающее блок ввода информации, первый регистр, предназначенный для записи количества проводимых циклов моделирования, второй регистр, предназначенный для записи максимального значения вероятности перехода канала связи из состояния возникновения ошибок, не связанных с внешними воздействиями, в состояние возникновения ошибок, обусловленных внешними воздействиями, третий регистр, предназначенный для записи максимального значения вероятности перехода канала связи из состояния возникновения ошибок, обусловленных внешними воздействиями, в состояние возникновения ошибок, не связанных с внешними воздействиями, четвертый регистр, предназначенный для записи максимального значения вероятности возникновения ошибки в одном разряде сообщения в состоянии возникновения ошибок, не связанных с внешними воздействиями, пятый регистр, предназначенный для записи максимального значения вероятности возникновения ошибки в одном разряде сообщения в состоянии возникновения ошибок, обусловленных внешними воздействиями, реверсивный счетчик количества проводимых циклов моделирования, генератор случайных чисел, первый компаратор, предназначенный для сравнения значения числа, поступившего с генератора случайных чисел и максимального значения вероятности перехода канала связи из состояния возникновения ошибок, не связанных с внешними воздействиями, в состояние возникновения ошибок, обусловленных внешними воздействиями, поступившего со второго регистра, второй компаратор, предназначенный для сравнения значения числа, поступившего с генератора случайных чисел и максимального значения вероятности перехода канала связи из состояния возникновения ошибок, обусловленных внешними воздействиями, в состояние возникновения ошибок, не связанных с внешними воздействиями, поступившего с третьего регистра, третий компаратор, предназначенный для сравнения значения числа, поступившего с генератора случайных чисел и максимального значения вероятности возникновения ошибки в одном разряде сообщения в состоянии возникновения ошибок, не связанных с внешними воздействиями, поступившего с четвертого регистра, четвертый компаратор, предназначенный для сравнения значения числа, поступившего с генератора случайных чисел и максимального значения вероятности возникновения ошибки в одном разряде сообщения в состоянии возникновения ошибок, обусловленных внешними воздействиями, поступившего с пятого регистра, блок элементов ИЛИ, первый и второй сумматоры, первый и второй блоки умножения, элемент задержки, первый и второй блоки элементов И, первый и второй блоки деления, накапливающий сумматор, блок отображения и выдачи результата, причем выходы блока ввода информации соединены со входами первого, второго, третьего, четвертого и пятого регистров, выход первого регистра параллельно соединен со входами реверсивного счетчика и второго блока деления, выходы второго, третьего, четвертого и пятого регистров соединены со входами первого, второго, третьего и четвертого компараторов соответственно, выходы реверсивного счетчика соединены со входами генератора случайных чисел и второго блока элементов И, выходы генератора случайных чисел соединены со входами первого, второго, третьего и четвертого компараторов, выходы первого, второго, третьего и четвертого компараторов соединены со входами блока элементов ИЛИ, выход первого компаратора соединен со входом первого сумматора, выход второго компаратора соединен со входом первого сумматора, выход блока элементов ИЛИ соединен со входом реверсивного счетчика, выходы первого и второго блоков умножения соединены со входами второго сумматора, выходы первого и второго сумматоров через первый блок элементов И соединены со входами первого блока деления, выход первого блока элементов И через элемент задержки соединен со входом реверсивного счетчика, выход первого блока деления соединен со входом накапливающего сумматора, выход накапливающего сумматора соединен со входом второго блока элементов И, выход второго блока элементов И соединен со входом второго блока деления, выход второго блока деления соединен со входом блока отображения и выдачи результата, отличающееся тем, что в устройство введены шестой регистр, предназначенный для записи максимального значения вероятности перехода канала связи из состояния, возникновения групп ошибок, в состояние возникновения ошибок, обусловленных внешними воздействиями, седьмой регистр, предназначенный для записи максимального значения вероятности перехода канала связи из состояния возникновения ошибок, обусловленных внешними воздействиями, в состояние возникновения групп ошибок, восьмой регистр, предназначенный для записи максимального значения вероятности возникновения ошибки в одном разряде сообщения в состоянии возникновения групп ошибок, пятый компаратор, предназначенный для сравнения значения числа, поступившего с генератора случайных чисел и максимального значения вероятности перехода канала связи из состояния возникновения групп ошибок, в состояние возникновения ошибок, обусловленных внешними воздействиями, поступившего с шестого регистра, шестой компаратор, предназначенный для сравнения значения числа, поступившего с генератора случайных чисел и максимального значения вероятности перехода канала связи из состояния возникновения ошибок, обусловленных внешними воздействиями, в состояние возникновения групп ошибок, поступившего с седьмого регистра, седьмой компаратор, предназначенный для сравнения значения числа, поступившего с генератора случайных чисел и максимального значения вероятности возникновения ошибки в одном разряде сообщения в состоянии возникновения групп ошибок, поступившего с восьмого регистра, третий, четвертый и пятый сумматоры, третий блок умножения, причем шестой, седьмой и восьмой выходы блока ввода информации соединены с шестым, седьмым и восьмым регистрами соответственно, выходы генератора случайных чисел соединены со входами пятого, шестого и седьмого компараторов, выходы шестого, седьмого и восьмого регистров соединены со входами пятого, шестого и седьмого компараторов соответственно, выходы пятого, шестого и седьмого компараторов соединены со входами блока элементов ИЛИ, выход первого компаратора дополнительно соединен со входами третьего и четвертого сумматоров, выход второго компаратора дополнительно соединен со входами четвертого и пятого сумматоров, выход третьего компаратора дополнительно соединен со входом первого блока умножения, выход пятого компаратора параллельно соединен со входами первого, третьего и пятого сумматоров, выход шестого компаратора параллельно соединен со входами первого, четвертого и пятого сумматоров, выход пятого сумматора соединен со входом первого блока умножения, выходы седьмого компаратора и четвертого сумматора соединены со входами второго блока умножения, выходы четвертого компаратора и третьего сумматора соединены со входами третьего блока умножения, выход третьего блока умножения соединен со входом второго сумматора.

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ЗНАЧЕНИЯ ХАРАКТЕРИСТИК ГОТОВНОСТИ ИЗДЕЛИЯ К ПРИМЕНЕНИЮ | 2014 |

|

RU2580099C2 |

| СПОСОБ РЕНТГЕНОДИАГНОСТИКИ ЗАБОЛЕВАНИЙ СЛЮННЫХ ЖЕЛЕЗ (ПНЕВМОСУБМАНДИБУЛОГРАФИИ) | 0 |

|

SU213254A1 |

| УСТРОЙСТВО для ОЦЕНКИ КАЧЕСТВА СВОБОДНОГО КАНАЛА ПЕРЕДАЧИ ДИСКРЕТНОЙ ИНФОРМАЦИИ | 0 |

|

SU220305A1 |

| US 11258674 B1, 22.02.2022 | |||

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ОБЪЕМНОЙ СКОРОСТИ КРОВОТОКА В АППАРАТУРЕ ИСКУССТВЕННОГО КРОВООБРАЩЕНИЯ | 1967 |

|

SU214124A1 |

Авторы

Даты

2025-04-16—Публикация

2024-05-03—Подача