(Л

С

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для моделирования конечных автоматов | 1980 |

|

SU955080A1 |

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1984 |

|

SU1254495A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ПАМЯТЬЮ | 1993 |

|

RU2037874C1 |

| Устройство для умножения полиномов многих переменных | 1980 |

|

SU922732A1 |

| Устройство для контроля | 1981 |

|

SU1072052A1 |

| Устройство для моделирования деятельности человека-оператора | 1986 |

|

SU1377870A1 |

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1989 |

|

SU1702377A1 |

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1984 |

|

SU1288704A1 |

| Коррелометр | 1980 |

|

SU1062717A1 |

| Устройство для контроля и диагностики дискретных объектов | 1980 |

|

SU942025A1 |

Изобретение относится к вычислительной технике, з частности к устройствам для моделирования деятельности человека-оператора системы человек-машина. Цель изобретения - расширение функциональных возможностей устройства за счет моделирования отказов и восстановления техники. Для достижения указанной цели устройство дополнительно содержит пятый, шестой и седьмой элементы И, две группы элементов И, две группы элементов ИЛИ и блок моделирования отказов, содержащий два блока памяти, два регистра вывода информации, комбинационный сумматор, два триггера, два регистра адреса, генератор случайных чисел, счетчик, схему сравнения, семь элементов И, шесть элементов ИЛИ и пять элементов задержки Устройство позволяет априорно оценить показатели качества деятельности человека-оператора в системе человек-машина 2 ил

l/l3o6peTet ие относится к вычислительной технике, в частности к устройствам для моделирована деятельности человека-оператора системы человек-машина и может быть использовано для статических исследований показателей качества операторской деятельности.

Цель изобретения - расширение функциональных возможностей устройства за счет моделирования отказов и восстановления техники.

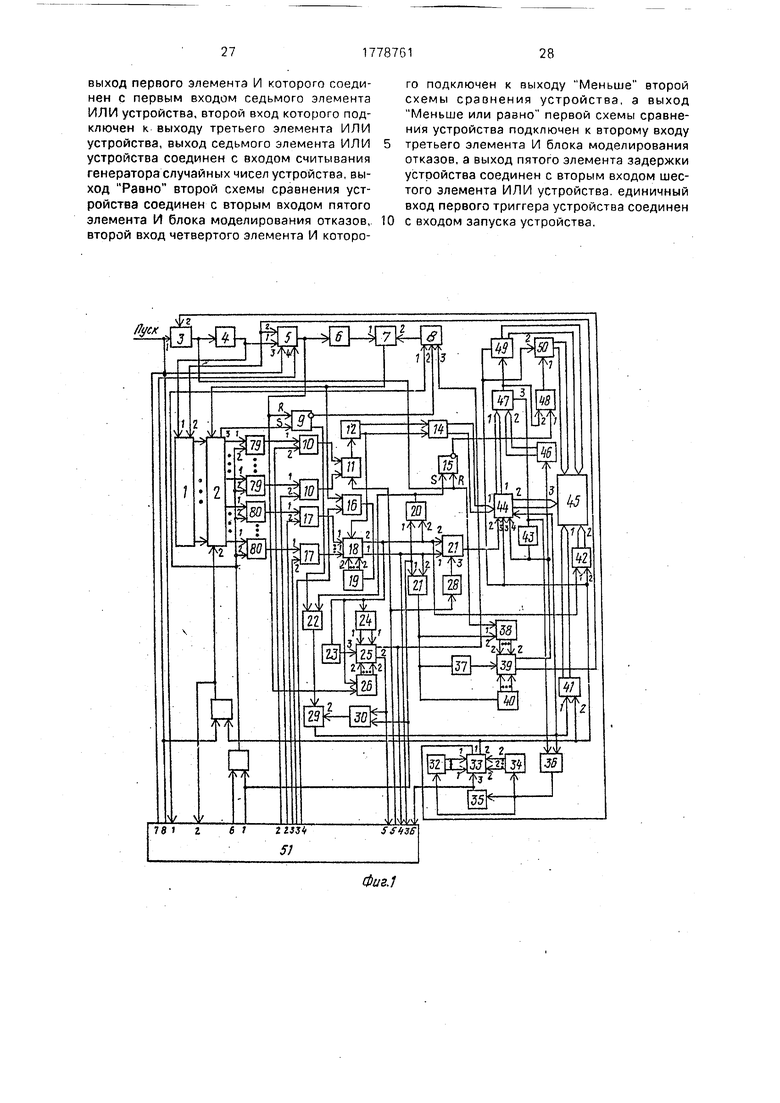

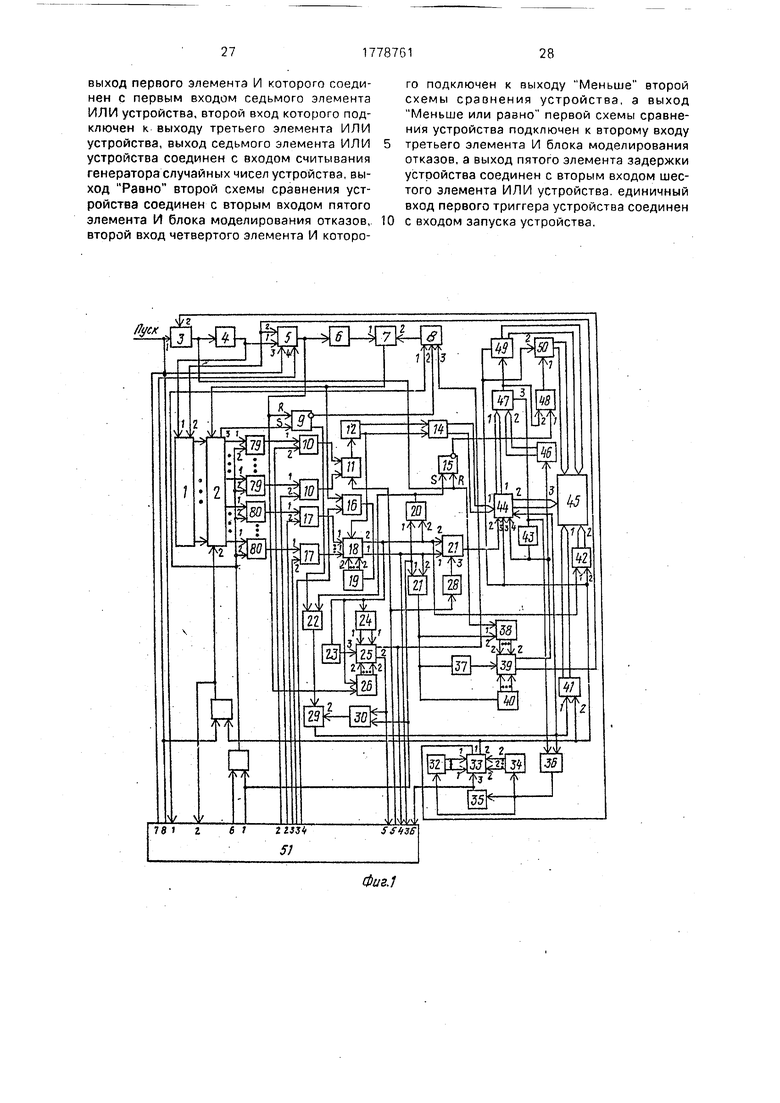

На фиг. 1 т эиведена структурная схема устройства. Устройство содержит: блок памяти 1, регистэ 2 вывода информации, первый элемент ИЛИ 3, первый элемент 4 задержки, второй элемент ИЛИ 5, второй элемент 6 задержки, третий элемент ИЛИ 7, первый элеме г И 8, второй триггер 9. первую группу эле иентов ИЛИ 10, генератор 11 импульсов со случайной деятельностью,

дифференцирующий элемент 12, преобразователь 14 временной интервал - код, третийтриггер 15, седьмой элемент ИЛИ 16, вторую группу элементов ИЛИ 17, первую схему 18 сравнения, генератор 19 случайных чисел, пятый элемент И 20, четвертый элемент ИЛИ 21, четвертый элемент И 22, третий элемент 23 задержки, регистр 24 установленного числа повторений операции, вторую схему сравнения 25, первый счетчик 26 ошибок, шестой элемент И 27, седьмой элемент 28 задержки, пятый элемент ИЛИ 29, второй элемент И 30, первый триггер 31, регистр 32 числа реализации, пятую схему сравнения 33, счетчик 34 реализаций, шестой элемент 35 задержки, шестой элемент ИЛИ 36, четвертый элемент задержки 37, счетчик 38 операций, третью схему 39 сравнения, регистр 40 операций алгоритма, счетчик 41 незавершенных реализаций втоU

0

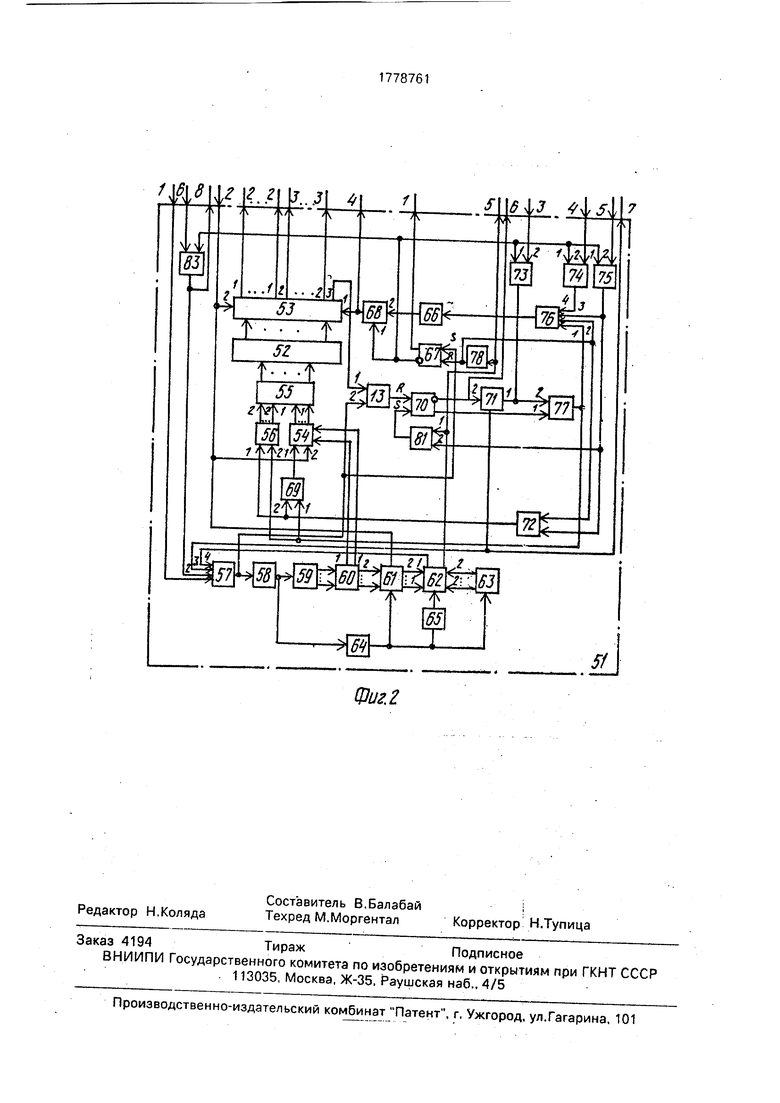

рой счетчик 42 ошибок, пятый элемент 43 задержки, накапливающий сумматор 44 времени, блок 45 регистрации, регистр 46 нормативного времени, четвертую схему 47 сравнения, третий элемент И 48, счетчик 49 своевременно выполненных реализаций, счетчик 50 своевременно и безошибочно выполненных реализаций первую 79 и вторую 80 группы элемэнтов И, седьмой элемент И 82,блок 51 моделирования отказов, содержащий (фиг. 2), второй блок 52 памяти, второй регистр 53 вывода информации, второй регистр адреса 54, комбинационный сумматор 55, счетчик операций 56 устранения отказов/первый элемент ИЛИ 57, первый элемент 58 задержки, первый регистр 59 адреса возможных неисправностей, первый блок 60 памяти, первый регистр 61 вывода информации, схему сравнения 62, второй генератор 63 случайных чисел, второй 64, третий 65 и пятый 66 элементы задержки, первый триггер 67, первый элемент И 68, шестой элемент ИЛИ 69, второй 70 триггер, седьмой элемент И 71, пятый элемент ИЛИ 72, третий 73, четвертый 74 и пятый 75 элементы И, четвертый элемент ИЛИ 76, шестой элемент И 77, четвертый элемент 78 задержки, второй элемент ИЛИ 13, третий элемент ИЛИ 81, второй элемент И 83.

Блок 1 памяти предназначен для хранения характеристик операций алгоритма. Блок имеет зону хранения значений математического ожидания mtj и среднеквадра- тического отклонения Gti времени выполнения операций, зону хранения значений вероятности безошибочного выполнения операций PJ и зону хранения признака операций: признак сенсорной операции - в виде 1, признак сенсомо- торной операции - в виде О. Управляющая составляющая моделируемого алгоритма характеризуется порядком следования операции алгоритма совместно с их признаком.

Регистр 2 вывода информации осуществляет прием из первого блока памяти, выдачу на обработку характеристик очередной операции и их хранение до перехода к моделированию следующей операции или к началу новой реализации.

Генератор 11 импульсов со случайной деятельностью, получив значение математического ожидания mti и среднеквадрати- ческого отклонения Gti. вырабатывает последовательность импульсов, длительность которой пропорционально времени Дц выполнения 1-й операции.

Дифференцируемый элемент 12 формирует импульс Начало, соответствующий

началу поступления очередной последовательности импульсов от генератора 11, и импульс Конец, соответствующий окончанию последовательности.

Преобразователь временной интервал код 14 формирует двоичное число, пропорциональное времени Дп, соответствующее длительности последовательности импульсов, выработанной генератором 11.

Первая схема 18 сравнения производит сравнение поступившего из блока 1 памяти значения вероятности PI безошибочно выполненной операции с случайным числом Xri, выработанным генератором 19 случайных чисел. Результат сравнения - импульс на одном из выходов. Операция считается выполненной, если Хн Pi, и наблюдается ошибка, если .

Регистр 24 установленного числа повторений операции предназначен для хранения и выдачи после каждой допущенной ошибки для сравнения введенного заранее числа, соответствующего допустимому числу повторений одной и той же операции Пд.

Вторая схема 25 сравнения сравнивает количество допущенных при выполнении данной операции ошибок п, подсчитываемое первым счетчиком 26 ошибок, со значением Пд установленного числа повторений.

При разрешается повторение той же операции, при повторение запрещается и реализация алгоритма прерывается. Результат сравнения - импульс на одном из выходов схемы.

Регистр 32 числа реализаций предназначен для хранения и выдачи после завершения или прерывания очередной реализации введенного заранее ту, запланированного в данном опыте числа реализаций алгоритма.

Пятая схема 33 сравнения осуществляет сравнение числа m выполненных и прерванных на данный момент реализаций, фиксируемого счетчика 34 с установленным в регистре 32 числом реализаций ту. Результатом сравнения является импульс на одном из выходов схемы 33, при или импульс на другом выходе при .

Третья схема 39 сравнения предназначена для сравнения числа k выполненных

операций в текущей реализации, формируемого счетчиком 38 операций, с установленным числом kp операций в моделируемом алгоритме из регистра 40 числа операций. Результат сравнения - импульс на одном из

выходов схемы 39 при и импульс на другом выходе при ,

Счетчик 41 подсчитывает количество прерванных из-за ошибочных действий оператора реализаций алгоритма.

Второй счетчик 42 ошибок подсчитывает общее число ошибок во всем комплексе запланированного числа реализаций алгоритма.

Накапливающий сумматор 44 фиксирует значение времени выполнения последней i-й операции Ati (независимо от правильности ее выполнения), суммирует его с значением времени, затраченного на выполнение всех предыдущих (1-1) операций текущей реализации НП

ti Ati + DFAtj + 2) Atij.

где Atij - время, затраченное на осуществление lj-того повторения j-й операции, в которой допущена ошибка, nj - число ошибочных повторений j-той операции до ее правильного выполнения, выдает получаемое значение времени выполнения данной реализации после ее полного завершения в четвертую схему 47 сравнения для сравнения с значением нормативного времени, суммирует значение всех полностью завершенных реализаций и выдает его в блок регистрации 45 после полного завершения всей процедуры.

Блок регистрации 45 формирует после завершения процедуры общее число допущенных ошибок, число прерванных реализаций, значение суммарного времени выполнения завершенных реализаций, число своевременно выполненных реализаций, число своевременно и безошибочно выполненных реализаций.

Регистр 46 нормативного времени содержит введенное заранее значение нормативного времени выполнения реализации алгоритма и выдает его для соавнения но сигналу 0 завершении данной реализации.

Четвертая схема 47 сравнения предназначена для сравнения значения времени затраченного на выполнение данной реализации алгоритма с нормативным значением из регистра 46 нормативного времени. Результат сравнения - импульсный сигнал на выходе схемы, если время выполнения реализации меньше или равно нормативному.

Второй блок памяти 52 предназначен для хранения характеристик выполнения операций алгоритмов устранения неисправностей ггц1,;, Gtp, Pp аналогичных характеристикам операций основного алгоритма управления в первом блоке 1 памяти, а также признака окончания алгоритма. Блок 52 содержит характеристики нескольких алгоритмов, что позволяет моделировать алгоритмы устранения различных неисправностей.

Второй регистр 53 вывода информации обеспечивает хранение характеристик очередной операции устранения неисправностей, до правильного завершения этой

операции и выдачу их для ее моделирования, Ввод информации разрешается постоянно без дополнительных команд.

Второй регистр 54 адреса предназначен для хранения адреса первой операции

0 алгоритма устранения неисправности и выдачу его во второй сумматор 55.

Сумматор 55 служит для суммирования адреса первой операции алгоритма неисправности с номером очередной операции

5 устранения неисправности, выдаваемым счетчиком 56 операций устранения неисправностей и для выдачи полученного результата на адресные входы блока памяти 52. Первый регистр 59 адреса возможных

0 неисправностей предназначен для поочередного обращения к ячейкам 60 памяти для вывода значений адреса и вероятности возникновения неисправности на дальнейшую обработку.

5Первый блок памяти 60 предназначен

для хранения численных значений адресов и вероятностей, QJV появления различных неисправностей технической части $ АСУ. Максимальное количество предполагаемых

0 неисправностей должно соответствовать числу предусмотренных алгоритмов устранения неисправностей в виде соответствующих комплектов характеристик во втором блоке 52 памяти.

5Регистр 59 адреса возможных неисправностей предназначен для поочередного обращения к ячейкам 60 памяти для вывода значений вероятности возникновения неисправности на дальнейшую обработку,

0Первый регистр 61 вывода информации

предназначен для хранения очередного значения вероятности возникновения неисправности и выдачи его на шестую схему 62 сравнения,

5 Схема 62 сравнения предназначена для сравнения очередного значения вероятности неисправности с случайным числом от второго генератора 63 случайных чисел УгЛ. При выполнении условия Yr# Q// техниче0 екая часть АСУ считается исправной. При исходе Yr/w (Зафиксируется возникновение неисправности.

Устройство работает следующим образом. Импульсный сигнал ПУСК от входа

5 устройства поступает на первый вход первого элемента 3 ИЛИ, на S-вход первого триггера 31 и через первый вход блока 51 моделирования о тказов на первый вход первого элемента 57 ИЛИ блока, Потенциальный сигнал с прямого выхода первого

триггера 31 поступает на второй управляющий вход регистра 2 вывода информации, разрешая ввод в него информации из блока памяти 1. Импульсный сигнал с выхода первого элемента 57 ИЛИ блока моделирования отказов поступает на S-вход первого триггера 67 и первый вход второго элемента 13 ИЛИ и с его выхода - на R-вход второго триггера 70. Потенциальный сигнал с пря мого выхода триггера 67 через первый выход блока 51 моделирования отказов подается на первый вход седьмого элемента 82 И и на первые входы шестого 27, пятого 20 и второго 30 элементов И, открывая их. Потенциальный сигнал с инверсного выхода второго триггера 70 через шестой выход блока 51 моделирования поступает на второй вход седьмого элемента 82 И и с его выхода - на первый вход первого элемента 8 И, готовя его к открытию и на вторые входы первой 79 и второй 80 групп элементов И, открывая их. На инверсном выходе триггера 67, подключенном к первым входам третьего 73, четвертого 74, пятого 75, второго 83 и первого 68 элементов И, сигнал отсутствует, и данные ключи закрыты. Потенциальный сигнал с прямого выхода первого триггера 31 подается также через второй вход блока 51 моделирования на вторые входы второго 53, первого 61 регистров вывода информации и на второй вход второго регистра 54 адреса, разрешая ввод информации в регистры из блока памяти, Импульсный сигнал с выхода первого элемента 3 ИЛИ поступает на R-вход третьего триггера 15 и на первый вход счетчика 38 операций, приводя его в исходное состояние. Потенциальный сигнал с инверсного выхода третьего триггера 15 подается ха первый вход третьего элемента 48 И, открывая его. Сигнал с выхода первого элемента 3 ИЛИ через первый элемент 4 задержки подается также на первый вход блока 1 памяти для разрешения считывания в регистр 2 вывода информации значений характеристик первой операции алгоритма. Время срабатывания первого элемента 4 задержки должно обеспечивать опережение появления сигнала на прямом выходе первого триггера 31, разрешающего запись информации в регистр 2 вывода информации по отношению к моменту разрешения считывания этой информации из блока 1 памяти. Импульсный сигнал с выхода первого элемента 4 задержки поступает также на первый вход второго элемента 5 ИЛИ и с его выхода - на R-вход второго триггера 9 и на первый вход первого счетчика 26 ошибок, обнуляя его. Потенциальный сигнал с инверсного выхода триггера 9 поступает на

второй вход первого элемента И 8 и совместно с сигналом на его первом входе от первого выхода блока 51 моделирования (см. выше) открывает первый элемент И 8

для сигналов по его третьему входу, Импуль- сный сигнал с выхода второго элемента ИЛИ 5 через второй элемент 6 задержки поступает на первый вход третьего элемента 7 ИЛИ и с его выхода - на первый управ0 ляющий вход регистра 2 вывода информации для разрешения считывания записанных в него значений характеристик операций алгоритма. Время срабатывания второго элемента 6 задержки должно обес5 печивать опережение момента поступления сигнала на первый вход блока памяти 1 и завершения считывания информации в регистр 2 вывода информации по отношению к моменту поступления на первый вход ре0 гистра 2 вывода информации сигнала, разрешающего вывод информации на обработку. Оно также обеспечивает приведение в нулевое состояние триггера 9 и обнуление счетчика ошибок 26 до начала

5 считывания информации из регистра 2. С выхода третьего элемента ИЛ И 7 сигнал также поступает на первый вход седьмого элемента ИЛИ 16 и с его выхода - на управляющий вход генератора 19 случай0 ных чисел, запущенного в момент включения устройства, для разрешения выдачи случайного числа через его выходы второй группы на входы второй группы первой схемы 18 сравнения. Информация о временных

5 характеристиках моделируемой операции с выходов первой группы регистра 2 вывода поступает через открытые элементы И 79 первой группы на первые входы соответствующих элементов ИЛИ 10 первой группы.

0 Информация о вероятностной характеристике операции с выходов второй группы регистра 2 подается через открытые элементы 80 И второй группы на первые входы соответствующих элементов 17 ИЛИ второй

5 группы. Информация о признаке вида операции подается с третьего выхода регистра 2 на S-вход второго триггера 9. Для сенса- моторной операции, имеющей признак О, триггер 9 не изменяет свое состояние, про0 должая поддерживать потенциальный сигнал своего инверсного выхода на втором входе первого элемента И 8 и удерживая в закрытом состоянии четвертый элемент 22 И, так как сигнал на его первом входе.сое5 диненном с прямым выходом триггера 9, отсутствует. Информация с выходов первой группы элементов 10 ИЛИ поступает на информационные входы генератора 11 импульсов со случайной деятельностью, который начинает формировать последовательность импульсов, следующих с выхода генератора 11 на информационный вход дифференцирующего элемента 12. Информация с выходов второй группы элементов ИЛИ 17 поступает на входы второй группы схемы 18 сравнения. При поступлении первого импульса из последовательности от генератора 11 дифференцирующий элемент 12 формирует импульс НАЧАЛО и передает его через свой первый выход на первый вход преобразователя 14 временной интервал - код. Прекращение поступления на вход дифференцирующего 12 элемента последовательности импульсов вызывает формирование на его втором выходе импульса КОНЕЦ, поступающего на третий управляющий вход первой схемы сравнения 18, раз- решая сравнение вероятностной характеристики моделируемой операции и уже введенного от генератора 19 значения случайного числа, а также на второй вход преобразователя 14 временной интервал - код. Преобразователь 14 формирует код числа, пропорционального временному интервалу между поступлением импульсов НАЧАЛО и КОНЕЦ, и через свои выходы передает на информационные входы первой группы накапливающего сумматора 44 времени для записи времени выполнения 1-й операции ДъСили Atij - при ошибочном ее выполнении).

Если результатом сравнения в первой схеме 18 сравнения является правильное выполнение операции, то импульсный сигнал с ее первого выхода передается на первый вход четвертого элемента 21 ИЛИ и с его выхода - на второй вход накапливающего сумматора 44, разрешая суммирование значения времени Atj, полученного от преобразователя 12 к суммарному времени выполнения предыдущих операций, на второй вход открытого ключевого шестого элемента И 27 и через третий вход блока 51 моделирования неисправности - на второй вход закрытого ключевого третьего элемента И 73, Сигнал с выхода шестого элемента 27 И поступает на второй счетный вход счетчика 38 операций, на управляющий вход регистра 40 числа операций в алгоритме и на вход четвертого элемента 37 задержки. Счетчик 38 суммирует очередную единицу и выдает результат на входы второй группы третьей схемы 39 сравнения. Регистр 40 выдает записанное в него значение числа операций на входы первой группы третьей схемы 39 сравнения. Сигнал с выхода четвертого элемента 37 задержки поступает на третий управляющий вход третьей схемы сравнения 39, разрешая сравнение введенных величин. Время срабатывания четвертого эле мента 37 задержки должно обеспечивать опережение завершения подсчета очередной операции и выдачи результата из счетчика 38 операций, а также выдачи установленного числа из регистра 40 операций в третью схему сравнения 39 по отноше- нию к моменту поступления сигнала, разрешающего сравнение этих чисел. Если

0 число операций в счетчике 38 меньше числа из регистра 40, на первом выходе третьей схемы 39 сравнения появляется импульсный сигнал, который поступает на второй вход второго элемента ИЛИ 5 и на второй

5 управляющий вход блока 1 памяти, разрешая считывание характеристик очередной операции. Далее процесс продолжается, как описано выше. При достижении в счетчике 38 операций числа, равного установ0 ленному в регистре 40 значению, после сравнения импульсный сигнал с второго выхода третьей схемы сравнения 39 поступает на третий вход накапливающего сумматора 44, на вход пятого элемента 43 задержки, на

5 управляющий вход регистра 46 нормативного времени, В накапливающем сумматоре 44 осуществляется выдача значения суммарного времени, затраченного на выполнение всех операций данной реализации

0 через свои информационные выходы первой группы на соответствующие входы первой группы четвертой схемы 47 сравнения, а также суммирование этого значения с суммарным временем выполнения всех

5 предыдущих завершенных реализаций алгоритма, Регистр 46 нормативного времени выдает записанное в него значение на информационные входы второй группы четвертой схемы 47 сравнения. С выхода

0 пятого элемента 43 задержки сигнал поступает на третий управляющий вход четвертой схемы сравнения, разрешая сравнение введенных в схему значений времени, и на первый вход шестого элемента 36 ИЛИ. Ес5 ли число накапливающего сумматора 44 меньше или равно числу из регистра 46, то на выходе схемы 47 сравнения появляется импульсный сигнал, поступающий на первый счетный вход счетчика 49 своевременно

0 выполненных реализаций и на второй вход открытого (см. выше) ключевого третьего элемента 48 И. Импульсный сигнал с выхода третьего элемента 48 И поступает на первый счетный вход счетчика 50 своевременно и

5 безошибочно выполненных реализаций.

Время срабатывания пятого элемента 43 задержки должно обеспечивать опережение завершения суммирования значений времени в сумматоре 44 и перезаписи пол- ученногозначения, атакже нормативной величины из регистра 46 в четвертую схему 47 сравнения по отношению к моменту прихода сигнала, разрешающего сравнение.

. Сигнал с выхода шестого 36 элемента ИЛИ поступает на вход шестого элемента 35 задержки, на счетный вход счетчика 34 реа- лизаций вход регистра 32 числа реализаций. С информационных выходов регистра 32 числа реализаций снимается записанное в нем значение на соответствующие входы первой группы пятой схемы 33 сравнения. С информационных выходов счетчика 34 на входы второй группы схемы 33 сравнения поступает очередное значение количества выполнявшихся реализаций. С выхода шее- того 35 элемента задержки сигнал поступает на третий управляющий вход пятой схемы 33 сравнения, разрешая сравнение введенных величин Время срабатывания пятого 35 элемента задержки устанавлива- ется аналогично четвертому элементу 37 задержки. Если число выполнявшихся к данному моменту реализаций меньше установленного, импульсный сигнал с первого выхода пятой схемы 33 сравнения поступа- ет на второй вход первого элемента ИЛИ 3. Начинается моделирование очередной реализации, При достижении в схеме 33 сравнения равенства импульсный сигнал появляется на втором выходе схемы 33 и поступает на R-вход триггера 31. на второй вход счетчика 41 прерванных операций, на второй вход второго счетчика 42 ошибок, на пятый вход сумматора 44 и на вторые входы счетчика 49 своевременно выполненных ре- ализаций и счетчика 50 своевременно и безошибочно выполненных реализаций. Первый триггер 31 переходит в нулевое состояние. Прямой выход первого триггера 31 обнуляется, и ввод информации в регистр 2, первый регистр 61 вывода и в регистр 54 адреса запрещается. С выходов счетчиков 41, 42, 49-и 50 на соответствующие информационные входы блока 45 регистрации снимаются сформированные в этих счетчи- ках значения числа прерванных реализаций, допущенных ошибок, своевременно выполненных реализаций и своевременно и безошибочно выполненных реализаций, а с выходов второй группы сумматора 44 в блок 45 снимается значение времени/ затрачен- ного на выполнение всех завершенных реализаций.

Если в процессе моделирования текущей операции в первой схеме 18 сравнения в результате сравнения получен исход , то есть совершена ошибка, то импульсный сигнал с второго выхода схемы 18 поступает на вход третьего элемента 23 задержки, на управляющий вход регистра

24 ошибок, на второй счетный вход первого счетчика 26 ошибок, на второй вход четвертого элемента ИЛИ 21. на второй вход открытого ключевого пятого элемента И 20 и на первый счетный вход второго счетчика 42 ошибок. Счетчик 42 суммирует очередную единицу, счетчик 26 суммирует единицу и выдает результат на сравнение во вторую схему сравнения 25. Регистр 24 выдает за- писанное в нем значение допустимого числа ошибок (повторений операции) во вторую схему 25 сравнения, Сигнал с выхода четвертого элемента ИЛИ 21 поступает на второй вход сумматора 44, где время, затраченное на попытку операции также, как и для правильно выполненной операции, суммируется с суммарным временем предыдущих операций. Сигнал с выхода пятого элемента 20 И (триггер 9 - в нулевое состояние и сигнала на его прямом выходе нет)и на R-вход третьего триггера 15. Инверсный выход триггера 15, соединенный с первым входом третьего элемента 48 И, обнуляется. Третий элемент 48 И закрывается, и при своевременном завершении данной реализации она не будет подсчитана в счетчике 50 своевременно и безошибочно выполненных реализаций.

Сигнал с выхода третьего элемента задержки 23 поступает на третий управляющий вход второй схемы 25 сравнения, разрешая сравнение. Время срабатывания третьего элемента 23 задержки определяется аналогично четвертому 37 и шестому 35 элементам задержки. Если число ошибок в счетчике 26 меньше значения в регистре 24 , импульсный сигнал с первого выхода второй схемы 25 сравнения поступает на третий вход открытого первого элемента 8 И и через четвертый вход блока 51 моделирования - на второй вход закрытого четвертого элемента И 74 (первый триггер 67 - в единичном состоянии). Сигнал с выхода первого элемента 8 И поступает на второй вход третьего элемента ИЛИ 7 и с его выхода - на первый вход регистра 2 вывода информации для повторного считывания характеристик невыполненной из-за ошибок операции для ее повторения. Если число ошибок в счетчике 26 достигло предельного значения, то есть сравнение в схеме 25 дало результат , импульсный сигнал с второго выхода третьей схемы 25 сравнения поступает на второй вход открытого второго элемента И 30, импульс поступает на второй вход пятого элемента 29 ИЛИ, с выхода пятого элемента ИЛИ 29 сигнал поступает на второй вход шестого элемента ИЛИ 36, на первый счетный вход счетчика 41 прерван- ных реализаций и на четвертый .;ход сумматора 44. По сигналу с выхода шестого элемента ИЛИ 36 осуществляется подсчет реализации прерванной из-за ошибки, так же, как по сигналу о завершении реализации от второго выхода третьей схемы 39 сравнения, и переход к выполнению ноьой реализации. Счетчик 41 фиксирует очередную прерванную реализацию. В сумматоре 44 по полученному сигналу стирается значение времени, затраченного на выполнение прерванной реализации.

При моделировании сенсорной операции с третьего выхода регистра 2 вывода информации снимается признак 1, который поступает на S-вход второго триггера 9. С прямого выхода триггера потенциальный сигнал поступает на первый вход четвертого элемента И 22, открывая его. Инверсный выход триггера 9, соединенный с вторым входом первого элемента 8 И который закрывается для сигналов, поступающих на его третий вход. При этом в случае совершения ошибок сигнал с второго выхода первой схемы сравнения 18 также, как для сенсэмо- торной операции, поступает на вход второй схемы 25 сравнения, управляющий вход регистра 24 ошибок, счетный вход первого счетчика 26 ошибок. В счетчике 26 фиксируется первая единица, после сравнения в третьей схеме 25 сравнения фиксируется исход . С первого выхода схемы 25 сигнал подается на третий вход закрытого первого элемента 8 И, и повторения операции запрещается. По сигналу с второго выхода первой схемы сравнения 18, поступающему на первый счетный вход счетчика 42, суммируется очередная ошибка. В сумматоре 44 по сигналу через четвертый элемент ИЛИ 21 на его второй вход также к значению времени предыдущих операций прибавляется время данной операции.

Сигнал с второго выхода нулевой схемы сравнения 18 через открытый пятый элемент 20 И поступает на второй вход на этот раз открыт го четвертого элемента 22 И, с его выхода на первый вход пятого элемента 29 ИЛИ, и далее повторяется процесс прерывания реализации и перехода к очередной реализации подобно случаю достижения равенства во второй схеме 25 сравнения.

Одновременно с описанными процессами функционирует блок 51 моделирования. Посигналу Пуск, поступившему через первый вход блока на первый вход первого элемента ИЛИ 57, с его выхода сигнал поступает на вход первого элемента 58 задержки, С выхода элемента 58 задержки сигнал поступает на управляющий вход первого регистра 59 адреса и на вход второго

элемента 64 задержки По сигналу на вход первого регистра 59 адреса возможной неисправности, регистр 59 адреса формирует на адресных выходах адрес текущей неисправности, а затем увеличивает его на единицу. Адрес текущей неисправности в адресных выходах регистра 59 адреса поступает на адресные входы первого блока памяти 60 для разрешения считывания оче0 редных значений вероятности возникновения неисправности в первый регистр 61 вывода информации и адреса первой операции алгоритма устранения данной неисп- равно сти во второй регистр 54 адреса

5 первой операции алгоритма устранения неисправности. Время срабатывания первого элемента 58 задержки определяется подобно первому элементу 4 задержки, исходя из необходимости обеспечить опережение

0 появления на втором управляющем входе регистра 61 сигнала разрешения ввода в него информации, поступающего от первого 31 триггера по отношению к моменту появления на входе регистра 59 адреса сигнала

5 от первого элемента 58 задержки, управляющего считыванием из блока 60 памяти информации. Сигнал с выхода второго элемента 64 задержки поступает на первый управляющий вход первого регистра 61 вы0 вода информации, разрешая считывание в схему 62 сравнения числа, на управляющий вход генератора 63 случайных чисел, разрешая вывод из него случайного числа в схему 62 сравнения, и на вход третьего элемента

5 65 задержки. Время срабатывания второго элемента 64 задержки должно обеспечивать опережение ввода числа в регистр 61 по отношению к моменту прихода на него сигнала для считывания числа Си: нал с выхода

0 третьего элемента 6Ь задержки поступает на третий управляющий вход схемы 62 сравнения, разрешая сравнение чисел. Время срабатывания третьего элемента 65 задержки должно обеспечивать отставание появле5 ния на управляющем входе схемы сравнения 62 сигнала, разрешающего сравнение, от момента ввода сравниваемой информации из генератора 63 и регистра 61. Если число из регистра 61 меньше случайно0 го числа (). то есть данная неисправность не возникла, импульсный сигнал с второго выхода схемы 62 сраЕ.пения поступает на четвертый вход первого элемента 57 ИЛИ, и моделируется возникновение оче5 редной неисправности. Если случайное число меньше вероятности возникновения данной неисправности или равно ему, то есть возникла неисправность, импульсный сигнал с второго выхода схемы 62 сравнения поступает на первый ьход третьего элемента 81 ИЛИ. на вход четвертого элемента 78 задержки и через пятый выход блока 51 моделирования - на второй управляющий вход генератора 11 последовательности импульсов, в результате чего генератор прекращает формирование последовательности импульсов, если в нем имеет место моделирование длительности очередной операции алгоритма, на вход седьмого элемента 28 задержки. Прекращение поступления на вход дифференцирующего 12 элемента от генератора 11 последовательности импульсов вызывает формирование на его втором выходе импульса Конец. В преобразователе 14 формируется значение времени, затраченного на выполнение операции до ее прерывания, которое передается в сумматоре 44. По сигналу с выхода седьмого элемента 28 задержки, поступающему на третий вход четвертого элемента ИЛИ 21 и с его выхода - на второй вход сумматора 44, записанное в него значение суммируется с суммарным временем предыдущих операций текущей реализации. Время срабатывания седьмого элемента 28 задержки должно обеспечивать опережение записи в сумматор 44 значения времени, по отношению к моменту прихода сигнала, разрешающего его обработку. Сигнал с выхода третьего элемента ИЛИ 81 поступает на вход второго триггера 70. С прямого выхода пятого триггера 70 потенциальный сигнал поступает на первый вход шестого элемента 77 И,открывая его Инверсный выход триггера 70, соединенный с вторым входом седьмого элемента И 71 и, через шестой выход блока 51 моделирования с вторым входом седьмого элемента И 82 устройства, обнуляется Седьмой элемент- И 71 блока моделирования и седьмой элемент устройства 82 И закрываются. Выход седьмого элемента I/I 82, соединенный с первым входом первого 8 элемента И и с вторыми входами первой 70 и второй 80 группы элементов И, обнуляется, и элементы И 8, 79 и 80 закрываются. Вывод характеристик операций из регистра 2, если неисправность возникла после окончания ее моделирования, но до завершения количественного анализа и перехода к очередной операции, запрещается.

Сигнал с выхода четвертого элемента 78 задержки поступает на R-вход первого триггера 67, на первый вход четвертого элемента 76 ИЛИ и на первый вход пятого элемента ИЛИ 72.

Триггер 67 переходит в нулевое состояние. Прямой выход триггера, соединенный через первый выход блока 51 моделирования с первыми входами шестого 27. пятого

20 и второго 30 элементов И, обнуляется, и ключи закрываются. При этом запрещается прохождение сигналов для моделирования прерывания реализации в случае ошибок в

действиях оператора, для подсчета прерванных и выполненных реализаций, для подсчета и сравнения числа операций текущей реализации и для задействования регистра 2 вывода для повторения операций в

0 процессе моделирования алгоритма устранения неисправности.

Потенциальный сигнал на инверсном выходе триггера 67 поступает на первый вход первого элемента 68 И и на первые

5 входы третьего 73, четвертого 74, пятого 75 и второго 83 элементов И, открывая их.

Сигнал с выхода пятого элемента ИЛИ 72 поступает на первый вход счетчика 56 операций устранения неисправности обну0 ляя счетчик, на второй вход шестого элемента ИЛИ 69 и с его выхода на первый управляющий вход второго регистра 54 адреса, разрешая считывание информации. Сигналы с выходов второго регистра 54 ад5 реса и с счетчика 56 операций устранения неисправности (в данном случае он равен нулю) поступает на соответствующие входы сумматора 55, с выходов которого сигнал (равный сумме сигналов от регистра и счет0 чика) поступает на адресные входы второго блока 52 памяти, разрешая выбрать для считывания информации адрес характеристик первой операции алгоритма устранения данной неисправности, которые по соответ5 ствующим информационным вводам вводятся во второй регистр 53 вывода информации. Сигнал с выхода четвертого элемента ИЛИ 76 поступает на вход пятого элемента 66 задержки и с его выхода - на

0 второй вход первого элемента 68 И.

Время задержки четвертого элемента 78 задержки в случае появления неисправности после завершения очередной операции основного алгоритма по длительности,

5 но до завершения ее анализа по количеству ошибок и операций в текущей реализации должно обеспечивать опережение появления сигналов о верности выполнения опера- ци.и на первом выходе первой схемы 18

0 сравнения, его прохождения на третью схему 39 сравнения, а также сигнала об ошибочности выполнения операции и появления в результате его сигнала на выходах второй схемы 25 сравнения, четвертого

5 элемента И 22 и пятого элемента ИЛИ 29 по отношению к моменту обнуления инверсного выхода триггера 67 и закрытия элементов И 20, 27 и 30. В этом случае, если операция выполнена правильно, и количество операций не достигло предельного значения.

сигнал с первого выхода третьей схемы сравнения 39 поступает в блок 1 памяти для считывания характеристик очередной операции и на первый регистр 2 для ее вывода, но информация через закрытые элементы И 79 и 80 не пройдет. Если допущена ошибка в сенсомоторной операции, но число повторений не превысило допустимого значения, то сигнал с первого выхода второй схемы 25 сравнения не пройдет ни через первый 8, ни через четвертый 74 закрытые элементы И. Если число операций достигло конечного значения, то с второго выхода третьей схемы 39 сравнения через пятый элемент 43 задержки или, если число ошибок достигло предельного значения или достигнута ошибка в сенсорной операции, по сигналу, поступившему со второго выхода второй схемы сравнения 25 или от выхода четвертого элемента И 22, с выхода пятого элемента ИЛИ 29 сигналы поступят на первый или второй входы шестого элемента ИЛИ 36, с его выхода - на шестой элемент 35 задержки и через шестой вход блока 51 моделирования и открытый второй элемент И 83 - на второй вход первого элемента ИЛИ 57. Далее, как после прихода импульса триггер 67 перейдет вновь в единичное состояние при котором элементы И 68, 73, 74, 75 и 83 закрываются, а элементы И 20, 27, 30 и 82 открываются. Триггер 70 перейдет в нулевое состояние, при котором элемент И 71 открывается, а элемент И 77 закрывается, кроме того по сигналу через шестой выход блока 51 моделирования и элемент И 82 открываются первый элемент И 8 и первая 79 и вторая 80 группы элементов И. Моделирование устранения возникнет неисправности запрещается, а по сигналу от первого элемента ИЛИ 57 на седьмой элемент задержки 58 вновь начинается моделирование возникновения неисправности. Кроме того, сигнал с выхода элемента И 83 поступит через восьмой выход блока 51 моделирования на четвертый вход второго элемента ИЛИ 5, и реализация основного алгоритма продолжается с прерванной или с очередной операции.

Таким образом, моделирование возникновения и устранения неисправности осуществляется только в процессе реализации основного алгоритма деятельности оператора. При переходе от одной реализации к другой моделирование аварийного алгоритма не имеет места.

Если сигналов о завершении или прерывания реализации основного алгоритма через шестой вход блока реализации нет, то процесс моделирования устранения неисправности продолжается

С выхода пятою элемента 66 задержки сигнал поступает на второй вход открытого первого элемента И 68 и с его выхода на первый управляющий вход второго регистра 53 вывода информации разрешая ее вывод, и через четвертый выход блока 51 моделирования -- на второй вход седьмого элемента ИЛИ 16 и с его выхода - на управляющий вход генератора 19 случайных чи0 сел для разрешения ввода значения случайного числа, в первую схему 18 сравнения. Время срабатывания пятого элемента 66 задерхчки должно обеспечить опережение ввода информации в регистр 53

5 по отношению к моменту разрешения ее считывания из регистра 53, но не меньше суммарного времени срабатывания третьей схемы сравнения 39, шестого элемента 35 задержки и пятого элемента 43 задержки,

0 что обеспечивает в описанном выше случае приход через шестой вход блока 51 моделирования сигнала о прерывании или завершении реализации опережения прихода сигнала от первого элемента 57 на S-вход

5 триггера 67 и закрытия элемента И 68 для предотвращения вывода информации из регистра 53.

По сигналу на первом управляющем входе регистра 53 значения временных ха0 рактеристик операции с выходов первой группы регистра 53 через выходы второй группы Ьлока 51 моделирования, передаются на вторые входы первой группы элементов ИЛИ 10 и с их выходов - на

5 информационные входы генератора 11 импульсов со случайной длительностью. Значение вероятностной характеристики данной операции с выходов второй группы регистра 53 через выходы третьей группы

0 блока 51 моделирования поступает на вторые входы второй группы элементов ИЛИ 17 и с их выходов - на входы второй группы первой схемы сравнения 18. Далее операция моделируется аналогично операции ос5 новного алгоритма за исключением того, что при правильном выполнении операции сигнал с первого выхода первой схемы 18 сравнения не проходит через закрытый шестой элемент И 27, и подсчет числа операций и

0 его сравнение с установленным не проводится и, таким образом, блокируется задействование четвертой 47 и пятой 33 схем сравнения с обеспечивающими элементами блока 1 памяти и регистра 2 вывода инфор5 мации. Кроме того, сигнал с первого выхода первой схемы 18 сравнения через третий вход блока 51 моделирования поступает на второй вход открытого третьего элемента И 73. С его выхода сигнал поступает на первый вход закрытого седьмого элемента 71 И и на

второй вход открытою шестого элемента И 77. Сигнал с выхода элемента И 77 поступает на второй вход четвертого элемента ИЛИ 76, на первый вход шестого элемента ИЛИ 69 и на второй вход счетчика 56 операций устранения неисправности, Счетчик 56 операций устранения неисправности увеличивает хранящееся в нем число на единицу, которое с его выходов записи поступает на вторую группу входов сумматора 55. Сигнал с шестого элемента 69 поступает на первый управляющий вход второго регистра адреса 54, разрешая считывание из него информации в сумматор 55 на его первую группу входов. Сумматор 55 суммирует значения чисел,поступивших на его первую и вторую группу входов, и выдает результат через свои выходы на адресные входы второго блока памяти 52 разрешая выбор характеристик очередной операции алгоритма уст- ранения неисправности. С выхода четвертого элемента ИЛИ 76 сигнал поступает на вход пятого элемента 66 задержки, с его выхода - на вход открытого первого элемента И 68 и с его выхода - на второй вход седьмого элемента ИЛИ 16 устройства и на управляющий вход регистра 53 вывода. Далее процесс моделирования операции аналогичен описанному.

В случае формирования в первой схеме 18 сравнения ошибки, по сигналу с второго выхода схемы 18 сравнения осуществляется подсчет ошибок в счетчиках 26 и 42, сравнение числа ошибок с допустимым значением во второй схеме сравнения 25, фиксация времени в сумматоре 44. Но так как первый 8, пятый 20 и второй 30 элементы И закрыты, то задействование регистра 2 вывода для повторения операции и подсчет прерванных реализаций с последующим сравнени- ем запрещены. Но если число повторений операции меньше допустимого, то сигнал с первого выхода второй схемы 25 сравнения через четвертый вход блока 51 моделирования поступает на второй вход открытого чет- вертого элемента И 74, с его выхода - на четвертый вход четвертого элемента ИЛИ 76, с выхода которого сигнал поступает на вход пятого элемента 66 задержки, с его выхода на второй вход открытого элемента И 68 и с его выхода - на первый управляющий вход регистра 53 вывода и на второй вход четвертого элемента ИЛИ 16 устройства. Моделирование операции повторяется. Если число ошибок достигло предельного значения, сигнал с второго выхода второй схемы 25 сравнения через пятый вход блока 51 моделирования поступает на второй вход открытого пятого элемента И 75 и с его выхода - на второй вход пятого элемента ИЛИ

72 и на третий вход четвертого элемента ИЛИ 76, а с его выхода на пятый элемент 66 задержки и далее - на второй вход открытого элемента И 68. Сигнал с выхода пятого элемента ИЛИ 72 поступает на второй вход шестого элемента ИЛИ 69 и на первый вход счетчика 56 операций устранения неисправности, который обнуляется, Сигнал с шестого элемента ИЛИ 69 поступает на первый управляющий вход второго регистра 54 адреса, который через сумматор 55 (т.к. на второй группе входов сумматора ноль) выдает на адресные входы второго блока памяти 52 адрес первой операции алгоритма устранения неисправности характеристики которой вновь считываются. Устранение неисправности начинается вновь.

При формировании сумматором 55 адреса последней операции алгоритма устранения неисправности ее характеристик из второго блока 52 памяти переписываются в регистр 53 вывода. При считывании информации из регистра 53 вывода на его третьем выходе появится импульсный сигнал (признак конца алгоритма устранения неисправности) который через второй элемент ИЛИ 13 поступает на R-вход второго триггера 70. Прямой выход триггера 70 обнуляется, и шестой элемент И 77 закрывается. Потенциальный сигнал с инверсного выхода триггера 70 поступает на вход седьмого элемента И 71 на второй вход седьмого элемента И 82 устройства, открывая их. В случае правильного выполнения последней операции сигнал с первого выхода второй схемы 25 сравнения проходит через третий вход блока 51 моделирования, через открытый третий элемент И 73 на второй вход закрытого шестого элемента И 77 и на первый вход открытого седьмого элемента И 71, С выхода этого элемента сигнал поступает на третий вход первого 57 элемента ИЛИ. С выхода первого 57 элемента ИЛИ сигнал поступает на S-вход первого триггера 67. Инверсный выход триггера 67 обнуляется, и третий 73. четвертый 74, пятый 75 первый 68 и второй 83 элементы И закрываются. Сигнал с прямого выхода триггера 67 поступает через первый выход блока 51 моделирования, через открытый элемент 82 И на вторые входы первой 79 и второй 80 групп элементов И, открывая их для вывода информации, и на первый вход первого элемента И 8, открывая его. Сигнал с выхода седьмого элемента И 71 поступает также че,рез седьмой выход блока 51 моделирования на третий вход второго элемента ИЛИ 5, а с его выхода - на R-вход второго триггера 9 и на вход второго элемента 6 задержки, с его выхода - на первый вход третьего элемента ИЛИ 7 и далее на первый вход регистра 2 вывода информации. Моделирование текущей реализации основного алгоритма возобновляется с прерванной или очередной операции. Сигнал с выхода первого эле- мента ИЛИ 57 поступает на вход первого элемента 58 задержки и возобновляется моделирование возникновения неисправности переходом к следующему адресу блока

60памяти. Если на последней операции ава- рийного алгоритма число повторений из-за ошибки достигнет допустимого значения, то сигнал с второго выхода второй схемы 25 сравнения, поступает через пятый вход блока 51 моделирования неисправности, через открытый пятый элемент 75 И поступает на третий вход элемента ИЛИ 76, на второй вход пятого элемента ИЛИ 72 и на второй вход третьего элемента ИЛИ 81, с выхода которого сигнал поступает на S-вход второ- го триггера 70. Инверсный выход второго триггера 70 обнуляется и седьмой элемент

И 71 блока моделирования и седьмой элемент И 82 устройства закрываются Потенциальный сигнал с прямого выхода триггера 70 поступает на первый вход шестого элемента И 77, открывая его. Сигнал с выхода пятого элемента И 72 поступает на второй вход шестого элемента ИЛИ 69 и на первый вход счетчика 56 операций устранения не- испрэвностей, обнуляя его. Моделирование устранения данной неисправности повторяется с первой операции.

При достижении числа прерванных и завершенных реализаций сигнал с второго вы- хода поступает на вход первого триггера 31. Прямой выход триггера связанный с вторыми входами регистра 2 устройства, первого

61и второго 53 регистров блока моделирования вывода информации, и ввод в регист- ры информации запрещен. Все процессы в устройстве моделирования прекращаются.

Формула изобретения Устройство для моделирования деятельности человека-оператора, содержа- щее блок памяти, регистр вывода информации, пять схем сравнения, тоитриг- гера, семь элементов задержки, семь элементов ИЛИ, четыре элемента И, генератор импульсов со случайной длительностью, дифференцирующий элемент, генератор случайных чисел, накапливающий сумматор, блок регистрации, преобразователь временной интервал-код, регистр установленного числа повторения операций, два счетчика ошибок, регистр числа реализаций, счетчик реализаций, счетчик операций. регистр операций алгоритма, счетчик незавершенных реализаций, регистр нормативного времени, счетчик своевременно

выполненных реализаций, счетчик своевременно и безошибочно выполненных реализаций, выходы блока памяти соединены соответственно с информационными входами регистра вывода информации, первый вход первого элемента ИЛИ является входом запуска устройства, а выход первого элемента ИЛИ соединен с входом первого элемента задержки, выход которого подключен к входу считывания начального адреса блока памяти и первому входу второго элемента ИЛИ, выход которого подключен к входу второго элемента задержки,выход которого соединен с первым входом третьего элемента ИЛИ, выход которого подключен к входу записи регистра вывода информации, второй вход третьего элемента ИЛИ подключен к выходу первого элемента И, прямой выход первого триггера соединен с входом разрешения ввода информации регистра вывода информации, выход знакового разряда которого подключен к единичному входу второго триггера, нулевой вход которого подключен к выходу второго элемента ИЛИ, инверсный выход второго триггера подключен к первому входу первого элемента И, выход генератора импульсов со случайной длительностью соединен с входом дифференцирующего элемента, первый выход которого соединен с входом запуска преобразователя временной интервал - код. вход останова которого подключен к второму выходу дифференцирующего элемента и входу разрешения сравнения первой схемы сравнения, информационные входы первой группы которой соединены соответственно с выходами генератора случайных чисел, выход первого элемента ИЛИ соединен с нулевым входом третьэго триггера и установочным входом счетчика операций, выход Меньше или оав- но первой схемы сравнения соединен с первым входом четвертого элемента ИЛИ, выход которого подключен к входу разрешения суммирования накаплиоагащего сумматора, а выход Больше первой схемы сравнения соединен с вторым входом четвертого элемента ИЛИ, входом считывания регистра установленного числа повторения операций, входом третьего элемента задержки и счетным входом первого счетчика ошибок, установочный вход которого подключен к выходу второго элемента ИЛИ, выход третьего элемента задержки соединен с входом разрешения сравнения второй схемы сравнения, информационные входы первой и второй групп которой подключены к разрядным выходам соответственно регистра установленного числа повторений операций и пероого счетчика ошибок, выход

Меньше второй схемы сравнения подключен к второму входу первого элемента И, а выход Равно второй схемы сравнения соединен с первым входом второго элемента И, выход четвертого элемента задержки со- единен с входом разрешения сравнения третьей схемы сравнения, информационные входы первой и второй групп которой соединены с разрядными выходами соответственно счетчика операций и регистра операций алгоритма, выход Равно третьей схемы сравнения соединен с входом пятого элемента задержки и входом считывания регистра нормативного времени, разрядные выходы которого соединены соответст- венно с информационными входами первой группы четвертой схемы сравнения, информационные входы второй группы которой подключены соответственно к информационным выходам первой группы накапливз- ющего сумматора, информационные входы которого соединены соответственно с выходами преобразователя временной интервал-код, выход пятого элемента задержки подключен к входу разрешения сравнения четвертой схемы сравнения, выход Меньше или равно которой соединен с первым входом третьего элемента И и входом считывания счетчика своевременно выполненных реализаций, счетный вход которого и счетный вход счетчика своевременно и безошибочно выполненных реализаций объединены и соединены с выходом Равно пятой схемы сравнения, выход третьего элемента И подключен к входу считывания счетчика своевременно и безошибочно выполненных реализаций, информационные выходы которого, информационные выходы счетчика своевременно выполненных реализаций, счетчика незавершенных реализа- ций, второго счетчика ошибок и информационные выходы второй группы накапливающего сумматора подключены к соответствующим входам блока регистрации, второй вход третьего элемента И со е- динен с инверсным выходом третьего триггера, прямой выход второго триггера подключен к первому входу четвертого элемента И, выход которого подключен к первому входу пятого элемента ИЛИ, выход которого соединен с установочным входом накапливающего сумматора, счетным входом счетчика незавершенных реализаций и первым входом шестого элемента ИЛИ, выход которого подключен к входу шестого элемента задержки, входу считывания регистра числа реализаций и счетному входу счетчика реализаций, выход шестого элемента задержки подключен к входу разрешения сравнения, информационные входы

первой и второй групп которой соединены соответственно с разрядными выходами регистра числа реализаций и счетчика реализаций, выход Больше пятой схемы сравнения подключен к второму входу первого элемента ИЛИ, а выход Равно пятой схемы сравнения подключен к нулевому входу первого триггера, входу считывания счетчика незавершенных реализаций, первому входу считывания накапливающего сумматора и входу считывания второго счетчика ошибок, счетный вход которого соединен с выходом Больше первой схемы сравнения, а второй вход считывания накапливающего сумматора соединен с выходом Равно третьей схемы срэвнения ,0 т л и ч а ,ю щ е е с я тем, что, с целью расширения функциональных возможностей за счет моделирования отказов и восстановлений техники, оно дополнительно содержит с пятого по седьмой элементы И, две группы элементов И, две группы элементов ИЛИ и блок моделирования отказов, содержащий два блока памяти, два регистра вывода информации, комбинационный сумматор, два триггера, два регистра адреса, генератор случайных чисел, счетчик операций устранения отказов, схему сравнения, семь элементов И, шесть элементов ИЛИ и пять элементов задержки, причем в блоке моделирования отказов выход первого элемента ИЛИ соединен с первым входом второго элемента ИЛИ, единичным входом первого триггера и входом первого элемента задержки, выход которого подключен к входу считывания первого регистра адреса и входу второго элемента задержки,выход которого соединен с входом записи первого регистра вывода информации, входом считывания генератора случайных чисел и входом третьего элемента задержки, выход которого подключен к входу разрешения сравнения схемы сравнения, информационные входы первой и второй групп которой соединены с информационными выходами соответственно первого регистра вывода информации и генератора случайных чисел, разрядные выходы первого регистра адреса подключены соответственно к адресным входам первого блока памяти, информационные выходы первой и второй групп которого соединены с информационными входами второго регистра адреса и первого регистра вывода информации, выход Больше схемы сравнения подключен к первому входу первого элемента ИЛИ, а выход Меньше или равно - к первому входу третьего элемента ИЛИ и входу четвертого элемента задержки. выход которого подключен к первым входам четвертого и пятого элементов ИЛИ и нулевому входу первого триггера, инверсный выход которого соединен с первыми входами первого, второго, третьего, четвертого и пятого элементов И, выход первого элемента И подключен к входу записи второго регист- ра вывода информации, разрядные входы которого подключены соответственно к выходам второго блока памяти, адресные входы, которого соединены соответственно с выходами комбинационного сумматора, ин- формационные входы первой и второй групп которого подключены к разрядным выходам соответственно второго регистра адреса и счетчика операций устранения отказов, выход второго элемента И соединен с вторым входом первого элемента ИЛИ, выход знакового разряда второго регистра вывода информации подключен к второму входу второго элемента ИЛИ. выход которого соединен с нулевым входом второго триг- гера, единичный вход которого подключен к выходу третьего элемента ИЛИ, прямой и инверсный выходы второго триггера соединены с первыми входами шестого и седьмого элементов И, вторые входы которых объединены и соединены с выходом третьего элемента И, выход четвертого элемента И подключен к второму входу четвертого элемента ИЛИ, выход которого соединен с входом пятого элемента задержки, выход которого подключен к второму входу первого элемента И, выход пятого элемента И соединен с третьим входом четвертого элемента ИЛИ, вторым входом третьего элемента ИЛИ и вторым входом пятого элемент ИЛИ, выход которого подключен к входу обнуления счетчика операций устранения отказов и первому входу шестого элемента ИЛИ, второй вход которого и счетный вход счетчика операций устранения отказов объединены и соединены с выходом шестого элемента И и четвертым входом четвертого элемента ИЛИ, выход седьмого элемента И соединен с третьим входом первого элемента ИЛИ, а выход шестого элемента ИЛИ подключен к входу считывания второго регистра адреса/входы разре- шения ввода информации второго регистра адреса, первого и второго регистров вывода информации объединены и соединены с прямым выходом первого триггера устройства, вход запуска которого подключен к четвертому входу первого элемента ИЛИ блока моделирования отказов, прямой выход первого триггера которого соединен с первым входом пятого элемента И устройства, вторым входом второго элемента И устройства и первыми входами шестого и седьмого элементов И устройства, выход второго элемента И устройства подключен к

второму входу пятого элемента ИЛИ устройства, второй вход пятого элемента И устройства соединен с выходом Больше первой схемы сравнения устройства, а выход пятого элемента И устройства соединен с единичным входом третьего триггера устройства и вторым входом четвертого элемента И устройства, выход Меньше или равно первой схемы сравнения устройства подключен к второму входу шестого элемента И устройства, выход которого соединен с входом четвертого элемента задержки устройства, входом считывания регистра опе- рэций алгоритмэ и счетным входом счетчика операций, выход Меньше или равно схемы сравнения блока моделирования отказов подключен к входу останова генератора импульсов со случайным интервалом следования и входу седьмого элемента задержки устройства, выход которого подключен к третьему входу четвертого элемента ИЛИ устройства, выход Меньше третьей схемы сравнения которого соединен с вторым входом второго элемента ИЛИ устройства и с адресным входом блока памяти устройства, третий и четвертый входы второго элемента ИЛИ устройства подключены соответственно к выходу седьмого элемента И блока моделирования отказов и выходу второго элемента И блока моделирования отказов, инверсный выход второго триггера которого подключен к второму входу седьмого элемента И устройства, выход которого соединен с третьим входом первого элемента И устройства и первыми входами элементов И первой и второй групп, вторые входы которых соединены соответственно с разрядными выходами регистра вывода информации устройства, выходы элементов И первой группы соединены соответственно с первыми входами элементов ИЛИ первой группы, выходы которых соединены соответственно с входами установки режима работы генератора импульсов со случайной длительностью, вход останова работы которого подключен к выходу Меньше или равно схемы сравнения блока моделирования отказов, второй вход второго элемента И которого соединен с выходом шестого элемента задержки устройства, выходы элементов И второй группы которого соединены соответственно с первыми входами элементов ИЛИ второй группы, выходы которых соединены соответственно с информационными входами второй группы первой схемы сравнения устройства, вторые входы элементов ИЛИ первой и второй групп соединены соответственно с разрядными выходами первой и второй групп второго регистра вывода информации блока моделирования отказов,

выход первого элемента И которого соединен с первым входом седьмого элемента ИЛИ устройства, второй вход которого подключен к выходу третьего элемента ИЛИ устройства, выход седьмого элемента ИЛИ устройства соединен с входом считывания генератора случайных чисел устройства, выход Равно второй схемы сравнения устройства соединен с вторым входом пятого элемента И блока моделирования отказов, второй вход четвертого элемента И которо

го подключен к выходу Меньше второй схемы сравнения устройства, а выход Меньше или разно первой схемы сравнения устройства подключен к второму входу третьего элемента И блока моделирования отказов, а выход пятого элемента задержки устоойства соединен с вторым входом шестого элемента ИЛИ устройства, единичный вход первого триггера устройства соединен с входом запуска устройства.

Фиг. г

| Устройство для моделирования деятельности человека-оператора | 1984 |

|

SU1164726A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для моделирования деятельности человека-оператора | 1984 |

|

SU1241254A2 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1992-11-30—Публикация

1990-07-13—Подача