(54) УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ВРЕМЕНИ

ЗАДЕРЖКИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для измерения времени задержки | 1987 |

|

SU1451640A2 |

| Анализатор реовазосигналов для индикации наличия сосудов с нарушенной проходимостью | 1988 |

|

SU1602454A1 |

| Способ измерения сдвига фаз | 1985 |

|

SU1242845A1 |

| Устройство для поверки преобразователей фаза-код | 1990 |

|

SU1774298A1 |

| СПОСОБ РЕГИСТРАЦИИ СЛАБЫХ СВЕТОВЫХ СИГНАЛОВ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2001 |

|

RU2190196C1 |

| СПОСОБ РЕГИСТРАЦИИ РЕОСИГНАЛА МЫШЦ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1994 |

|

RU2090133C1 |

| Радиометр | 1990 |

|

SU1723460A1 |

| Способ измерения временных интервалов | 1977 |

|

SU980062A1 |

| Устройство для измерения параметров цифровых полупроводниковых элементов | 1977 |

|

SU693274A1 |

| Функциональный генератор | 1987 |

|

SU1501100A1 |

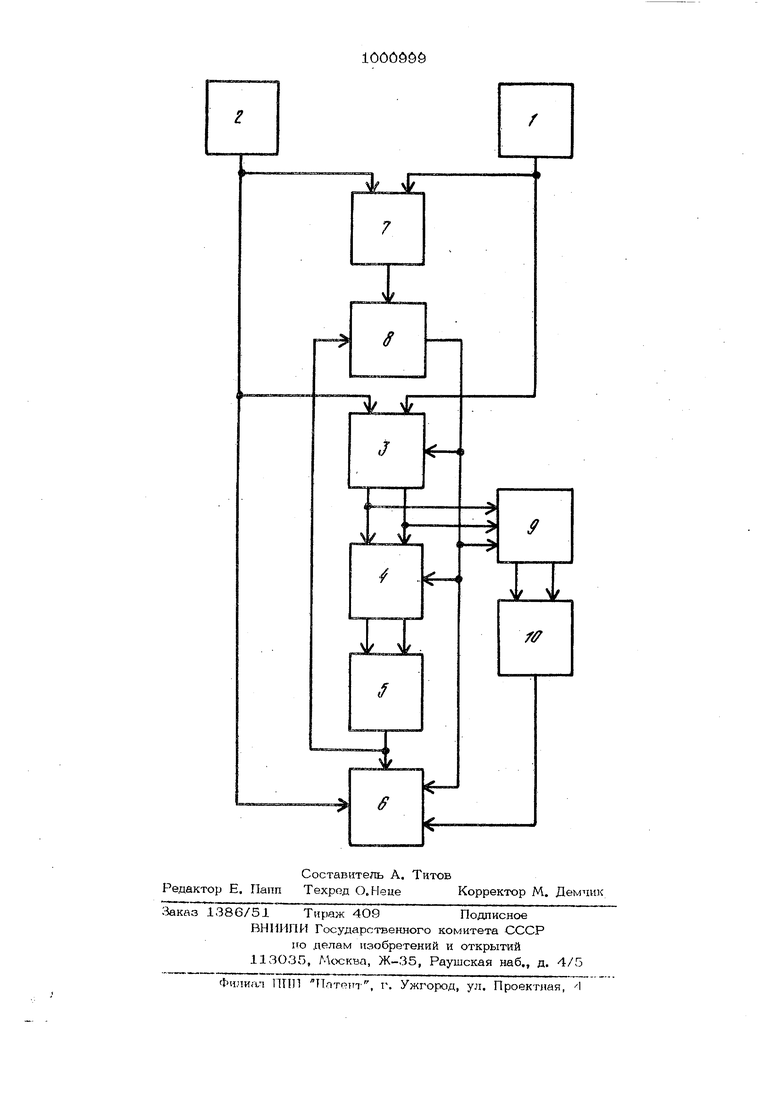

1 Изобретение относится к электроиэмерениям и может быть использовано для измерения времени за;:.ержки сигналов стробирования наносекундного диапазона в компонентах стробирования разных интегральных стробируемых схем, в частности монолитных стробируемых аналогоцифровых преобразователей непосредственного сравнения и монолитных стробируемых быстродействующих компараторов. Известно устройство для измерения времени задержки , содержащее задающий генератор, генератор пачек импульсов, дифференциальный каскад, переменные линии задержки, согласованный тройник, дискриминатор, элемент совпадения и счетчик, вход которого соединен с выходо элемента совпадения, входы которого соединены соответственно с выходами задающего генератора, генератора помех и дискриминатора, вход которого подключен к выходу согласованного тройника, входы которого соединены соответствоино с выходом первого переменного липни задерж- ки И С последовательно соединенными второй линией задержки и измеряемым объектом, причем входы первого и второго переменных линий задержки подключены к выходам дифференциального каскада хо- . ды которого подключены к выходам генератора пачек, соединенного своим входом с задающим генератором С 1 . Недостатком известного устройства является то, что он не позволяет определить время задержки сигналов стробирования интегральных схем, компоненты стробирования которых не имеют внещних выходных выводов, необходимых для подключения этих компонентов к устройству. Известно устройство для измерения времени задержки, содержащее блок фор- мирования временного интервала, блок управления, блок обработки и регистрации информации и блок расщирения времени задержки, выполненный в виде генератора одиночных импульсов, блок коммутации соединенного с дополтштельиой линией за.аержки и с подключаемым к нему измеряемым элементом, причем выход гене ратора одшючных импульсов соединен с входом блока коммутации, выход которого через блок формирования временного интервала соединен с входом блока обработки и регистрации информации, выход линии задержки соединен с генератором одиночных импульсов, выходы блока упра ления соединены с генератором одиночных импульсов, с блоком коммутации, блоком формирования временного интервала, блоком обработки и регистрации информации, а входы блока управления соединены с выходами блока формировани временного интервала и блока обработки и регистрации информации 2 ,Однако это устройство также имеет недостаточные функциональные возможности. Цель изобретения -, расширение функциональньк возможностей устройства путем обеспечения возможности измерения времени- задержки сигналов стробировани в компонентах стробирования интегральных стробируемых схем, не имеющих внешних выходных вьшодов этих компонен тов. Поставленная цель достигается тем, что в устройство, содержащее блок формирования временного интервала, блок управления, блок обработки и регистраци информации и блок расширения времени задержки, введены управляемый генерато импульсов, генератор импульсов, блок фо мирования временного сдвига, блок формирования сигналов и блок совпадени причем выход управляемого генератора импульсов соединен с первым входом бл ка формирования временного сдвига и пе вым входом блока совпадения, выход которого соединен с входом запуска блока управления, выход которого соединен с входами сброса блока формирования вре менного сдвига, блока расширения време задержки, блока формирования сигналов блока обработки и регистрации информации, а выход генератора импульсов соед нен с вторым входом блока совпадения, тактовым входом блока обработки и регистрации информации и вторым входом блока формирования временного сдвига, первый выход которого соединен с первым входом блока расширения времени задержки и с управляющим входом блока формирования сигналов, а второй - с вхо дом стробирования блока формирования сигналов и с вторым входом блока расширения времени задержки, выходы кото рого соединены соответственно с входам запуска и останова блока формирования временного интервала, выход которого соединен с входом разрешения блока управления и управляющим входом блока обработки и регистрации информации, На чертеже показана блок-схема предлагаемого устройствам. Устройство содержит управляемый генератор 1 импульсов, генератор 2 импульсов, блок 3 формирования временного сдвига, блок 4 расширения времени задержки, блок 5 формирования временного интервала, блок 6 обработки и регистрации информации, блок 7 совпадения, блок 8 управления и блок 9 формирования сигналов. Выход управляемого генератора 1 соединен с первым входом блока 3 формирования временного сигнала и с первым входом блока 7 совпадения, выход которого соединен с входом запуска блока 8 управления, выход которого.соединен с входами сброса блока 3, блока 4 расширения времени задержки, блока 9 формирования сигналов и блока 6 обработки и регистрации ипформа11ИИ, а выход генератора 2 импульсов соединен с вторым входом блока 7 совпадения, тактовым входом блока 6 обработки и регистрации информации и вторым входом блока 3 формирования временного сдвига, первый выход которого соединен с первым входом блока 4 расшкре- ния времени задержки, с управляющим входом блока 9 формирования сигналов, а второй - с входом стробирования блока 9 формирования сигналов и с вторым входом блока 4 расширения времени задержки, выходы которого соединены соответственно с входами запуска и останова блока 5 формирования временного интервала, выход которого соединен с входом разрешения блока 8 управления и управляющим входом блока 6 обработки и регистрации информации. Управляемый генератор 1 импульсов вьшоянен в виде кварцевого генератора с плавной подстройкой частоты повторения. Блок 3 формирования временного сдвига содержит два независимых двоичных счетчика и триггер разрешения. Блок 4 расширения времени задержки представляет собой два независимых двоичных счетчика. Блок 5 формирования временного интервала выполнен в виде триггера, формирующего прямоугольный импульс, начало которого совпадает с передним фронтом импульса на первом выходе блока 4 расширения времени за,аержки, а конец- с передним фронтом иктпульса на втором выходе того же блока , Блок 6 обработки и регистрации информации содержит двоично-десйтичный счетчик, буфферный регистр, элементы дешифраторов и индикацию для визуального наблюдения величины измеряемого времени задержки и состояния выходной информации исследуемого элемента 1О. Блок 7 совпадения содержит элемент совпадения с малым гистерезисом фикС ирования совпадения во времени передних фронтов сигналов генераторов 1 и 2, блок 8 управления содержит триггер разрешения и эдемент останова. Блок 9 формирования сигналов выполнен в виде формирователя сигнала стробирования с крутым передним фронтом, форми хэвателя сигнала с малым внутренним сопротивлекием, 4ормирующего входной сигнал с крутым передним фронтом и элемента остакова формирования сигналов. Исследуемый элемент 10 подключается к выходам формирователей входного сигнала и сигнала стробирования блока 9 формирования сигналов и к входу блока 6 обработки и регистрации информации. Устройство работает следующим образом. Ручная плавная подстройка частоты позволяет установить частоту сигнала управляемого генератора 1 импульсов, равную или меньше частоты следования сигнала на выходе генератора 2 импульсов. При этом максимальная разница между периодами этих сигналов является в несколько раз меньше величины периодов этих сигналов. Прямоугольные импуль сы с выходов управляемого генератора 1 и генератора 2 поступают на входы блока 7 совпадения; элемент совпадения которого обладает малым гистерезисом фиксирования совпадения во времени передних фронтов сигналов генераторов 1 и 2. При совпадении передних фронтов , сигналов генераторов 1 и 2 блок 7 совпадения вырабатывает сигнал запуска, который поступает на вход запуска блока 8 управления. Передний фронт этого сигнала формирует сигнал управления схемой останова блока 8 управления, а задний фронт переводит триггер разрешения блока управления в состо5шие, запираюшее дальнейшее прохождение сигнала запуска на вход элемента останова блока 8 управ ления. Сигнал управления на выходе блока 8 управления, сформированный элемен том останова этогхэ блока, устанавливает в нулевые состояния счетчики блока 3 формирования временного сдвига, блока 4 расширения времени задержки, блока обработки и регистрации информации 6, переводит элемент останова блока-9 формирования сигналов на ждущий режим и устанавливает триггер разрешения блока 3 формирования временного сдвига в открытое состояние, разрешающее проход импульсов с выходов управляемого генератора 1 и генератора 2 на входы двоичных счетчиков того же блока 3, в которых число укладывающихся счетных импульсо одинаково и равно N . Если TC; - период сигнала генератора импульсов 2, а Tj.4A-t - период сигнала управляемого генератора 1 импульсов, то временной сдвиг дТ между началами импульсов на выходах блока 3 формирования временного сдвига после полного заполнения счетчиков равен ()-НЛ, (-1) где At - прирост периода сигнала генератора 1 после его подстройки. Импульсы с выходов блока 3 поступа ют на блок 9 формирования сигналов, где формируются для исследуемого элемента 10 входной сигнал и сигнал стробирования с крутыми передними фронтами, временной сдвиг между которыми равен АТх, , после чего элемент останова формирования сигналов блока 9 переводится в закрытое состояние, запрещающее дальнейшее прохождение импульсов с выходов блока 3 формирования временного сдвига на формирователи сигналов блока 9. Сформировагшые сигналы поступают на соответствующие шины входа и стробирования исследуемого элемента 1О, который перевозбуждается в начале перепада входного сигнала. Передний фронт.этого сигнала при подстройке частоты следования импульсов управляемого генератора 1 перемещается во времени (задерживается) по сравнению с передним фронтом сигнала стробирования на величину ДТ, которая зависит от прироста периода Л-t сигнала генератора 1 после подстройки его частоты. Если при этом время задержки сигнала стробирования исследуемого элемента 10 больше сформированного временного сдвига ДТ между передними фронтами перепада входного сигнала и сигнала стробирования, то компонент стробирования элемента 10 зафиксирует сигнал, соответ ствуюший сформированному блоком 9 входному перепаду. В противном случае компонент стробирования зафиксирует сигнал, соответствующий нулевому начальному входовому уровню, так как сигнал стро- бирования появится раньше на выходе ко понента стробирования, чем перепад вход ного сигнала достигнет уровня логическо напряжения, т.е. такого уровня, который компонентом стробирования Исследуемого элемента 10 уже принимается как логич кая единица или логический нуль соответ ственно. Сигнал, зафиксированный компонентом стробирования после появления его на выходе элемента 10, дешифрируется, записьгоается в буферный регистр блока обработки и регистрации информации 6 и вьздается на индикаторы того же блока 6 для визуального наблюдения. Малое внутреннее сопротивление формиро вателя входного сигнала блока 9 уменьшает влияние входной емкости элемента 10 на время достижения входным сигналом уровня логического напряжения. Ука занное влияние уменьшается еще и тем, что элемент 10 перевозбуждается входным сигналом с крутым передним фронтом в Начала его перепада. При этом временной сдвиг ДТ на выходе блока 3 равен времени задержки сигнала стробирования исследуемого элемента 1О в момент начала изменения состо5шия ее выходной информации, что свидетельствует о том, что компонентом стробировани фиксируется начало перепада входного сигнала. Импульсы, -временной сдвиг межау передними фронтами которых /jT;( , с выходов блока 3 формирования временного сдйига поступают на входы двоичных счетчиков блока 4 расширения времени зацержки,в которых число уклацывающихся счетных импульсов одинаково и равно М. Временной сдвиг дТчу между началами им пульсов на выходах счетчиков после полного их заполнения равен ДТу.МЛТ. (2) На выходе блока формирования времен ного интервала 5 этот времнной сдвиг и Т,, транспортируется на прямоугольный импульс шириной . Передний фронт этого импульса открьтает вход для поступления счетных импульсов с выхода генератора импульсов 2 на двоично-десятичный счетчик блока 6 обработки и регистрации информации. Задний фронт импульса на выходе блока 5 формирования временного интервала закрьгаает прохождение счетных импульсов на двоично-де- сятишый счетчик блока 6, записывает информацию с этого счетчика в буферный регистр блока 6 обработки и регистрации информации, триггер разреишния блока 3 формирования временного сдвига переводит в закрытое состо1шие, а триггер разрешения блока 8 управления - на ждущий режим. Информация на буферном регистре блока 6 дешифрируется и выдается на индикаторы того же блока 6 для визуального представления измеряемого времени задержки сигнала стробирования. При совпадении передних фронтов управляемого генератора 1 импульсов и генератора 2 импульсов начинается новый цикл измерений. Число 2 , записанное на двоично-десятичном счетчике блока 6 обработки и регистрации информации, равно т Х т сс Временной сдвиг ЛТ является эквивалентным измеряемому времени задержки сигнала стробирования в компоненте стробирования исследуемой стробируемой интегральной схемы Ю, Если М и ТгМ -Я выбрать такими, чтобы ,, то измеренное время задержки будет выражено в наносекундах. Таким образом, использование предлагаемого устройства обеспечивает возможность измерения времени задержки сигналов стробирования в Компонентах стробирования интегральных стробируемых схем, не имеющих внешнего выходного вьшода этого компонента. Устройство не требует формирования дополнительного выходного вывода компонента стробирования интегральной схемы на контрольной контактной площадке ее кристалла, необходимого для проведения указанньрс измерений известным устройством. Это снижает себестоимость таких интегральных схем. Кроме того, предлагаемое устройство возможно использовать kaK у изготовителей, так и у потребителей интегральных стробируемых схем, поскольку оно обеспечивает возможность измерения времени задержки сигналов стробирования не только в отдельных кристаллах схем, имеющих дополнительные внешние выходные выходы компонента стробирования, но и в любых полностью изготовленных интегральных стробируемых схемах без таких выводов. Формула изобретения Устройство для измерения времени задержки, содержащее блок формирования

време1шого н}1тервала, блок управления, блок обработки и регистрации информации и блок расширения времени задержки, отличающееся тем, что, с целью расширения функциональных воз- 5 можностей, в него введены управляемый генератор импульсов, генератор импульсов, блок формирования временного сдвига, блок формирования сигналов и блок совпадения, причем выход управляемого ге- нератора импульсов соединен с первым входом блока формирования временного сдвига и первым входом блока совпадения, выход которого соединен с входом запуска блока управления, выход которого сое- дниен с входами сброса блока формирования временного сдвига,блока расширения времени задержки, блока с1юрмирования сигнапов и блока обработки и регистрации т1({юрмации, а выход генератора им- 20 пульсов соединен с вторым входом блока совпаде}шя, тактовым входом блока обработки и регистрации информации и вторым

входом блока формирования временного сдвига, первый выход которого соединен с первым входом блока расширения времени задержки и с управл$иошим входом блока формирования сигналов, а второй с входом стробирования блока формирования сигналов и с вторым входом блока расширения времени задержки, выходы которого соединены соответственно с входами запуска и останова блока формирования временного интервала, выход которого соединен с входом разрешения блока управления и управляющим входом блока обработки и регистрации информации.

Источники информации, принятые во внимание при экспертизе

Авторы

Даты

1983-02-28—Публикация

1981-07-15—Подача