() ЦИФРОВОЙ ГЕНЕРАТОР ГАРМОНИЧЕСКИХ ФУНКЦИЙ

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой генератор гармоническихфуНКций | 1979 |

|

SU840858A1 |

| Цифровой генератор гармонических функций | 1983 |

|

SU1224802A1 |

| Цифровой генератор гармонических функций | 1983 |

|

SU1164686A1 |

| Обратимый преобразователь координат | 1982 |

|

SU1035617A1 |

| Устройство для преобразования координат | 1983 |

|

SU1141405A1 |

| Устройство для вычисления функций синуса и косинуса | 1974 |

|

SU531161A1 |

| Цифровой преобразователь координат | 1980 |

|

SU942004A1 |

| Цифровой генератор гармонических функций | 1977 |

|

SU662927A1 |

| Синусно-косинусный функциональный преобразователь | 1981 |

|

SU970357A1 |

| Устройство для вычисления функций синуса и косинуса | 1981 |

|

SU1003081A1 |

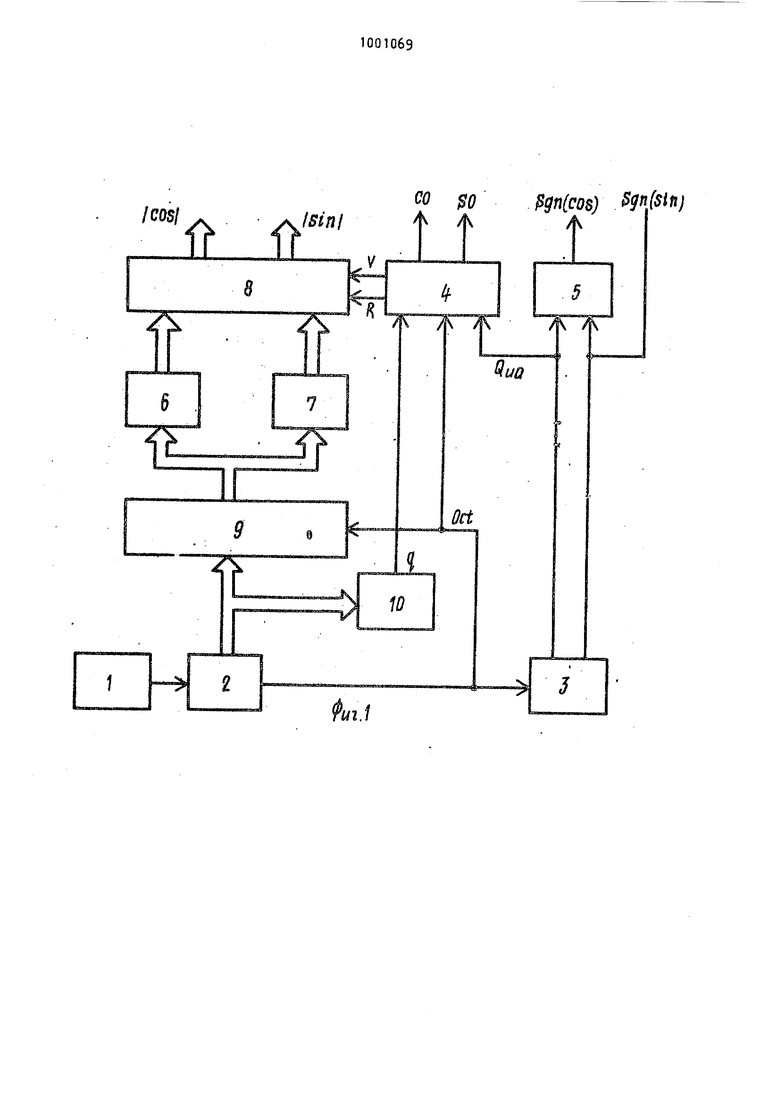

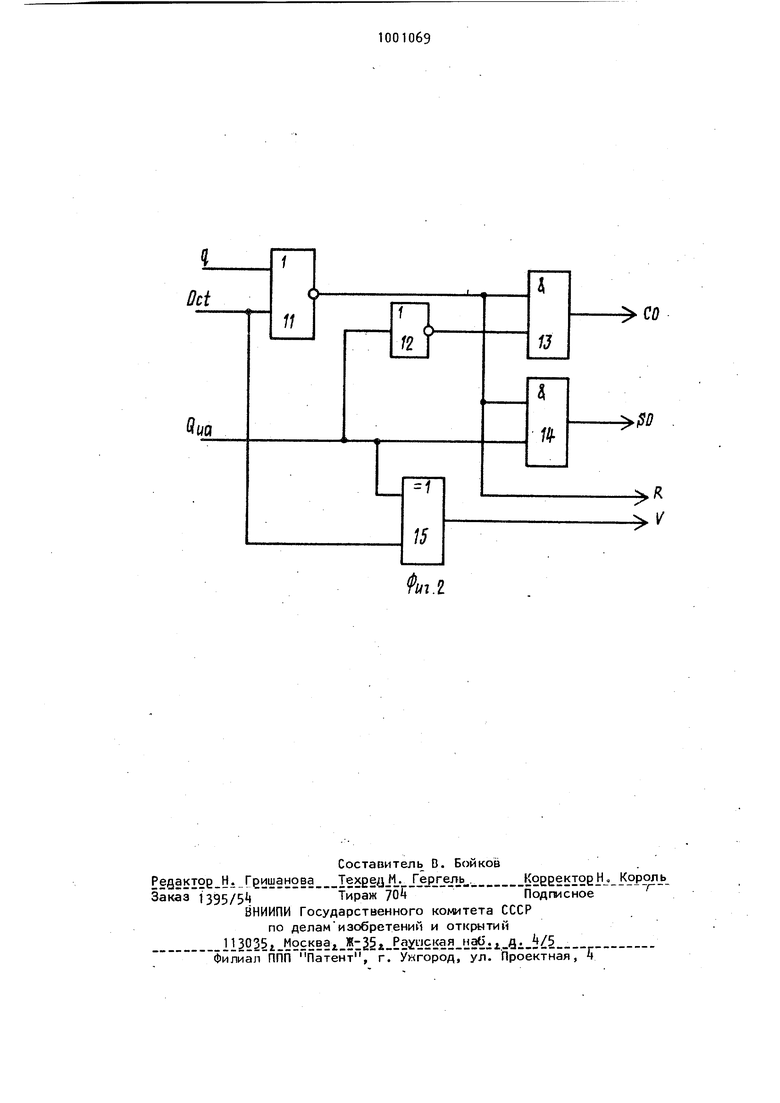

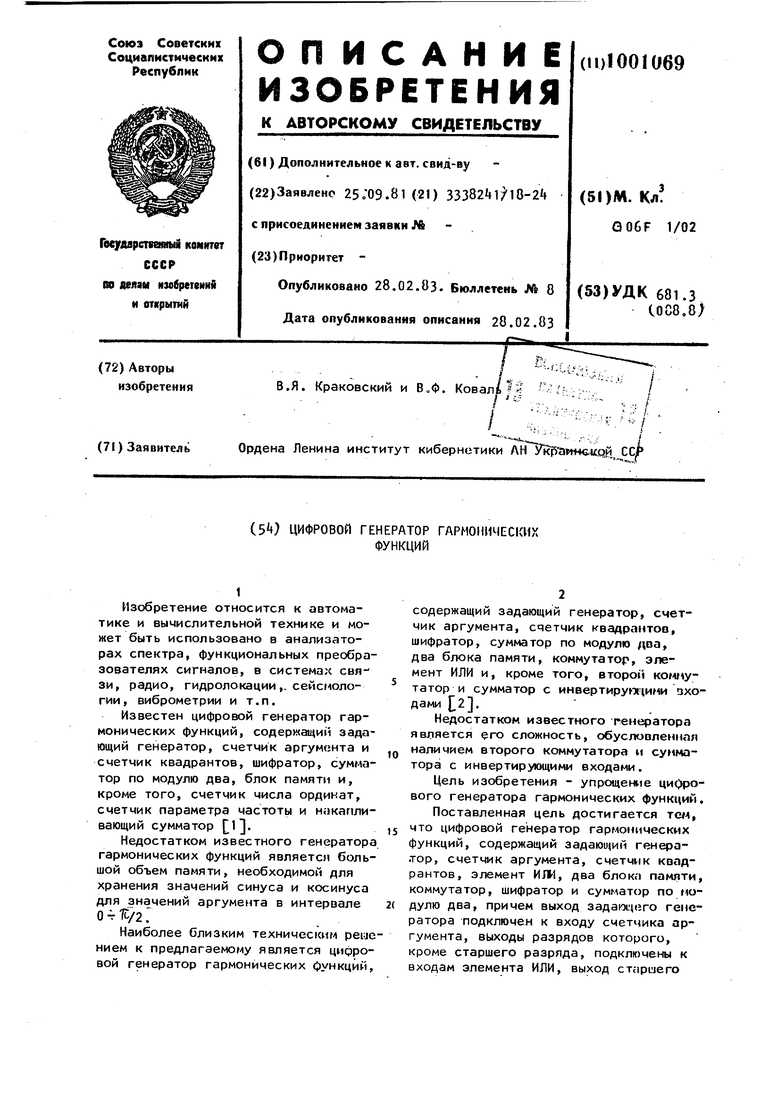

Изобретение относится к автоматике и вычислительной технике и может быть использовано в анализаторах спектра, функциональных преобразователях сигналов, в системах свя аи, радио, гидролокации,, сейсмологии, виброметрии и т.п. Известен цифровой генератор гармонических функций, содержащий задающий генератор, счетчик аргумента и счетчик квадрантов, шифратор, сумматор по модулю два, блок памяти и, кроме того, счетчик числа ординат, счетчик параметра частоты и накапливающий сумматор р. Недостатком известного генератора гармонических функций является большой объем памя ти, необходимой для хранения значений синуса и косинуса для значений аргумента в интервале Наиболее близким техническим реше нием к предлагаемому является цифровой генератор гармонических функций. содержащий задающий генератор, счетчик аргумента, счетчик квадрантов, шифратор, сумматор по модулю два, два блока памяти, коммутатор, элемент ИЛИ и, кроме того, STOpoii Kowiyтатор и сумматор с инвартиру«-1ими зходами . Недостатком известного генератора является его сложность, обусловленная наличием второго коммутатора и сумматора с инвертир «)щими входами. Цель изобретения - упрощение цифрового генератора гармонических функций, Поставленная цель достигается тем, что цифровой генератор гармонических функций, содержащий задающий генератор, счетчик аргумента, счетчик квадрантов, элемент ИЛИ, два блокп памяти, коммутатор, шифратор и сумматор по подулю два, причем выход задащиго генератора подключен к входу счетчика аргумента, выходы разрядов которого, кроме старшего разряда, подключены к входам элемента ИЛИ, выход стсчршего разряда счетчика аргумента подключенк входу счетчика квадрантов, выход элемента ИЛИ, выход старшего разряда счетчика аргумента и выход первого разряда счетчика квадрантов подключены соответственно к первому, второму и третьему входам шифратора, выходы первого и второго блоков памяти подклю чены к соответствующим информационным входам коммутатора, управляющий вход и вход запрета коммутатора подключены соответственно к первому и второму выходам шифратора, выходы первого и второго разрядов счетчика квадрантов подключены к входам сумматора по модулю два, выходы коммутатора являются выходами дробной части косинуса и си нуса генератора, третий и четвертый выходы шифратора являются выходами целой части косинуса и синуса генератора, выход сумматора по модулю два и выход второго разряда счетчика квадрантов являются выходами знаковых разрядов косинуса и синуса цифрового генератора гармонических функций, содер-2 жит блок преобразования прямого кода а дополнительный код, информационны входы которого подключены к В1,ходам разрядов счетчика аргумента, icpoiie старшего разряда, управляющий вход блока преобразования прямого кода в дополнительный-код подключен к выхо ду старшего разряда счетчика аргуме та, выход блока преобразования прям го кода в дополнительный код подклю чен к адресным входам блоков Кроме того, шифратор состоит из элемента ИЛИ-НЕ, элемента НЕ, двух элементов И и сумматора по иодугю два, причем первый и второй входы элемента ИЛИ-НЕ и вход элемента НЕ являются соответственно первым, вто рым и третьим входами шифратора, первый и второй входы сумматора по модулю два подключены соответственно к второму входу элемента ИЛИ-НЕ и к входу элемента НЕ, выход элемента ИЛИ-НЕ и элемента НЕ подключе ны к входам первого элемента И, выход элемента ИЛИ-НЕ и вход элемента НЕ подключены к входам второго элемента И, выходы элемента ИЛИ-НЕ, сумматора по модулю два, первого и второго элементов И являются соотве ственно первым, вторым, третьим и четвертым выходами шифратора. На фиг. 1 представлена функциональная схема цифрового генератора 100 9 гармонических функций; на фиг. 2 функциональная схема шифратора. Цифровой генератор гармонических функций содержит задаюи1ий генератор 1, счетчик 2 аргумента, счетчик } квадрантов, шифратор k, сумматор fj по модуло два, блоки 6 и 7 памяти, коммутатор 8, блок 9 преобразования прямого кода в дополнительный код, элемент ИЛИ 10. Шифратор k содержит элемент 11, элемент flE 12, элементы И 13 и И и сумматор 15 по модулю два. Генератор гармонических функций работает следующим образом. На периоде 27Г при шаге дискретизации д х аргумента х генератор выдает К, 2 отсчетов :)начеций синуса и косинуса. Два старших разряда кода аргумента х предстполяются счетчиком 3 квадратпов, пИ-2 младших разрядов - счетчиком /. аргумента. В первом 6 и втором 7 Плоках памяти (ПЗУ) по адресам х хранятся соответственно дробные части значений sinx и cosx для TC/k х s 7с/2 - Ь.х. Для формирования адреса при обращении к блокам 6 и 7 памяти используются ,Г1-3 глладших разряда счетчика 2. Для выработки значений синуса и косинуса произвольного угла (0 х5- ITc) формируется соответствующим о()ризом адрес и обеспечивается перекоимутация выходов блоков памяти в каналы синуса и косинуса. При этом адрес рбраце ния к блокам памяти вырабатывается блоком 9 в зависимости от значения старшего разряда счетчика 2 аргумента (Oct) таким образом, что при Oct О, блоки адресуются дополнительным (по модулю ) кодом, а при Oct . 1 прямым кодом. Если п-3 младших разряда сметчика 2 представлены нулевой кoмf5инaциeй то ка выходе элемента ИЛИ 10 сигнал q О, во всех остальных случаях . При q О и Oct О (углы вида КТС/2; К 0,1,..,) шифратор h вырабатывает сигнал R 1, которьй устанавливает на общих группах выходов коммутатора 8 нулевые значения и устанавливает значения разрядов целой части значений функций косинуса СО и синуса 50, равными соответственно СО Qua, SO Qua, где Qua - выход младшего разряда счетчика 3. Во всех остальных случаях R О, , SO О. Если Oct Qua, тю выход шифратора V О , при Oct Qua,V 1. При V О 51 коммутатор 8 на выход (cos) подает значенме кода дробной части из блока 6, а на выход (sin) - из блока 7 ПриУ 1 подключение блоков противоположно. Знаки синуса и косинуса Оор мируются на выходе старшего разряда счетчика 3 и выходе сумматора 5 по модулю два. Шифратор 1 выполняет следующие ло гические функции: R qVOct, СО - RAQua, SO RAOua V Oct Ф Qua. Предлагаемый генератор тре()ует м ший объем оборудования благодаря от сутствию сумматора и второго коммут Формула изобретения 1. Цифровой генератор гap юничec функций, содержащий задающий генера тор, счетчик аргумента, счетчик квадрантов, элемент ИЛИ, два блока памяти, коммутатор, шифратор и сумматорпо модулю два, причем выход задающего генератора подключен к входу счетчика аргумента, выходы разрядов которого, кроме старыего разряда, подключены к входам элемента ИЛИ, выход старшего разряда счет чика аргумента подключен к входу счетчика квадрантов, выход элемента ИЛИ, выход старшего разряда счетчика аргумента и выход первого разряда счетчика квадрантов подключены соответственно к первому, второму и третьему входам шифратора, выходы первого и второго блоков памя ти подключены к соответствующим информационным входам коммутатора, управляющий вход и вход запретакоммутатора подключены соответственно к первому и второму выходам шифратора, выходы первого и второго разрядов счетчика квадрантов подключены ко входам сумматора по модуло два, выходы коммутатора являются внходамм дробной части косинуса и синуса генератора, третий и четверть выхо9 . « ды шифратора являются вь( целой части косинуса и синуса генератора, выход сумматора по модулю два и выход второго разряда счетчика квадрантов являются выходами знаковых разрядов косинуса и синуса цифрового генератора гармонических функций, отли чающийся тем, что, с целью упрощения он содержит блок преобразования прямого кода в дополнительный код, информационные входы которого подключены к выхода разрядов счетчика аргумента, кроме старшего разряда, управляющий вход блока преобразования прямого кода В дополнительный код подключен к выходу старшего разряда сметчика аргумента, выход блока преобразования прямого кода в дополнительный код подключен к адресным входам блоков памяти . 2. Генератор по п. 1, о т л и - чающийся тем, что шифратор состоит из элемента ИГН-НЕ, элемента НЕ, двух элементов И и сумматора по ьюдулю два, причем первы11 и второй входы элемента ИЛИ-НЕ и вход элемента НЕ являются соответственно первым, вторым и третьим входами, шифратора, первый и второй входы сумматора по модулю два подключены соответственно к второму входу элемента ИЛИ-НЕ и к входу элемента НЕ, выходы элемента ИЛИ-НЕ и элемента НЕ подклочены к входам первого элемента И, выход элемента ИЛИ-НЕ и вход элемента НЕ подключены к входам второго элемента И, выходы элемента ИЛИ-НЕ, сумматора по модулю два, первого и второго элементов И являются соответственно первым, вторым, третьим и четвертым выходами шифратора. Источники информации, принятые во внимание при экспертизе 1,Авторское свидетелБство СССР К 662927, кл. Q06F 1/02, 1979. 2.Авторское свидетельство СССР по заявке К° 281595, , кл. G06F 1/02, 1979 Спрототип).

0 gn(cos) fsin)

Авторы

Даты

1983-02-28—Публикация

1981-09-25—Подача