Изобретение относится к области вычислительной техники и может быть использовано в специализированных вычислительных машинах, в навигационных информационно-вычислительных и управляющих системах.

Известно устройство для вычисления функций синуса и косинуса, содержащее четыре блока управления, генератор; тактовых импульсов, счетчик аргумента, четыре группы элементов И, регистр косинуса, регистр синуса, два триггера, две группы элементов ИЛИ, сумматоры приращений синуса и косинуса, счетчик коррекции 1.

Недостатком этого устройства является низкое быстродействие.

Наиболее близким по технической сущности к предлагаемому является устройство для вычисления функций синуса и косинуса, содержащее п-разрядный входной регистр, сумматор по модулю два, первый и рторой коммутаторы, реверсивный счетчик, блок памяти, число-импульсный преобразователь, блок управления, генератор тактовых импульсов, сумматоры адреса и коррекции, элементы И, ИЛИ и НЕ.

Погрешность воспроизведения функции в известном устройстве не превышает , т.е. приблизительно составляет 10 . Время вычисления зависит от положения кода угла на интервале аппроксимации и находится в пределах от 132tyj, , где t - nep:iод частоты тактовых игпульсов 12 .

Недостатком известного устройства является низкая точность.

Целью изобретения является повы10шение точности вычисления функций.

Поставленная цель достигаетск тем, что.в устройство для вычисления функций синуса и косинуса, содержащее п-разрядный входной регистр (где

15 п - разрядность аргумента), сумматор по модулю два, блок управления, блок памяти функции и блок памяти приращений, причем выход п-го разряда входного регистра соединен с первым

20 входом сумматора по модулю два и является выходом знака синуса устройства, выход (n-l)-ro разряда входного регистра соединен с первым входом блока управления и со вторым

25 входом сумматора по модулю два, выход которого является выходом знака косинуса устройства, введены (п-2)-разрядный сумматор по модулю два, первый, второй.и третий блоки

30 памяти частных произведений, первый

и второй сумматоры частных проиэведе НИИ и сумматор функции, причем вы- , ХОД1Д (п-2)-х младших разрядов входного регистра соединены с первыми входами соответствующих разрядов (п-2)-разрядного сумматора по модулю два, вторые входы которых соеди.йены с выходом блока управления, вто рой вход которого соединен с входом устройства, выходы старших разрядов (п-2)-разрядного сумматора по модулю два соединены с адресными входами блоков памяти функции и приращений, выходы средних разрядов - с первыми адресными входами первого и третье.го блоков памяти.частных произведений, выходы младших разрядов - с первыми адресными входами второго блока памяти частных произведений, : вторые адресньз входы первого и второго блоков памяти частных произведений соединены с выходами старших разрядов блока памяти приращений, выходы младших разрядов которого соединены со вторыми адресными входами третьего блока памяти частных произведений, причем выходы второго и третьего блоков частных произведений соединены соответственно с первыми и втррыми в-ходами первого сумматора частных произведений, выходы первого блока памяти частных произведений и первого сумматора частных произведений соединены соответственно с первыми и вторыми входами, второго сумматора частных произведений, выходы которого соединены с первыми .входами сумматора функций, вторые входы которого соединены с выходами блока памяти функций, выходы сумматора функций соединены с выходом устройства.

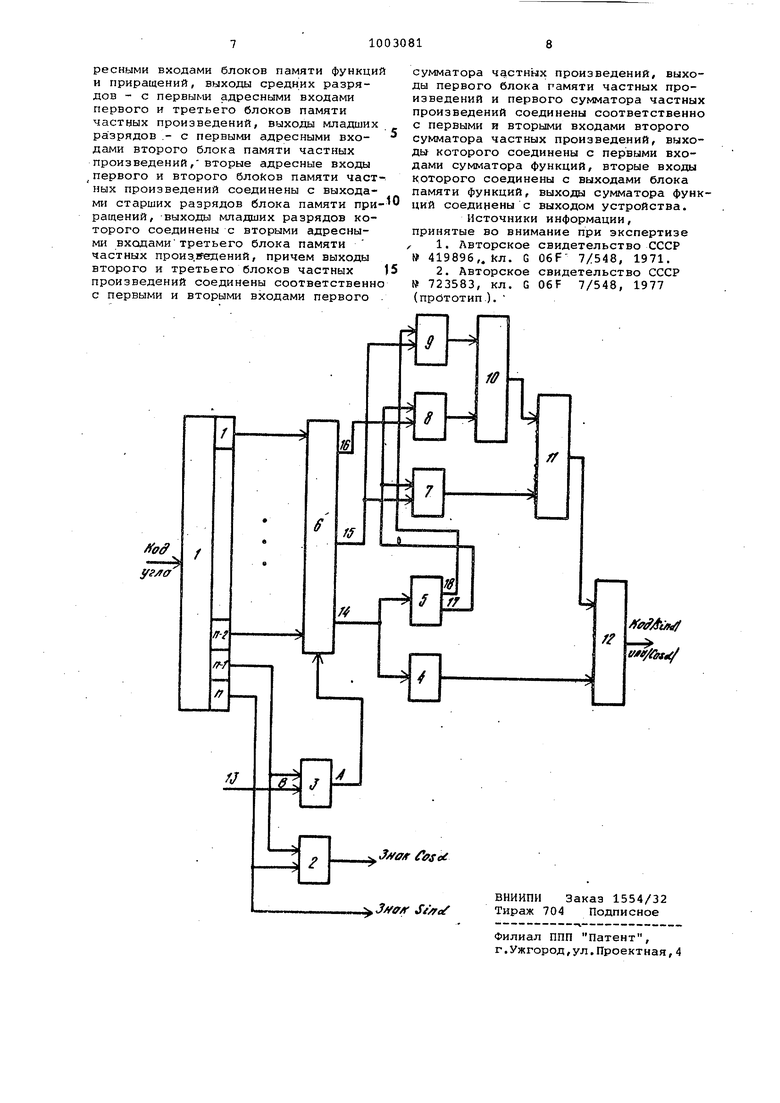

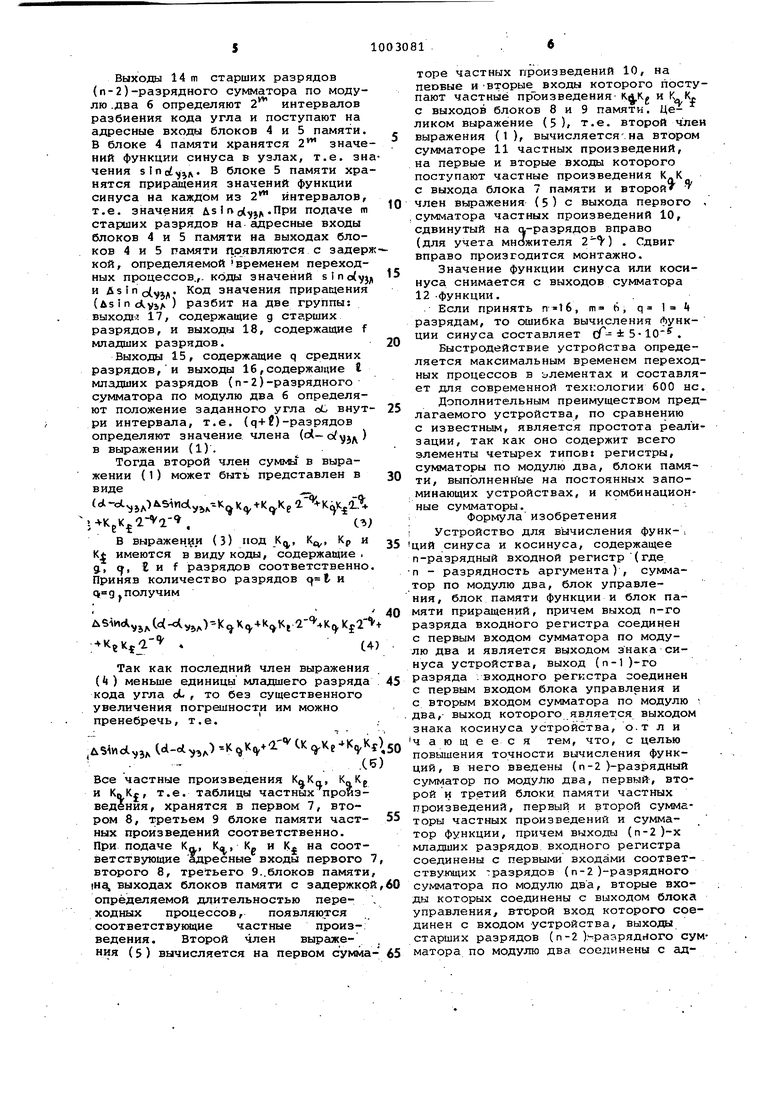

На чертеже представлена блок-схема устройства.

Устройство для вычисления функций синуса и косинуса содержит регистр 1 входной, сумматор 2 по модулю два, блок 3 управления, блок 4 памяти функции, блок 5 памяти приращений, (п-2)-разрядный сумматор 6 по модулю два, блоки 7-9 памяти частных произведений, сумматоры 10 и 11 частных произведений, сумматор 12 функции, вход 13 устройства, выходы старших 14, средних 15 и младших 16 , рядов (п-2)-разрядного сумматора по модулю два, выходы старших 17. и младших 18 разрядов блока памяти приращения.

Устройство работает следующим образом.

Вычисление функций синуса и косинуса производится в диапазоне изменения кода угла об, от О до 360 и основано на использовании кусочнолинейной аппроксимации. При этом при вычислении функций синуса и косинуса используют тригонометрические формулы приведения, позтому ниже будем рассматривать работу устройства при вычислении функции синуса.

Для вычисления функции синуса

диапазон изменения кода угла об. разбивается на одинаковых интервалов. Левую границу каждого интервала назовем узлом и значение кода угла в узле обозначим , значение

функции в узле обозначим 5 па4узЛ) приращение значения функции на каждом интервале обозначим isincs x, Тогда вычисление функции синуса может быть выполнено по формуле

,,)(). (1)

siMi-5iM i j,j(uSin ciЕсли заданный код угла ofc содержит п разрядов, то п-ый и (п-1)-й разряды определяют квадрант, в котором вычисляется функция, т-разрядов (с п-2 по n-m-2) определят номер интервала внутри квадранта, которому

принадлежит угол at , а остальные

(ц+t) младшие разряды определят положение заданного кода угла внутри интервала (т, q, i - количество разрядов, соответствующих выходам 14,

16 и 17 (п-2)-разрядного сумматора по модулю два).

В блоке 3 управления формируется управляющий сигнал Л, поступающий на второй вход (п-2)-разрядного сумматора по модулю два 6. Управляющий сигнал А формируется в соответствии с выражением

(2)

Вла„,УВАа„,

где В - признак функции, поступающий на второй вход блока 3 управления, при вычислении функции синуса; 5 h значение (n-l)-ro разряда

кода угла.

Блок 3 управления в соответствии ;: выражением (2) реализует двоичную функцию равнозначности и может бнть Q реализован последовательным включением сумматора по модулю два и инвертора.Выходы (п-2)-х младших разрядов входного регистра 1 через (п-2)-разрядный сумматор по модулю два 6 поступают на адресные входы

блоков 4, 5, 7, 8и 9 памяти. При

этом, если управляющий сигнал , т.е. всоответствии с тригонометрическими формулами приведения вычис- ляется функция косинуса, на адрес0 ные блоков 4,5, 7,8 и 9 памяти поступает обратный код угла, а .если (при вычислении функции синуса) , На адресные входы блоков 4, 5, 7, 8 и 9 памяти поступает пря5 мой код угла. Выходы 14 m старших разрядов (п- 2)-разрядного сумматора по модулю .два 6 определяют 2 интервалов разбиения кода угла и поступают на адресные входы блоков 4 и 5 памяти. В блоке 4 памяти хранятся 2 значе ний функции синуса в узлах, т.е. зн чения 51по{у5л. В блоке 5 памяти хра нятся приращения значений функции синуса на каждом из 2 интервалов, т.е. значения AS I г о1 }л-При подаче m старших разрядов на адресные входы блоков 4 и 5 памяти на выходах блоков 4 и 5 памяти появляются с задерж кой, определяемой временем переходных процессов.,, коды значений si по( и Д51По(у,. Код значения приращения (usinclkviA ) разбит на две группы: ВЫХОД1-Л 17, содержащие g старших разрядов, и выходы 18, содержащие f младших разрядов. Выходы 15, содержащие q средних разрядов, и выходы 16,содержащие I младших разрядов (п-2)-разрядного сумматора по модулю два 6 определяют положение заданного угла оС внутри интервала, т.е. (q+)-разрядов определяют значение члена (ct- ) в выражении (1). Тогда второй член суммы в выражении (1) может быть представлен в виде (d-ots, jj,-) u.,,,--K Kq,.Kp .с,; В выражении (3) под К, Kj,, Кр и К| имеются в виду коды, содержащие . g, , и f разрядов соответственно Приняв количество разрядов q t и ц дополучим ASiMA,,j,,),j, + (2-%K(K52 (4 Так как последний член выражения (k ) меньше единицы младшего разряда кода угла сС. , то без существенного увеличения погрешности им можно пренебречь, т.е. ,A5 MoL 3 W-olv3A -KqK,,K5 Все частные произведения , K.Kg и КпК, т.е. таблицы частных произведения, хранятся в первом 7, втором 8, третьем 9 блоке памяти частных произведений соответственно. При подаче Ka,i «.К. и К на соответствующие адресные входы первого 7 второго 8, третьего 9..блоков памяти, (На, выходах блоков памяти с задержкой определяемой длительностью переходных процессов, появляются соответствующие частные произведения. Второй член выргикения (5 ) вычисляется на первом сгумматоре частных произведений 10, на пеовые и вторые входы которого поступают частные прЪизведения- g и К К. с выходов блоков 8 и 9 памяти. Целиком выражение (5), т.е. второй член выражения (1), вычисляется-.на втором сумматоре 11 частных произведений, на первые и вторые входы которого поступают частные произведения К.К с выхода блока 7 памяти и второй член выражения (5 ) с выхода первого , .сумматора частных произведений 10, сдвинутый на а-разрядов вправо (для учета множителя ) . Сдвиг вправо произгодится монтажно. Значение функции синуса или косинуса снимается с выходов сумматора 12 -функции. Если принять , та 6, q разрядам, то ошибка вычисления функции синуса составляет сГ-±5-10. Быстродействие устройства определяется максимальным временем переходных процессов в элементах и составляет для современной технологии 600 не. Дополнительным преимуществом предлагаемого устройства, по сравнению с известным, является простота реализации, так как оно содержит всего элементы четырех типов: регистры, сумматоры по модулю два, блоки памяти, выпЬлненные на постоянных запоминающих устройствах, и комбинационные сумматоры. Формула изобретения Устройство для вычисления функ-. ций синуса и косинуса, содержащее п-разрядный входной регистр(где п - разрядность аргумента) , сумматор по модулю два, блок управления, блок памяти функции и блок памяти приращений, причем выход п-го разряда входного регистра соединен с первым входом сумматора по модулю два и является выходом знака синуса устройства, выход (п-1)-го разряда входного регистра соединен с первым входом блока управления и с вторым входом сумматора по модулю два,- выход которого является выходом знака косинуса устройства, о.т л и чающееся тем, что, с целью повышения точности вычисления функций, в него введены (п-2 )-разрядный сумматор по модулю два, первый, второй и третий блоки памяти частных произведений, первый и второй сумматоры частных произведений и сумматор функции, причем выходы (п-2)-х младших разрядов входного регистра соединены с пepвыIvIи входами соответствующих разрядов (п-2 )-разрядного сумматора по модулю два, вторые входы которых соединены с выходом блока управления, второй вход которого соединен с входом устройства, выходы старших разрядов (п-2 Ьраэряд ого сумматора по модулю два соединены с ад

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления функций синуса и косинуса | 1977 |

|

SU723583A1 |

| Устройство для реализации быстрых преобразований в базисах дискретных ортогональных функций | 1983 |

|

SU1115060A1 |

| Устройство для вычисления тригонометрических функций | 1985 |

|

SU1257639A1 |

| Синусно-косинусный преобразователь | 1986 |

|

SU1339555A1 |

| Устройство для вычисления функций синуса и косинуса | 1980 |

|

SU907546A1 |

| Цифровой генератор функций | 1989 |

|

SU1663607A1 |

| Устройство для вычисления функций синуса и косинуса | 1977 |

|

SU622090A1 |

| Синусно-косинусный преобразователь | 1981 |

|

SU1042013A1 |

| Синусно-косинусный преобразователь | 1986 |

|

SU1388855A1 |

| Преобразователь кода угла в коды синуса и косинуса | 1977 |

|

SU684554A1 |

Авторы

Даты

1983-03-07—Публикация

1981-10-16—Подача