(54) УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИЙ СИНУСА И КОСИНУСА

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления функций синуса и косинуса | 1981 |

|

SU960809A1 |

| Устройство для вычисления синуса и косинуса | 1978 |

|

SU781818A1 |

| Цифровой генератор гармонических сигналов | 2015 |

|

RU2616877C1 |

| Цифровой вычислитель синуса и косинуса | 1977 |

|

SU682905A1 |

| Устройство для вычисления функций синуса и косинуса | 1984 |

|

SU1205140A1 |

| Цифровой функциональный преобразователь | 1979 |

|

SU922733A2 |

| Цифровой функциональный преобразователь | 1976 |

|

SU748434A1 |

| Цифровой функциональный преобразователь | 1977 |

|

SU678488A1 |

| Синусно-косинусный функциональный преобразователь | 1981 |

|

SU970357A1 |

| Устройство для вычисления тригоно-МЕТРичЕСКиХ фуНКций | 1979 |

|

SU832555A1 |

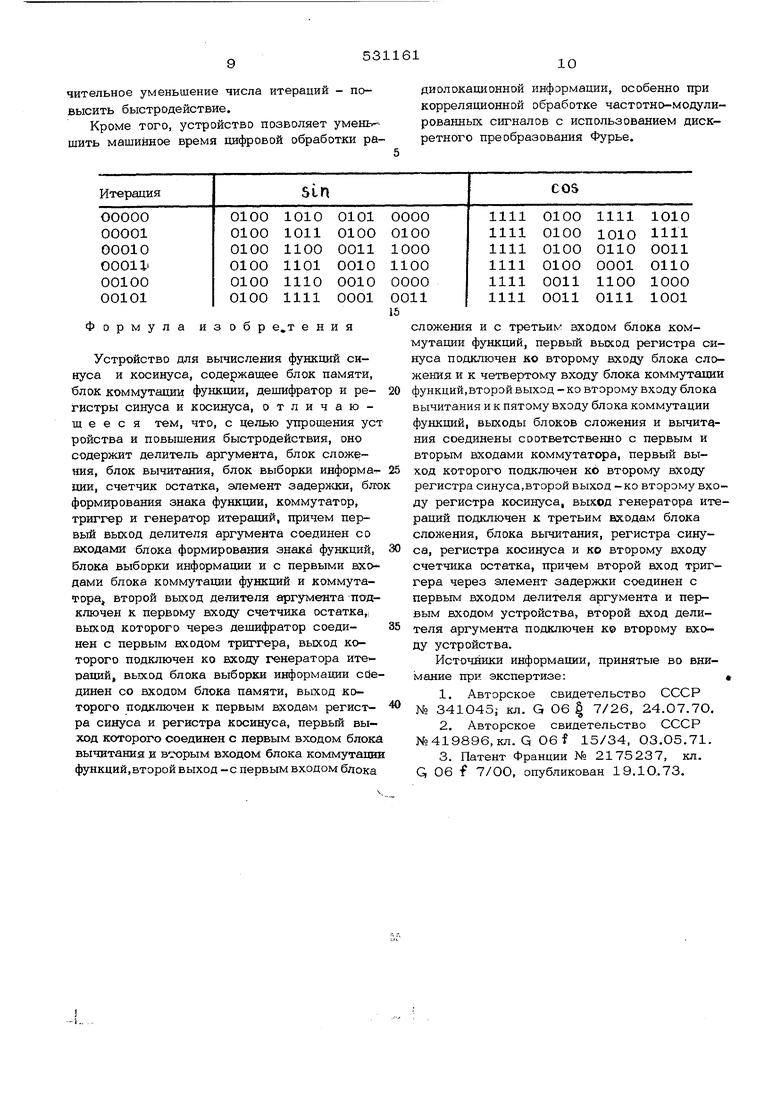

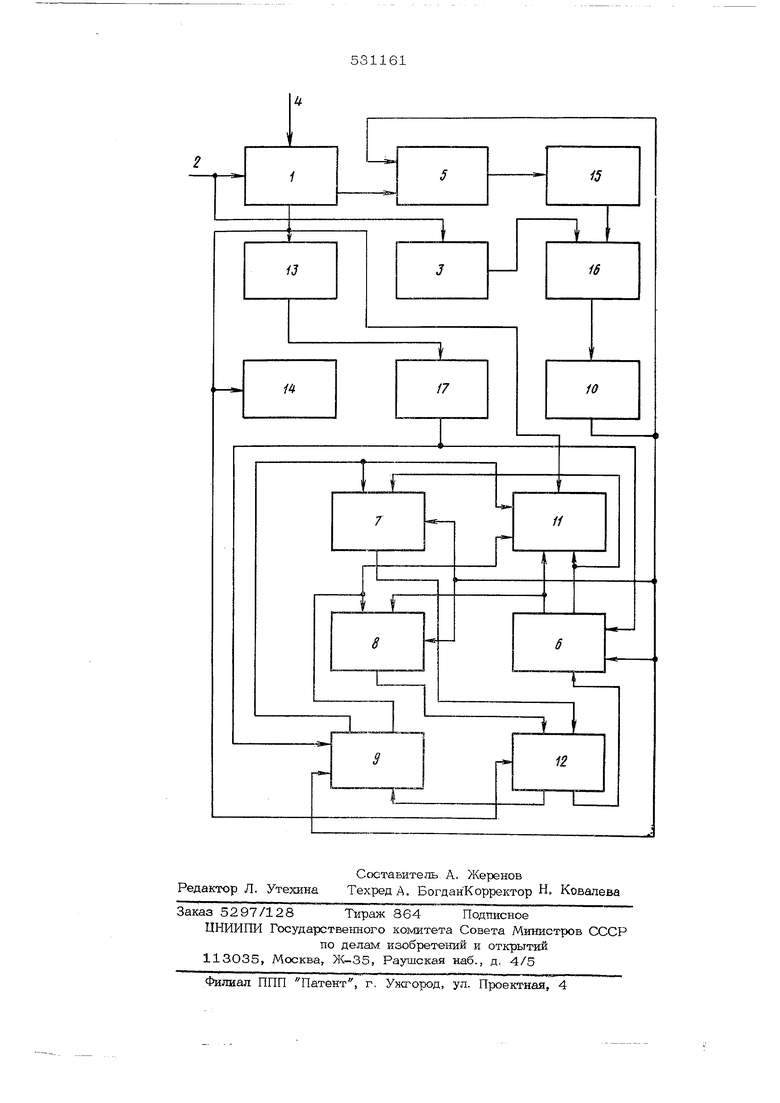

Изобретение относится к области вычислительной техники и может быть использовано в устройствах для обработки частотномодулированных сигналов при цифровой филь рации с применением дискретного преобразования Фурье. Известно устройство для определения фун ций синуса и косинуса fl , в состав которого входят триггеры, элементы И, ИЛИ, триггерный регистр, шифратор и элементы задержки. Известно-также устройство того же назначения , содержащее блоки управления, генератор тактовых импульсов, счетчик аргумента, элементы И, ИЛИ, регистры синут са и косинуса и триггеры. В известных устройствах при применении итерационного метода вычисления функ- ций синуса и косинуса при больших интервалах задания значений аргумента требует- ся значительное число итераций, что, вопервых, существенно снижает скорость вычисления функций и, во-вторых, приводит к накоплению ошибки в пределах интервала з Дания значения аргумента. Из известных устройств наиболее близким по технической сущности к изобретению является устройство для вычисления синуса и косинуса угла, выраженного в двоичном коде 3 . Это устройство содержит блок памяти, блок коммутации функций, дешифратор и регистры синуса и косинуса, В устройстве для вычисления синуса и косинуса угла разряды, представляющие значение угла в выводятся с разрешением Д& на информационные входы регистра. На выходах этого регистра сначала появляются значения 0- - дв . Кроме того, выходы регистров связаны с помощью инверсной схемы, имеющей два устойчивых состояния, с выходами блока памяти (ПЗУ). В зависимости от состояния инверсной разрядной схемы на выходах ЗУ появляется либо значение синуса в , либо синус угла, значения разрядов которого инвертированы относительно разрядов со значениями (0 - д в) , т.е, угла (). Устройство может быть использс)вано для почти одновременного определения синуса и косинуса угла Q-, значения которого вьфажены в цифровой форме Известное устройство, в принципе, решае задачу вычисления функций синуса и косину са. Однако использование табличного ЗУ со значениями синусоидальной функции от О до ТГ/2 существенно усложняет устройство и не позволяет одновременно определять значения синуса и косинуса по заданному значению аргумента. Целью изобретения является упрощение устройства и повышение быстродействия. Поставленная цель достигается тем, что предложенное устройство содержит делитель аргумента, блок сложения, блок вычитания, блок выборки информации, счетчик остатка, элемент задеряски, блок формирования знака функции, коммутатор, триггер и генератор итераций. Первый выход делителя аргумента соединен со входами блока формирования знака функций, блока выборки информации и с первыми входами блока коммутации функций и коммутатора. Вто рой выход делителя аргумента подключен к первому входу счетчика остатка, выход которого через дешифратор соединен с первым входом триггера, выход которого подключен ко генератора итераций. Выход блока выборки информагате соединен со вх дом блока памяти, вьзхсд которого подключек к первым входам регистра синуса и ре гистра косинуса, первый выход которого соединен с первым входом блока вычитания и вторым входом блока коммутации фун ций, второй - с первым входом блока ело;; ения и с третьим входом блока коммутации функций. Первый выход: регистра синуса подключен ко второму входу блока сложения и к четвертому входу блока ко.ммутации функций,втэрэй выход -ко второму входу блока вычитания и к пятому входу блока ко мутации функций. Выходы блоков сложения и вычитания соединены соответственно с первым и вторым входами коммутатора, пе вый выход которого подключен ко второму входу регистра синуса,второй выход -ко вторэ му входу регистра косинуса.Выход генератора итераций подключен к третьим входам блока сложения, блока вычитания, регистра си нуса, регистра косинуса и ко второму входу счетчика остатка, второй вход триггера через элемент задержали соединен с первым входом делителя аргумента, и первым входом устройства. Второй аход делителя аргумента подключен ко второму входу устро ства. Это позволяет воспроизводить элементар ные тригонометрические функции при дискретном задании аргумента при помощи итерационного принципа с использованием блоа памяти для опорных значений функций. На чертеже представлена функциональная схема устройства, где обозначены: делитель 1 аргумента, вход 2 устройства, элемент 3 задержки; вход 4 устройства для ввода делителя, счетчик 5 остатка, регистр 6 синуса, блок 7 сложения, блок 8 вычитания,регистр 9 косинуса, генератор 10 итераций, блок 11 коммутации функций, коммутатор 12, блок 13 выборки информации, блок 14 формирования знака функций, дешифратор 15, триггер 16 и блок 17 памяти. В исходном состоянии по входу 4 на делитель 1 аргумента вводится постоянное число - двоичная часть от 1Т (например, 1Г / 3 2 ). Триггер 16 устанавливается в нулевое состояние, ив блок 17 вводятся опорные значения функций (в данном случае для аргументов ГГ/52, ,, ТГ/Ъ2 --. Sir/32 , т.е. восемь значений, так как при аргументе, прев ыьиающем 81Т/52 - fl/ можно пользоваться формулами приведения. Значение аргумента в двоичном коде записывается в делитель 1 аргумента, в котором осуществляется деление на ТГ /32, В результате деления образуется число, в котором остаток (используются только пять разрядов), определяющий число итераций, н параллельном коде записывается в счетчик о остатка, в определенные разряды усеченной целой части (в данном случае шесть младших разрядов) вводятся в блок 14 формирования знака функций, блок 13 выборки информации, блок 11 коммутации функций и в коммутатор 12. В блок 13 выборки информация поступает с четырех младщих разрядов целой части. Согласно значению трех разрядов, определяющих микроинтервал, из блока 17 памяти должны быть считаны и записаны в регистр 6 синуса и регистр 9 косинуса соответствующие значения функций. При этом значение четвертого разряда показывает, какой восьмой части круга принадлежит аргумент - 0,11:/4 или Т1/4,К/2. Значение О указывает на промежуток 0,ТГ/4 и соответственно на считывание из блока 17 значений функций, поставленных в соответствие значению трех младших разрядов целой части. Значение 1 указывает на промежуток It/4-, IT/Z 3 и соответственно, - на считывание из блока 17 последующих значений функций синуса и кснсинуса, что соответствует зеркальному значению аргумента в промежутке О,IT/43 В этом случае в коммутаторе 12 осущест вляется переключение выходов блока 7 еложения и блока 8 вычитания, т.е. производится интегрирование назад. В блок 14 поступает информация с пятого и шестого разрядов целой части, указывающая номер квадранта и соответствен- но, знак функций синуса и косинуса. В блоке 11 коммутации функций информация чет вертого и пятого разрядов указывает на не обходимость реверса функций. При введении аргумента записи в регист ры 6 и 9 соответствующих значений функций с задержкой, определенной элементом 3 задержки, триггер .16 перебрасывается в единичное состояние, и запускается генератор 10 итераций. В этом случае число, образованное первой половиной разрядов в регистре 9 коси нуса, прибавляется к числу, образованному второй половиной разрядов регистра 6 синуса, и следовательно, в регистре 6 синуса устанавливается число, превышающее исходное на величину, соответствующую одной итерации. Число, образованное первой половиной разрядов регистра 6 синуса, вычитается из числа, образованного второй половиной разрядов регистра 9 косинуса и, следовательно, в регистре 9 косинуса устанавливается число, меньшее исходного на вели,чину также соответствующую одной итерации. Описанная процедура накопления в регистрах 6,9 повторяется до тех пор, пока не будет вы чтено из счетчика 5 остатка значение остатк В этом случае с выхода дешифратора 15 (например, многовходового элемента И) сигналом, фиксирующим нулевое состояние счетчика 5 остатка, триггер 16 устанавливается в единичное состояние и генератор 10 итераций затормаживается. При этом на выходе устройства формируются значения функций синуса и косинуса, а также знак функций, указывающий их принадлежность соответствующему номеру октанта. Работа устройства основана на использовании двух математических принцкшов: на вычислении функций синуса и косинуса как решения системы дифференциальных уравненийметодом Эйлера и на предварительном деле нии аргумента на постоянное число - двоич ную долю от ТГ - с целью определения знаков синуса и косинуса, а также определения начальных условий. Для этого выбираются две константы; шаг решения и шаг, с помощью которого задаются начальные условия. В качестве первого шага выбирается целая отрицательная степень двойки и в качестве второго - число 1Г/4, умноженное на целую отрицательную степень двойки. Предположим, например, что выбраны, соответственно, 1/256 0,00000001 ( и 17/4:8 0,00001(.i)1t. Это означает, чти система решается со значением итерации 1/256 и с исходными данными, соответствующими аргументу из совокупности значений 0,11/32, 2ТГ/52, ,..., 8 IT/32 5 ближайших к заданному значению аргумента. Следовательно, при решении системы для любого аргумента необходимо выполнять не более (It / 32 : 1/256) Pi 25 итераций. Для вычисления функций синуса и косинуса произвольного аргумента заданное значение аргумента делится на « 0,000110О10010О01О(2.) причем используются только шесть младших разрядов целой части частного и пять разрядов (с четвертого по восьмой после запятой) остатка от деления. Разряды частного с седьмого и старще отбрасываются, так как они лишь указывают, сколько раз в аргументе содержатся 2ТС, т.е. период. Шестой и пятый разряды указывают номер квадранта, в который попадает аргумент после вычитания из него кратного 2 fC /00-1 квадрант, 01- II квадрант, 10 - II квадрант и 11 - IV квадрант). значения определяют знаки функций синуса и косинуса (00: ++, О1:+-, 10: -,).. Четвертый и пятый разряды несут информа- цию о наличии или отсутствии необходим ос- ти реверса синуса и косинуса согласно фор мулам приведения: если эти разряды одинаковы, то синус и косинус сохраняют свои наименования, если же разряды различны, то синус и косинус меняются ролями. Четвертый разряд целой части показывает, какой восьмой части круга принадлежит аргумент после вычитания из него кратного И/2: значение О указывает на промежуток О, tl/4l, значение 1 - на промежуток tr/4; .It/a. В первом случае (если четвертый разряд есть О) обе функции находят непосредственно от аргумента, редуцированного по модулю 1Г/4 (поскольку редукция по модулю tr/4 равнозначна тогда редукции по модулю Я/2, и дальше необходимо лишь использование формул приведения), во.втором случае(если четвертый разряд есть 1) их находят от дополнения аргумента, редуцированного по модулю 1Г/4, до 1Г/4. Например, если исходный аргумент ot-Q равен ТГ/6 € (О Тс/4), т.е. четвертый разряд - О, то находятся гфямо Sin oL о и Cos d-Q . Если же с1.о ТС/3 (,ТГ/4, 11/2), т.е. четвертый разряд - 1, то после редукции по модулю 17/4 получается о сС 1Г/4 -с1 , а дополнение равно ЗТ/6, причем Cos ai , Sin cL о Cos 51Л л . Далее три младших разряда целой части частного указывают на микроинтервал интегрирования, а пятиразрядный остаток (с четвертой цифры по вйсьмую после запятой на число итераций, которые необходимо выполнить при интегрировании системы. Рассматривается сначала случай, когда четвертая цифра целой части частного равна О, т.е. d. е С О, ТГ /4 , где сС -аргу мент после редукции по модулю ТС/4. Тогда соответствие между младшей тройкой разрядов целой части частного и микроинтервалом интегрирования будет такое: ООО - I О, ТС /32 ; 001 - С П /32, 2 П /3 ОЮ- 2 1с /32, 3 IT/321;,.,; 1t/32, ТГ /41. Пятиразрядньй остаток означает число итераций, которое необходимо сделать при интегрировании системы вперед. Например, если младшая тройка частного есть 011, а остаток равен 01000, то будет сделано .) 9 шагов от начальных зн чений Sin и COS 311/32, которые вызываются из блока памяти на регистры. Рассмотрим случай, когда четвертая ци ра целой части частного равна 1, т,е oL 1Г/4, ТГ/2. Тогда соответствие между младшей тройкой и микроинтервалом зеркально по отношению к вышеприведенному: 000 - L 7 11/32, 17/43; 001 - б Tl 71Г/32. 1Г/32, 671/32 ;....; Ill , It/32. Пятиразрядный остаток на этот раз пре ставляет уже число итераций не вперед а назад - от верхнего предела микроинтервала. Интегрирование вьшолняется по формуламY. Y-+О,ОООО OOO-I , пЧч г-0.0000 oooi.. В качестве примера рассмотрим ние51Т1о1оИ 1 0000, 000 0101 1100 0010, При делении сСд на 1Г/32,й: 0,00011001 0010 001О целая часть частного равна 10100011, а остаток составляет 0,0000 0101 О001 1100. Две старшие цифры частного (10) не нужны,так как они показывают лишь,что о 4ТС . Отбрасывая иХ (в устройстве это делается автоматически), получаем 100О11. От остатка сохраняются лишь цифры с четвертой по восьмую ( в устройстве это также выполняется автоматически), т.е. 00101. Принимая во внимание сущность описанного алгоритма, видно, что угол принадлежит) квадранту и после приведения по - к первой восьмой части. Это значит, что перед обеими функциями нужно взять знак минус. Далее интервал интегрирования ГЗЯ732, 4 jr/32j . Число итераций интегрирования равно (при значении остатка 00101) пяти, В случае из ЗУ считываются значения ЗТг/32 и cos g равные в двоичной записи О,010О1010О1001101 и ОД11101001111101 соответстве1шо. Указанные значения записываются в регистр синуса и в регистр косинуса только дробными частями. Решение системы состоит в том, что при каждой итерации текушее значение косинуса сдвигается на восемь разрядов вправо, тфибавляется к текущему значению синуса и после этого полученное значение синуса, сдвинутое на восемь разрядов вправо, вычитается из текущего значения косинуса. Процесс заканчивается после пятой, итерации. Промежуточные вычисления сведены в таблицу. Истинные значения синуса и косинуса этого угла с точностью до шестнадцатого двоичного знака равны соответственно 0,0100, 1111 О001 0101 и 0,1111 ООН 0111 1О10, т,е, погрешность в данком случае составляет одну или две единицы шестнадцатого двоичного знака после запятой. Используя формулы приведения (инфор - мация от шестого, пятого и четвертого разрядов uejiOii части) получаем окончательно S-iTioC,..0,0100 1111 ООО1 ООН, Cos ,1111 ООН 0111 1О01. Таким образом, использование принципа вычисления функций синуса и косинуса как решения системы дифференциальных уравнений, предварительное деление аргумента на постоянное число с целью определения знаков синуса, косинуса и начальных условий, а также использование небольшого по объему блока памяти для опорных значений функций позволяет существенно повысить точность вычисления синуса и косинуса, а значительное уменьшение числа итераций - повысить быстродействие.

Кроме того, устройство позволяет умень-шить машинное время цифровой обработки раФормула изобр е.т е н и я Устройство для вычисления функций синуса и косинуса, содержащее блок памяти, блок коммутации функции, дешифратор и регистры синуса и косинуса, отличающееся тем, что, с целью упрощения уст ройства и повышения быстродействия, оно содержит делитель аргумента, блок сложения, блок вычитания, блок выборки информа-т ции, счетчик остатка, элемент задерлжи, бл формирования знака функции, коммутатор, триггер и генератор итераций, причем первый выход делителя аргумента соединен со входами блока формирования знака функций, блока выборки информации и с первыми вх дами блока коммутации функций и коммутатора, второй выход делителя аргумента подключен к первому входу счетчика остатка,; выход которого через дешифратор соединен с первым входом триггера, выход которого подключен ко входу генератора итераций, выход блока выборки информации cde динен со входом блока памяти, выход которого подключен к первым входам регистра синуса и регистра косинуса, первый выход которого соединен с первым входом блока вычитания и всчэрым входом блока коммутаци функций,второй выход -с первым входом блока

диолокационной информации, особенно при корреляционной обработке частотно-модулированных сигналов с использованием дискретного преобразования Фурье. сложения и с третьим входом блока коммутации функций, первый выход регистра оинуса подключен ко второму входу блока сложения и к четвертому входу блока коммутации функций,второй выход - ко второму входу блока вычитания и к пятому входу блока коммутации функций, выходы блоков сложения и вычитания соединены соответственно с первым и вторым входами коммутатора, первый выход которого подключен ко второму входу регистра синуса,второй выход -ко второму входу регистра косинуса, выход генератора итераций подключен к третьим входам блока сложения, блока вычитания, регистра синуса, регистра косинуса и ко второму входу счетчика остатка, причем второй вход триггера через элемент задержки соединен с первым входом делителя аргумента и первым входом устройства, второй вход делител;я аргумента подключен ке второму входу устройства. Источники информации, принятые во внимание при экспертизе: 1.Авторское свидетельство СССР № 341045; кл. G Об 7/26, 24.07.7О. 2.Авторское свидетельство СССР №419896, кл. Q Об f 15/34,03.05.71. 3.Патент Франции № 2175237, кл. Q 06 -f 7/ОО, опубликован 19.10.73.

Авторы

Даты

1976-10-05—Публикация

1974-11-04—Подача