Изобретение относится к радиоэлектронике, представляет автогенератор электрических колебаний, номинальные значения частоты генерации которых определяются числовым эквивалентом внешнего управляющего кода, и может использоваться в устройствах различного назначения, например, в качестве управляемых гетеродинов или датчиков дискретного множества частот.

Аналогом предлагаемого устройства может служить синтезатор с предварительной установкой УГ [1] , содержащий входную шину fог частоты опорного генератора, выходную шину частоты управляемого генератора, делитель с фиксированным коэффициентом деления (ДФКД) частоты fог, фазовый детектор Д, фильтр нижних частот (ФНЧ), аналоговый сумматор (СМ) напряжения eупр1 и напряжения предустановки eупр2, управляемый генератор (УГ), делитель с переменным коэффициентом деления (ДПКД) частоты fуг, дешифратор (ДШ) кода N предустановки, цифроаналоговый преобразователь (ЦАП), формирующий eупр2, и кодовую шину (Код для N).

Диапазон перестройки УГО разделен на ряд поддиапазонов, а предварительная установка fуг производится подачей на второй вход См напряжения eупр2 с выхода ЦАП. Точная установка fуг осуществляется системой ИФАПЧ с помощью напряжения eупр1, формируемого фазовым детектором Д и ФНЧ.

Наиболее близка по технической сути и наличию существенных признаков к предлагаемому устройству схема для цифровой установки частоты автогенератора фиг. 1 и 2 (Schaltung zur digitalen Frequenzeinstellung eines Oszillators, Fig1 und 2) [2] , содержащая 1 автогенератор (УГ), управляемый по 8 входу напряжением Ur, выходную 2 шину сигнала с частотой fx, вентильную 3 схему, содержащую четыре 9, 10, 11, 12 JK-триггера, три 13, 14, 15 двухкодовых вентиля, двухвходовый 16 элемент ИЛИ и два 17, 18 инвертора, первый 4 счетчик счетного времени колебаний с частотой fx, второй реверсивный 6 счетчик с 6a параллельными выходами, соединенными со входами 6b регистра 7 преобразователя код-напряжение (ПКН), формирующего напряжение Ur, управляющее частотой fx, например, с помощью варикапа (Kapazitatdiode).

У выбранного прототипа кольцо автоподстройки частоты до номинального значения функционирует по принципу электронно-счетного частотомера (ЭСЧ), когда число колебаний с периодом 1/fx подсчитывается первым счетчиком за время T0, равное длительности номинального мерного интервала (Soll-Zeitintervall), одновременно сравниваясь с соответствующим этому интервалу номинальным числом колебаний (Soll-Schwingungzahl). При этом число колебаний, отличное от номинального, с учетом знака расстройки, поступает на V- или R-вход реверсивного 6 счетчика, а результат управляемого счета преобразуется в регулирующее напряжение Ur, воздействующее на параметрический элемент резонатора УГ.

Быстродействие таких устройств оценивается длительностью переходного процесса с момента включения мерного интервала (или изменения коэффициента деления первого 4 счетчика), по истечении которого значение частоты fx приближается к номинальному с заданной точностью.

Дискрет перестройки частоты Δf на единицу счета ЭСЧ-предельная аппаратурная точность - определяется заданной длительностью T0 мерного интервала и не зависит от номинала измеряемой частоты Δf = 1/To (Гц), где T0 в (с), который определяет информационную емкость N счетной структуры, задающую число n ее двоичных разрядов n≥log2N, где N=T0•fxмакс.

К технической сложности названного прототипа, влияющей на длительность переходного процесса при определении величины частотной расстройки относительно номинала, можно отнести использование двухступенчатой счетной схемы с реверсивным 6 счетчиком конечного результата и коммутацией направления счета комбинационной вентильной 3 схемой.

Кроме вышесказанного, прототипу, использующему счетчики позиционного двоичного кода (ПДК), свойственны ограничения по предельному значению частоты счета из-за возможных сбоев в многоразрядной схеме с промежуточной коммутацией направления счета.

Задача, решаемая предлагаемым устройством, состоит в повышении его быстродействия во время установления заданного значения частоты колебаний fxi при ограниченном мерном интервале, за счет использования специализированного ДПКД, вычисляющего абсолютную величину ее расстройки относительно номинала и определяющего знак ошибки при подсчете заданного числа периодов колебаний диапазонного автогенератора.

Для ее решения использованы следующие технические средства:

- предлагаемый ДПКД построен на основе многоразрядного синхронного счетчика импульсов в коде Грея с параллельной предустановкой исходных данных, конечное состояние которого, после подсчета текущего числа колебаний, преобразуется в управляющее воздействие на частотозависимые элементы резонатора при автоподстройке частоты генератора до номинала;

- для задания длительности T0 мерного интервала в состав устройства введен собственный ДФКД, тактируемый импульсами внешнего генератора эталонной частоты с дискретами 1/f0, а для точного заполнения мерного интервала дискретами 1/fx анализируемой частоты fx применен управляющий RS-триггер, одновременно открывающий входы ДФКД и ДПКД выходными импульсами с длительностью T0;

- для ускорения вхождения генератора в синхронизм после записи управляющего кода, частота генерации fx перед включением ее измерения, предварительно с допустимой точностью, устанавливается в окрестности нужного номинала fxн за счет выбора емкости фиксированной величины из набора элементов в составе резонатора.

При постоянной длительности T0 мерного интервала число Nx периодов колебаний, подсчитываемое за время измерения, пропорционально частоте генерации fx:

Nx=T0•fx; Nxмакс=T0•fмакс; Nxмин=T0•fxмин; ΔNx= Nмакс-Nмин.

Диапазону перестройки частоты ΔF = fмакс-fмин с запасом на краях и учетом естественной нестабильности соответствует разность ΔN = Nмакс-Nмин..

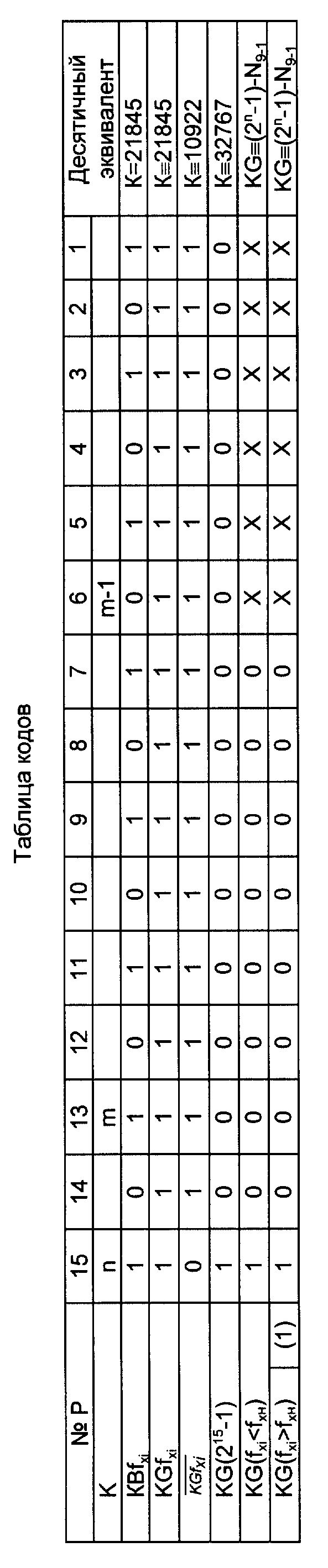

После подсчета за время измерения реального числа колебаний с периодом 1/fxi порядка (n-1)-(m-l) JK-триггеров старших разрядов ДПКД переходят в состояния логического нуля, n-й JK-триггер - в состояние логической единицы, а JK-триггеры младших разрядов с первого по (m-l)-й регистрируют остаточный код Грея, числовое значение которого, соответствующее естественной нестабильности частоты генератора, служит для преобразования в управляющие воздействия на параметры резонатора автогенератора.

Абсолютная величина информационной емкости m-l названных JK-триггеров счетчика импульсов в 2m-l-1 единиц счета соответствует десятичному эквиваленту кода наибольшей величины естественной расстройки частоты автогенератора относительно номинального значения.

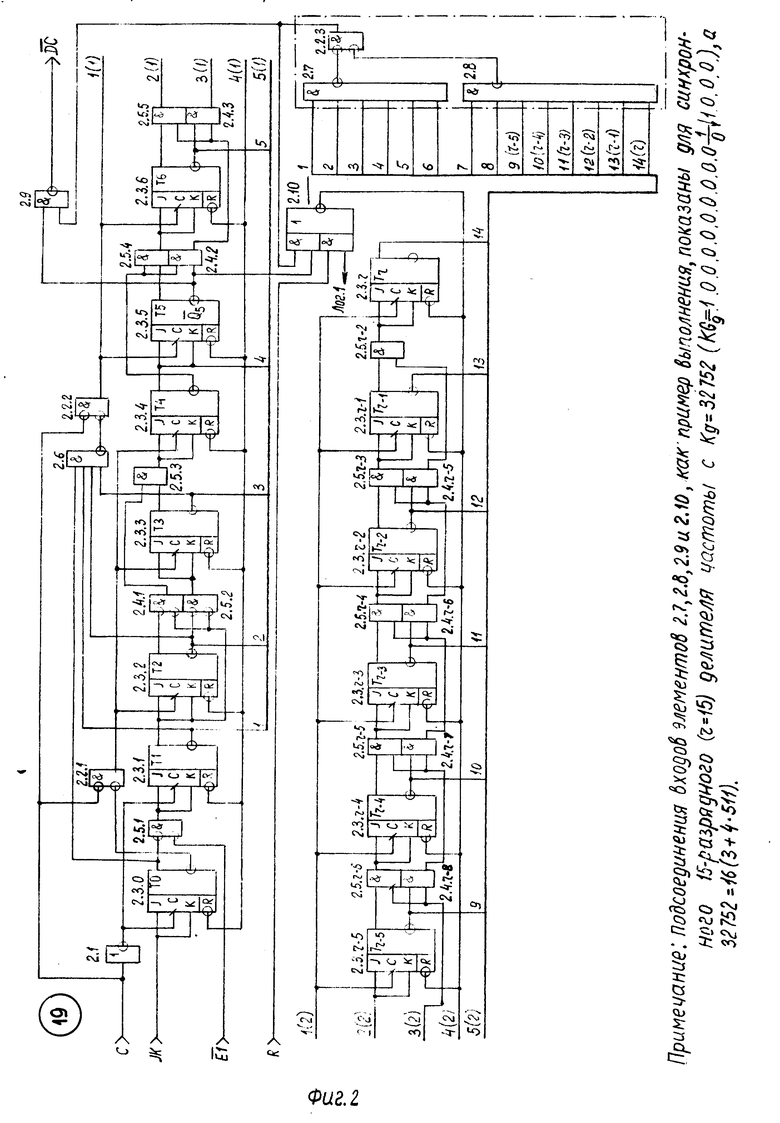

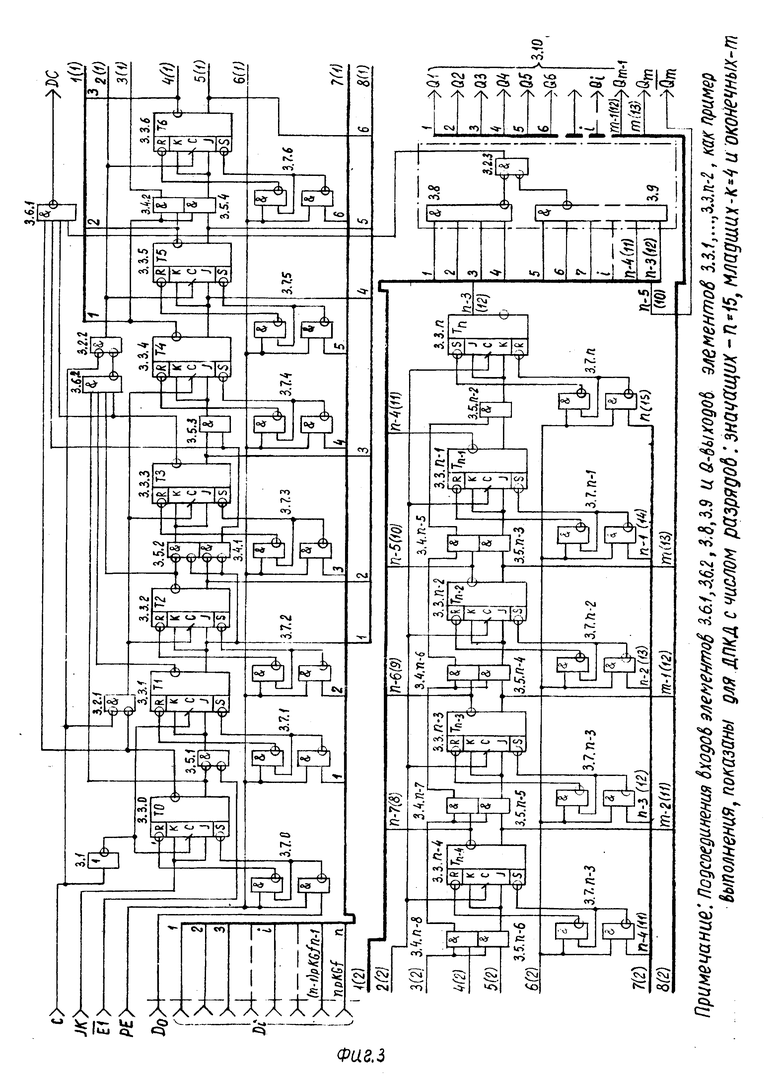

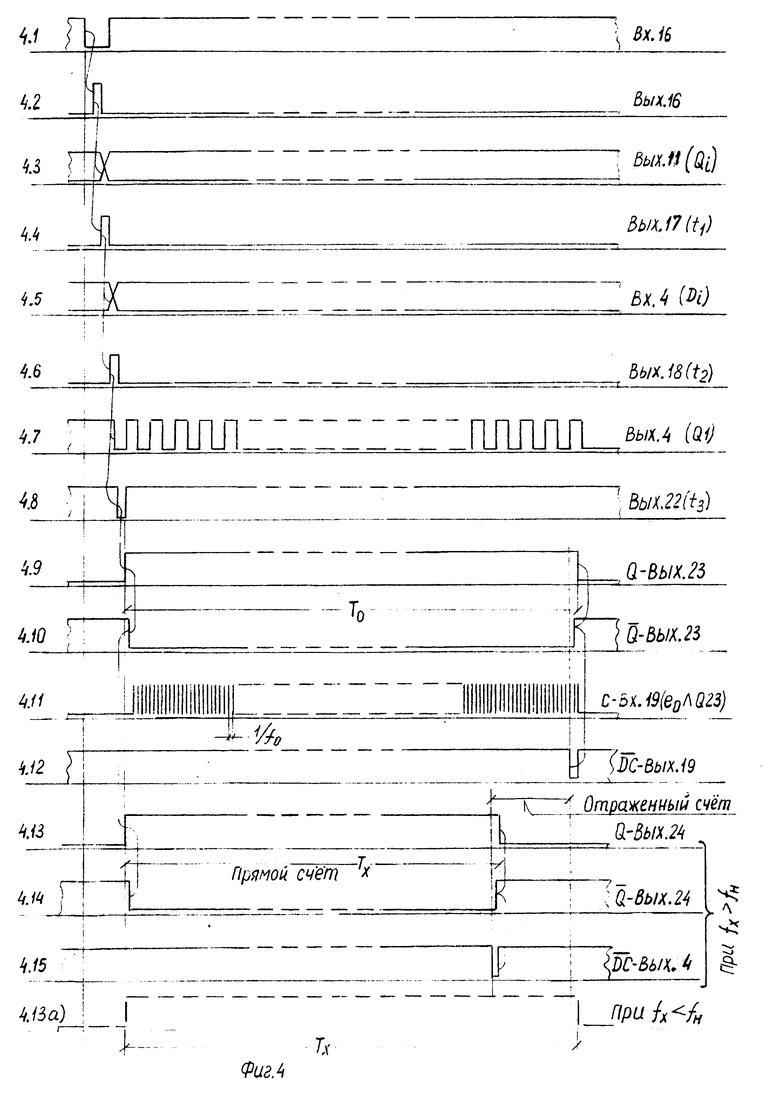

На фиг. 1 приведена электрическая функциональная схема управляемого генератора с предустановкой частоты; на фиг. 2 развернутая функциональная схема ДФКД (элемент 19 фиг. 1); на фиг. 3 развернутая функциональная схема ДПКД (элемент 4 фиг. 1); на фиг. 4 временные соотношения, поясняющие процесс управления подстройкойи частоты автогенератора G (элемент 1 фиг. 1), а на фиг. 1a - фрагмент временных соотношений, поясняющий формирование импульса  на выходе ДПКД в момент "отражения" счета в его счетчике импульсов, когда текущее значение fxi частоты колебаний превышает номинальное fxн.

на выходе ДПКД в момент "отражения" счета в его счетчике импульсов, когда текущее значение fxi частоты колебаний превышает номинальное fxн.

Устройство (фиг. 1) содержит, соединенные в кольцо 1 автогенератор G электрических колебаний с p-входовой 1.1 шиной дискретных команд и с аналоговым 1.2 входом, сигнальную 2 шину выхода fx частоты колебаний, подключенную к входу 3 формирователя импульсов с периодом 1/fx, выход которого соединен с C-входом синхронизации делителя 4 с переменным коэффициентом деления (ДПКД), элемент 2х2И-ИЛИ-НЕ 6 с m-входовым 5 преобразователем кода Грея в позиционный двоичный код (ПДК), у которого m выходов поразрядно подключены к m входам Bj-группы входов m-разрядного 7 сумматора ПДК, m выходов которого поразрядно подключены к m входам m-разрядного 8 регистра ПДК, у которого l выходов старших разрядов поразрядно подключены к l входам 9.1 потенциального дешифратора, который является первым элементом функционального 9 преобразователя, а m-l выходов младших разрядов m-разрядного регистра ПДК поразрядно подключены к m-l входам 9.2 преобразователя ПДК-напряжение, который является вторым элементом функционального 9 преобразователя, p выходов которого поэлементно подключены ко входам p-входовой 1.1 шины дискретных команд 1 автогенератора G электрических колебаний, аналоговый 1.2 вход которого соединен с выходом 9.2 преобразователя ПДК-напряжение, и n Di-входов предустановки ДПКД поразрядно соединены с n выходами 12 преобразователя ПДК в код Грея, n входов которого поразрядно соединены с n выходами буферного 11 регистра и с n входами Аi-группы входов 13 схемы вычитания, у которой m выходов кода разности Ai минус Bi поразрядно подключены к m входам Aj-группы входов m-разрядного 7 сумматора ПДК, и n входов Bi-группы входов схемы вычитания поразрядно подключены к соответствующим выходам n-разрядной 14 шины обратного ПДК граничной fмин частоты колебаний, а C0-вход переноса схемы вычитания подключен к шине логической единицы, и выходы n-разрядной 10 шины управляющего ПДК поразрядно подключены к соответствующим n входам буферного регистра, у которого выход первого разряда ПДК, подключенный к входу первого разряда преобразователя ПДК в код Грея, дополнительно подключен к D0-входу предустановки ДПКД, и C-вход синхронизации буферного регистра подключен к выходу детектора 16 фронта запускающего импульса, вход которого подключен к шине 15 "Запуск", выход детектора фронта запускающего импульса также соединен со входом первого 17 элемента задержки, выход которого соединен с PE-входом записиДПКД и со входом второго 18 элемента задержки, выход которого соединен с R-входом сброса 19 делителя с фиксированным коэффициентом деления (ДФКД) и с входом третьего 22 элемента задержки, выход которого соединен с  входом установки первого 23 RS-триггера, с

входом установки первого 23 RS-триггера, с  входом установки второго 24 RS-триггера и с первым входом 26 элемента 2ИЛИ-НЕ инверсной логики, выход которого соединен с C-входом синхронизации m-разрядного регистра ПДК, а второй вход соединен с выходом четвертого 25 элемента задержки, вход которого подключен к

входом установки второго 24 RS-триггера и с первым входом 26 элемента 2ИЛИ-НЕ инверсной логики, выход которого соединен с C-входом синхронизации m-разрядного регистра ПДК, а второй вход соединен с выходом четвертого 25 элемента задержки, вход которого подключен к  входу сброса ДФКД и к

входу сброса ДФКД и к  выходу сброса первого 23 RS-триггера, и C-вход синхронизации ДФКД подключен к выходу инвертора 20, вход которого подключен к сигнальной шине 21 импульсов f0 эталонной частоты, при этом, согласно изобретению, ДФКД (фиг. 2) выполнен в виде r-разрядного синхронного счетчика импульсов в коде Грея, у которого JK-вход разрешения счета ДФКД подключен к J- и K-входам нулевого 2.3.0 JK-триггера, прямой выход которого подключен ко второму входу первого 2.5.1 элемента 2И-НЕ инверсной логики межразрядной связи, первый вход которого соединен с

выходу сброса первого 23 RS-триггера, и C-вход синхронизации ДФКД подключен к выходу инвертора 20, вход которого подключен к сигнальной шине 21 импульсов f0 эталонной частоты, при этом, согласно изобретению, ДФКД (фиг. 2) выполнен в виде r-разрядного синхронного счетчика импульсов в коде Грея, у которого JK-вход разрешения счета ДФКД подключен к J- и K-входам нулевого 2.3.0 JK-триггера, прямой выход которого подключен ко второму входу первого 2.5.1 элемента 2И-НЕ инверсной логики межразрядной связи, первый вход которого соединен с  входом управления счетом ДФКД, а выход соединен с J- и K-входами первого 2.3.1 JK-триггера, прямой выход которого соединен с j- и k-входами второго 2.3.2 JK-триггера и с первыми входами второго 2.5.2 элемента 2И-НЕ инверсной логики межразрядной связи и первого 2.4.1 элемента 2И-НЕ инверсной логики сквозного переноса, второй вход которого соединен с прямым выходом второго 2.3.2 JK-триггера, а выход - с первым входом третьего 2.5.3 элемента 2И межразрядной связи, выход которого соединен с J- и K-входами четвертого 2.3.4 JK-триггера, а второй вход - с прямым выходом третьего 2.3.3 JK-триггера, J- и K-входы которого соединены с выходом второго 2.5.2 элемента 2И-НЕ инверсной логики межразрядной связи, второй вход которого подключен к инверсному выходу второго 2.3.2 JK-триггера, и прямой выход четвертого 2.3.4 JK-триггера подключен к J- и K-входам пятого 2.3.5 JK-триггера, а инверсный выход соединен с первыми входами второго 2.4.2 элемента 2И сквозного переноса и четвертого 2.5.4 элемента 2И межразрядной связи, выход которого соединен с J- и K-входами шестого 2.3.6 JK-триггера, а второй вход соединен с прямым выходом пятого 2.3.5 JK-триггера, инверсный выход которого подключен к второму входу второго 2.4.2 элемента 2И сквозного переноса, выход которого соединен с первыми входами пятого 2.5.5 элемента 2И межразрядной связи и третьего 2.4.3 элемента 2И сквозного переноса, выход которого соединен с первыми входами шестого элемента 2И межразрядной связи и четвертого элемента 2И сквозного переноса,..., и выход (r-5)-го 2.4. r-5 элемента 2И сквозного переноса соединен с первым входом (r-2)-го 2.5.r-2 элемента 2И межразрядной связи, второй вход которого соединен с прямым выходом (r-1)-го 2.3.r-1 JK-триггера, а выход соединен с J- и K-входами r-го 2.3.r JK-триггера, C-входы синхронизации нулевого 2.3.0 JK-триггера и первого 2.3.1 JK-триггера соединены с выходом логического 2.1 инвертора, вход которого соединен C-входом синхронизации ДФКД, с первым входом первого 2.2.1 элемента 2И-НЕ инверсной логики и с первым входом второго 2.2.2 элемента 2И-НЕ инверсной логики, выход которого соединен с C-входами синхронизации r-4 JK-триггеров с пятого 2.3.5 JK-триггера по r-й JK-триггер, а второй вход соединен с выходом 2.6 элемента 4И-НЕ, первый вход которого подключен к прямому выходу нулевого 2.3.0 JK-триггера, а второй, третий и четвертый входы соответственно подключены к инверсным выходам первого 2.3.1, второго 2.3.2 и третьего 2.3.3 JK-триггеров, второй вход первого элемента 2И-НЕ инверсной логики соединен с инверсным логики соединен с инверсным выходом нулевого 2.2.0 JK-триггера, а выход - с C-входами синхронизации второго 2.3.2, третьего 2.3.3 и четвертого 2.3.4 JK-триггеров, и выход (r-1)-входового 2.7 дешифратора соединен с первым входом 2.9 элемента 2И-НЕ и с первым входом первой группы входов 2И 2.10 элемента 2х2И-ИЛИ-НЕ, второй вход которой и второй вход элемента 2И-НЕ, в зависимости от числового эквивалента Kдj коэффициента деления, подключены к прямому выходу i-го JK-триггера при значениях Kдj= 2i-1•(1+4j), где j=1,2,..., или - к инверсному выходу i-го JK-триггера при значениях Kдj=2i-1•(3+4j), где j=0,1,2,..., а входы (r-1)-входового дешифратора подключены к прямым или инверсным выходам остальных r-1 JK-триггеров в соответствии с поразрядно записанным кодом Грея, числовой эквивалент которого равен целочисленному эквиваленту Kдj коэффициента деления, и первый вход второй группы входов 2И элемента 2х2И-ИЛИ-НЕ подключен к R-входу сброса ДФКД, а выход элемента 2х2И-ИЛИ-НЕ соединен с

входом управления счетом ДФКД, а выход соединен с J- и K-входами первого 2.3.1 JK-триггера, прямой выход которого соединен с j- и k-входами второго 2.3.2 JK-триггера и с первыми входами второго 2.5.2 элемента 2И-НЕ инверсной логики межразрядной связи и первого 2.4.1 элемента 2И-НЕ инверсной логики сквозного переноса, второй вход которого соединен с прямым выходом второго 2.3.2 JK-триггера, а выход - с первым входом третьего 2.5.3 элемента 2И межразрядной связи, выход которого соединен с J- и K-входами четвертого 2.3.4 JK-триггера, а второй вход - с прямым выходом третьего 2.3.3 JK-триггера, J- и K-входы которого соединены с выходом второго 2.5.2 элемента 2И-НЕ инверсной логики межразрядной связи, второй вход которого подключен к инверсному выходу второго 2.3.2 JK-триггера, и прямой выход четвертого 2.3.4 JK-триггера подключен к J- и K-входам пятого 2.3.5 JK-триггера, а инверсный выход соединен с первыми входами второго 2.4.2 элемента 2И сквозного переноса и четвертого 2.5.4 элемента 2И межразрядной связи, выход которого соединен с J- и K-входами шестого 2.3.6 JK-триггера, а второй вход соединен с прямым выходом пятого 2.3.5 JK-триггера, инверсный выход которого подключен к второму входу второго 2.4.2 элемента 2И сквозного переноса, выход которого соединен с первыми входами пятого 2.5.5 элемента 2И межразрядной связи и третьего 2.4.3 элемента 2И сквозного переноса, выход которого соединен с первыми входами шестого элемента 2И межразрядной связи и четвертого элемента 2И сквозного переноса,..., и выход (r-5)-го 2.4. r-5 элемента 2И сквозного переноса соединен с первым входом (r-2)-го 2.5.r-2 элемента 2И межразрядной связи, второй вход которого соединен с прямым выходом (r-1)-го 2.3.r-1 JK-триггера, а выход соединен с J- и K-входами r-го 2.3.r JK-триггера, C-входы синхронизации нулевого 2.3.0 JK-триггера и первого 2.3.1 JK-триггера соединены с выходом логического 2.1 инвертора, вход которого соединен C-входом синхронизации ДФКД, с первым входом первого 2.2.1 элемента 2И-НЕ инверсной логики и с первым входом второго 2.2.2 элемента 2И-НЕ инверсной логики, выход которого соединен с C-входами синхронизации r-4 JK-триггеров с пятого 2.3.5 JK-триггера по r-й JK-триггер, а второй вход соединен с выходом 2.6 элемента 4И-НЕ, первый вход которого подключен к прямому выходу нулевого 2.3.0 JK-триггера, а второй, третий и четвертый входы соответственно подключены к инверсным выходам первого 2.3.1, второго 2.3.2 и третьего 2.3.3 JK-триггеров, второй вход первого элемента 2И-НЕ инверсной логики соединен с инверсным логики соединен с инверсным выходом нулевого 2.2.0 JK-триггера, а выход - с C-входами синхронизации второго 2.3.2, третьего 2.3.3 и четвертого 2.3.4 JK-триггеров, и выход (r-1)-входового 2.7 дешифратора соединен с первым входом 2.9 элемента 2И-НЕ и с первым входом первой группы входов 2И 2.10 элемента 2х2И-ИЛИ-НЕ, второй вход которой и второй вход элемента 2И-НЕ, в зависимости от числового эквивалента Kдj коэффициента деления, подключены к прямому выходу i-го JK-триггера при значениях Kдj= 2i-1•(1+4j), где j=1,2,..., или - к инверсному выходу i-го JK-триггера при значениях Kдj=2i-1•(3+4j), где j=0,1,2,..., а входы (r-1)-входового дешифратора подключены к прямым или инверсным выходам остальных r-1 JK-триггеров в соответствии с поразрядно записанным кодом Грея, числовой эквивалент которого равен целочисленному эквиваленту Kдj коэффициента деления, и первый вход второй группы входов 2И элемента 2х2И-ИЛИ-НЕ подключен к R-входу сброса ДФКД, а выход элемента 2х2И-ИЛИ-НЕ соединен с  входами сброса r+1 JK-триггеров с нулевого 2.3.0 JK-триггера по r-й 2.3.r JK-триггер, и выход 2.9 элемента 2И-НЕ подключен к

входами сброса r+1 JK-триггеров с нулевого 2.3.0 JK-триггера по r-й 2.3.r JK-триггер, и выход 2.9 элемента 2И-НЕ подключен к  выходу сброса ДФКД, у которого JK-вход разрешения счета ДФКД соединен с JK-входом разрешения счета ДПКД (фиг. 3) и подключен к прямому выходу первого 23 RS-триггера, инверсный выход которого соединен с

выходу сброса ДФКД, у которого JK-вход разрешения счета ДФКД соединен с JK-входом разрешения счета ДПКД (фиг. 3) и подключен к прямому выходу первого 23 RS-триггера, инверсный выход которого соединен с  входом управления счетом ДФКД и с

входом управления счетом ДФКД и с  входом управления счетом ДПКД, который выполнен в виде n-разрядного синхронного счетчика импульсов в коде Грея, у которого JK-вход разрешения счета ДПКД подключен к J- и K-входам нулевого 3.3.0 JK-триггера, прямой выход которого подключен к второму входу первого 3.5.1 элемента 2И-НЕ инверсной логики межразрядной связи, первый вход которого подключен к

входом управления счетом ДПКД, который выполнен в виде n-разрядного синхронного счетчика импульсов в коде Грея, у которого JK-вход разрешения счета ДПКД подключен к J- и K-входам нулевого 3.3.0 JK-триггера, прямой выход которого подключен к второму входу первого 3.5.1 элемента 2И-НЕ инверсной логики межразрядной связи, первый вход которого подключен к  входу управления счетом ДПКД, а выход соединен с J- и K-входами первого 3.3.1 JK-триггера, прямой выход которого подключен к J- и K-входам второго 3.3.2 JK-триггера, к первым входам второго 3.5.2 элемента 2И-НЕ инверсной логики межразрядной связи и первого 3.4.1 элемента 2И-НЕ инверсной логики сквозного переноса, второй вход которого соединен с прямым выходом второго 3.3.2 JK-триггера, а выход - с первым входом третьего 3.5.3 элемента 2И межразрядной связи, выход которого соединен с J- и K-входами четвертого 3.3.4 JK-триггера, а второй вход - с прямым выходом третьего 3.3.3 JK-триггера, J- и K-входы которого соединены с выходом второго 3.5.2 элемента 2И-НЕ инверсной логики межразрядной связи, второй вход которого подключен к инверсному выходу второго 3.3.2 JK-триггера, и прямой выход четвертого JK-триггера подключен к J- и K-входам пятого 3.3.5 JK-триггера, а инверсный выход соединен с первыми входами второго 3.4.2 элемента 2И сквозного переноса и четвертого 3.5.4 элемента 2И межразрядной связи, выход которого соединен с J- и K-входами шестого 3.3.6 JK-триггера, а второй вход соединен с прямым выходом пятого 3.3.5 JK-триггера, инверсный выход которого подключен к второму входу второго 3.4.2 элемента 2И сквозного переноса, выход которого соединен с первыми входами пятого 3.5.5 элемента 2И межразрядной связи и третьего 3.4.3 элемента 2И сквозного переноса, выход которого соединен с первыми входами шестого элемента 2И межразрядной связи и четвертого элемента 2И сквозного переноса,. . ., а выход (n-5)-го 3.4.n-5 элемента 2И сквозного переноса соединен с первым входом (n-2)-го 3.5.n-2 элемента 2И межразрядной связи, второй вход которого соединен с прямым выходом (n-1)-го 3.3.n-1 JK-триггера, а выход соединен с J- и K-входами n-го 3.3.n JK-триггера, C-входы синхронизации нулевого 3.3.0 JK-триггера и первого 2.3.1 JK-триггера соединены с выходом логического 3.1 инвертора, вход которого соединен с C-входом синхронизации ДПКД, с первым входом первого 3.2.1 элемента 2И-НЕ инверсной логики и с первым входом второго 3.2.2 элемента 2И-НЕ инверсной логики, выход которого соединен с C-входами синхронизации n-4 JK-триггеров с пятого 3.3.5 JK-триггера по n-й 3.3. n JK-триггер, а второй вход соединен с выходом второго 3.6.2 элемента 4И-НЕ, первый вход которого подключен к прямому выходу нулевого 3.3.0 JK-триггера, второй вход соединен с инверсным выходом первого 3.3.1 JK-триггера, третий вход подключен к инверсному выходу второго 3.3.2 JK-триггера, четвертый вход соединен с инверсным выходом третьего 3.3.3 JK-триггера и с третьим входом первого 3.6.1 элемента 4И-НЕ, выход которого подключен к

входу управления счетом ДПКД, а выход соединен с J- и K-входами первого 3.3.1 JK-триггера, прямой выход которого подключен к J- и K-входам второго 3.3.2 JK-триггера, к первым входам второго 3.5.2 элемента 2И-НЕ инверсной логики межразрядной связи и первого 3.4.1 элемента 2И-НЕ инверсной логики сквозного переноса, второй вход которого соединен с прямым выходом второго 3.3.2 JK-триггера, а выход - с первым входом третьего 3.5.3 элемента 2И межразрядной связи, выход которого соединен с J- и K-входами четвертого 3.3.4 JK-триггера, а второй вход - с прямым выходом третьего 3.3.3 JK-триггера, J- и K-входы которого соединены с выходом второго 3.5.2 элемента 2И-НЕ инверсной логики межразрядной связи, второй вход которого подключен к инверсному выходу второго 3.3.2 JK-триггера, и прямой выход четвертого JK-триггера подключен к J- и K-входам пятого 3.3.5 JK-триггера, а инверсный выход соединен с первыми входами второго 3.4.2 элемента 2И сквозного переноса и четвертого 3.5.4 элемента 2И межразрядной связи, выход которого соединен с J- и K-входами шестого 3.3.6 JK-триггера, а второй вход соединен с прямым выходом пятого 3.3.5 JK-триггера, инверсный выход которого подключен к второму входу второго 3.4.2 элемента 2И сквозного переноса, выход которого соединен с первыми входами пятого 3.5.5 элемента 2И межразрядной связи и третьего 3.4.3 элемента 2И сквозного переноса, выход которого соединен с первыми входами шестого элемента 2И межразрядной связи и четвертого элемента 2И сквозного переноса,. . ., а выход (n-5)-го 3.4.n-5 элемента 2И сквозного переноса соединен с первым входом (n-2)-го 3.5.n-2 элемента 2И межразрядной связи, второй вход которого соединен с прямым выходом (n-1)-го 3.3.n-1 JK-триггера, а выход соединен с J- и K-входами n-го 3.3.n JK-триггера, C-входы синхронизации нулевого 3.3.0 JK-триггера и первого 2.3.1 JK-триггера соединены с выходом логического 3.1 инвертора, вход которого соединен с C-входом синхронизации ДПКД, с первым входом первого 3.2.1 элемента 2И-НЕ инверсной логики и с первым входом второго 3.2.2 элемента 2И-НЕ инверсной логики, выход которого соединен с C-входами синхронизации n-4 JK-триггеров с пятого 3.3.5 JK-триггера по n-й 3.3. n JK-триггер, а второй вход соединен с выходом второго 3.6.2 элемента 4И-НЕ, первый вход которого подключен к прямому выходу нулевого 3.3.0 JK-триггера, второй вход соединен с инверсным выходом первого 3.3.1 JK-триггера, третий вход подключен к инверсному выходу второго 3.3.2 JK-триггера, четвертый вход соединен с инверсным выходом третьего 3.3.3 JK-триггера и с третьим входом первого 3.6.1 элемента 4И-НЕ, выход которого подключен к  выходу переключения счета ДПКД, а первый вход соединен с вторым входом второго элемента 2И-НЕ инверсной логики и с инверсным выходом нулевого 3.3.0 JK-триггера, второй вход первого элемента 4И-НЕ подключен к выходу первого 3.4.1 элемента 2И-НЕ инверсной логики сквозного переноса, а четвертый выход соединен с выходом третьего 3.2.3 элемента 2И-НЕ инверсной логики, первый вход которого соединен с выходом третьего 3.8 элемента 4И-НЕ, второй вход - с выходом (n-7)-входового 3.9 элемента И-НЕ, у которых n-3 входов поразрядно подключены к инверсным выходам n-4 JK-триггеров с четвертого 3.3.4 JK-триггера по (n-1)-й 3.3n-1 JK-триггер и к прямому выходу n-го 3.3.n JK-триггера ДПКД, и PE-вход записи ДПКД подключен к первым входам элементов 2И-НЕ n+1 3.7.0,...,3.7.n логических пар элементов 2И-НЕ, у которых n прямых сигнальных выходов поразрядно подключены к

выходу переключения счета ДПКД, а первый вход соединен с вторым входом второго элемента 2И-НЕ инверсной логики и с инверсным выходом нулевого 3.3.0 JK-триггера, второй вход первого элемента 4И-НЕ подключен к выходу первого 3.4.1 элемента 2И-НЕ инверсной логики сквозного переноса, а четвертый выход соединен с выходом третьего 3.2.3 элемента 2И-НЕ инверсной логики, первый вход которого соединен с выходом третьего 3.8 элемента 4И-НЕ, второй вход - с выходом (n-7)-входового 3.9 элемента И-НЕ, у которых n-3 входов поразрядно подключены к инверсным выходам n-4 JK-триггеров с четвертого 3.3.4 JK-триггера по (n-1)-й 3.3n-1 JK-триггер и к прямому выходу n-го 3.3.n JK-триггера ДПКД, и PE-вход записи ДПКД подключен к первым входам элементов 2И-НЕ n+1 3.7.0,...,3.7.n логических пар элементов 2И-НЕ, у которых n прямых сигнальных выходов поразрядно подключены к  входам установкам n JK-триггеров с нулевого 3.3.0 JK-триггера по (n-1)-й 3.3.n-1 JK-триггер, а n инверсных сигнальных выходов поразрядно соединены с их

входам установкам n JK-триггеров с нулевого 3.3.0 JK-триггера по (n-1)-й 3.3.n-1 JK-триггер, а n инверсных сигнальных выходов поразрядно соединены с их  входами сброса в названной последовательности, и прямой сигнальный выход n-ой 3.7.n логической пары элементов 2И-НЕ подключен к

входами сброса в названной последовательности, и прямой сигнальный выход n-ой 3.7.n логической пары элементов 2И-НЕ подключен к  входу сброса n-го 3.3.n JK-триггера, а инверсный сигнальный выход соединен с его

входу сброса n-го 3.3.n JK-триггера, а инверсный сигнальный выход соединен с его  -входом установки, и сигнальный вход первого элемента 2И-НЕ нулевой 3.7.0 логической пары элементов 2И-НЕ соединен с D0-входом предустановки ДПКД, а сигнальные входы первых элементов 2И-НЕ n 3.7.1,...,3.7.n логических пар элементов 2И-НЕ поразрядно соединены с соответствующими Di-входами предустановки ДПКД с первого по n-й, и выход первого элемента 2И-НЕ инверсной логики соединен с C-выходами синхронизации второго 3.3.2, третьего 3.3.3 и четвертого 3.3.4 JK-триггеров,

-входом установки, и сигнальный вход первого элемента 2И-НЕ нулевой 3.7.0 логической пары элементов 2И-НЕ соединен с D0-входом предустановки ДПКД, а сигнальные входы первых элементов 2И-НЕ n 3.7.1,...,3.7.n логических пар элементов 2И-НЕ поразрядно соединены с соответствующими Di-входами предустановки ДПКД с первого по n-й, и выход первого элемента 2И-НЕ инверсной логики соединен с C-выходами синхронизации второго 3.3.2, третьего 3.3.3 и четвертого 3.3.4 JK-триггеров,  выход переключения счета ДПКД соединен с

выход переключения счета ДПКД соединен с  входом сброса второго 24 RS-триггера, инверсный выход которого соединен с C0-входом переноса m-разрядного 7 сумматора ПДК и с первым входом первой 2И группы входов 6 элемента 2х2И-ИЛИ-НЕ, второй вход которой соединен с прямым выходом m-го JK-триггера ДПКД, а первый вход второй 2И группы входов элемента 2х2И-ИЛИ-НЕ соединен с прямым выходом второго 24 RS-триггера, второй вход которой соединен с инверсным выходом m-го JK-триггера ДПКД, и выход элемента 2х2И-ИЛИ-НЕ соединен с входом старшего m-го разряда 5 преобразователя кода Грея в ПДК, m-1 входов которого поразрядно подключены к соответствующим входам выходной сигнальной 3.10 шины ДПКД (фиг. 3), Q1-выход которой подключен к прямому выходу первого 3.3.1 JK-триггера, Q2-выход - к прямому выходу второго 3.3.2 JK-триггера,..., Qi-выход - к прямому выходу i-го JK-триггера,..., Qm-1-выход - к прямому выходу (m-1)-го JK-триггера, и Qm-выход - к прямому выходу m-го JK-триггера, а

входом сброса второго 24 RS-триггера, инверсный выход которого соединен с C0-входом переноса m-разрядного 7 сумматора ПДК и с первым входом первой 2И группы входов 6 элемента 2х2И-ИЛИ-НЕ, второй вход которой соединен с прямым выходом m-го JK-триггера ДПКД, а первый вход второй 2И группы входов элемента 2х2И-ИЛИ-НЕ соединен с прямым выходом второго 24 RS-триггера, второй вход которой соединен с инверсным выходом m-го JK-триггера ДПКД, и выход элемента 2х2И-ИЛИ-НЕ соединен с входом старшего m-го разряда 5 преобразователя кода Грея в ПДК, m-1 входов которого поразрядно подключены к соответствующим входам выходной сигнальной 3.10 шины ДПКД (фиг. 3), Q1-выход которой подключен к прямому выходу первого 3.3.1 JK-триггера, Q2-выход - к прямому выходу второго 3.3.2 JK-триггера,..., Qi-выход - к прямому выходу i-го JK-триггера,..., Qm-1-выход - к прямому выходу (m-1)-го JK-триггера, и Qm-выход - к прямому выходу m-го JK-триггера, а  выход к его инверсному выходу. Элементы 1, 3, 4, 5, 6, 7, 8 и 9, соединенные в кольцо, обеспечивают автоподстройку до номинального значения частоты колебаний из диапазона перестройки в соответствии с числовым эквивалентом управляющего ПДК на сигнальной 10 шине управления.

выход к его инверсному выходу. Элементы 1, 3, 4, 5, 6, 7, 8 и 9, соединенные в кольцо, обеспечивают автоподстройку до номинального значения частоты колебаний из диапазона перестройки в соответствии с числовым эквивалентом управляющего ПДК на сигнальной 10 шине управления.

Работа кольца автоподстройки обеспечивается с помощью вспомогательных 11, 12, 13, 16, 17, 18, 19, 22, 23, 24, 25 и 26 элементов, а 2, 10, 14, 15, 20 и 21 элементы необходимы для связей устройства с потребителем и с внешними устройствами синхронизации и управления.

Функции временного дискриминатора выполняет n-разрядный ДПКД, подсчитывающий за время T0 число ΔNx= To•(fн-fx) периодов 1/fx колебаний, отличных от номинала Nн= T0•fн, и определяющий в соединении с элементами 24, 6 и 5 знак ошибки.

При описании работы УСТРОЙСТВА (фиг. 1, 1a и 4) рассматриваются оба случая компенсации расстройки:

fxi<fxн, когда к исходному числовому эквиваленту Nн прибавляется поправка ΔNx, и fxi>fxн, когда она из него вычитается.

Работа устройства (фиг. 1, 1a, 2, 3 и 4) описывается на примере функциональной схемы (фиг. 1) с 15-разрядным r=15 ДФКД 19 и с 15 разрядным n=15 ДПКД 4, в m-1, при m=13, элементах которого после окончания текущего цикла счета и до начала следующего сохраняется остаточный код числа колебаний отличного от номинального значения, числовой эквивалент которого не превышает 2m-l-1 единиц счета.

Для этого на шину 21 непрерывно поступают импульсы эталонной частоты с периодом 1/f0, на шину 10 перед каждым запуском поступает n-разрядный ПДК номинального fxн значения частоты колебаний из диапазона fxмакс-fxмин перестройки, а на шину 14 постоянно подан n-разрядный обратный ПДК минимальной частоты  колебаний fмин, числовое значение которого Nмин меньше Nxмин на 2m-l-1 единиц счета.

колебаний fмин, числовое значение которого Nмин меньше Nxмин на 2m-l-1 единиц счета.

До поступления первого импульса запуска Вх.16 (фиг. 4.1) на шине выхода 2 присутствуют непрерывные периодические колебания с частотой fxi, естественная нестабильность которой соответствует числовому значению остаточного кода в m-l младших разрядах m-разрядного регистра 8 (фиг. 1), из которых число l старших разрядов, в зависимости от информационной емкости 2n-1 ДПКД и дискрета перестройки Δf, составляет от 2 до 8 единиц.

При этом n выходов элементов 11 и 12, m выходов элементов 13 и 7, m выходов элементов 4, 5, 7 и 8, выходы элементов 9.1, 23 и 24, r счетных элементов ДФКД 19 находятся в неопределенных состояниях (логический нуль или единица), C-входы синхронизации элементов 4 и 19, выходы элементов 22 и 25 находятся в состоянии логической единицы, а выход элемента 26 в состоянии логического нуля.

Положительный импульс Вых.16 (фиг. 4.2), соответствующий фронту первого и далее последующих импульсов запуска Вх.16 (фиг. 4.1), поступая на C-вход синхронизации буферного регистра 11, производит поразрядную запись n-разрядного кода частоты колебаний fxн, который с его n Qi-выходов поразрядно поступает на n входов Ai-группы входов схемы вычитания 13, на D0-вход предустановки ДПКД по цепи 1рВК и на n греевских Di-входов предустановки ПДКД с выходов n-разрядного преобразователя 12 ПДК в код Грея B/G. Положительный импульс Вых.16, задержанный на время t1 (Вых. 17, фиг. 4.4), с выхода элемента 17, поступая на PE-вход записи ДПКД, производит параллельную запись исходных данных в n+1 элементов счета ДПКД, а задержанный на время t2 (Вых. 18, фиг. 4.6) элементом 18, производит первоначальное обнуление счетчика импульсов в составе ДФКД 19, подготавливая его к точному подсчету длительности T0 мерного интервала с нуля отсчета. Положительный импульс с выхода элемента 18 (Вых. 22, фиг. 4.8), задержанный на время t3, поступая с выхода элемента 22 на  вход установки первого 23 RS-триггера, устанавливает его в состояние "единица", разрешая подсчет импульсов с периодом 1/f0 элементами ДФКД и с периодом 1/fx элементами ДПКД, когда на их JK-входы с прямого выхода первого RS-триггера 23 поступил положительный импульс T0 мерного интервала, а на

вход установки первого 23 RS-триггера, устанавливает его в состояние "единица", разрешая подсчет импульсов с периодом 1/f0 элементами ДФКД и с периодом 1/fx элементами ДПКД, когда на их JK-входы с прямого выхода первого RS-триггера 23 поступил положительный импульс T0 мерного интервала, а на  входы управления счетом отрицательная фаза T0 с его инверсного выхода, длительность которых ограничивается фронтом отрицательного импульса

входы управления счетом отрицательная фаза T0 с его инверсного выхода, длительность которых ограничивается фронтом отрицательного импульса  вых. 19 фиг. 4.12, поступившим на

вых. 19 фиг. 4.12, поступившим на  вход сброса RS-триггера 23 с

вход сброса RS-триггера 23 с  выхода сброса ДФКД 19 в момент окончания подсчета импульсов эталонной частоты (фиг. 4.9-4.12).

выхода сброса ДФКД 19 в момент окончания подсчета импульсов эталонной частоты (фиг. 4.9-4.12).

Импульс Вых. 22, поступивший также на  вход установки RS-триггера 24, первоначально устанавливает его в состояние "единица" в предположении, что текущее число импульсов с периодом 1/fxi за время измерения fxi будет меньше номинального с периодом 1/fxн при fxi<fxн. При этом положительный перепад L/H с прямого выхода второго RS-триггера, 24, поступивший на первый вход элемента 6, а отрицательный H/L с инверсного выхода, поступивший на C0-вход переноса элемента 7 и на третий вход элемента 6, после прекращения счета импульсом

вход установки RS-триггера 24, первоначально устанавливает его в состояние "единица" в предположении, что текущее число импульсов с периодом 1/fxi за время измерения fxi будет меньше номинального с периодом 1/fxн при fxi<fxн. При этом положительный перепад L/H с прямого выхода второго RS-триггера, 24, поступивший на первый вход элемента 6, а отрицательный H/L с инверсного выхода, поступивший на C0-вход переноса элемента 7 и на третий вход элемента 6, после прекращения счета импульсом  вых.19 фиг. 4.12, обеспечивают суммирование m-разрядного ПДК на входах Aj-группы входов элемента 7 с прямым ПДК на входах Bj-группы входов, полученным в результате подразрядного преобразования остаточного кода Грея в позиционный код, при подключении высокого уровня с

вых.19 фиг. 4.12, обеспечивают суммирование m-разрядного ПДК на входах Aj-группы входов элемента 7 с прямым ПДК на входах Bj-группы входов, полученным в результате подразрядного преобразования остаточного кода Грея в позиционный код, при подключении высокого уровня с  выхода ДПКД 4 к входу старшего разряда элемента 5 через второй вход группы 2И элемента 6 с инверсией на выходе.

выхода ДПКД 4 к входу старшего разряда элемента 5 через второй вход группы 2И элемента 6 с инверсией на выходе.

Если текущее число импульсов с периодом 1/fxi окажется больше номинального, соответствующего полному заполнению счетных ячеек ДПКД, то в момент перехода от прямого счета к отраженному (фиг. 4.13, 4.14) на его  выходе переключения счета формируется отрицательный импульс (фиг. 4.15) с длительностью 1/fxi, фронт которого переключает второй 24 RS-триггер в инверсное ("нулевое") состояние по

выходе переключения счета формируется отрицательный импульс (фиг. 4.15) с длительностью 1/fxi, фронт которого переключает второй 24 RS-триггер в инверсное ("нулевое") состояние по  входу сброса, перестраивая сумматор кодов 7 на вычитание из m-разрядного ПДК на входах Aj-группы входов m-разрядного обратного ПДК на m входах Bj-группы входов, полученного после поразрядного преобразования остаточного кода Грея в позиционный код с подключениями высокого уровня с инверсного выхода RS-триггера 24 к C0-входу сумматора кодов и к третьему входу элемента 6, а также низкого уровня с Qm-выхода ДПКД через четвертый вход элемента 6, с последующей инверсией, ко входу старшего разряда элемента 5.

входу сброса, перестраивая сумматор кодов 7 на вычитание из m-разрядного ПДК на входах Aj-группы входов m-разрядного обратного ПДК на m входах Bj-группы входов, полученного после поразрядного преобразования остаточного кода Грея в позиционный код с подключениями высокого уровня с инверсного выхода RS-триггера 24 к C0-входу сумматора кодов и к третьему входу элемента 6, а также низкого уровня с Qm-выхода ДПКД через четвертый вход элемента 6, с последующей инверсией, ко входу старшего разряда элемента 5.

Параметрическое управление частотой автогенератора G1 происходит вследствие изменения величины эквивалентной емкости его резонатора.

Значению fмин соответствуют Cэкв.макс при практически неизменных значениях Lэкв. и Rэкв. в диапазоне перестройки.

Каждому номиналу частоты fxi генерации соответствует эквивалентная емкость резонатора Cэкв.i=Cм+Cнi+Cдi, состоящая из: Cм - распределенной емкости монтажа, Cнi - сосредоточенной емкости переключаемых элементов, Cдi - параметрической емкости управляемого элемента.

Для получения необходимого значения Cэкв.i кодовая комбинация старших разрядов регистра ПДК 8, поступая на l входов потенциального дешифратора 9.1, выбирает соответствующую команду из p набора на его выходе, которая включает в резонаторе необходимый номинал сосредоточенной емкости Cнi, величина которой обеспечивает начальную отстройку частоты fxi от fмин. Окончательно расстройка δfxi, вызванная естественной нестабильностью элементов автогенератора G1, числовой эквивалент которой не превышает емкости m-l младших разрядов регистра ПДК, поразрядно соединенных с входами функционального преобразователя B/U 9.2, компенсируется при автоподстройке, в результате чего напряжение смещения с выхода элемента 9.2 подстраивает емкость перехода до необходимого значения Cдi.

При известных дискрете перестройки Δfx и граничных частотах диапазона, легко получить простые расчетные соотношения величин Cэкв.i для каждого из номиналов fxi частоты генерации:

Nxi=fxi•T0;

n≥log2•Nмакс;

2n-1<Nмакс<2n-1;

Nмин=Nмакс-(2m-1);

m≥log2(Nмакс-Nмин+1);

fxi= fмин+Δfi;

Собственно числовое значение сигнала ошибки, соответствующее m-разрядному коду Грея на Q1,...,Qm-1,  и Qm-выходах ячеек счетчика импульсов ДПКД 4 фиг. 1, вычисляется после записи исходных данных, поступивших на его Di-входы, и подсчета реального количества периодов колебаний автогенератора G1 фиг. 1 до появления фронта импульса

и Qm-выходах ячеек счетчика импульсов ДПКД 4 фиг. 1, вычисляется после записи исходных данных, поступивших на его Di-входы, и подсчета реального количества периодов колебаний автогенератора G1 фиг. 1 до появления фронта импульса  вых.19 фиг. 4.12, останавливающего счет в рассматриваемом цикле при переключении RS-триггера 23 в нулевое состояние. С приходом импульса Вых.17 фиг. 4.4 на PE-вход ДПКД 4 фиг. 1, в нулевой 3.3.0 JK-триггер счетчика импульсов записывается состояние первого разряда ПДК fxi с 1pBK-выхода буферного регистра 11, а в n 3.3.1...3.3.n JK-триггеров, начиная с первого 3.3.1, по Di-входам поразрядно записывается дополнение до (2n-1) числового значения n-разрядного кода Грея текущего значения частоты fxi, которое отличается от исходного значения, поступающего с n выходов преобразователя B/G 12 только инверсным состоянием старшего n-го разряда кода.

вых.19 фиг. 4.12, останавливающего счет в рассматриваемом цикле при переключении RS-триггера 23 в нулевое состояние. С приходом импульса Вых.17 фиг. 4.4 на PE-вход ДПКД 4 фиг. 1, в нулевой 3.3.0 JK-триггер счетчика импульсов записывается состояние первого разряда ПДК fxi с 1pBK-выхода буферного регистра 11, а в n 3.3.1...3.3.n JK-триггеров, начиная с первого 3.3.1, по Di-входам поразрядно записывается дополнение до (2n-1) числового значения n-разрядного кода Грея текущего значения частоты fxi, которое отличается от исходного значения, поступающего с n выходов преобразователя B/G 12 только инверсным состоянием старшего n-го разряда кода.

Упрощение записи достигается перекрестным вводом логических "нуля" или "единицы" по  или

или  входам n-го 3.3.n JK-триггера счетчика импульсов ДПКД фиг. 3.

входам n-го 3.3.n JK-триггера счетчика импульсов ДПКД фиг. 3.

При досчитыании до (2n-1) необходимого числа периодов колебаний 1/fxi происходит частичное, при fxi<fxн заполнение ячеек счетчика импульсов ДПКД 4 или избыточное, при fxi>fxн (см. таблица).

Числовое значение (m-l) младших разрядов XXX...X остаточного кода Грея соответствует абсолютной величине сигнала ошибки, преобразуемой в управляющее воздействие на параметры резонатора автогенератора.

В описанном генераторе (фиг. 1) за счет предложенного построения ДПКД 4 в соединении с ДФКД 19 и элементами 23, 24, 6, 5 обеспечено совмещение измерения текущего значения частоты fxi автогенератора G1, с одновременным вычислением абсолютной величины сигнала ошибки, и определение знака расстройки, что при ограниченном мерном интервале T0 позволяет улучшить быстродействие устройства за счет исключения дополнительных вычислительных операций.

Список Литературы

1. Левин А.А. и др. Синтезаторы частот с системой ИФАП. - М.: Рис. 1989. с. 14, рис. 1.3, УДК 621.396.662.

2. BRD, Int. Cl2, H 03 B 3/04, (11) 2163971, (73) Siemens AG 1000 Berlin und 8000 Munchen, (54) Schaltung zur digitalen Frequenzeinstellung..., (72) Schlosser Karl, (Перевод. кассета ГКР 2/К 108).

| название | год | авторы | номер документа |

|---|---|---|---|

| МНОГОРАЗРЯДНЫЙ УПРАВЛЯЕМЫЙ ДЕЛИТЕЛЬ ЧАСТОТЫ | 1996 |

|

RU2119248C1 |

| ЖДУЩИЙ ФОРМИРОВАТЕЛЬ ИМПУЛЬСОВ | 1993 |

|

RU2047939C1 |

| СИНХРОННЫЙ ДЕЛИТЕЛЬ ЧАСТОТЫ | 1992 |

|

RU2037957C1 |

| Синтезатор частот | 1976 |

|

SU799101A1 |

| ДИСКРЕТНО-АНАЛОГОВЫЙ СИНУС-ГЕНЕРАТОР | 1995 |

|

RU2108657C1 |

| Делитель частоты с переменным коэффициентом деления | 1988 |

|

SU1653153A1 |

| Синтезатор частот | 1985 |

|

SU1363457A1 |

| Синтезатор частот | 1980 |

|

SU886254A2 |

| Цифровой синтезатор частот | 1990 |

|

SU1748251A1 |

| Цифровой синтезатор частоты | 1986 |

|

SU1356222A1 |

Изобретение относится к области радиоэлектроники и может использоваться в устройствах различного назначения, например, в качестве управляемых гетеродинов или датчиков дискретного множества частот. Задача, решаемая предлагаемым устройством, состоит в повышении его быстродействия за счет использования делителя с переменным коэффициентом деления (ДПКД), который вычисляет абсолютную величину расстройки относительно номинала и определяет ее знак. Управляемый генератор с предустановкой частоты содержит автогенератор G электрических колебании, формирователь импульсов, делитель частоты с переменным коэффициентом деления, m-входовый преобразователь кода Грея в позиционный двоичный код (ПДК), элемент 2х2И-ИЛИ-НЕ, сумматор ПДК, регистр ПДК, функциональный преобразователь, буферный регистр ПДК, преобразователь кодов ПДК в код Грея, схему вычитания, детектор фронта запускающего импульса, четыре элемента задержки делитель частоты с фиксированным коэффициентом деления, инвертор, первый RS-триггер, второй RS-триггер и элемент 2ИЛИ-НЕ инверсной логики. 4 ил., 1 табл.

Управляемый генератор с предустановкой частоты, содержащий соединенные в кольцо автогенератор G электрических колебаний с p-входовой шиной дискретных команд и с аналоговым входом, сигнальную шину выхода fx частоты колебаний, подключенную к входу формирователя импульсов с периодом 1/fx, выход которого соединен с C-входом синхронизации делителя частоты с переменным коэффициентом деления (ДПКД), элемент 2 х 2И-ИЛИ-НЕ с m-входовым преобразователем кода Грея в позиционный двоичный код (ПДК), у которого m выходов поразрядно подключены к m входам Bj группы входов m-разрядного сумматора ПДК, m выходов которого поразрядно подключены к входам m-разрядного регистра ПДК, у которого l выходов старших разрядов поразрядно подключены к l входам потенциального дешифратора, который является первым элементом функционального преобразователя, а m - l выходов младших разрядов m-разрядного регистра ПДК поразрядно подключены к m - l входам преобразователя ПДК - напряжение, который является вторым элементом функционального преобразователя, p выходов которого поэлементно подключены к входам p-входовой шины дискретных команд автогенератора G электрических колебаний, аналоговый вход которого соединен с выходом преобразователя ПДК - напряжение, и n Di-входов предустановки ДПКД поразрядно соединены с выходами преобразователя ПДК в код Грея, n входов которого поразрядно соединены с n выходами буферного регистра и с n входами Ai группы входов схемы вычитания, у которой m выходов кода разности Ai минус Bi поразрядно подключены к m входам Aj группы входов m-разрядного сумматора ПДК, и n входов Bi группы входов схемы вычитания поразрядно подключены к соответствующим выходам n-разрядной шины обратного ПДК граничной fмин частоты колебаний, а CO-вход переноса схемы вычитания подключен к шине логической единицы, и выходы n-разрядной шины управляющего ПДК разрядно подключены к соответствующим n входам буферного регистра, у которого выход первого младшего разряда ПДК, подключенный к входу первого разряда преобразователя ПДК в код Грея, дополнительно подключен к DO-входу предустановки ДПКД, и C-вход синхронизации буферного регистра подключен к выходу детектора фронта запускающего импульса, вход которого подключен к шине "Запуск", выход детектора фронта запускающего импульса также соединен с входом первого элемента задержки, выход которого соединен с PE-входом записи ДПКД и с входом второго элемента задержки, выход которого соединен с R-входом сброса делителя с фиксированным коэффициентом деления (ДФКД) и с входом третьего элемента задержки, выход которого соединен с  входом установки первого RS-триггера, с

входом установки первого RS-триггера, с  входом установки второго RS-триггера и с первым входом элемента 2ИЛИ-НЕ инверсной логики, выход которого соединен с C-входом синхронизации m-разрядного регистра ПДК, а второй вход соединен с выходом четвертого элемента задержки, вход которого подключен к

входом установки второго RS-триггера и с первым входом элемента 2ИЛИ-НЕ инверсной логики, выход которого соединен с C-входом синхронизации m-разрядного регистра ПДК, а второй вход соединен с выходом четвертого элемента задержки, вход которого подключен к  выходу сброса ДФКД и к

выходу сброса ДФКД и к  входу сброса первого RS-триггера, и C-вход синхронизации ДФКД подключен к выходу инвертора, вход которого подключен к сигнальной шине импульсов f0 эталонной частоты, отличающийся тем, что ДФКД выполнен в виде r-разрядного синхронного счетчика импульсов в коде Грея, у которого JR-вход разрешения счета ДФКД подключен к J- и K-входам нулевого JK-триггера, прямой выход которого подключен к второму входу первого элемента 2И-НЕ инверсной логики межразрядной связи, первый вход которого соединен с

входу сброса первого RS-триггера, и C-вход синхронизации ДФКД подключен к выходу инвертора, вход которого подключен к сигнальной шине импульсов f0 эталонной частоты, отличающийся тем, что ДФКД выполнен в виде r-разрядного синхронного счетчика импульсов в коде Грея, у которого JR-вход разрешения счета ДФКД подключен к J- и K-входам нулевого JK-триггера, прямой выход которого подключен к второму входу первого элемента 2И-НЕ инверсной логики межразрядной связи, первый вход которого соединен с  входом управления счетом ДФКД, а выход соединен с J- и K-входами первого JK-триггера, прямой выход которого соединен с J- и K-входами второго JK-триггера и с первыми входами второго элемента 2И-НЕ инверсной логики межразрядной связи и первого элемента 2И-НЕ инверсной логики сквозного переноса, второй вход которого соединен с прямым входом второго JK-триггера, а выход - с первым входом третьего элемента 2И межразрядной связи, выход которого соединен с J- и K-входами четвертого JK-триггера, а второй вход - с прямым выходом третьего JK-триггера, J- и K-входы которого соединены с выходом второго элемента 2И-НЕ инверсной логики межразрядной связи, второй вход которого подключен к инверсному выходу второго JK-триггера, и прямой выход четвертого JK-триггера подключен к J- и K-входам пятого JK-триггера, а инверсный выход соединен с первыми входами второго элемента 2И сквозного переноса и четвертого элемента 2И межразрядной связи, выход которого соединен с J- и K-входами шестого JK-триггера, а второй вход соединен с прямым выходом пятого JK-триггера, инверсный выход которого подключен к второму входу второго элемента 2И сквозного переноса, выход которого соединен с первыми входами пятого элемента 2И межразрядной связи и третьего элемента 2И

входом управления счетом ДФКД, а выход соединен с J- и K-входами первого JK-триггера, прямой выход которого соединен с J- и K-входами второго JK-триггера и с первыми входами второго элемента 2И-НЕ инверсной логики межразрядной связи и первого элемента 2И-НЕ инверсной логики сквозного переноса, второй вход которого соединен с прямым входом второго JK-триггера, а выход - с первым входом третьего элемента 2И межразрядной связи, выход которого соединен с J- и K-входами четвертого JK-триггера, а второй вход - с прямым выходом третьего JK-триггера, J- и K-входы которого соединены с выходом второго элемента 2И-НЕ инверсной логики межразрядной связи, второй вход которого подключен к инверсному выходу второго JK-триггера, и прямой выход четвертого JK-триггера подключен к J- и K-входам пятого JK-триггера, а инверсный выход соединен с первыми входами второго элемента 2И сквозного переноса и четвертого элемента 2И межразрядной связи, выход которого соединен с J- и K-входами шестого JK-триггера, а второй вход соединен с прямым выходом пятого JK-триггера, инверсный выход которого подключен к второму входу второго элемента 2И сквозного переноса, выход которого соединен с первыми входами пятого элемента 2И межразрядной связи и третьего элемента 2И

сквозного переноса, выход которого соединен с первыми входами шестого элемента 2И межразрядной связи и четвертого элемента 2И сквозного переноса, . . . , и выход (r - 5)-го элемента 2И сквозного переноса соединен с первым входом (r - 2)-го элемента 2И межразрядной связи, второй вход которого соединен с прямым выходом (r - 1)-го JK-триггера, а выход соединен с J- и K-входами r-го JK-триггера, C-входы синхронизации нулевого JK-триггера и первого JK-триггера соединены с выходом логического инвертора, вход которого соединен с C-входом синхронизации ДФКД, с первым входом первого элемента 2И-НЕ инверсной логики и с первым входом второго элемента 2И-НЕ инверсной логики, выход которого соединен с C-входами синхронизации r - 4 JK-триггеров с пятого JK-триггер по r-й JK-триггер, а второй вход соединен с выходом элемента 4И-НЕ, первый вход которого подключен к прямому выходу нулевого JK-триггера, а второй, третий и четвертый входы соответственно подключены к инверсным выходам первого, второго и третьего JK-триггеров, второй выход первого элемента 2И-НЕ инверсной логики соединен с инверсным выходом нулевого JK-триггера, а выход - с C-входами синхронизации второго, третьего и четвертого JK-триггеров, и выход (r - 1)-входового дешифратора соединен с первым входом элемента 2И-НЕ и с первым входом первой группы входов 2И элемента 2 х 2И-ИЛИ-НЕ, второй вход которой и второй вход элемента 2И-НЕ в зависимости от числового эквивалента Kдj коэффициента деления подключены к прямому выходу i-го JK-триггера при значениях Kдj = 2i-1 • (1 + 4j),

где j = 1, 2 ..., или к инверсному выходу i-го JK-триггера при значениях Kдj = 2i-1 • (3 + 4j), где j = 0, 1, 2 ..., а входы (r - 1)-входового дешифратора подключены к прямым или инверсным выходам остальных r - 1 JK-триггеров в соответствии с поразрядно записанным кодом Грея, числовой эквивалент которого равен целочисленному эквиваленту Kдj коэффициента деления, первый вход второй группы входов элемента 2 х 2И-ИЛИ-НЕ подключен к R-входу сброса ДФКД, а выход элемента 2 х 2И-ИЛИ-НЕ соединен с  входами сброса r + 1 JK-триггеров с нулевого JK-триггера по r-й JK-триггер, выход элемента 2И-НЕ подключен к

входами сброса r + 1 JK-триггеров с нулевого JK-триггера по r-й JK-триггер, выход элемента 2И-НЕ подключен к  выходу сброса ДФКД, у которого JK-вход разрешения счета ДФКД соединен с JK-входом разрешения счета ДПКД и подключен к прямому выходу первого RS-триггера, инверсный выход которого соединен с

выходу сброса ДФКД, у которого JK-вход разрешения счета ДФКД соединен с JK-входом разрешения счета ДПКД и подключен к прямому выходу первого RS-триггера, инверсный выход которого соединен с  входом управления счетом ДФКД и с

входом управления счетом ДФКД и с  входом управления счетом ДПКД, который выполнен в виде n-разрядного синхронного счетчика импульсов в коде Грея, у которого JK-вход разрешения счета ДПКД подключен к J- и K-входам нулевого JK-триггера, прямой выход которого подключен к второму входу первого элемента 2И-НЕ инверсной логики межразрядной связи, первый вход которого подключен в

входом управления счетом ДПКД, который выполнен в виде n-разрядного синхронного счетчика импульсов в коде Грея, у которого JK-вход разрешения счета ДПКД подключен к J- и K-входам нулевого JK-триггера, прямой выход которого подключен к второму входу первого элемента 2И-НЕ инверсной логики межразрядной связи, первый вход которого подключен в  входу управления счетом ДПКД, а выход соединен с J- и K-входами первого JK-триггера, прямой выход которого подключен к J- и K-входам второго JK-триггера, к первым входам второго элемента 2И-НЕ инверсной логики межразрядной связи и первого элемента 2И-НЕ инверсной логики сквозного переноса, второй вход которого соединен с прямым выходом второго JK-триггера, а выход - с первым входом третьего элемента 2И межразрядной связи, выход которого

входу управления счетом ДПКД, а выход соединен с J- и K-входами первого JK-триггера, прямой выход которого подключен к J- и K-входам второго JK-триггера, к первым входам второго элемента 2И-НЕ инверсной логики межразрядной связи и первого элемента 2И-НЕ инверсной логики сквозного переноса, второй вход которого соединен с прямым выходом второго JK-триггера, а выход - с первым входом третьего элемента 2И межразрядной связи, выход которого

соединен с J- и K-входами четвертого JK-триггера, а второй вход - с прямым выходом третьего JK-триггера, J- и K-входы которого соединены с выходом второго элемента 2И-НЕ инверсной логики межразрядной связи, второй вход которого подключен к инверсному выходу второго JK-триггера, прямой выход четвертого JK-триггера подключен к J- и R-входом пятого JK-триггера, а инверсный выход соединен с первыми входами второго элемента 2И сквозного переноса и четвертого элемента 2И межразрядной связи, выход которого соединен с J- и K-входами шестого JK-триггера, а второй вход соединен с прямым выходом пятого JK-триггера, инверсный выход которого подключен к второму входу второго элемента 2И сквозного переноса, выход которого соединен с первыми входами пятого элемента 2И межразрядной связи и третьего элемента 2И сквозного переноса, выход которого соединен с первыми входами шестого элемента 2И межразрядной связи и четвертого элемента 2И сквозного переноса, ..., а выход (n - 5)-го элемента 2И сквозного переноса соединен с первым входом (n - 2)-го элемента 2И межразрядной связи, второй вход которого соединен с прямым выходом (n - 1)-го JK-триггера, а выход соединен с J- и K-входами n-го JK-триггера, C-входы синхронизации нулевого JK-триггера и первого JK-триггера соединены с выходом логического инвертора, вход которого соединен с C-входом синхронизации ДПКД, с первым входом первого элемента 2И-НЕ инверсной логики и с первым входом второго элемента 2И-НЕ инверсной логики, выход которого соединен с C-входами синхронизации n - 4 JK-триггеров с пятого JK-триггера по n-й JK-триггер, а второй вход соединен с выходом второго элемента 4И-НЕ, первый вход которого подключен к

прямому выходу нулевого JK-триггера, второй вход соединен с инверсным выходом первого JK-триггера, третий вход подключен к инверсному выходу второго JK-триггера, четвертый вход соединен с инверсным выходом третьего JK-триггера и с третьим выходом первого элемента 4И-НЕ, выход которого подключен к  выходу переключения счета ДПКД, а первый вход соединен с вторым входом второго элемента 2И-НЕ инверсной логики и с инверсным выходом нулевого JK-триггера, второй вход первого элемента 4И-НЕ подключен к выходу первого элемента 2И-НЕ инверсной логики сквозного переноса, а четвертый вход соединен с выходом третьего элемента 2И-НЕ инверсной логики, первый вход которого соединен с выходом третьего элемента 4И-НЕ, второй вход - с выходом (n - 7)-входового элемента И-НЕ, у которых n - 3 входов поразрядно подключены к инверсным выходам n - 4 JK-триггеров с четвертого JK-триггера по (n - 1)-й JK-триггер и к прямому выходу n-го JK-триггера ДПКД, PE-вход записи ДПКД подключен к объединенным первым входам n + 1 логических пар элементов 2И-НЕ, у которых n прямых сигнальных выходов поразрядно подключены к

выходу переключения счета ДПКД, а первый вход соединен с вторым входом второго элемента 2И-НЕ инверсной логики и с инверсным выходом нулевого JK-триггера, второй вход первого элемента 4И-НЕ подключен к выходу первого элемента 2И-НЕ инверсной логики сквозного переноса, а четвертый вход соединен с выходом третьего элемента 2И-НЕ инверсной логики, первый вход которого соединен с выходом третьего элемента 4И-НЕ, второй вход - с выходом (n - 7)-входового элемента И-НЕ, у которых n - 3 входов поразрядно подключены к инверсным выходам n - 4 JK-триггеров с четвертого JK-триггера по (n - 1)-й JK-триггер и к прямому выходу n-го JK-триггера ДПКД, PE-вход записи ДПКД подключен к объединенным первым входам n + 1 логических пар элементов 2И-НЕ, у которых n прямых сигнальных выходов поразрядно подключены к  входам установки n JK-триггеров с нулевого JK-триггера по (n - 1)-й JK-триггер, а n инверсных сигнальных выходов поразрядно соединены с их

входам установки n JK-триггеров с нулевого JK-триггера по (n - 1)-й JK-триггер, а n инверсных сигнальных выходов поразрядно соединены с их  входами сброса в названной последовательности, прямой сигнальный выход n-й логической пары элементов 2И-НЕ подключен к

входами сброса в названной последовательности, прямой сигнальный выход n-й логической пары элементов 2И-НЕ подключен к  входу сброса n-го JK-триггера, а инверсный сигнальный выход соединен с его

входу сброса n-го JK-триггера, а инверсный сигнальный выход соединен с его  входом установки, сигнальный вход первого элемента 2И-НЕ нулевой логической пары элементов 2И-НЕ соединен с DO-входом предустановки ДПКД, а сигнальные входы первых элементов 2И-НЕ n логических пар элементов 2И-НЕ поразрядно соединены с соответствующими Di-входами предустановки ДПКД с первого по n-й, выход первого элемента 2И-НЕ инверсной логики соединен с C-входами синхронизации второго, третьего и четвертого JK-триггеров,

входом установки, сигнальный вход первого элемента 2И-НЕ нулевой логической пары элементов 2И-НЕ соединен с DO-входом предустановки ДПКД, а сигнальные входы первых элементов 2И-НЕ n логических пар элементов 2И-НЕ поразрядно соединены с соответствующими Di-входами предустановки ДПКД с первого по n-й, выход первого элемента 2И-НЕ инверсной логики соединен с C-входами синхронизации второго, третьего и четвертого JK-триггеров,  выход переключения счета ДПКД соединен с

выход переключения счета ДПКД соединен с  входом сброса второго RS-триггера, инверсный выход которого соединен с CO-входом переноса m-разрядного сумматора ПДК и с первым входом первой 2И группы входов элемента 2 х 2И-ИЛИ-НЕ, второй вход которой соединен с прямым выходом m-го JK-триггера ДПКД, а первый вход второй 2И группы входов элемента 2 х 2И-ИЛИ-НЕ соединен с прямым выходом второго RS-триггера, второй вход которой соединен с инверсным выходом m-го JK-триггера ДПКД, выход элемента 2 х 2И-ИЛИ-НЕ соединен с входом старшего m-го разряда преобразователя кода Грея в ПКД, остальные m - 1 входов которого поразрядно подключены к соответствующим m - 1 входам выходной сигнальной шины ДПКД, Q1-выход которой подключен к прямому выходу первого JK-триггера, Q2-выход - к прямому выходу второго JK-триггера, . . ., Qi-выход - к прямому выходу i-го JK-триггера, Qm-1-выход - к прямому выходу (m-1)-го JK-триггера,

входом сброса второго RS-триггера, инверсный выход которого соединен с CO-входом переноса m-разрядного сумматора ПДК и с первым входом первой 2И группы входов элемента 2 х 2И-ИЛИ-НЕ, второй вход которой соединен с прямым выходом m-го JK-триггера ДПКД, а первый вход второй 2И группы входов элемента 2 х 2И-ИЛИ-НЕ соединен с прямым выходом второго RS-триггера, второй вход которой соединен с инверсным выходом m-го JK-триггера ДПКД, выход элемента 2 х 2И-ИЛИ-НЕ соединен с входом старшего m-го разряда преобразователя кода Грея в ПКД, остальные m - 1 входов которого поразрядно подключены к соответствующим m - 1 входам выходной сигнальной шины ДПКД, Q1-выход которой подключен к прямому выходу первого JK-триггера, Q2-выход - к прямому выходу второго JK-триггера, . . ., Qi-выход - к прямому выходу i-го JK-триггера, Qm-1-выход - к прямому выходу (m-1)-го JK-триггера,  -выход - к прямому выходу m-го JK-триггера, а

-выход - к прямому выходу m-го JK-триггера, а  -выход - к его инверсному выходу.

-выход - к его инверсному выходу.

| СПОСОБ ПРОВЕТРИВАНИЯ ВЫЕМОЧНОГО УЧАСТКА | 1999 |

|

RU2163971C2 |

| Способ деления периодов следования импульсных сигналов | 1985 |

|

SU1651352A1 |

| Генератор синусоидальных колебаний инфранизкой частоты | 1978 |

|

SU765983A2 |

| СПОСОБ РЕГУЛИРОВАНИЯ МОЩНОСТИ | 1999 |

|

RU2164007C1 |

| Левин В.А | |||

| и др | |||

| Синтезаторы частот с системой ИФАП | |||

| - М.: Радио и связь, 1989, с.14. | |||

Авторы

Даты

1998-11-10—Публикация

1997-02-27—Подача