(5) ИНЖЕКЦИОННЫЙ ДИНАМИЧЕСКИЙ ЭЛЕМЕНТ

1

Изобретение относился к микроэлектронике, а именно к интегральным инжекционным логическим схемам.

По основному авт. св. № 953731 известен инжекционный динамический элемент, содержащий бистабильную ячейку на первом и втором многоколлекторных транзисторах п-р-п типа с перекрестнымиколлёкторно-базовыми связями, базы и эмиттеры которых соединены соответственно с коллекторами инжектирующих транзисторов, ключевой транзистор nrp-h типа, база которого соединена с управляющим входом, а эмиттер - с о&цей шиной.

Незадействованные коллекторы первого и второго многоколлекторных транзисторов подключены к выходам устройства, база буферного транзистора п-р-п типа соединена с информационным входом, вторым коллектором; первого многоколлекторного тра.нзистора и коллектором соответствующего инжектирующего транзистора эмиттер

подключен к общей шине, а коллектор к базе первого многоколлекторного транзистора и первому коллектору ключевого транзистора, база которого подключена к коллектору соответству ющего инжектирующего транзистора, а второй коллектор - к эмиттеру переинжектирующего транзистора и коллектору соответствующего инжектирующего транзистора , базы инжектирующих и переинжектирующего транзисторов подключены к общей шине, а эмиттеры инжектирующих транзисторов - к шине питания П 3Недостатком этого устройства являются узкие функциональные возможности.

Цель изобретения - расширение функциональных возможностей.

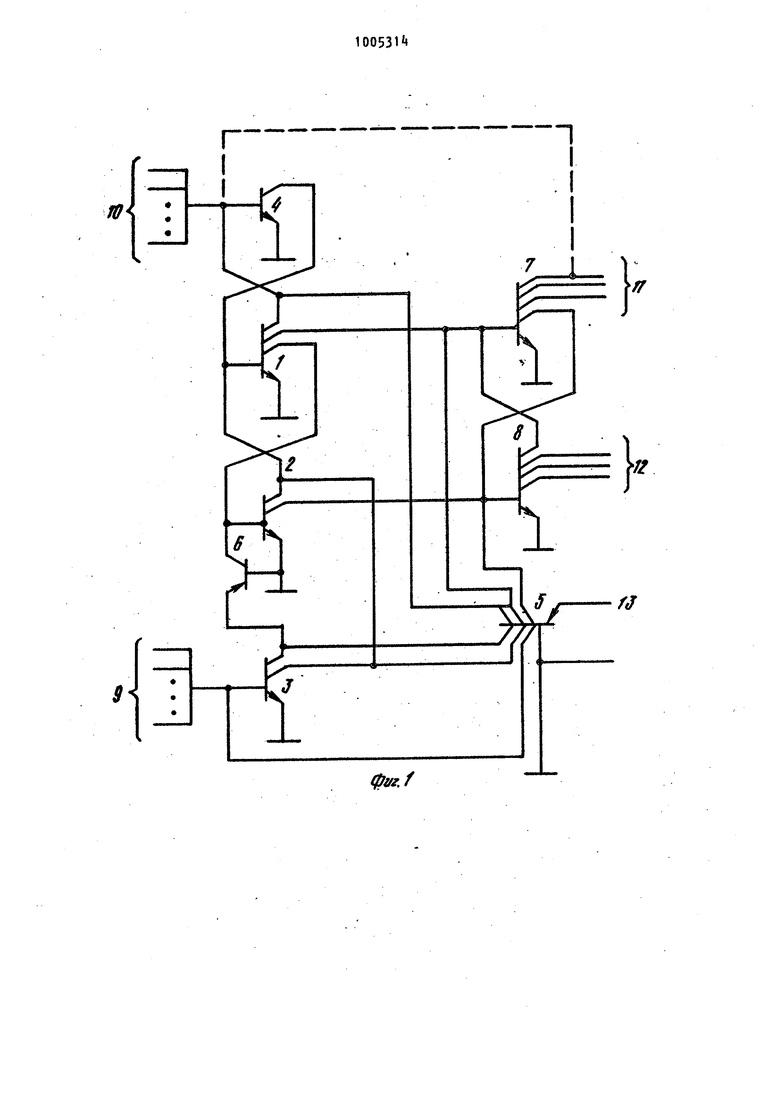

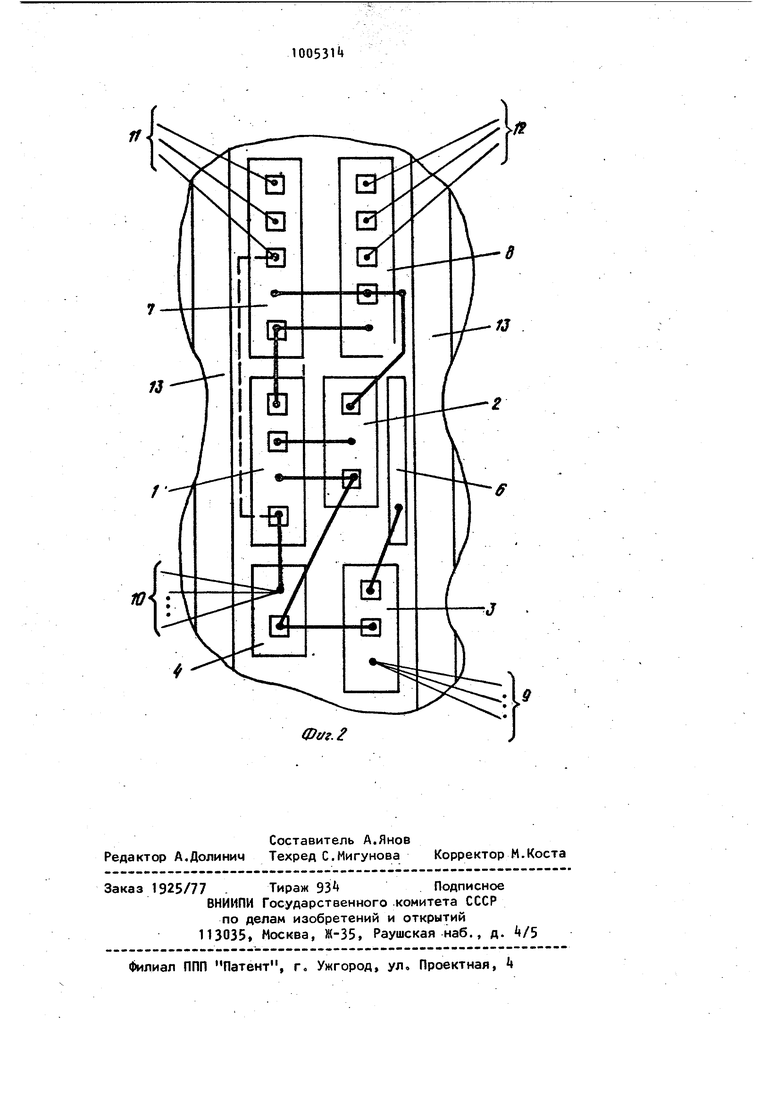

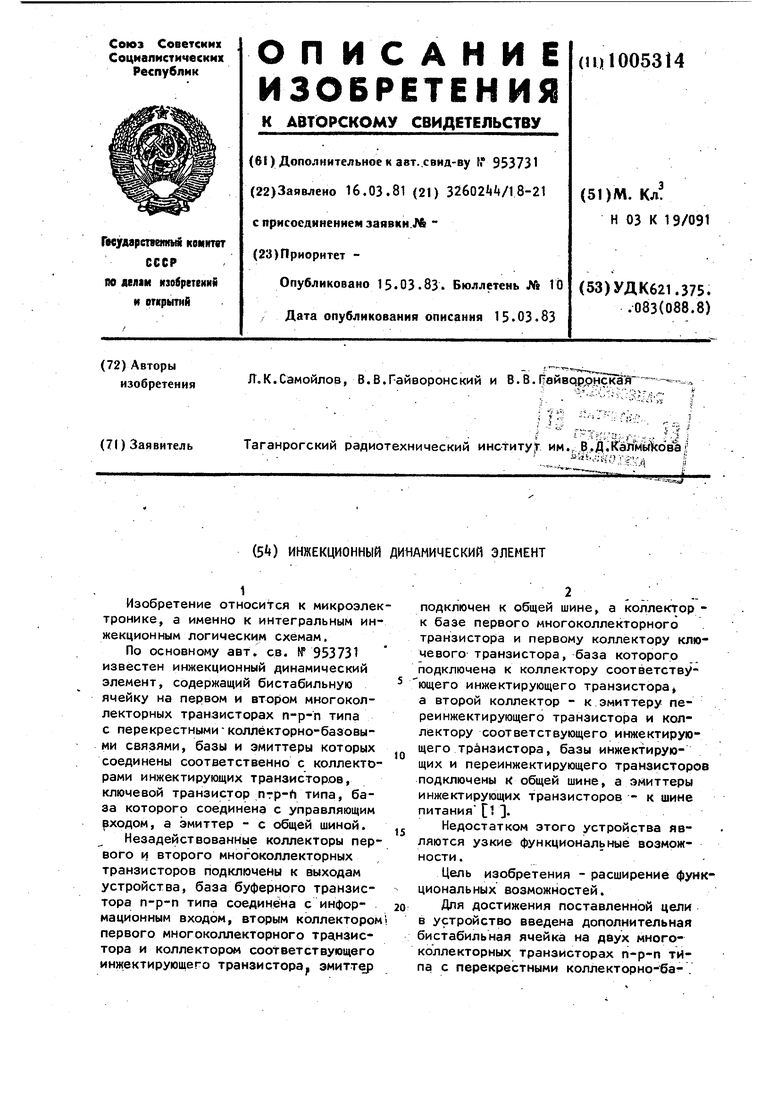

Для достижения поставленной цели в устройство введена дополнительная бистабильная ячейка на двух многоколлекторных транзисторах п-р-п типа с перекрестными коллекторно-ба- . зовыми связями, базы которых подключены соответственно к коллекторам первого и второго многоканальных транзисторов и дополнительным коллек торам инжектирующего р-п-р транзистора, а эмиттеры к общей шине. te фиг. 1 изображена принципиальная схема предлагаемого устройства} на фиг. 2 - функционально-топологическая схема. Устройство содержит первый и второй многоколлекторные транзисторы (МКТ) 1 и 2, ключевой транзистор 3, буферный транзистор Ц, инжектирующий транзистор 5, переинжектирующий транзистор 6, МКТ дополнительной бистабильной ячейки 7 и 8, управляющие входы 9, информационные входы 10, вы ходы 11 и 12, шина питания 13. Устройство работает следующим образом. Пусть в исходном состоянии открыт один из f.KT дополнительной бистабиль ной ячейки 7, хотя бы на одном из информационных входов Ю присутствует логический нуль, а на всех управляющих входах 9 - логические единицы Ток, инжектирующий в базу ключевого транзистора 3, приводит к открыванию последнего., который своими коллек торами перехватывает токи питания МКТ бистабильной ячейки 1 и 2, удерживая их в закрытом состоянии. Буфер ный транзистор закрыт, поскольку его ток питания перехватывается входом, соединенным с логическим нулем. Второй МКТ дополнительной бистабильной ячейки 2 также закрыт. Такое сос тояниэ схемы может поддерживаться сколь угодно долго. Изменения входных сигналов на информационных входах приводят лишь к переключениям буферного транзистора k, который открывается при всех логических единицах на входах 10, не влияющих на состояние бистабильной ячейки на МКТ 1 и 2, который выдает на прямые выходы 12 логические нули, а на инверс ные выходы 11 - логические единицы. Если теперь на любом из управляющих входов 9 произойдет перекпюче- ние сигнала в логический нуль, то ключевой транзистор 3 закроется, а на МКТ 1 и 2 будет подан питающий ток от инжектирующего транзистора 5Поскольку в базовой цепи МКТ 2 находится задержка в виде переинжектирующего р-п-р транзистора 6, то срстояние бистабильной ячейки опредеЮ4 ляется сигналами на информационных входах 10,в данный момент времени. Так например, при лЬгическом нуле хотя бы на одном из входов 10 (буферный транзистор в данный момент времени закрыт) ток питания МКТ 1 достигнет базовой р-области последнего раньше, чем ток питания МКТ 2. МКТ 1 откроется и своими коллекторами выключит (закроет путем перехвата токов питания) МКТ 2, МКТ 7 и буферный транзистор . Изменения сигналов на информационных входах 10 теперь блокированы коллектором открытого МКТ 1 , база буферного транзистора 4 обесточена. Закрывание МКТ 7 дополнительной бистабильной ячейки приводит к расшунтированию входа МКТ 8, который открывается. На выходах устройства устанавливается информация, соответственйо на прямых выходах логические нули, на инверсных выходах 1J - логические единицы. Если к моменту закрывания ключевого транзистора 3 на всех информационных входах 10 присутствуют логические единицы, то буферный транзис тор k будет открыт током питания, поступающим в его базу от инжектирующего транзистора и, следовательно, удержит НКТ 1 в закрытом состоянии. Ток питания МКТ 2 через переинжектирующий .р-п-р транзистор б достигнет базы МКТ 2, который открывшись выключит МКТ 8 и удержит в закрытом состоянии МКТ 1. Последующие изменения сигналов на информационных входах 1П приводят к переключениям буферного транзистора , которые лишь подтверждают состояние бистабильной ячейки на МКТ 1, 2. МКТ 8, выключившись-, расшунтирует цепь базы МКТ 7, который открывается и на выходах устройства устанавливаются логические нули и логические единицы на 11 и 12 выходах соответственно. При очередном поступлении сигналов на управляющую шину, приводящих к открыванию ключевого транзистора (т.е. на всех входах 9 логические единицы), МКТ 1, 2 закрываются, а состояние дополнительной бистабильной ячейки фиксируется. (ак видно из приведенного описания принципа действия, устройство функционирует как синхронный (динамический) О-триггер, воспринимающий входную информацию и изменяющий состояние дополнительной бистабильной ячейки (выходы которой являются вы510ходами устройства) только на фронте сигнала синхронизации приводящего к закрыванию ключевого транзис тора 3, а остальное время записанная информация не изменяется. К осо бенностям схемы следует отнести так же наличие нулевых логических функций И (в положительной логике) на управляющих входах 9 и на информационных входах 10, которые реализуются без затрат оборудования и позволяют значительно расширить функциональные возможности устройства. Предложенное устройство обладает широкими функциональными ВОЗМОЖностями. Так при замыкании одного из коллекторов МКТ 7 с информационным D-входом (на фиг. 1, 2 связь показана пунктиром)организуется триггер со счетным входом (с прямым и инверсным выходами), причем переключения триггера осуществляется синхронно в моменты времени соответствующие перепаду сигнала на входе синхронизации из логической единицы в логический нуль. Без затрат оббрудования данное схемотех ческое решение триггерного устрЫ ства может использовано и ках I-К триггер при следующей коммутации в схеме: один из коллекторов МКТ 7 соединен с базой буферного транзистора k, база МКТ 1 соединена гальванически с группой входов К собранных по И, а база МКТ 2 соединена непосредственно связью со со входами I, которые также образую путем соединения в одной точке ) ло гическую схему так называемого монтажног.о или проводного И. Предлагаемое изобретение может быть использовано для построения счетчиков, делителей частоты, статических и сдвигающих регистров, логических устройств, реализующих динамический метод кодирования информации, поточных обрабатывающих структур и т.д. Широкие функциональные возможности малая площадь, занимаемая на кристалле, и низкая величина работы пере-, ключения позволяет считать предложенное устройство перспективной ячейкой БИС с технологией , Формула изобретения Инжекционный динамический элемент по авт. св. № 953731 отличающийся тем, что, с целью расширения функциональных возможностей, в него введена дополнительная бистабильная ячейка на двух многоколлекторных транзисторах п-р-п типа с перекрестными коллекторно-базовыми связями, базы которых подключены соответственно, к коллекторам первого и второго многоколлекторных транзисторов и дополнительным коллекторам инжектирующего р-п-р транзистора, а эмиттеры - к общей шине. Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР К 953731, кл. Н 03 К 91/091, 1980.

W

Фиг. г

/

| название | год | авторы | номер документа |

|---|---|---|---|

| Инжекционный динамический элемент | 1980 |

|

SU953731A1 |

| Ячейка памяти | 1982 |

|

SU1140165A1 |

| Одноразрядный комбинационный сумматор | 1981 |

|

SU981995A1 |

| Тактируемый @ -триггер в интегральной инжекционной логике | 1982 |

|

SU1051692A1 |

| Тактируемый @ -триггер @ -типа | 1985 |

|

SU1275738A1 |

| Четырехразрядный преобразователь двоичного кода в циклический код Грея | 1986 |

|

SU1388993A1 |

| Одноразрядный сумматор | 1980 |

|

SU907543A1 |

| Интегральный четырехзначный D-триггер | 1986 |

|

SU1338012A1 |

| И @ Л ячейка | 1986 |

|

SU1386951A1 |

| Триггер | 1983 |

|

SU1150734A1 |

Авторы

Даты

1983-03-15—Публикация

1981-03-16—Подача