n - р - n ключевого транзистора и третьим коллектором второго n - р - n ключевого транзистора, второй коллектор второго n - р - n согласующего транзистора соединен с базой и соответствующим коллектором второго n - р - n ключевого транзистора последующего каскада ячейки памя ти , база и коллектор блокировочного n - р - n - транзистора подключены к соответствующим . объединенным коллекторам пер вого и второго n - р - n - ключевых транзисторов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Ячейка памяти для регистра сдвига | 1979 |

|

SU851495A1 |

| Аналого-цифровой преобразователь | 1980 |

|

SU902243A1 |

| Тактируемый @ -триггер в интегральной инжекционной логике | 1982 |

|

SU1051692A1 |

| Ячейка памяти | 1974 |

|

SU546935A1 |

| Многоуровневая ячейка памяти | 1980 |

|

SU1067534A1 |

| Четырехуровневый одноразрядный сумматор | 1982 |

|

SU1095174A1 |

| Буферный логический элемент и @ л типа | 1981 |

|

SU980289A1 |

| Интегральный инжекционный логический элемент | 1982 |

|

SU1046933A1 |

| Инжекционный динамический элемент | 1980 |

|

SU953731A1 |

| Динамический логический элемент | 1979 |

|

SU822370A1 |

ЯЧЕЙКА ПАМЯТИ, содержащая в каждом из четырех каскадов первый и второй п - р - п ключевые транзисторы, база пердого п - р - п ключевого транзистора соединена с первым KOJtnejtTopoM второго п - р - п ключевого транзистора, тактирующий п - .р - п-транзистор, база которого соединена с тактовой шиной, опорный п - р - п-транзистор, база которого соединена с эмиттерами п т р - п ключевых транзисторов и общей шиной, a эмиттер - с источником питания, колпекторы - с базами соответствующих п - р - п-транзисторов, отличающая ся тем, что, с целью повышения надежности за счет точной установки выходных значений токов ячейки памяти, в нее введены первый, второй, третий и четвертый п - р -птранзисторы связи, a в каждый каскад, кроме последнего, введены третий п - р - п ключевой транзистор, первый и второй п - р - п согласукнцие транзисторы, в 1етвертый каскад введены первый блокировочный и первый согласующий п - р - п-транзисто- ры, причем первый коллектор тактирующего п - р - п-транзистора соединен с тактовой шиной, второй коллектор с базой первого п - р - п-транзисто- pa связи, другие коллекторы - с базами и первыми коллекторами третьих п - р - п ключевых транзисторов и вторьми коллекторами вторых п - р - п ключевых транзисторов, первый коллектор первого п - р - п транзисто- pa саязи соединен с базой и первым коллектором второго, п - р - п-транзистора связи, второй коллектор которого соединен с первым коллектором третьего п - р - п-транзистора связи, базой и соответствующим коллектором второго п - р - п ключевого транзистора первого каскада ячейки памяти, второй коллектор третьего п - р - п транзистора связи, соединенный с его базой и входной шиной, подключен к коллектору п - р - п-транзистора связи, база которого соединена с вторым коллектором первого п - р - п4 транзистора связи, первый коллектор О первого п - р - п ключевого транзистора соединен с его базой, второй Sb Dn коллектор соединен с базой первого п - р - п ключевого транзистора последукицего каскада, причем второй коллектор первого согласующего п - р - п-транёистора четвертого каскада соединен с базой первого п - р - п ключевого транзистора первого каскада ячейки памяти, a третий коллектор является выходом ячейки памяти, база второго согласующего п - р - п-транзитора первого, второго и третьего каскадов ячейки памяти соединена с его первым коллектором и вторым коллектором третьего

Изобретение относится к вычитательной технике и предназначено для построения БИС.

Известны инжекционные ячейки памяти, содержаоще триггер на n - р - п-транзисторах и инжектирующие р - n - р-транзисторы, коллекторы которых соединены с базами n - р - п-транзисторов СО.

Недостатками известных ячеек являются незначительные функциональные возможности, ограниченные одновходовой операцией сдвига информации, и ограничение по количеству запоминаемых входных уровней. .

Известна также схема динамического логического злемента, содержащего триггер на n - р - п-транзисторах, инжектирующие р - n - ртранзисторы, базы которых соединены с эмиттерами n - р - п-транзисторов и шиной нулевого потенциала.

Схема имеет более широкие функциональные возможности, однако может оперировать цифровыми сигналами лишь двух логических уровней.

Наиболее близкой к предлагаемой является ячейка памяти, которая содержит триггеры-компараторы, входной р n - р-транзистор, коллекторы которого соответственно соединены с базами первых n - р - п-транзисторов триггеров, схема содержит также блокировочный многоколлектор ный n - р - п-тран8истор, опорный многоколлекторный р - n - р-транзистор, р - n - р-транзистор связи, коллекто которого соответственно соединены с базами триггеров-компараторов, эмиттер - с базой блокировочного транзистора и тактовой шиной, эмиттеры n - р - п-транзисторо и базы р - n - р-транзисторов объеднены с шиной нулевого потенциала 2J

К недостаткам известного устройства относятся использование генератора опорных импульсов; использование различных источников напряжения для записи входной информации и ее хранения, что неизбежно приводи к неоднозначности результатов; использование в качестве развязываюпщх горизонтальных р - n - р-транзисторов , которые в силу своей электрофизической симметрии Требуют соблюдения строгого потенциального режима, т.е. требуют на выходе устройства использовать схему с низким входным сопротивлением. Все это приводит к. усложнению и удорожанию технологии изготовления указанного устройства в микроэлектронном исполнении.

Цель изобретения - повышение надежности ячейки памяти за счет точной установки выходных значений токов.

Поставленная цель достигается тем, что ячейка памяти, содержащая в каждом из четырех каскадов первый и второй n - р - n ключевые транзисторы, база первого n - р - n ключевого транзистора соединена с первым коллектором второго n - р - n ктаочевого транзистора, тактирующий n - р - п-транзистор, база которого соединена с тактовой шиной, рпорн n - р п-транзистрр, база которого соединена с эмиттерами n - р - n ключевых транзисторов и общей шиной, а эмиттер - с источником питания, коллекторы - с базами соответствуюпц1х n - р - п-транзисторов, дополнительно содержит первый, второй, третий и четвертый n - р - п-транзисторы связи, а в каждый каскад, кроме последнего, введены третий n - р - n ключевой транзистор, первый и второй п - р - п согласующие транзисторы, в четвертый каскад введены первьй блокировочный и перТвый согласующий п - р - птранзисторы, причем первый коллектор тактирукнцего п - р - п-транзистора соединен с тактовой шиной, второй коллектор - с базой первого п - р - птранзистора связи, другие коллекторы - с базами и первыми коллекторами третьих п - р - п ключевых транзисторов и вторыми коллекторами вторых п - р - п ключевых транзисторов, первый коллектор первого п - р - птранзистора связи соединен с базой и первым коллектором второго п - р - птранзистора связи, второй коллектор которого соединен с первым коллектором третьего п - р - п-транзистора связи, базой и соответствующим коллектором второго п - р - п ключевого транзистора первого каскада ячейки памяти, второй коллектор третьего п - р - п-транзистора связи, соединенный с его базой и входной шиной, подк1почен к коллектору п - р - птранзистора связи, база которого соединена с вторым коллектором первого п - р - п-транзистора связи, первый коллектор первого п - р - п ключевого транзистора соединен с его базой, а второй коллектор соединен с базой первого п - р - п ключевого транзистора последующего каскада, причем второй коллектор первого согласующего п -р - п-транзистора четвертого каскада соединен с базой первого п - р ключевого транзистора первого каскада ячейки памяти, а третий коллектор является выходом ячейки памяти, база второго согласующего п - р - птранзистора первого, второго и третьего каскадов ячейки памяти соединена с его первым коллектором и вторым коллектором третьего п - р - п ключевого транзистора и третьим коллектором второго п - р - п ключевого транзистора, .второй коллектор второг п - р - п согласующего транзистора соединен с базой и соответствующим коллектором второго п - р - п ключевого транзистора последующего каскда ячейки памяти, база и коллектор блокировочного п - р - п- транзистора подключены к соответствующим объедиНевньн коллекторам первого и второго п - р - О ктаочевых транзисторов.

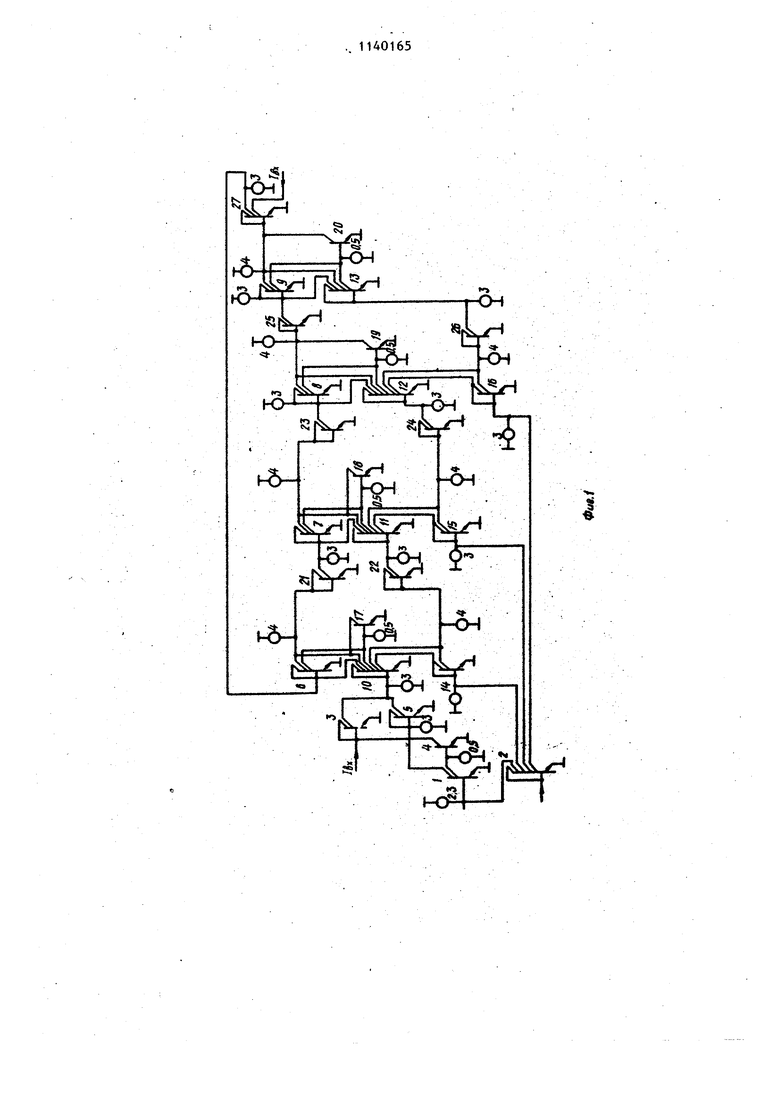

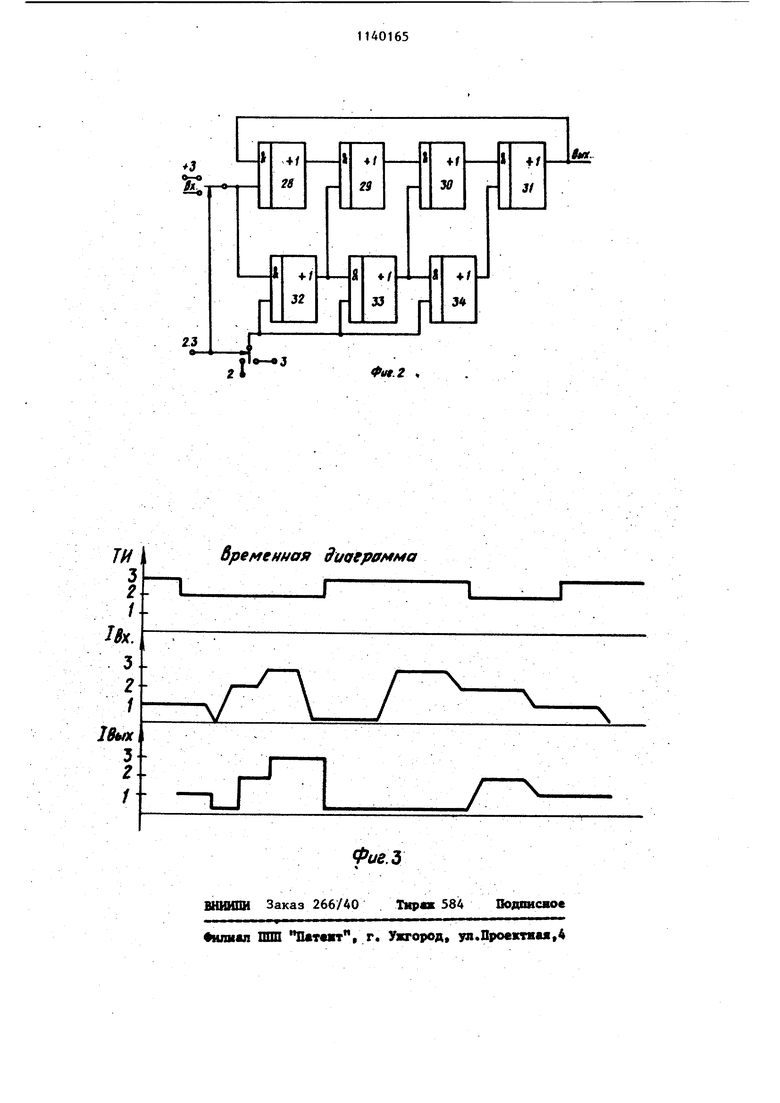

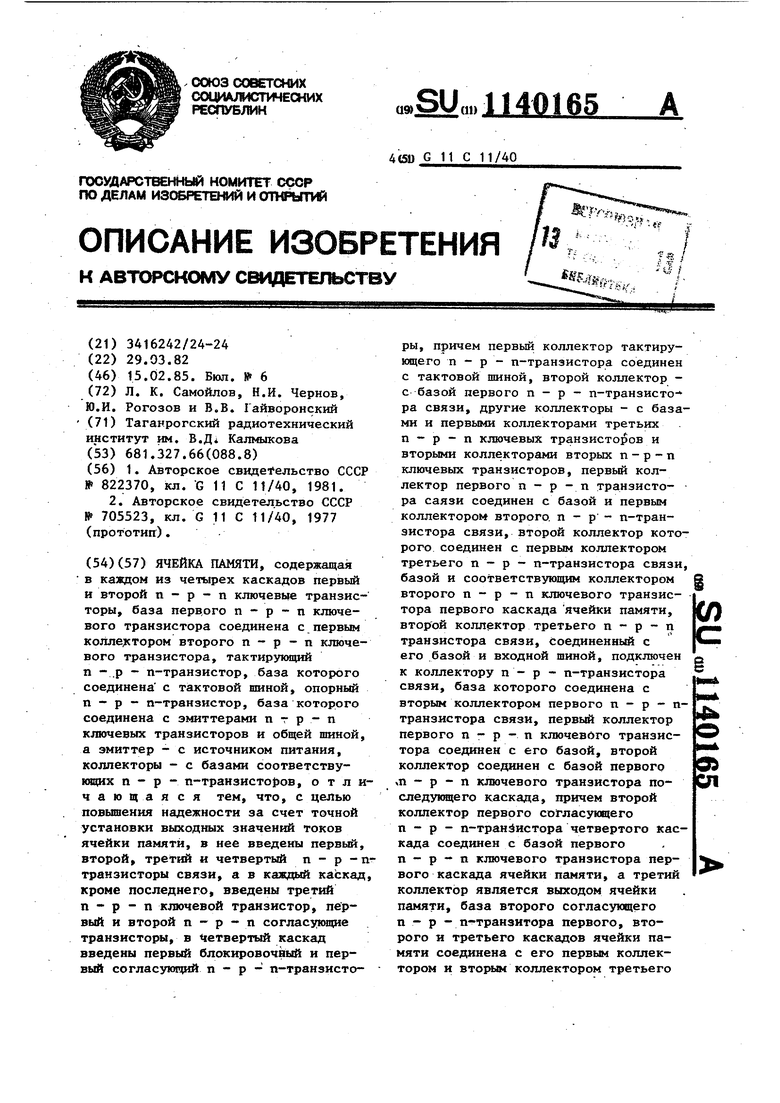

На фиг. 1 приведена электрическая принципиальная схема ячейки памяти д четырехуровневого входного сигнала; на фиг. 2 - функциональная схема устройства, поясняющая принцип ее работы; на фиг. 3 - временная диаграмма работы устройства.

Ячейка памяти (фиг. 1) содержит многоколлекторный п - р - п-транзистор 1, связан тактирующий многоколлекторный п - р - п-транзистор 2, п - р - п-транзисторы 3, 4 и 5 связи, первые ключевые многоколлекторные п - р - п-транзисторы 6-9, вторые ключевые п - р - п-транзисторы 10-13, третьи ключевые многоколлекторные п - р - п-транзисторы 14, 15 и 16, блокировочные п - р - п транзисторы J7-20, согласующие п - р - п-транзисторы 21-27, опорный многоколлекторный р - п - ртранзистор, который для облегчения чтения чертежа обозначен источниками тока, каждый из которых есть коллектор опорного р - р - р-транзистора, величина токов обозначена цифрами в относительных единицах, причем величины токов устанавливаются путем изменения соотношений длин базовой и инжектирующей р-областей.

База транзистора 1 соединена с вторым коллектором транзистора 2 и с одним из коллекторов транзистора 28, база и первый коллектор транзистора 2 соединены с тактовой шиной, коллектор транзистора 1 соединен с базой и коллектором транзистора 5 и источником тока величиной 3 единицы, второй коллектор транзистора 1 соединен с источником тока (0,5 единиц) и базой транзистора 4, коллектор которого соединен с входной шино базой и первым коллектором транзисто ра 3, вторые коллекторы транзисторов 3 и 5, соединены с базой и первым -коллектором транзистора 10, вторые коллекторы,транзисторов 10-13 соединены соответственно с базой и первым коллектором транзисторов 6-9 и вторыми коллекторами согласуюо(их транзисторов 27, 21, 23 и 25, коллекторы транзистора 2 соедийены соответственно с базой и первым коллектором транзисторов 14, 15 и 16, третьими коллекторами транзисторов 10, 11 и 12, четвертые коллекторы транзистоI ров 10-13 соединены соответственно с коллекторами транзисторов 17-20, вторыми коллекторами транзисторов 6-9, базой и первым коллектором согласующих транзисторов 21, 23, 25 и 27, пятые коллекторы транзисторов . 10-13 соединены соответственно с ба зой транзисторов 17-20 и третьими коллекторами транзисторов 6-9, шестые коллекторы транзисторов 10-13 соединены с вторыми коллекторами транзисторов 14, 15 и 16, базой и первьо 1 коллектором транзисторов 22, 24 и 26. На г. 2 изображены элементы 28 34, объединенные в функциональную схему ячейки памяти. Работает устройство в двух режимах: режиме записи и редаше хранения. Для четырехуровневой ячейки подаются тактирующие импульсы ампли тудой 2 единицы - для записи, 3 еди ницы - для хранения записанной инфор мации (фиг. 3). Рассмотрим работу устройства по функциональной схеме (фиг. 2). Тактирующие импульсы подаются на входной муль- иплексор - транзисторы 1, 3, 4 и 5 (фиг. 1), который подключает в режиме записи на первые входел элементов 28 и 32 входной ток а на второй вход элементов 32, 33 и 34 - ток, равный 3 единицам в режиме хранения на первые входы элементов 28 и 32 подается сигнал вели чиной 3 единицы, а на второй вход элементов 32, 33 и 34 - ток величиной 2 единицы. Логические элементы 28-34. реализуют функцию ГХ,, при х X min(x ; Xj) + 1 1«. При X X Если ячейка памяти хранит нулево сигнал, т.е. на выходе элемента 31 формируется сигнал нулевого уровня, то, так как на втором входе элемента 28 формируется сигнал величиной единицы, выход элемента 28 имеет сигнал единичного уровня, на первом входе элемента 32 формируется сигнал 3 единицы, на втором входе г 2 единицы, на входе элемента 32 сигнал 3 единицы. Аналогичные значе ния сигналов формируются на выходах элементов 33 и 34. Таким образом, на выходе элемента 29 присутствует сигнал 2 единицы,ла выходе элемента 30-3 единицы, на выходе элемента 31 - нулевой сигнал, который подает . 5 ся на первый вхбд элемента 28. Следовательно, цепь замкнута и на выходе ячейки памяти постоянно сохраняется нулевой сигнал до прихода импульса записи. Если по тактовому импульсу на первые входы элементов 28 и 32 подается сигнал единичного уровня, на выходах Элементов 28, 29 и 30 сохраняются значения сигналов, равных 1, 2 и 3 единицам, а на выходах элементов 32, 33 и 34 соответственно устанавливаются значения сигналов равных 2, 3 и О единицам. Таким образом, через некоторое время после пода-чи тактового импульса на первом входе элемента 31 формируется сигнал 3 единицы, на втором - О единиц, а на выходе устройства - единичный сигнал, равный входному сигналу (единичный уровень). При этом на выходах элементов 28, 29 и 30 соответственно устанавливаются сигналы 2, 3 И О единиц. Подача на тину управления сигнала хранения (сигнала трех уровней.) приводит к установлению на выходах элементов 32, 33 и 34 уровней сигналов,равных 3 единицам, а элементы 28-31 Сохраняют с-вое состояние. По данной структуре возможно построить N-уровневую ячейку памяти. Транзисторы 1-5 (фиг. 1) обеспечивают управление ячейкой памяти, подключают к ней управляющие и входной сигналы. Элемент 28 (фиг. 2) выполнен на транзисторах 6, 10, 17 и 27, элемент 32 выполнен на транзисторах 10 и 14, элемент 29 построен на транзисторах 21, 22, 7, 11, 15 и 18, элемент 33 - на транзисторах 22, 11, 15 и 18, элементы 30 и 31 соответственно состоят из транзисторов 23, 24, 8, 12, 19, 25, 26, 9, 13, 20, элемент 34 построен на транзисторах 24, 12, 16 и 19. Если ячейка памяти находится в режиме хранения нулевого уровня, то на тактовой шине формируется сигнал 3 единицы (фиг. 3), коллекторный ток транзистора 2 равен 3 единицам, поэтому транзисторы 1, 14, 15 и 16 закрыты. Транзистор 4 открыт и своим коллектором шунтирует вход транзистора 3. Коллекторный ток транзистора 5 равен 3 единицам, поэтому на входе транзистора 10 формируется нулевой входной ток. Так как транзисторы 14, 15 и 16 закрыты, то входной ток транзисторов 22, 24, 26 равен 4 единицам, а входные токи тран зисторов 11, 12-и 13 - нулю. Так как ячейка памяти хранит нулевой то то входной ток транзистора 6 равен нулю, а входной ток транзистора 18 - 0,5 единицам. Так как коллекторные токи транзисторов 6 и 10 рав ны нулю, то ток, инжектируемьй на вход транзистора 21, шунтируется транзистором 17, поэтому входной то .а следовательно, коллекторный ток транзистора 21 равен нулю. Соответственно, входной ток транзистора 7 равен 3 единицам, а входной ток транзистора 23 - 1 единице. Тогда входной ток транзисторов 8 и 25 равен 2 единицам, входной ток транзистора 27-3 единицам, а ток, поступающий на вход транзистора 6, равен 0. Таким образом, ячейка памяти приходит в устойчивое состояни Предположим, что при переходе ячейки памяти в режим записи (на тактовой шине 2 единицы) на входе формируется ток, равный.1 единице. В этом случае транзистор 1 открывается, транзисторы 4 и 5 - закрывают ся, поэтому входной ток транзистора 10 равен для данного случая 2 единицам.-Входные токи транзисторов 14, 15 и 16 равны единице. Транзистор 14 закрьшается транзистором 10 коллекторный ток которого равен 2 единицам, поэтому коллекторный ток транзистора 14 равен О, а входной 5 . 8 ток транзистора 22-2 единицам. Аналогично, входной ток транзисторов 11-1 единица, 24-3 единищл, 12-0 единиц, 26 - 3 единицы, 13 О единиц. При этом изменяют свои значения входные токи транзисторов 21, 7, 23, 8, 25, 9 и 27, которые становятся соответственно равными 2, 1, 3, О, О, 3 и 1 единицам. ТаКИМ образом, на выходе устройства устанавливается значение входного тока. После окончания переходного процесса можно подать на тактовую шину значение тока 3 единицы, переводя устройство в режим хранения. Таким образом, устройство позволяет хранить необходимое число уровней входного сигнала, при этом возможна дискретизация аналогового непрерывного входного сигнала по уровню и времени. В предлагаемом устройстве не используются переинжектирующие р-области, образующие р - п - р-транзисторы, обладающие электрофизической симметрией. Поэтому изобретение позволяет на 30% и более повысить точность установления (записи) выходные уровней по сравнению с известным устройством. При этом однородность, предлагаемого устройства (так как последнее можно реализовать на идентичных ячейках) упрощает процесс проектирования, изготовления и тестирования устройства, его эксплуатацию.

Фив. 2 «

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Динамический логический элемент | 1979 |

|

SU822370A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Ячейка памяти | 1977 |

|

SU705523A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1985-02-15—Публикация

1982-03-29—Подача