Изобретение относится к вычисли- тельной технике и может быть использовано при построении больших интегральных схем (БИС) обработки информации .

Известен интегральный полусумматор, построенный на элементах, содержащий шесть п-р-п транзисторов и многоколлекторный р-п-р транзистор, коллекторы которого соединены с соответствующими базами п-р-п транзисторов 1 .

Недостатком данного устройства является то, что оно не реализует функцию суммирования трех переменных.

Известен также инжекционный полусумматор, содержащий многоколлекторный р-п-р транзистор, эмиттер которого соединен с шиной питания сумматора, два двухколлекторных транзистора р-п-р типа, эмиттеры которых являются информационными входами сумматора, первые коллекторы объединены с базой первого г-р-п транзистора, а вторые соответственно - с эмиттерами третьего и четвертого р-п-р транзисторов, коллекторы которых соединены с базой четвертого п-р-п транзистора, коллектор последнего соединен с эмиттером шестого р-п-р

транзистора, эмиттер пятого и коллектор первого п-р-п транзисторов объединены, коллекторы пятого и шестого р-п-р транзисторов соединены с базой пятого п-р-п транзистора, коллектор последнего подключен к выходной шине 2.

Недостатком известного сумматора является то, что он не реализует

10 функцию суммирования трех переменных. Для построения полного сумматора необходимо соединить два таких устройства последовательно,что приведет к увеличению площади, занимаемой устройст15вом на кристалле, к увеличению потребляемой мощности и снижению быстродействия.

Цель изобретения - расширение функциональных возможностей устройст20ва за счет возможности суммирования трех переменных.

Эта цель достигается тем, что одноразрядный сумматор, содержащий п-р-п и р-п-р транзисторы, многокол25 лекторные п-р-п транзисторы и много-, коллекторный р-п-р транзистор, эмиттер которого соединен с шиной питания сумматора, а коллекторы,, соответственно, с эмиттерами всех р-п-р транзисторов и базами первого,второго и

третьего многоколлекторных п-р-п тразисторов ,коллекторы первого и второг р-п-р транзисторов соединены с базой первого п-р-п транзистора, а коллекторы третьего и четвертого- транзисторов соединены с базой четвертого многоколлекторного п-р-п транзистора, базы всех р-п-р транзисторов, эмиттер первого п-р-п транзистора, база многоколлекторного р-п-р транзистора и эмиттеры всех миогоколлекторных транзисторов аоединены с шиной нулевого потенциала сумматора, содержит дополнительно второй п-р-п транзистор, база которого соединена .с одним из коллек.торов многоколлекторного р-п-р транзистора и с первыми коллекторами первого, второго и третьего многоколлекторных п-р-п транзисторов, вторые коллекторы этих транзисторов соединены соответственно с эмиттерами первого, второго и пятого р-п-р транзисторов, коллектор пятого -р-п-р транзистора соединен с коллектором второго р-п-р транзистора, коллектор четвертого р-п-р транзистора соединен с коллектором шестого р-п-р транзистора, эмиттер которого соединен с третьими коллекторами первого и второго многоколлекторных п-р-п транзисторов, эмиттер четвертого транзистора соединен с третьим коллектором третьего и четвертым 1соллектором второго многоколлекторных п-р-п транзисторов, четвертые коллекторы первого и третьего многоколлекторных п-р-п транзисторов соединены с эмиттером третьего р-п-р транзистора,коллекторы первого и второго п-р-п транзисторов соединены с выходом суммы сумматора,первый коллетор четвертого многоколлекторного п-р-п транзистора соединен с базой первого транзистора, второй коллектор четвертого многоколлекторного п-р-п транзистора соединен с выходом переноса сумглатора, а входами: сумматора являются базы первого, второго и третьего многоколлекторных п-р-п транзисторов.

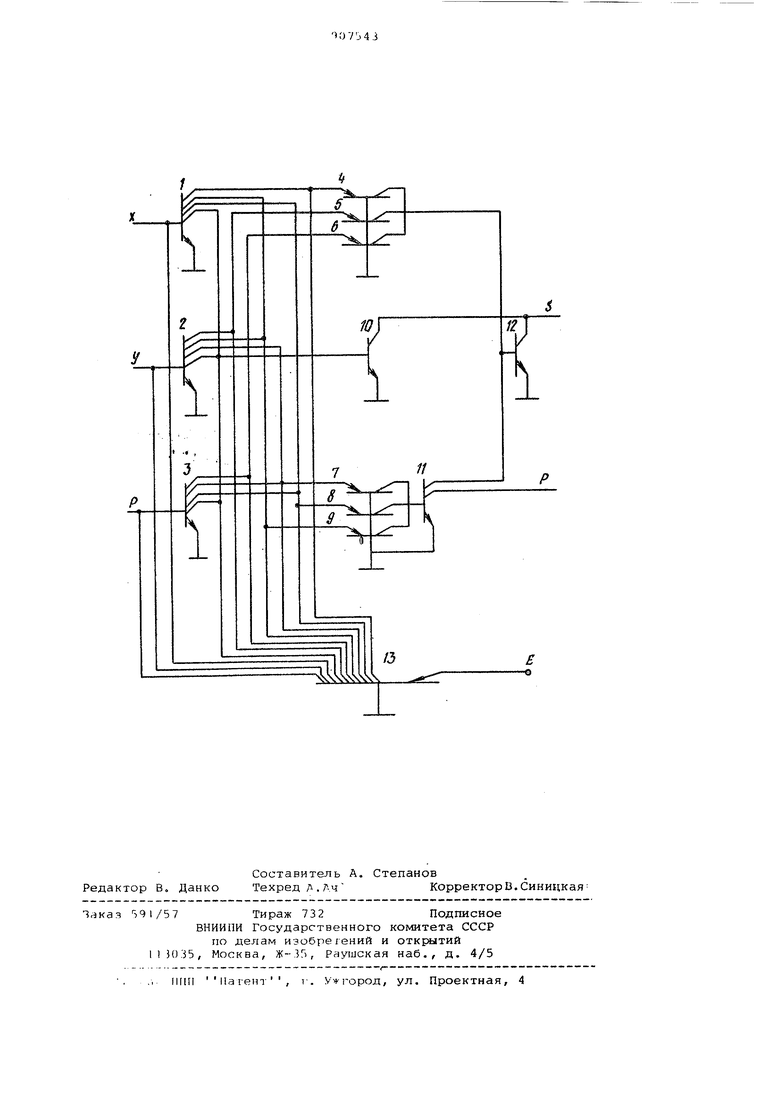

На чертеже представлена электрическая принципиальная схема одноразрядного сумматора.

CyivEviaTop содержит четырехколлекторные п-р-п транзисторы 1-3, р-п-р транзисторы 4-9, п-р-п транзистор 10 двухколлекторный п-р-п транзистор 11 п-р-п транзистор 12, многоколлекторный р-п-р транзистор 13, эмиттером Бсех п-р-п и базой всех р-п-р транзисторов является подложка - п-шина, соединенная с шиной нулевого потенциала .

Входами устройства являются базы транзисторов 1-3, первые коллекторы которых соединены, соответственно, с эмиттерами транзисторов 4-6, приче эмиттерами последних являются переинжектирующие Р-области, а их коллекторами является общая для всех трех транзисторов базовая Р-область-п-ртранзистора 12, вторые коллекторы 1-3 транзисторов соединены с базой транзистора 10, остальные коллекторы транзисторов 1-3 попарно объединены с эмиттерами транзисторов 7,8,9 которыми являются переинжектирующие Р-области, коллектором транзисторов 7-9 является базовая Р-область транзистора 11, коллектор транзистора 10 соединен с коллектором транзистора 12 и выходной шиной суммы, база транзистора 12 соединена с первым коЬектором транзистора 11, второй коллектор которого соединен с шиной переноса, эмиттер транзистора 13 соединен с шиной питания и представляет собой общую для всех транзисторов инжектирующую Р-область, коллекторами транзистора 13 являются базовые Р-области транзисторов 1,2,3 и 10 и эмиттерные Р-области транзисторов. 4-9„

Для пояснения работы устройства предположим, что на входе устройства имеет кодовую комбинацию х 1, , р О, В этом случае часть тока, инжектируемого транзистором 13 в базу транзистора 12, перехватывается транзистором 1, а часть тока через транзисторы 5 и б инжектируется в базу транзистора 12, так как, согласно, схеме, через транзистор 7 ток от инжектирующего транзистора 13 поступае в базу транзистора 11, что приводит его отпиранию, открытый транзистор 1 перехватывает ток, инжектируемый транзисторами 5 и б, в результате чего транзистор 12 закрывается, а так как транзистор 10 также закрыт, то на выходе устройства получаем S 1, р 0.

Если на входе устройства имеем кодовую комбинацию ,, то согласно изложенным рассуждениям, транзистор 10 закрыт, так как инжектируемый транзистором 13 ток перехватывается транзисторами (открытыми) 1 и 3, транзистор 11 закрыт, а ток, инжектируемый транзистором 5 в базу транзистора 12, открывает его, следовательно на выходе сумматора получаем S О , р 1 .

Формула изобретения

Одноразрядный сумматор, содержащий п-р-п и р-п-р транзисторы, многоколлекторные транзисторы и многоколлекторный р-п-р транзистор,эмиттер которого соединен с шиной питания сумматора, а коллекторл, соответственно, с эмиттерами всех р-п-р транзисто.ров и базами первого, второго и третьего многоколлекторных п-р-п транзисторов, коллекторы первого и

второго p-n-p транзисторов соединены с базой первого п-р-п транзистора, а коллекторы третьего и четвертого р-п-р транзисторов соединены с базой четвертого многоколлекторного п-р-п транзистора, базы всех р-п-р транзисторов, эмиттер первого п-р-п транзистора,база многоколлекторного j)-n-p транзистора и эмиттеры всех мнгоколлекторных п-р-п транзисторов соединены с шиной нулевого потенциала сумматора, отличающийс я тем, что, с целью расширения функциональных возможностей за счет возможности суммирования трех переменных , сумматор содержит второй п-р-п транзистор, база которого соединена с одним из коллекторов много коллекторного р-п-р транзистора и с первыми коллекторами первого, второго и третьего многоколлекторных п-р-п транзисторов, вторые коллекторы этих транзисторов соединены соответственно с эмиттерами первого, второго и пятого р-п-р транзисторов, коллектор пятого р-п-р транзистора соединен с коллектором второго р-п-р транзистора, коллектор четвертого р-п-р транзистора соединен с коллектором шестого р-п-р транзистора, эмиттер которого соединен с третьими

коллекторами первого и второго многоколлекторных п-р-п транзисторов, эмиттер четвертого р-п-р транзистора соединен с третьим коллектором третьего и четвертым коллектором второго многоколлекторных п-р-п транзисторов, четвертые коллекторы первого и третьего многоколлекторных п-р-п транзисторов соединены с эмиттером третьего р-п-р транзистора, коллекторы первого и второго п-р-п транoзисторов соединены с выходом суммы сумматора, первый коллектор четвертого многоколлекторного п-р-п транзистора соединен с базой первого п-р-п транзистора, второй коллектор

5 четвертого многоколлекторного п-р-п . транзистора соединен с выходом переноса сумматора, а входами сумматора являются базы первого, второго и третьего многоколлекторных п-р-п

0 транзисторов. I

Источники информации, принятые во внимание при экспертизе

1. 1У1икроэлектроника (Электронная техника . Серия 3.). 1977,

5 № 5.с. 74, рис 4.

2,Авторское свидетельство CCCi по заявке № 2818009/18-24,

кл. G 06 F 7/50, 1979.

| название | год | авторы | номер документа |

|---|---|---|---|

| Одноразрядный комбинационный сумматор | 1981 |

|

SU981995A1 |

| Тактируемый @ -триггер в интегральной инжекционной логике | 1982 |

|

SU1051692A1 |

| Инжекционный динамический элемент | 1980 |

|

SU953731A1 |

| Четырехуровневый одноразрядный сумматор | 1982 |

|

SU1095174A1 |

| Тактируемый @ -триггер @ -типа | 1985 |

|

SU1275738A1 |

| Буферный логический элемент и @ л типа | 1981 |

|

SU980289A1 |

| Четырехразрядный преобразователь двоичного кода в циклический код Грея | 1986 |

|

SU1388993A1 |

| Двоичный сумматор на инжекционных элементах | 1982 |

|

SU1109740A1 |

| Ячейка памяти | 1982 |

|

SU1140165A1 |

| Схема контроля на четность И @ Л-типа | 1988 |

|

SU1525906A1 |

Авторы

Даты

1982-02-23—Публикация

1980-06-12—Подача