113

Изобретение относится к импульсной технике и может быть использовано в устройствах многозначной логики,

Цель изобретения - сокращение площади, занимаемой устройством при реализации на кристалле, уменьшение потребляемой мощности и повышение быстродействия,

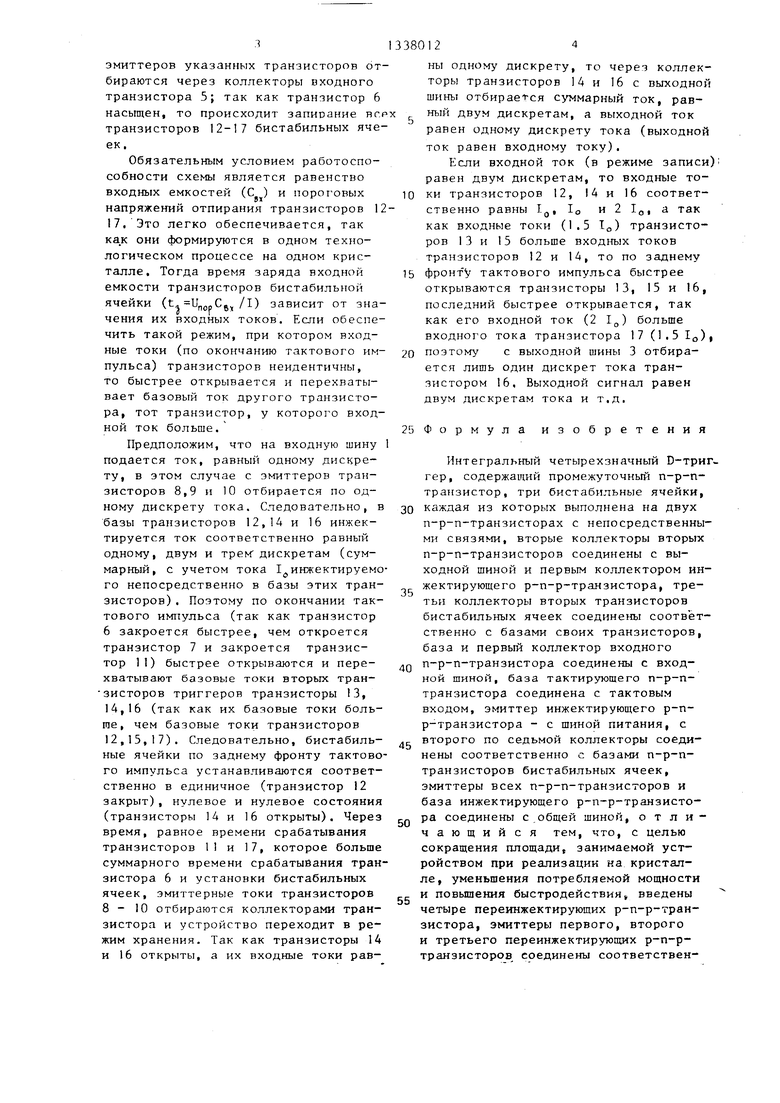

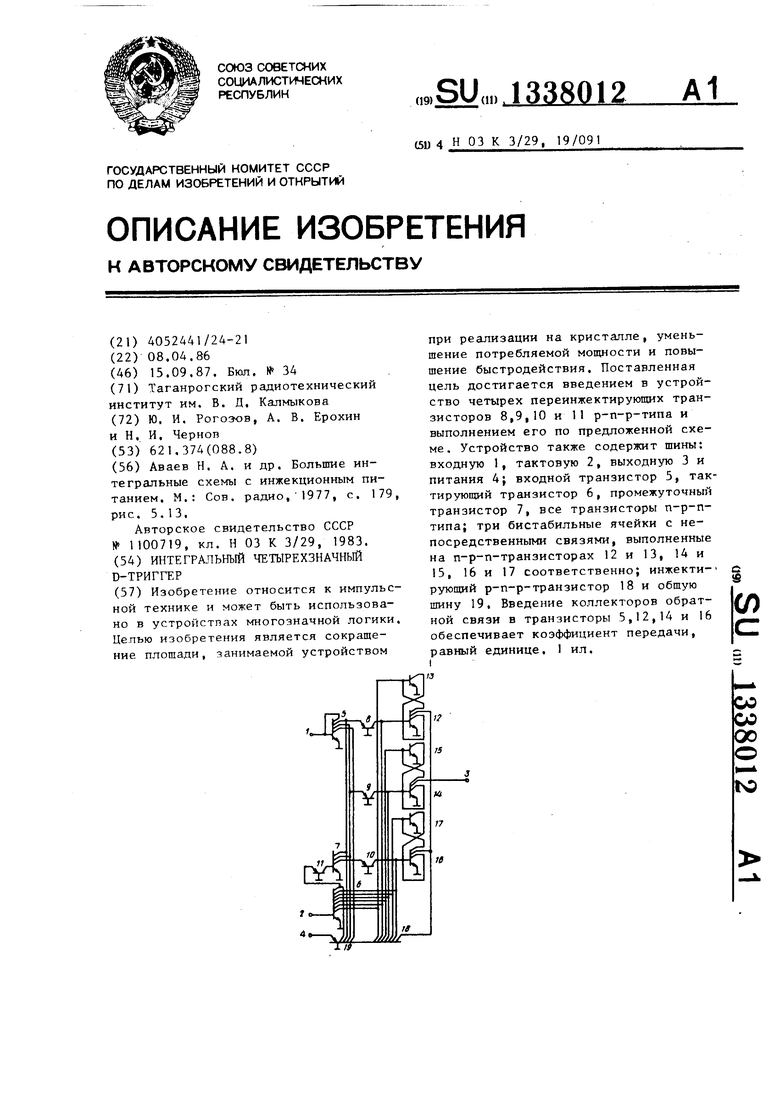

На чертеже приведена принципиальная схема интегрального четырехзначного D-триггера,

Интегральный четырехзначный D-триг гер содержит входную 1, тактовую 2, выходную 3 шины и щину 4 питания, входной п-р-п-транзистор 5, тактирующий п-р-п-транзистор 6, промежуточный п-р-п-транзистор 7, первый 8, второй 9, третий 10 и четвертый 1I переинжектирующие р-п-р-транзисторы, первую, вторую и третью бистабиль- ные ячейки с непосредственными связями, выполненные соответственно на

первых и вторых п-р-п-транзисторах

12 и 13; 14 и 15; 16 и 17; инжектирующий р-п-р-транзистор 18 и общую шину 19,

Шина 1 устройства соединена с базой и первым коллектором транзисто- ра 5, тактовая шина 2 соединена с базой тактирующего транзистора 6, первый коллектор которого соединен с эмиттером транзистора 11, коллектор которого соединен с базой транзисто- ра 7, первый коллектор которого соединен с вторым коллектором транзистора 5 и эмиттером транзистора 8, эмиттер тр анзистора 9 соединен с третьим коллектором транзистора 5 и вто- рым коллектором транзистора 7, третий коллектор которого соединен с четвертым коллектором транзистора 5 и эмиттером транзистора 10, коллектор транзистора 8 соединен с базой и пер- вым коллектором транзистора 12, коллектор транзистора 9 - с базой и первым коллектором транзистора 14, коллектор транзистора 10 - с базой и первым коллектором -транзистора 16, вторые коллекторы транзисторов 12, 14 и 16 объединены с выходной шиной 3, третьи коллекторы транзисторов 12, 14 и 16 соединены соответственно с базами транзисторов 13, 15 и 17, коллекторы транзисторов 13, 15 и 17 соединены соответственно с базами транзисторов 12, 14 и 16, с второго по седьмой коллекторы транзистора

0

5

5

0 5 0 5 0 g

122

6 соединены соответственно с базами транзисторов 12-17, эмиттер инжектирующего транзистора 18 соединен с шиной 4 питания, а соответствующие коллекторы - с эмиттерами переинжектирующих транзисторов 8-11, с базами транзисторов 12-17 и выходной шиной 3, эмиттеры п-р-п-транзисторов 5,6,7,12-16 и базы р-п-р-транзисто- ров 8-11, 18 соединены с общей шиной 19. В эмиттеры транзисторов 8-11 задаются соответственно 1.0, 2.0, 3, 1,0 уровней тока, в базы транзисторов 12,14,16 - по 1.5 уровня тока, в базы транзисторов 13, 15,17 - 1,0 уровень тока, в выходную шину - 3.0 уровня тока.

Значения тока обеспечиваются соотношением геометрических размеров коллекторных и эмиттерных областей р-п-р-транзисторов. Введение коллекторов обратной связи в транзисторы 5.12.14,16 обеспечивает эффективный коэффициент передачи, равный единице.

Триггер работает следующим образом,

В режиме хранения на тактовой шине имеется сигнал низкого логического уровня. В этом случае транзистор 6 закрыт, а транзистор 7 насыщен, последний через свои коллекторы отбирает токи, инжектируемые в эмиттеры транзисторов 8 - 10, Поэтому биста- бильные ячейки находятся в режиме хранения. Предположим, что транзисторы 13, 15, 17 насьпцены, тогда транзисторы 12,14,16 закрыты, следовательно, в выходную шину инжектируется ток, равный трем дискретам. Выходной сигнал хранится до прихода тактового импульса. Изменение входного сигнала не влияет на состояние триггера,

С приходом тактового импульса устройство переходит в режим записи.

Подача на транзистор 6 сигнала высокого логического уровня приводит к его отпиранию.

С отпиранием транзистора 6 через время задержки, равное времени срабатывания транзисторов 11 и 7 (транзистор 11 здесь выполняет функцию элемента задержки, назначение которого будет пояснено ниже), происходит запирание транзистора 7, который уже не отбирает с эмиттеров транзисторов 8,9,10 токи, токи с

эмиттеров указанных транзисторов отбираются через коллекторы входного транзистора 5; так как транзистор 6 насыщен, то происходит запирание ВГ.Р транзисторов 12-17 бистабильных ячеек ,

Обязательным условием работоспособности схемы является равенство входных емкостей (С ) и пороговых

X

напряжений отпирания транзисторов 12 17, Это легко обеспечивается, так ка.к они формируются в одном технологическом процессе на одном кристалле. Тогда время заряда входной емкости транзисторов бистабильной ячейки (t,) зависит от значения их входных токов. Если обеспечить такой режим, при котором входные токи (по окончанию тактового импульса) транзисторов неидентичны, то быстрее открывается и перехватывает базовый ток другого транзистора, тот транзистор, у которого входной ток больше.

Предположим, что на входную шину подается ток, равный одному дискрету, в этом случае с эмиттеров транзисторов 8,9 и 10 отбирается по одному дискрету тока. Следовательно, в базы транзисторов 12,14 и 16 инжектируется ток соответственно равный одному, двум и трем дискретам (суммарный, с учетом тока 1 инжектируемого непосредственно в базы этих транзисторов) , Поэтому по окончании тактового импульса (так как транзистор 6 закроется быстрее, чем откроется транзистор 7 и закроется транзистор 11) быстрее открываются и перехватывают базовые токи вторых тран- зисторов триггеров транзисторы 13, 14,16 (так как их базовые токи боль- гае, чем базовые токи транзисторов 12,15,17). Следовательно, бистабиль- ные ячейки по заднему фронту тактового импульса устанавливаются соответственно в единичное (транзистор 12 закрыт), нулевое и нулевое состояния (транзисторы 14 и 16 открыты). Через время, равное времени срабатывания транзисторов 1 и 17, которое больше суммарного времени срабатывания транзистора 6 и установки бистабильных ячеек, эмиттерные токи транзисторов 8 - 10 отбираются коллекторами транзистора и устройство переходит в режим хранения. Так как транзисторы 14 и 16 открыты, а их входные токи рав

ны одному дискрету, то через коллекторы транзисторов 14 и 16 с выходной шины отбирается суммарный ток, равный двум дискретам, а выходной ток равен одному дискрету тока (выходной ток равен входному току),

Если входной ток (в режиме записи)i равен двум дискретам, то входные токи транзисторов 12, 14 и 16 соответственно равны Ig, TO и 2 Ig, а так как входные токи (1.5 IQ) транзисторов 13 и 15 больше входных токов транзисторов 12 и 14, то по заднему

фронт у тактового импульса быстрее открываются транзисторы 13, 15 и 16, последний быстрее открывается, так как его входной ток (2 I,) больше входного тока транзистора 17 (l.SIo),

поэтому с выходной шины 3 отбирается лишь один дискрет тока транзистором 16, Выходной сигнал равен двум дискретам тока и т,д.

Формула изобретения

Интегральный четырехзначный D-триг- гер, содержащий промежуточный п-р-п- транзистор, три бистабильные ячейки, каждая из которых выполнена на двух п-р-п-транзисторах с непосредственными связями, вторые коллекторы вторых п-р-п-транзисторов соединены с выходной шиной и первым коллектором инжектирующего р-п-р-транзистора, третьи коллекторы вторых транзисторов бистабильных ячеек соединены соответственно с базами своих транзисторов, база и первый коллектор входного п-р-п-транзистора соединены с входной шиной, база тактирующего п-р-п- транзистора соединена с тактовым входом, эмиттер инжектирующего р-п- р-транзистора - с шиной питания, с второго по седьмой коллекторы соединены соответственно с базами п-р-п- транзисторов бистабильных ячеек, эмиттеры всех п-р-п-транзисторов и база инжектирующего р-п-р-транзистора соединены с общей шиной, отличающийся тем, что, с целью сокращения площади, занимаемой устройством при реализации на кристалле, уменьшения потребляемой мощности и повышения быстродействии, введены четыре переинжектирующих р-п-р-транзистора, эмиттеры первого, второго и третьего переинжектирующих р-п-р- транзисторов соединены соответствен0

5

0

5

0

5

но с вторым, третьим и четвертым коллекторами входного п-р-п-транзнсто- ра, соответственно с первым, вторым и третьим коллекторами промежуточного п-р-п-транзистора и восьмым, девятым и десятым -коллекторами р-п- р-инжектирующего транзистора, а эмиттер четвертого переинжектирующего р-п-р-транзистора - с первым колСоставитель А. Янов Редактор Н. Киштулинец Техред В.Кадар

Заказ 4142/53Тираж 901Подписное

ВНИИПН Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

лектором тактирующего п-р-п-транзистора и одиннадцатым коллектором инжектирующего р п-р-транзистора, коллекторы первого, второго, третьего и четвертого переинжектирующего р-п-р-транзистора соединены соответственно с базами вторых п-р-п-тран- зисторов бистабильньгх ячеек и промежуточного п-р-п-транчистора.

Корректор Л. Беекид

| название | год | авторы | номер документа |

|---|---|---|---|

| Тактируемый @ -триггер @ -типа | 1985 |

|

SU1275738A1 |

| Схема контроля на четность И @ Л типа | 1985 |

|

SU1269253A1 |

| Четырехразрядный преобразователь двоичного кода в циклический код Грея | 1986 |

|

SU1388993A1 |

| Ячейка памяти | 1982 |

|

SU1140165A1 |

| Двоичный делитель частоты @ типа | 1983 |

|

SU1112533A1 |

| Инжекционный динамический элемент | 1981 |

|

SU1005314A2 |

| Инжекционный динамический элемент | 1980 |

|

SU953731A1 |

| Тактируемый JK-триггер И @ Л-типа | 1987 |

|

SU1422367A1 |

| Четырехуровневый триггер | 1982 |

|

SU1056268A1 |

| Тактируемый @ -триггер в интегральной инжекционной логике | 1982 |

|

SU1051692A1 |

Изобретение относится к импульсной технике и может быть использовано в устройствах многозначной логики. Целью изобретения является сокращение площади, занимаемой устройством при реализации на кристалле, уменьшение потребляемой мощности и повышение быстродействия. Поставленная цель достигается введением в устройство четырех переинжектирующих транзисторов 8,9,10 и 11 р-п-р-типа и выполнением его по предложенной схеме. Устройство также содержит шины: входную 1, тактовую 2, выходную 3 и питания 4; входной транзистор 5, тактирующий транзистор 6, промежуточный транзистор 7, все транзисторы п-р-п- типа; три бистабильные ячейки с непосредственными связями, выполненные на п-р-п-транзисторах 12 и 13, 14 и 15, 16 и 17 соответственно; инжекти- рующий р-п-р-транзистор 18 и общую шину 19, Введение коллекторов обратной связи в транзисторы 5,12,14 и 16 обеспечивает коэффициент передачи, равный единице. 1 ил. (Л оо со 00 Ю

| Аваев Н | |||

| А | |||

| и др | |||

| Большие интегральные схемы с инжекционным питанием | |||

| М.: Сов | |||

| радио, 1977, с | |||

| Вагонетка для движения по одной колее в обоих направлениях | 1920 |

|

SU179A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Интегральный четырехзначный @ -триггер | 1983 |

|

SU1100719A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1987-09-15—Публикация

1986-04-08—Подача