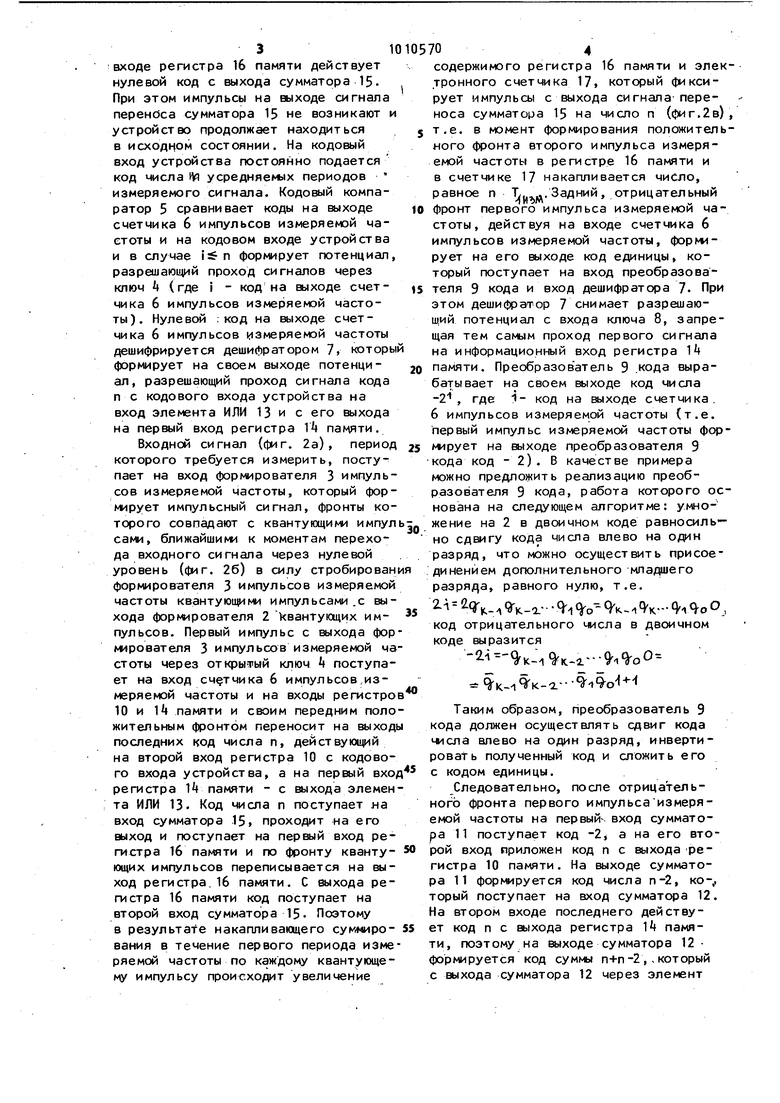

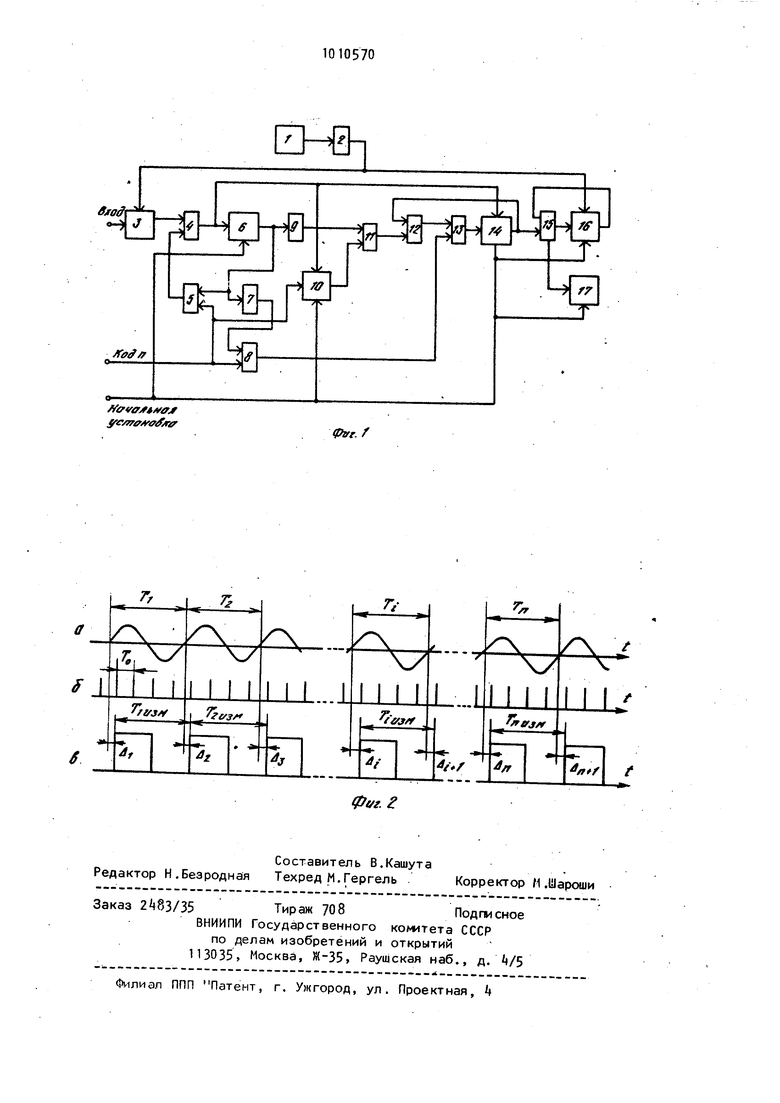

Изобретение относится к цифровой измерительной технике. . Известен цифровой частотомер, содержащий опорный генератор, формирователь квантующих импульсов, формирователь импульсов измеряемой част ты, счетчик импульсов измеряемой частоты, ключ, электронный счетчик Недостаток известного устройства состоит в невысокой точности. Наиболее близким по технической сущности к предлагаемому является устройство, содержащее последователь но соединенные генератор опорной ча стоты, формирователь импульсов, первый ключ, электронный счетчик, второй ключ и сумматор, третий ключ, а также последовательно соединенные формирователь импульсов измеряемой частоты, счетчик, выход которого сое динен с вторым входом первого ключа, выход формирователя импульсов измеряемой частоты связан с вторыми входами второго и третьего ключа, второ выход электронного счетчика подключен к первому входу третьего ключа, выход последнего соединен с вторым входом сумматора, второй выход счетчика подключен к третьим входам второго и третьего ключа 2. Однако такое устройство характери зуется низкой точностью измерения, и недостаточной надежностью, обусловленной синхронизацией процесса суммирования импульсами измеряемой частоты. Цель изобретения - повышение точности измерения и повышение надежности работы. Поставленная цель достигается тем что в цифровой измеритель длительно сти периода, содержащий последовател но соединенные опорной генератор и фор 4 ро ват ел ь квантующих импульсов, первый сумматор, электронный счетчик последовательно соединенные формиро ватель импульсов измеряемой частоты и первь1й ключ, второй ключ, а также счетчик импульсов измеряемой частоты, введены преобразователь кода, кодовый компаратор, дешифратор, пер вый регистр памяти, а также последо вательно соединенные второй сумматор элемент ИЛИ, второй регистр памяти, третий сумматор и третий регистр па мяти, выход которого соединен с вто рым входом третьего сумматора, второй выход последнего подключен к вхо ду электронного счетчика, выход второго регистра памяти соединен с первым входом второго сумматора, второй вход которого подключен к выходу первого сумматора, первый вход которого соединен с выходом преобразователя кода, вход последнего подключен к первому входу кодового компаратора, входу дешифратора и выходу счетчика импульсов измеряемой частоты, вход последнего соединен с первым входом первого и с вторым входом второго регистров памяти и выходом первого ключа, второй вход которого подключен к выходу кодового компаратора, второй вход последнего соединен с вторым входом первого регистра памяти и первым входом второго ключа, второй вход которого подключен к выходу дешифратора, выход второго ключа связан с вторым входом элемента ИЛИ, выход формирователя квантующих импульсов подключен к первому входу формирователя импульсов измеряемой частоты и второму входу третьего регистра, выход первого регистра памяти соединен с вторым входом первого сумматора. На фиг. 1 представлена структурная схема устройства; на фиг. 2 временные диаграммы, поясняющие работу цифровбго измерителя длительности периода. Устройство содержит опорный генератор 1, формирователи 2 и 3 квантующих импульсов и импульсов измеряемой частоты соответственно, первый ключ (, кодовый компаратор 5, счетчик 6 импульсов измеряемой частоты, дешифратор 7 второй ключ 8, преобразователь 9 кода, первый регистр 10 памяти, первый 11 и второй 12 сумт маторы, элемент ИЛИ 13, второй регистр Т памяти, третий сумматор 15f третий регистр 16 памяти, электронный счетчик 17. Цифровой измеритель длительности периода работает следующим образом. Перед началом цикла измерения счетчик 6 импульсов измеряемой частоты, регистры 10, 1 и 16 памяти и электронный счетчик 17 установлены в нулевое состояние сигналом начальной установки. Следовательно на выходах сумматоров 11, 12 и 15 действуют коды нулей . Квантующие импульсы поступают на второй вход регистра 1б памяти, но не изменяют состояния последнего, так как на первом входе регистра 16 памяти действует нулевой код с выхода сумматора 15. При этом импульсы на выходе сигнала переноса сумматора 15 не возникают и устройство продолжает находиться в исходном состоянии. На кодовый вход устройства постоянно подается код числа 11й усредняемых периодов измеряемого сигнала. Кодоа |й компаратор 5 сравнивает коды на выходе счетчика 6 импульсов измеряемой частоты и на кодовом входе устройства и в случае п формирует потенциал, разрешающий проход сигналов через ключ Ц (где i - код на выходе счетчика 6 импульсов измеряемой частоты). Нулевой : код на а 1ходе счетчика 6 импульсов измеряемой частоты дешифрируется дешифратором 7, которы формирует на своем выходе потенциал, разрешающий проход сигнала кода ПС кодового входа устройства на вход элемента ИЛИ 13 и с его выхода на первый вход регистра 1 . Входной сигнал (({яг. 2а), период которого требуется измерить, поступает на вход формирователя 3 импульсов измеряемой частоты, который формирует импульсный сигнал, фронты которого совпадают с квантующими импул сами, ближайшими к моментам перехода входного сигнала через нулевой уровень (фиг. 26) в силу стробирован формирователя 3 импульсов измеряемой частоты квантующими импульсами.с выхода формирователя 2 Квантующих импульсов. Первый импульс с выхода фор мирователя 3 импульсов измеряемой ча стоты через открыгый ключ t поступает на вход счетчика 6 импульсов измеряемой частоты и на входы регистро 10 и Т памяти и своим передним поло жительным фронтом переносит на выход последних код числа п, действующий на второй вход регистра 10 с кодового входа устройства, а на первый вхо регистра 1 памяти - с выхода элемен та ИЛИ 13. Код числа п поступает яа вход сумматора 15, проходит на его выход и поступает на первый вход регистра 16 памчти и по фронту квантующих импульсов переписывается на выход регистра. 16 памяти. С выхода регмстра 16 памяти код поступает на второй вход сумматора 15. Поэтому в результате накапливающего суммирования в течение первого периода изме ряемой частоты по каждому квантующему импульсу происходит увеличение содержимого регистра 16 памяти и электронного счетчика 17, который фиксирует импульсы с выхода сигнала переноса сумматора 15 на число п (фиг.2в), т.е. в момент формирования положительного (йронта второго импульса измеряемой частоты в регистре 16 памяти и в счетчике 17 накапливается число, равное п Г, л. Задний, отрицательный фронт первого импульса измеряемой частоты, действуя на входе счетчика 6 импульсов измеряемой частоты, формирует на его выходе код единицы, который поступает на вход преобразователя 9 кода и вход дешифратс за 7. При этом дешифратор 7 снимает разрешающий потенциал с входа ключа 8, запрещая тем самым проход первого сигнала на информационный вход регистра Tt памяти. Преобразователь 9 .кода вырабатывает на своем выходе код числа -2 , где 1- код на выходе счетчика. 6 импульсов измеряемой частоты (т.е. первый импульс измеряемой частоты формирует на выходе преобразователя 9 кода код - 2) . В качестве примера можно предложить реализацию преобразователя 9 кода, работа которого основана на следующем алгоритме: у.множение на 2 в двоичном коде равносильно сдвигу кода числа влево на один разряд, что можно осуществить присоединением дополнительного мпадаего разряда, равного нулю, т.е. 2.П . .- % (о 9к--1 «VK-«V-t «}о О , код отрицательного числа в двоичном коде выразится .- oO- %ic-i9K-a---3i o Таким образом, преобразователь 9 кода должен осуществлять сдвиг кода числа влево на один разряд, инвертировать полученный код и сложить его кодом единицы. с Следовательно, после отрицательного фронта первого импульсаизмеряемой частоты на первый- вход сумматора 11 поступает код -2, а на его второй вход приложен код п с выхода регистра 10 памяти. На выходе сумматоа 11 фор(руется код числа л-2, коорый поступает на вход сумматора 12. а втором входе последнего действут код п с выхода регистра Tt памяи, поэтому на выходе сумматора 12ормируется код суммы п+п-2,, который с выхода сумматора 12 через элемент ИЛИ 13 прикладывается к первому ду регистра 1 памяти. Положительный фронт второго импульса измеряемой частоты переписывает код п+п-2 2п-2 с первого входа регистра 1 памяти на его выход и, следовательно, на вход сумматора 15. По каждому квантующему импульсу содержимое регистра 16 памяти и электронного счетчика 17 увеличивается на 2п-2 в течение второго периода импульсов измеряемой частоты. Кроме того, передний фронт второго импульса Измеряемой частоты подтверждает код на выходе регистра 10 памяти и-переводит счетчик 6 импульсов измеряемой чистоты в состояПреобразователь кода формирует на своем выходе код числа -t, который, поступая на вход сумматора 1, суммируется с кодом п, действующим на выходе регистра 10 памяти, формируя на выходе сумматора 11, и, следовательно, на входе сумматора 12 код суммы п-4. Сумматор 12 осуществляет суммирование кода п-4 с кодом 2п-2, поступающим на его второй вход с выхода регистра k памяти и, форми рует на своем выходе код Зп-6, который через элемент ИЛИ 13 поступает на первый вход регистра 14 памяти. Положительный фронт третьего импульса измеряемой частоты переписывает код Зп-6 на выход регистра 14 памяти, обеспечивая тем самым накапливающее суммирование числа Зп-6 по каждому квантующему импульсу в сумматоре 15, регистре 1б памяти и электронном счет чике 17 а отрицательный фронт третье го импульса измеряемой частоты форми рует на информационном входе регистра 14 памяти код числа 4п-12, Регист ры 10, 14 и 1б памяти построены таким образом, что на их выходы перепи сывается код, который присутствует на первых входах в момент действия положительного фронта сигнала на вхо дах синхронизации, и не реагируют на р зменения сигналов на информационных входах в течение длительности импуль lea на входе синхронизации. Для 1-ого периода измеряемой частоты можно написать выражение для

в -ДУ|л-СУ -2.))

I ср ;

V ()yц-l)

При условии статистической независимости погрешностей Д дисперсия погрешности измерения ДТ.р

)И

2: см-гм)

Ъ6

Р Ib()(m iXmx)/ ода числа на выходе регистра 15 паят и следующим образом. Q.-.iCVl-lXi-l) ::. Ill .1 (i-i)-i() (l) i-i Из выражения (1 следует, что (n+ + 1) -vt импульс измеряемой частоты форN dpyeT на выходе регистра 14 памяти код нуля . Одновременно (п+1)-и импульс измеряемой частоты устанавливает на выходе счетчика 6 импульсов измеряемой частоты, а следовательно, на втором входе кодового компаратора кода п+1, который превышает код числа п, приложенного к первому входу кодового компаратора 5. Поэтому последний формирует потенциал, запрещающий проход сигналов через ключ 4. При этом в регистре 1б памяти и электронном счетчике 17 фиксируется смело Т, пропорциональное периоду исследуемого сигнала ,M | nM-i+),,,,. При этом устройство продолжает сохранять накопленный результат, так как на входе сумматора 15 действует код нуля с выхода регистра 14 памяг ти, а ключ 4 закрыт потенциалом с выхода кодового компаратора 5. Си1- нал начальной установки переводит в нулевое состояние регистры 10, 14 и 1б памяти, электронный счетчик 17 , и счетчик 6 импульсов измеряемой частоты. При этом открывается ключ 4,и начинается новый цикл измерения. Оценку среднего из п периодов исследуемого сигнала производят следующим образом: . ЬТх сР и, .SliCM-i+i) vi((Xvi+2l Погрешность измерения одного периода Ij, и среднего из п периодов измеряемого сигнала 1 1И%м- л - 1- а iToL - -7.+ + 14-1 2. -Г) гдеСУд -fi - дисперсия Погрешности 0 кретности измерения од го периода исследуемог сигнала. Аналогично можно показать, что дисперсия ошибки измерения, обусло ленная аддитивным шумом во входном сигнале, выразится OTmUT, Р %4hViHv Vi где б ... - дисперсия шумовой ошибки измерении одного периода исследуемого сигнала . А11, г,. где Т, время корреляции случайно процесса. В устройстве-прототипе число, н капливаемое в сумматоре, определяет выражением (..,,,, .f поэтому длительность среднего из п периодов равна ц(г-ч. tyx . i + tl b-i Следовательно, среднеквадратичес кая погрешность измерения определит ся выражением г- { т AGcrfn .p)r гдеСГд Тр/12 - среднеквадратическая погрешност ь дискрет ности при квантовани одного периода измер емого сигнала. Для сравнения точности измерения 1г1звес(5ного и предлагаемого устройств найдем отношение выражений (3 и(Ь ) , ) Bg CV A Mvi+z) Т.е. точность измерения увели1 1вается в 1, раза. Благодаря тому, что фронты импульсов измеряемой частоты привязаны к квантующим импульсам,процессы накапливающего суммирования в сумматорах 11, 12 и 15 синхронизированы, что выгодно отличает предлагаемое устройство от известного, так как исключаются грубые сбои в работе устройства при совпадении во времени фронтов импульсов измеряемой частоты и квантующих импульсов. Таким образом, введение новых элементов и связей между ними позволяет повысить точность измерения и на/ ежность работы устройства. При построении макета устройства использовались микросхема серий 521, 133, 130. Макет испытывался при измерении периода сигнала частоты f, 10 кГц с выхода частотного компаратора и времени измерения17 1 с (п 10000) . Для сравнения этот же сигнал-измерялся с помощью серийно выпускаемого частотомера . Суммарная погрешность измерения погрешность дискретности и шумовая погрешность) при использовании серийного прибора, использующего классический алгоритм измерения, оказалась в 20 раз больше погрешности, показанной макетом предлагаемого устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой измеритель длительности периода | 1980 |

|

SU920556A1 |

| Цифровой фазометр | 1980 |

|

SU892343A1 |

| Цифровой частотомер | 1983 |

|

SU1167519A1 |

| Цифровой измеритель длительности периода | 1988 |

|

SU1582176A1 |

| Цифровой измеритель длительности периода | 1981 |

|

SU1004955A1 |

| Способ измерения частоты | 1987 |

|

SU1613968A1 |

| Устройство для измерения сдвига фаз | 1986 |

|

SU1381406A1 |

| Устройство для измерения разности периодов двух электрических сигналов | 1985 |

|

SU1285395A1 |

| Умножитель частоты | 1988 |

|

SU1608779A1 |

| Измеритель длительности временных интервалов | 1980 |

|

SU949625A1 |

1 1ФРОВОЙ ИЗМЕРИТЕЛЬ ДЛИТЕЛЬНОСТИ ПЕРИОДА, содержащий последовательно соединенные опорный генератор и формирователь квантукщих импульсов, первый сумматор, электронный счетчик, последовательно соединенные формирователь импульсов измеряемой частоты и первый ключ, второй ключ, а также счетчик импульсов измеряемой частоты, отличающий ся тем, что, с целью.повышения точности и надежности измерений, в него введе1 Г преобразователь кода, кодовый компаратор, дешифратор, первый регистр памяти, а также последовательно соединенные второй сумматор, элемент ИЛИ, второй регистр памяти, третий сумматор и третий регистр памяти, выход которого соединен с вторым входом третьего сумматора, второй выход последнего подключен к входу электронного счетчика, выход второго регистра памяти соединен с первым входом второго сумматора, второй вход которого подключен к выходу первого сумматора, первый вход которого соединен с выходом преобразовател кода, вход последнего подк;)ючен к первому входу кодового компаратора, входу дешифратора и выходу счетчика импульсов измеряемой частоты, вход последнего соединен с первым входом первого и с вторым входом второго регистров памяти и ЕЫХОдом первого ключа, второй вход которого подключен к выходу кодового комО) паратора, второй вход последнего соединен с вторым входом первого регистр а. памяти и первым входом второго ключа, второй вход которого подключён к выходу дешифратора, выход второго ключа Соединен с вторым входов элемента ИЛИ, выход формирователя кванту юи91х импульсов подключен к первому ;входу формирователя импульсов измеря;емой частоты и к второму входу треСП ,.тьего регистра, выход первого регистvj ра памяти соединен с вторым входом первого сумматора.

ffVff t ff

yc/Tfff ffArff

руг. f

Авторы

Даты

1983-04-07—Публикация

1981-12-23—Подача