fO

.-20

25

11285395

Изобретение относится к измериельной технике и может быть испольовано при построении прецизионных змерителей частоты и устройств для сравнения шкал времени.

Цель изобретения - повышение точости измерения разности.периодов.

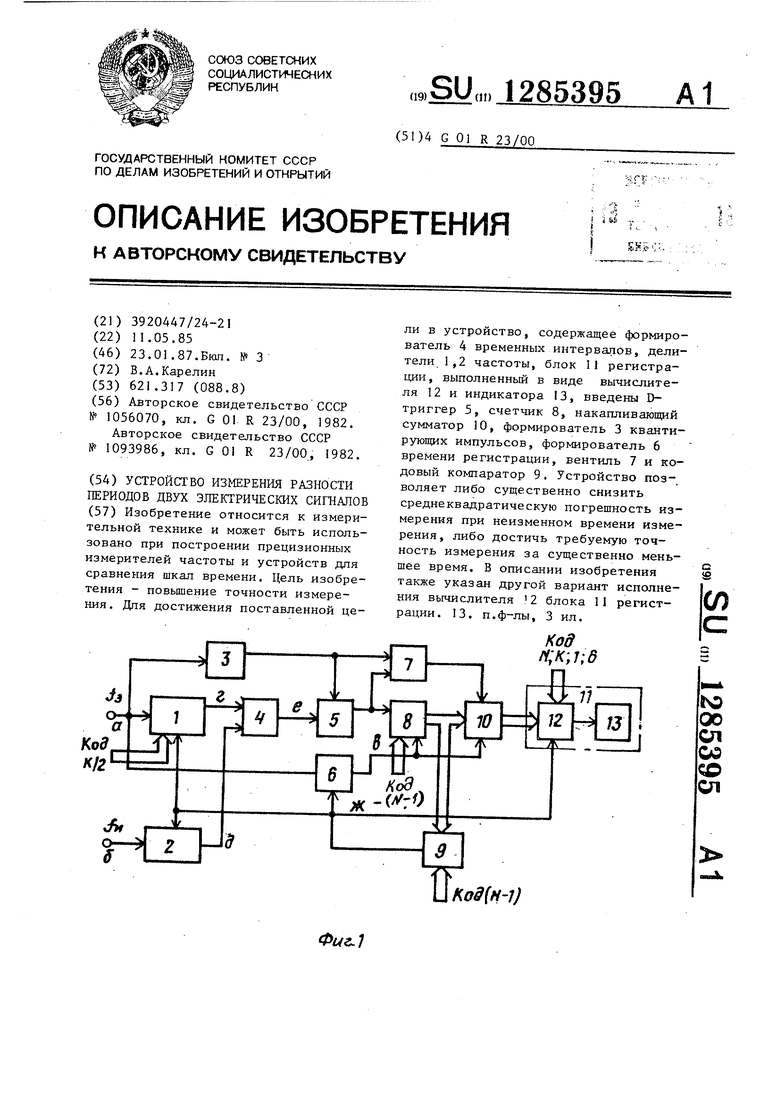

На фиг.1 представлена блок-схема стройства; на фиг.2 - временные .диаграммы; на фиг. 3 - блок-схема выислителя.

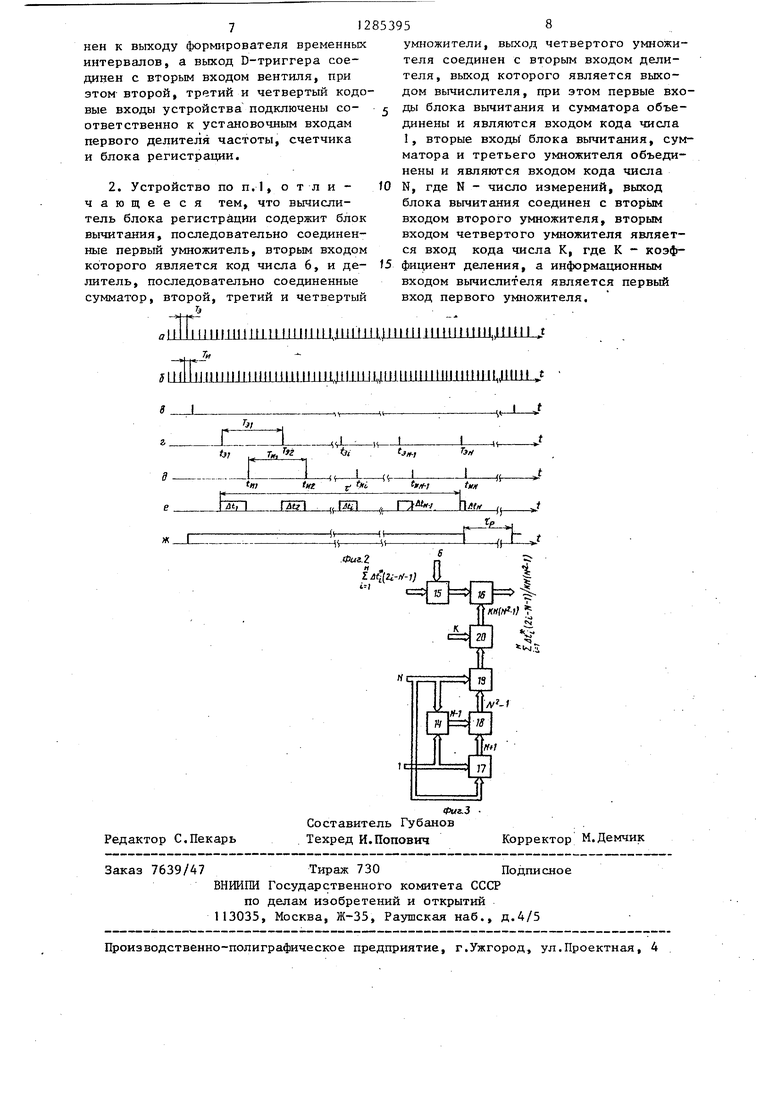

Устройство (фиг.) содержит первый и второй делители 1 и 2 частоты, ормирователь 3 квантующих импульсов, ормирователь 4 временных интервалов, -триггер 5, формирователь 6 времени регистрации, вентиль 7, счетчик 8, кодовый компаратор 9, накапливающий сумматор 10, блок 11 регистрации,выполненный в виде последовательно сое диненных вычислителя V2 и индикатора 13.

ходы эталонной и измеряемой частот соответственно через пе.рвЫй и второй деители 1 и 2 частоты соединены с входами ормирователя 4 временных интервалов, Выход формирова теля 4 временных интервалов через последовательно соединенные D-триггер 5у:Счетчик 8 и накапливащий сумматор 10 соединен с информационным входом блока 11 регистрации, установочный вход которого подключен к чет- вертбму кодовому входу устройства. Пер-. вый кодовый вход устройства соединен с вторым входом кодового компаратора 91, первый вход которого подключен к вы- ходу счетчика 8, а выход соединен с управляющим входом первого и второго делителей 1 и 2 частоты, формирователя 6 времени регистрации и блока 11 регистрации. Сигнальный вход формирователя 6 времени регист- - рации подсоединен к входу первого делителя 1 частоты и к входу формирователя 3 квантующих импульсов, а выход соединен с входом синхронизации записи счетчика 8 и входом начальной установки накапливающего сумматора 10, Вход синхронизации накапливающего сумматора 10 соединен с выходом вентиля 7, первьй вход которого соединен с выходом формирователя 3 квантующих импульсов и с входом синхронизации D-триггер а 5,° а второй вход соединен с выходом D- триггера 5. Второй и третий кодовые входы устройства соединены соответственно с установочными входами дели.х и

Ю

35

40

45

50

55

fO

20

25

85395

, ,

. - 2

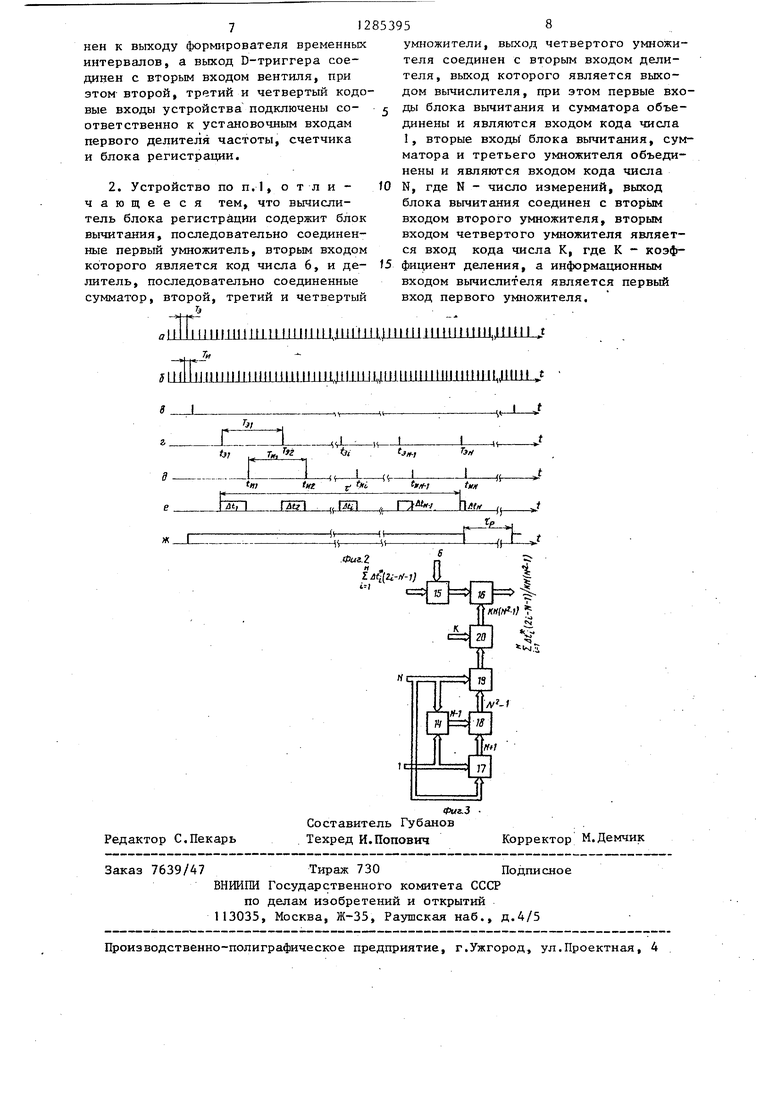

теля 1 частоты и блока 11 регистрации. Вычислитель 12 блока 11 регистрации содержит (фиг.З) блок 14 вычитания, последовательно соединенные первый умножитель 15, вторым входом которого является вход кода 6, и делитель 16, последовательно соединенные сумматор 17, второй 18,третий 19 и четвертый 20 умножители. Выход четвертого умножителя 20 соединен с вторым входом делителя 16, вы- .ход которого является выходом вычислителя , при этом первые входы блока 14 вычитания и сумматора 17 объеди- иены и являются входом кода 1.Вторые входы блока 14 вычитания, сумматора 17 и третьего умножителя 19 объединены и являются входом кода N. Выход блока 14 вычитания соединён с вторым входом второго умножителя 18. Вторым входом четвертого умножителя является вход кода К. Информационным входом вычислителя является первый вход первого умножителя 15.

Устройство работает следующим образом.

В исходном состоянии на второй вход кодового компаратора 9 и установочные входы делителя 1 частоты и счетчика 8 подаются соответственно кодь чисел: (N-1); К/2; - (N-1). На выходе счетчика 8 установлен код (N-1), который подается на первый вход кодового компаратора 9. Совпадение кодов на первом и втором входах кодового компаратора 9 формирует на выходе последнего потенциал нулевого уровня (фиг.2,ж), который, поступая на управляющие входы делителей 1 и 2 частоты, устанавливает и удерживает их соответственно в состояниях к/2 и О. При этом импульсы эталонной fg и измеряемой

Ю

35

40

45

50

г, частот, поступая на соответствующие делители 1 и 2 частоты, не изменяют их состояний и импульсы с периодами следования Т и Тщ не посту-

55

пают на входы формирователя 4 временных интервалов. На выходе формирователя 4 временных интервалов сохраняется потенциал нулевого уровня, который через D-триггер 5, синхронизи- руемьй квантующими импульсами, поступает на второй вход вентиля 7, запрещая тем самым проход квантующих импульсов на вход синхронизации накапливающего сумматора 10. Через временной интервал fp (фиг. 2,ж) , формируемый формирователем 6 времени регистрации, на выходе последнего вы- рабатьшается импульс (фиг.2,в), который обнуляет память накапливающего сумматора 10 и переписывает код - (N-1) входа установки счетчика 8 на его выход. При этом равенство кодов на входах кодового компаратора 9 нарушается и на его выходе формируется потенциал единичного уровня (фиг. 2,ж), разрешающий работу делителей 1 и 2 частоты. Делители 1 и 2 частоты осуществляют деление импульсов f и и с коэффициентом пересчета

К, формируя на своих выходах импуль- 15 на входе синхронизации накапливаюсь с периодом следования соответственно Т

Э1

- КТз , Т J

KTj, (фиг.2,

щего сумматора 10 в течение интервала времени At(i 1,2,...,N). Следовательно, после окончания i-ro импульса At в накапливающем суммато

г,д). При этом временной интервал лt между первыми импульсами на выходе первого и второго делителей 1 20 ре 10 фиксируется код числа а|, рав- и 2 частоты примерно равен Т, ного

так как первый делитель 1 частоты начинает работать, находясь в состоянии к/2, а второй делитель 2 частоты - находясь в состоя U

25

а; tl (2J-N-1), (1)

J-i

при i N, т.е. на момент окбнчанияг времени измерения Т. ,

НИИ О

КТ + КйТ

Импульсы Т КТ

при i N, т.е. на момент окбнчания времени измерения Т. ,

к

а„ 7 At(2i-N-l). (2) Ul

(фиг.2,г,д) d

выхрдов соответственно первого делителя 1 частоты и второго де- ЗО лителя 2 частоты поступают на входы формирователя 4 временных интервалов, на выходе которого вырабатывается импульс единичного уровня длительностью ut: At, + КАТ (i-1). эс/, , ч

, ,., „ . -э- потенциал (фиг.А,ж), устанавливаю- где 1 1,2,... ,N. Импульсы At пос- „ х-±- /

После окончания импульса At на выходе счетчика 8 формируется код, равный (N-1), который, поступая на первый вход кодового коммутатора 9, устанавливает на его выходе нулевой

тупают на информационный вход D-триг- гера 5, на выходе которого вырабатываются импульсы Atj . фронты импульсов At формируются ближайшими к фронтам At квантующими импульсами благодаря синхронизации

D-триггера 5 сигналами с выхода формирователя 3 квантующих импульсов.

40

щий и удерживающий делители I и 2 . частоты соответственно в состояниях к/2 и О, разрешающий работу формирователя 6 времени регистрации и переписывающий в блок 11 регистрации код числа ац с выхода накапливающего сумматора 10. В блоке 11 регистрации осуществляется умножение в вычислителе 12 в соответствии с

щий и удерживающий делители I и 2 . частоты соответственно в состояниях к/2 и О, разрешающий работу формирователя 6 времени регистрации и переписывающий в блок 11 регистрации код числа ац с выхода накапливающего сумматора 10. В блоке 11 регистрации осуществляется умножение в вычислителе 12 в соответствии с

Такое формирование At, позволяет 45 ТV

- его структурной схемой (фиг.З) чиссинхронизировать работу накапливаю-vsyni.j/

Щего сумматора 10 и счетчика 8, на счетный вход которого подаются имла а,. на нормализующий коэффициент 6KN(), код которого поступает с четвертого кодового входа устройства, для получения численного значения Д Т , т.е. N

пульсы At. Импульс ut,- поступает на второй вход вентиля 7 и разреша- ет на время At проход квантующих импульсов на вход синхронизации накапливающего сумматора 10; На информационном входе накапливающего сумматора 10 действует код числа - (N-1) + 2 (i-1). поскольку импульсы

одновременно поступают на суммирующий счетный вход счетчика 8, который срабатывает по заднему фронту

импульса ДС, обеспечивая тем самым задержку (i-1), так как во время действия i-ro импульса дсГ на информационном входе накапливающего сумматора 10 приложен код, установленный после окончания (i-l)-ro импульса (увеличение состояния счетчика 8 на 2 по каждому импульсу .At i обеспечивается подачей этих импульсов на счетный вход второго разряда счётчика В, т.е. разряда, соответствующего 2). Код числа (N - - 1)+2 (i-1) суммируется по каждому квантующему импульсу, действующему

щего сумматора 10 в течение интервала времени At(i 1,2,...,N). Следовательно, после окончания i-ro импульса At в накапливающем сумматоре 10 фиксируется код числа а|, рав- ного

а; tl (2J-N-1), (1)

J-i

при i N, т.е. на момент окбнчанияг времени измерения Т. ,

к

а„ 7 At(2i-N-l). (2) Ul

/, , ч

/, , ч

После окончания импульса At на выходе счетчика 8 формируется код, равный (N-1), который, поступая на первый вход кодового коммутатора 9, устанавливает на его выходе нулевой

потенциал (фиг.А,ж), устанавливаю- „ х-±- /

щий и удерживающий делители I и 2 . частоты соответственно в состояниях к/2 и О, разрешающий работу формирователя 6 времени регистрации и переписывающий в блок 11 регистрации код числа ац с выхода накапливающего сумматора 10. В блоке 11 регистрации осуществляется умножение в вычислителе 12 в соответствии с

ТV

vsyni.j/

ла а,. на нормализующий коэффициент 6KN(), код которого поступает с четвертого кодового входа устройства, для получения численного значения Д Т , т.е. N

(3)

дт

At (2i-N-l) KN()

После формирования формирователем 6 времени регистрации запускающего импульса (фиг,2,в) цикл измерения повторяется.

Определим оптимальный алгоритм обработки фазовых отсчетов (временных интервалов .At) по критерию минимума среднего квадрата ошибки, С этой целью запишем значение At,- в виде очевидного соотношения

At;

At,

х,К4Т,

(4)

где Х| 0,1,2,.,., N-1.

XV

Уравнение (4) относится к управле

киям лшнейной регрессии (3). Известно, что наилучшей оценкой 4Т (в . смысле минимума среднего квадрата ошибки) величины 4Т по измеренным значениям At является оценка, полученная по методу наименьших квадратов (МНК). Согласно этому методу для оценки ДТ можно записать фор

в виде

N

мулу (3)

N71Д t Xi -Г X;

-JZi-LlJrL-ljZi-1

ФГх - (tx,)

ДТ

(

(-1

1-1

Учитывая, что х :,, -. целые числа от О до (N-1) и используя выражения для суммы последовательностей целых чисел и суммы последовательностей квадратов целых чисел,, .получим

N

ЛТ

2g:()tt

)

N

6 gl (2i-N-l) Ati

Щы)

(6)

Следовательно, предлагаемое устройство реализует оптимальный по критерию минимума среднего квадрата ошибки алгоритм измерения частоты по фазовым отсчетам сигнала.

Дисперсию погрешности ) определим, полагая статистическую не- зависимость.случайньЬс погрешностей

if

(7)

шЩ1а-Ц1-)

)

о , ,

где Vg - дисперсия случайной погрешности Ai..

Среднеквадратическую погрешность получим из (7)

б-(йт) И&о/к VN(№-I). (8)

Вьшгрьш в точности по сравнению с известным устройством определим, сравнивая выражения (8) и (3),

. J.a. Ji.a.

jj joVta41 .

R J -J2HINJ-11 .. (9) о , . V с /м 14 J

12(N-1)

Т.е. при выигрьш в точности весьма значительный. Например, при

Таким образом, предлагаемое устройство позволяет либо существенно снизить среднеквадратическую погрешность измерения при одинаковом с из- вестньм способом времени измерения, либо достичь требуемую точность измерения за существенно меньшее время по сравнению с известным способом.

Формула изобретения

1. Устройство измерения разности периодов двух электрических сигналов, содержащее формирователь временных нтервалов, первый и второй входы которого через первый и второй делители частоты соединены с соответствующими входами устройства, и блок регистрации, выполненный в виде поседовательно соединенньпс вычислитея и индикатора, отличающее- с я тем, что, с целью повьш1ения точности измерения, в него дополнительно введены последовательно соединенные D-триггер, счетчик и накапливающий сумматор, формирователь квантующих импульсов, формирователь времени регистрации, вентиль и кодовый компаратор, первый вход которого соединен

с выходом счетчика, второй вход подключен к первому кодовому входу устройства, а выход соединен с управ- лякнцйми входами блока регистрации, первого и второго делителей частоты

и формирователя времени регистрации, второй вход которого соединен с входами формирователя квантукяцих импульсов и первого делителя частоты, а выход подсоединен к входу синхронизации записи счетчика и к входу начальной установки накапливающего сумматора, выход которого подключен к информационному входу блока регистрации, а второй вход синхронизации

соединен с выходом вентил я, первый вход которого соединен с выходом формирователя квантуннцих импульсов и с входом синхронизации D-триггера,информационный вход которого подсоединен к выходу формирователя временных интервалов, а выход D-триггера соединен с вторым входом вентиля, при ЭТОМ второй, третий и четвертый кодовые входы устройства подключены со- ответственно к установочным входам первого делителя частоты, счетчика и блока регистрации.

2. Устройство по п.1, о т л и - чающееся тем, что вычислитель блока регистрации содержит блок вычитания, по еледовательно соединен- ные первый умножитель, вторым входом

которого является код числа 6, и де- 15 фициент деления, а информационным

литель, последовательно соединенные сумматор, второй, третий и четвертый

Гз

1Ш1ШШШШ 1ЩД1и1ДШИ1П11И1М111и{1111 .t

sm

lll ||||||||||IHIIIIHHUtllllll,IIHIIIIIlllllllllliU LiiUt

Редактор С.Пекарь

Фаг.3 Составитель Губанов.

. Техред И.ПоповичКорректор М.Демчик

Заказ 7639/47Тираж 730Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д.4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная, 4

умножители, выход четвертого умножителя соединен с вторым входом делителя, выход которого является выходом вычислителя, при этом первые входы блока вычитания и сумматора объединены и являются входом кода числа 1, вторые входы блока вьпттания, сумматора и третьего умножителя объединены и являются входом кода числа N, где N - число измерений, выход блока вычитания соединен с вторым входом второго умножителя, вторым входом четвертого умножителя является вход кода числа К, где К - коэфвходом вычислителя является первый вход первого умножителя.

1м (

i-l

I

I

KlifH -l}

V

л

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой измеритель длительности периода | 1988 |

|

SU1582176A1 |

| Измеритель сдвига фаз (его варианты) | 1982 |

|

SU1040432A1 |

| Устройство для симметрирования токов трехфазных сетей | 1988 |

|

SU1686600A1 |

| Устройство для измерения параметров жидкости | 1990 |

|

SU1830460A1 |

| Устройство для измерения симметричных составляющих напряжений трехфазной сети | 1990 |

|

SU1781642A1 |

| Цифровой фазометр | 1980 |

|

SU892343A1 |

| Устройство для измерения сдвига фаз | 1986 |

|

SU1381406A1 |

| Способ измерения частоты | 1987 |

|

SU1613968A1 |

| Цифровой измеритель длительности периода | 1980 |

|

SU920556A1 |

| Устройство для определения вероятностных характеристик фазы случайного сигнала | 1982 |

|

SU1112377A1 |

Изобретение относится к измерительной технике и может быть использовано при построении прецизионных измерителей частоты и устройств дпя сравнения шкал времени. Цель изобретения - повышение точности измерения. Дпя достижения поставленной цеФцг.1 ли в устройство, содержащее формирователь 4 временных интервалов, делители 1,2 частоты, блок 11 регистрации , выполненный в виде вычислителя 12 и индикатора 13, введены D- триггер 5, счетчик 8, накапливающий сумматор 10, формирователь 3 кванти- рующих импульсов, формирователь 6 времени регистрации, вентиль 7 и кодовый компаратор 9. Устройство позволяет либо существенно снизить среднеквадратическую погрешность измерения при неизменном времени измерения, либо достичь требуемую точность измерения за существенно меньшее время. В описании изобретения также указан другой вариант исполнения вычислителя 2 блока 1J регистрации. 13. п.ф-лы, 3 ил. с (Л с: ND 00 сл оо сл и Код(н-1)

| Способ измерения частотных флуктуаций высокостабильных генераторов | 1982 |

|

SU1056070A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Способ измерения частоты | 1982 |

|

SU1093986A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1987-01-23—Публикация

1985-05-11—Подача