1

Изобретение относится к радиоизмерительной технике, предназначено для измерения периода гармонических сигналов и может быть использовано при создании прецизионных частотно-измерительных систем.

Известно устройство измерения периода, содержащее генератор опорной частотыi декадные делители опор- . ной частоты, формирователе, селектор, электронный счетчик, формирователь, декадные делители измеряемой частоты и схему формирования времени счета l .

Недостатком данного устройства является относительно высокая ошибка измерения при исследовании периода сигналов, прошедших различные преобразовательные устройства (приемники, компараторы частоты и другие) , внутренние шумы которых вносят паразитную фазовую модуляцию анализируемого сигнала, приводящую к погрешности измерения периода.

Наиболее близким по технической сущности к изобретению является измеритель периодов, содержащий формирователь, элементы И, триггер, генератор опорной частоты, делитель частоты, электронный счетчик, одновибратор, триггер-и селектор 2.

Однако, в данном устройстве наблюдается наличие значительной погрешности измерения периода сигналов,

10 прошедших разного рода преобразовательные устройства, а также содержится ошибка измерения, обусловленная формирователем, вырабатывающим прямоугольное напряжение из синусо15идального сигнала, и шумы которого приводят к флюктуациям фронтов измеряемого сигнала.

Цель изобретения - повышение точности измерения длительности периода.

20

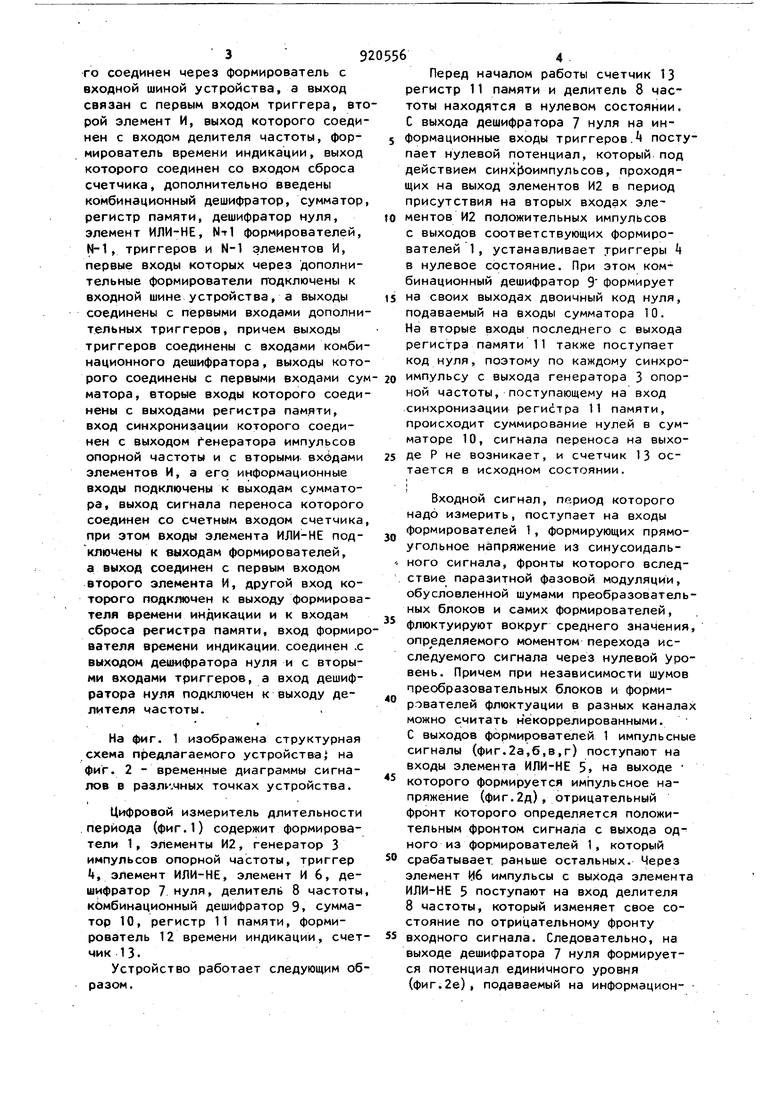

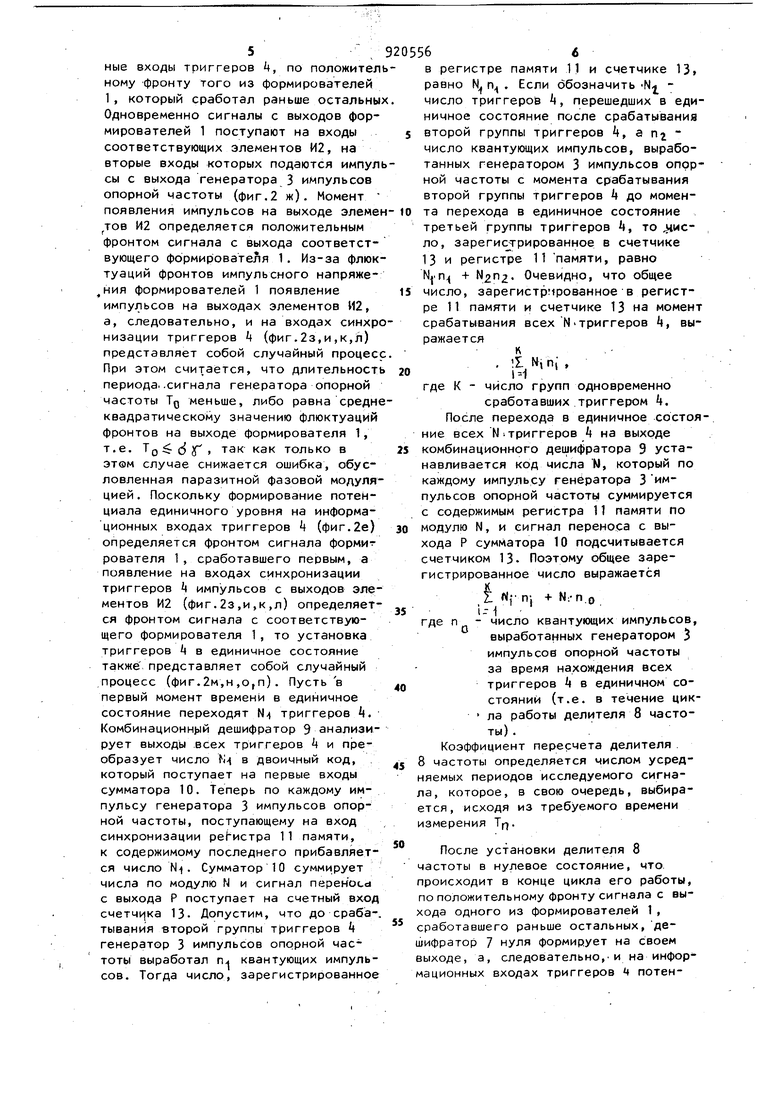

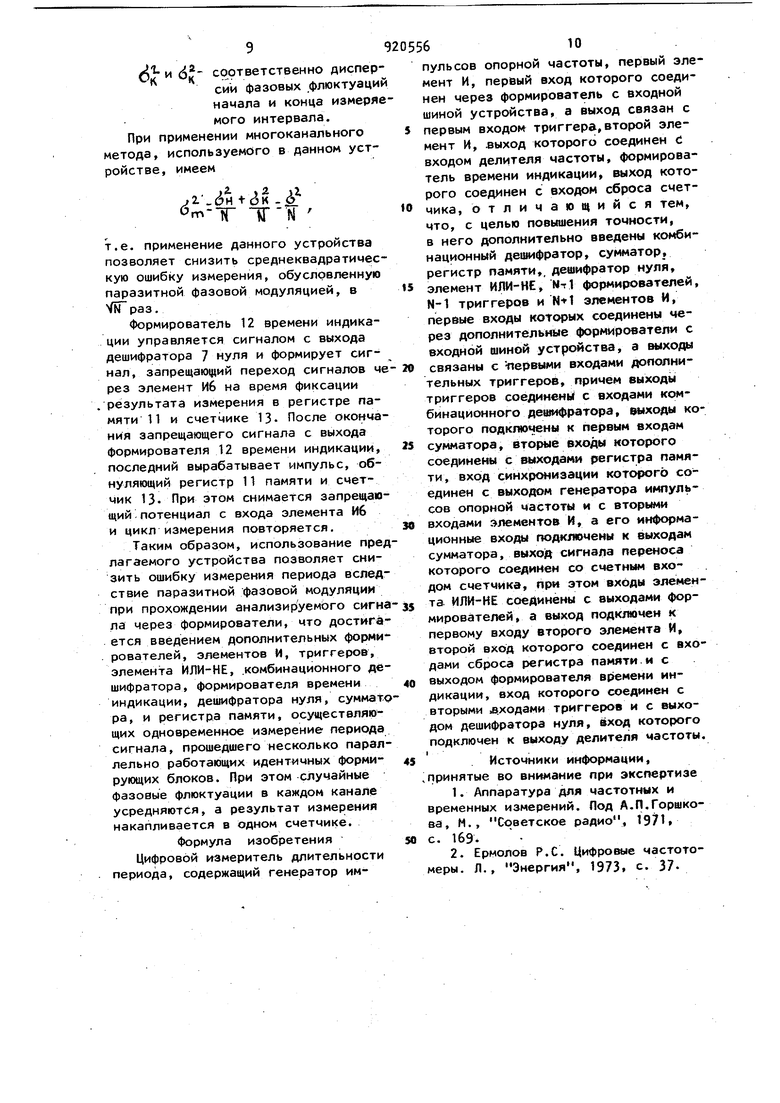

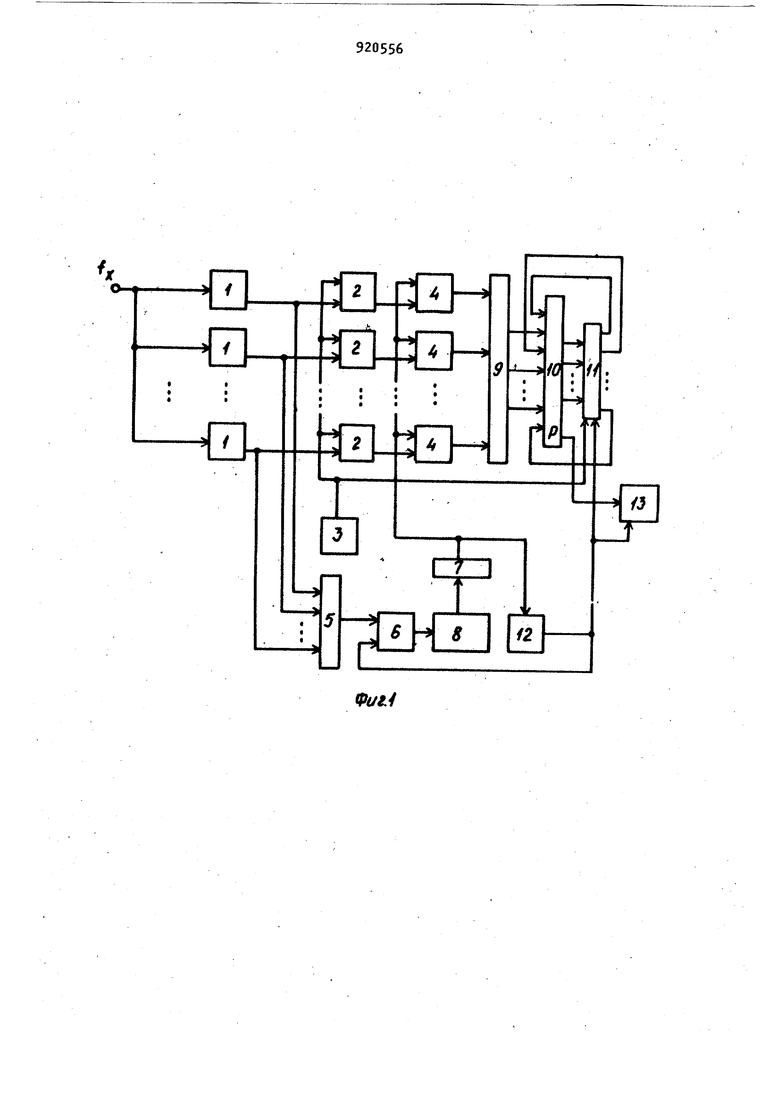

Поставленная цель достигается тем, что в устройство, содержащее генератор импульсов опорной частоты, первый элемент И, первый вход которого соединен через формирователь с входной шиной устройства, а выход связан с первым входом триггера, вто рой элемент И, выход которого соединен с входом делителя частоты, формирователь времени индикации, выход которого соединен со входом сброса счетчика, дополнительно введены комбинационный дешифратор, сумматор регистр памяти, дешифратор нуля, элемент ИЛИ-НЕ, Nil формирователей, N-1, триггеров и N-1 элементов И, первые входы которых через дополнительные формирователи подключены к входной шине устройства, а выходы соединены с первыми входами дополнительных триггеров, причем выходы триггеров соединены с входами комбинационного дешифратора, выходы которого соединены с первыми входами сум матора, вторые входы которого соеди нены с выходами регистра памяти, вход синхронизации которого соединен с выходом Генератора импульсов опорной частоты и с вторыми входами элементов И, а его информационные входы подключены к выходам сумматора, выход сигнала переноса которого соединен со счетным входом счетчика при этом входы элемента ИЛИ-НЕ подключены к выходам формирователей, а выход соединен с первым входом второго элемента И, другой вход которого подключен к выходу формирова теля времени индикации и к входам Сброса регистра памяти, вход формир вателя времени индикации, соединен .с выходом дешифратора нуля и с вторыми входами триггеров, а вход дешифратора нуля подключен к выходу делителя частоты. На фиг. 1 изображена структурная схема предлагаемого устройства на фиг. 2 - временные диаграммы сигналов в различных точках устройства. Цифровой измеритель длительности периода (фиг.1) содержит формирователи 1, элементы И2, генератор 3 импульсов опорной частоты, триггер , элемент ИЛИ-НЕ, элемент И 6, дешифратор 7 нуля, делитель 8 частоты комбинационный дешифратор 9 сумматор 10, регистр 11 памяти, формирователь 12 времени индикации, счет чик 13. Устройство работает следующим об разом . 9 4 Перед началом работы счетчик 13 регистр 11 памяти и делитель 8 частоты находятся в нулевом состоянии. С выхода дешифратора 7 нуля на информационные входы триггеров. поступает нулевой потенциал, который под действием синхр5оимпульсов, проходящих на выход элементов И2 в период присутствия на вторых входах элементов И2 положительных импульсов с выходов соответствующих формирователей 1, устанавливает триггеры в нулевое состояние. При этом комбинационный дешифратор 9 формирует на своих выходах двоичный код нуля, подаваемый на входы сумматора 10. На вторые входы последнего с выхода регистра памяти 11 также поступает код нуля, поэтому по каждому синхроимпульсу с выхода генератора 3 опорНОИ частоты, поступающему на вход синхронизации регистра 11 памяти, происходит суммирование нулей в сумматоре 10, сигнала переноса на выходе Р не возникает, и счетчик 13 остается в исходном состоянии. Входной сигнал, период которого надо измерить, поступает на входы формирователей 1, формирующих прямоугольное напряжение из синусоидального сигнала, фронты которого вследствие паразитной фазовой модуляции, обусловленной шумами преобразовательных блоков и самих формирователей, Флюктуируют вокруг среднего значения. определяемого моментом перехода исследуемого сигнала через нулевой уровень. Причем при независимости шумов преобразовательных блоков и формирователей флюктуации в разных каналах можно считать некоррелированными. С выходов формирователей 1 импульсные сигналы (фиг.2а,б,в,г) поступают на входы элемента ИЛИ-НЕ 5, на выходе которого формируется импульсное напряжение (фиг.2д), отрицательный фронт которого определяется положительным фронтом сигнала с выхода одного из формирователей 1 , который срабатывает раньше остальных. Через элемент Иб импульсы с выхода элемента ИЛИ-НЕ 5 поступают на вход делителя 8 частоты, который изменяет свое состояние по отрицательному фронту входного сигнала. Следовательно, на выходе дешифратора 7 нуля формируется потенциал единичного уровня (фиг.2е), подаваемый на информацион- 5 9 ные входы триггеров 4, по положительному фронту Того из формирователей 1, который сработал раньше остальных. Одновременно сигналы с выходов формирователей 1 поступают на входы соответствующих элементов И2, на вторые входы которых подаются импульсы с выхода генератора 3 импульсов опорной частоты (фиг.2 ж). Момент появления импульсов на выходе элеменJOB И2 определяется положительным фронтом сигнала с выхода соответствующего формир1ователя 1. Из-за флюк туации фронтов импульсного напряже ния формирователей 1 появление импульсов на выходах элементов И2, а, следовательно, и на входах синхр низации триггеров h (фиг.2з,и,к,л) представляет собой случайный процес При этом считается, что длительност периода, .сигнала генератора опорной частоты TQ меньше, либо равна средн квадратическому значению флюктуации фронтов на выходе формирователя 1, т.е. TO.(;, так как только в этом случае снижается ошибка, обусловленная паразитной фазовой модуля цией. Поскольку формирование потенциала единичного уровня на информационных входах триггеров Ц (фиг.2е) определяется фронтом сигнала формирователя 1, сработавшего первым, а появление на входах синхронизации триггеров Ц импульсов с выходов элементов И2 (фиг.2з,и,к,л) определяется фронтом сигнала с соответствующего формирователя 1, то установка триггеров в единичное состояние также представляет собой случайный процесс (фиг.2м,н ,о,п) . Пусть в первый момент времени в единичное состояние переходят N триггеров , Комбинационн1з1й дешифратор 9 анализирует выходы .всех триггеров 4 и п(эеобразует число в двоичный код, , который поступает на первые входы сумматора 10. Теперь по каждому импульсу генератора 3 импульсов опорной частоты, поступающему на вход синхронизации регистра 11 памяти, к содержимому последнего прибавляется число N. Сумматор 10 суммирует числа по модулю N и сигнал nepeHotd с выхода Р поступает на счетный вход счетч1/|ка 13- Допустим, что до срабатывания второй группы триггеров k генератор 3 импульсов опорной частоты выработал п.4 квантующих импульсов. Тогда число, зарегистрированное 66 в регистре памяти 11 и счетчике 13, равно N п , Если обозначить -ti число триггеров 4, перешедших в единичное состояние после срабатывани13 второй группы триггеров 4, а п число квантующих импульсов, выработанных генератором 3 импульсов опорной частоты с момента срабатывания второй группы триггеров до момента перехода в единичное состояние третьей группы триггеров k, то число, зарегистрированное; в счетчике 13 и регистре 11 памяти, равно N|n + N202- Очевидно, что общее число, зарегистргфованное в регистре 11 памяти и счетчике 13 на момент срабатывания всех N-триггеров 4, выражается . jl Nini . где К - число групп одновременно сработавших триггером t. После перехода в единичное состояние всех N триггеров t на выходе комбинационного дешифратора 9 устанавливается код числа N, который по каждому импульсу генератора 3 импульсов опорной частоты суммируется с содержимым регистра 1} памяти по модулю N, и сигнал переноса с выхода Р сумматора 10 подсчитывается счетчиком 13- Поэтому общее зарегистрированное число выражается I rtf П-, + N:-n.o : где п - число квантующих импульсов, выработанных генератором 3 импульсов опорной частоты за время нахождения всех триггеров k в единичном состояний (т.е. в течение цикла работы делителя 8 частоКоэффициент пересчета делителя частоты определяется числом усредяемых периодов исследуемого сигнаа, которое, в свою очередь, выбиратся, исходя из требуемого времени змерения Tj-j. После установки делителя 8 астоты в нулевое состояние, что. роисходит в конце цикла его работы, по положительному фронту сигнала с выода одного из формирователей 1 , работавшего раньше остальных, деифратор 7 нуля формирует на своем ыходе, а, следовательно, и на инфор ационных входах триггеров 4 потенциал нулевого уровня. В силу наличия паразитной фазовой модуляции, приводящей к флюктуациям фронтов прямоугольного напряжения на выходах формирователей 1 , появление импульсов .на выходах элементов И2 (фиг.2з,и, к,л), а следовательно, и перевсЗд триггеров в нулевое состояние (фиг.2м,н,о,п) представляет из себя случайный процесс. Поэтому по аналогии с началом интервала времени измерения можно записать выражение для числа, зарегистрированного в регистре 11 памяти и счетчике- 13 с момента сформирования потенциала нулевого уровня на выходе дешифратора 7 нуля, определяемого фронтом сигнала формирователя 1, сработавшего последним

-Njn. J где Mj - число триггеров Ц, оставшихся в единичном состоянии после обнуления j-ой группы триггеров , П1 - число квантующих импульсов, выработанных генератором 3 импульйов опорной частоты в промежутке между обнулениями j-ой и (j+1)-oй группы триггеров k, т - число групп одновременно

обнуленных триггеров k, После перехода в нулевое состояние всех N триггеров k на первые входы сумматора 10 с выхода комбинационного дешифратора 9 подается код О, и увеличение содержимого регистра 11 памяти и счетчика 13 прекращается. При этом в регистре 11 памяти и счетчике 13 фиксируется число ,пропорциональное измеряемому периоду анализируемого сигнала, т.е.

К tn Побш, lHtn-, . f

-

f

Среднее значение измеренного интервала времени, равного N пе риодам анализируемого сигнала, определяется как

Т JC г5 т Мо. т Lобщ - -2. Л ,То Y

m

1 п:Той

i

Рассмотрим первое слагаемое в выражении (2) и находим предел,к которому оно стремится, при и TQ- 0. Очевидно, что в этом случае произведение njTo переходит в непрерывную случайную величину t, характеризующую флюктуации фронтов прямоугольного напряжения на выходах формирователей 1, отношение N{ N превращается в плотность вероятности (jL)(t-y) случайной величины t, а

сумма заменяется интегралом, т.е.

f ОО I

tL-m .Е niTo -5tv

- jq 00 tM N.«0 V ,

(dt J MtloV-to. ()

Аналогичные рассуждения по отношению к третьему слагаемому в выражении (2 позволяют записать

I .-г MJ -Гл I jbTT-it,,.

Eim

J--1 TO- О

u)(t;)dt, ц)

Здесь t(j и tg - математические х кидания соответственно начала и конца измеряемого интервала времени. Следовательно, при Тд-у О и имеем оценку измеряемого интервала времени с рулевой дисперсией, при конечных N и TO, а силу независимости флюктуации фазы в различных каналах, получаем оценку этого интервала с дисперсией, уменьшенной в N раз по сравнению с оценкой, получаемой при использовании одноканальных измерителей периода, в известных устройства-х. Действительно, случайная ошибка измерения периода исследуемого сигнала, обусловленная паразитной фазовой модуляцией, определяется флюктуациями фронтов прямоугольного напряжения формирователей 1 в начале и в конце интервала времени измерения, т.е.

,

2. - дисперсия ошибки измерения интервала времени, равного N периодам входного сигнала одноканальным методом; J и Sсоответственно диспер сии фазовых флюктуаци начала и конца измеря мого интервала. При применении многоканального метода, используемого в данном устройстве, имеем .r.6HtaK- 1Г т.е. применение данного устройства позволяет снизить среднеквадратичес кую ошибку измерения, обусловленную паразитной фазовой модуляцией, в Ч|Граз. Формирователь 12 времени индикации управляется сигналом с выхода дешифратора 7 нуля и формирует сигнал, запрещающий переход сигналов ч рез элемент Иб на время фиксации .результата измерения в регистре памяти 1 1 и счетчике 13- После оконча ния запрещающего сигнала с выхода формирователя 12 времени индикации, , последний вырабатывает импульс, обнуляющий регистр 11 памяти и счетчик 13. При этом снимается запрещаю щий потенциал с входа элемента Иб и цикл измерения повторяется, Таким образом, использование пред лагаемого устройства позволяет снизить ошибку измерения периода вслед ствие паразитной фазовой модуляции при прохождении анализируемого сигна ла через формирователи, что достига ется введением дополнительных формирователей, элементов И, триггеров, элемента ИЛИ-НЕ, .комбинационного дешифратора, формирователя времени индикации, дешифратора нуля, суммато ра, и регистра памяти, осуществляющих одновременное измерение периода сигнала, прошедшего несколько параллельно работающих идентичных формирующих блоков. При этом случайные фазовые флюктуации в каждом канале усредняются, а результат измерения накапливается в Одном счетчике. Формула изобретения Цифровой измеритель длительности периода, содержащий генератор импульсов опорной частоты, первый элемент И, первый вход которого соединен через формирователь с входной шиной устройства, а выход связан с первым входом триггера, второй элемент И, .выход которого соединен С входом делителя частоты, формирователь времени индикации, выход которого соединен с входом сброса счетчика, отличающийся тем, что, с целью повышения точности, в него дополнительно введены комбинационный дешифратор, сумматор, регистр памяти,, дешифратор нуля, элемент ИЛИ-НЕ, Мт1 формирователей, N-1 триггеров и элементов И, первые входы которых соединены через дополнительные формирователи с входной шиной устройства, а выходы связаны с -первыми входами дополнительных триггеров, причем выходы триггеров соединень с входами комбинационного дешифратора, выходы которого подключены к первым входам сумматора, вторые входы которого соединены с выходами регистра памяти, вход синхронизации которого соединен с выходом генератора импульсов опорной частоты и с вторыми входами элементов И, а его информационные входы подключены к выходам сумматора, выход сигнала переноса которого соединен со счетным входом счетчика, при этом входы элемента ИЛИ-НЕ соединены с выходами формирователей, а выход подключен к первому входу второго элемента И, второй вход которого соединен с входами сброса регистра памяти.и с выходом формирователя времени индикации, вход которого соединен с вторыми а.ходами триггеров и с выходом дешифратора нуля, вход которого подключен к выходу делителя частоты. - . Источники информации, ринятые во внимание при экспертизе 1.Аппаратура для частотных и ременных измерений. Под А.П.Горшкоа, М., Советское радио, 1971 . 169. 2.Ермолов Р.С. Цифровые частотоеры. Л., Энергия, 1973, с. jriiiilliiiiiiritniiitiiiiiiiiiiiiiiMb,

iiitrnnnnitiitiiiini

MHIIHIttllllllHUiil riHtiimiiiiniiiiiiiniitnun

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой фазометр | 1980 |

|

SU892343A1 |

| Цифровой измеритель длительности периода | 1981 |

|

SU1010570A1 |

| Устройство для измерения ритма сердца | 1985 |

|

SU1284512A1 |

| ЦИФРОВОЙ ЧАСТОТОМЕР | 1996 |

|

RU2097774C1 |

| Цифровой измеритель длительности периода | 1981 |

|

SU1004955A1 |

| Измеритель длительности временных интервалов | 1980 |

|

SU949625A1 |

| Цифровой измеритель периода | 1978 |

|

SU771563A1 |

| Устройство индикации пеленга | 1983 |

|

SU1167555A1 |

| СТЕНД ДЛЯ ИЗУЧЕНИЯ ЭЛЕКТРОННЫХ СРЕДСТВ АВТОМАТИЗАЦИИ | 2005 |

|

RU2279718C1 |

| Устройство для вычисления параметров диаграмм разрежения индикаторов при исследовании сердечно-сосудистой системы | 1982 |

|

SU1157547A1 |

Фиг.2.

Авторы

Даты

1982-04-15—Публикация

1980-07-28—Подача