О

00

сх

Изобретение относится к автоматике .и вычислительной технике и предназначено для согласования полосы входного сигнала с полосой пропускания, анализирующей и измерительной аппаратуры.

Известен цифровой регистратор, который позволяет путем соответствующего выбора скорости выдачи данных перенести спектр частот исходного сигнала в рабочий диапазон частот ряда записывающих и анализирующих приборов. Такой регистратор состоит из устройства-выборки дискретных данных, аналого-цифрового преобразователя, запоминающего устройства, цифроаналогового.преобразователя, устройства управления.и фильтра |нижних частот ,ll.

Известно устройство для временного сжатия входного сигнала, содержащее блоки управления и блок памяти, выполненные с применением магнитострикционных линий задержки, причем входы магнитострикционных линий блоков памяти соединены с помощью магнитострикционных линий задержки блока управления с выходамипреобразователя аналог-код, а выходы соединены с входом преобразователя код - аналог t2 1.

Недостатками этих устройств яв-. ляется сложность, так как они также включают в себя одновременно неработающие преобразователи аналог - код и код - аналог.

Наиболее близким по технической сущности к предлагаемому является устройство для сжатия во времени входного сигнала, содержащее преобразователь аналог - код, информационный вход которого соединен с входом устройства, выход - с информационным входом оперативного запоминающего блока, выход которого соединен с информационным входом преобразователя код - аналог, управляющий вход которого соединен с первым выходом хронизатора, а выход с выходом устройства. Вход блока определения периода подключен к входу устройства, первый выход блока определения периода соединен с первым входом блока умножения частоты, второй выход - с первым входом блока дресации и первым входом хронизатора, второй, третий, четвертый, ятый и шестой выходы которого соеинены соответственно с вторым и ретьимвходами блока адресации, торым, третьим и четвертым входами лока умножения- частоты, первый ыход блока умножения Частоты Соеди- ен с управляющим входом преобразоателя аналог - код и четвертыгл вхоом блока адресации, выход которого оединен с управляющим входом опеативного запоминающего блока,, второй выход блока умножения частоты соединен с вторым входом хронизатора СзЗ.

Недостатком устройства является сложность, так как оно включаеу в сбя преобразователи аналог - код и код - аналог, которые требуют ряда прецизионных комплектующих изделий. Устройство для временного сжатия входного сигнала не требует одновременной работы преобразователей аналоГ - код и код - аналог так как процессы регистрации и вывода сигнала имеют различные временные масштабы и следуют друг за другом.

Цель изобретения - упрощение устройства ,

Поставленная цель достигается тем, что в устройство для.сжатия во времени входного сигнала, содержаще преобразова.тель код - аналог, форми рователь импульсов, вход которого подключен к входу устройства, первый выход - к. первым входам хронизатора и блока адресации, второй выход - к первому входу блока умножения .частоты, первый выход которого соединен с вторым входом блока адресации, второй выход - с вторым входом хронизатора, первый выход которого подключен к второму входу блока умножения частоты, второй выход к третьему входу блока адресации, выход которого соединен с управляющим входом оперативного запоминающего блока, введены блок сравнения, коммутатор, регистр последовательного приближения, первый вход которого подключен к первому выходу блока умножения частоты, второй вход к выходу блока сравнения, выход объединен с информационным входом оперативного запоминающего блока и подключен к первому входу коммута- . тора, второй вход которого соединен с первым выходом формирователя имг пульсов, третий вход - с выходом оперативного запоминающего блока, выход через преобразователь -код аналог - с выходом устройства и первым входом блока сравнения, второй вход которого подключен к входу устройсбгва.

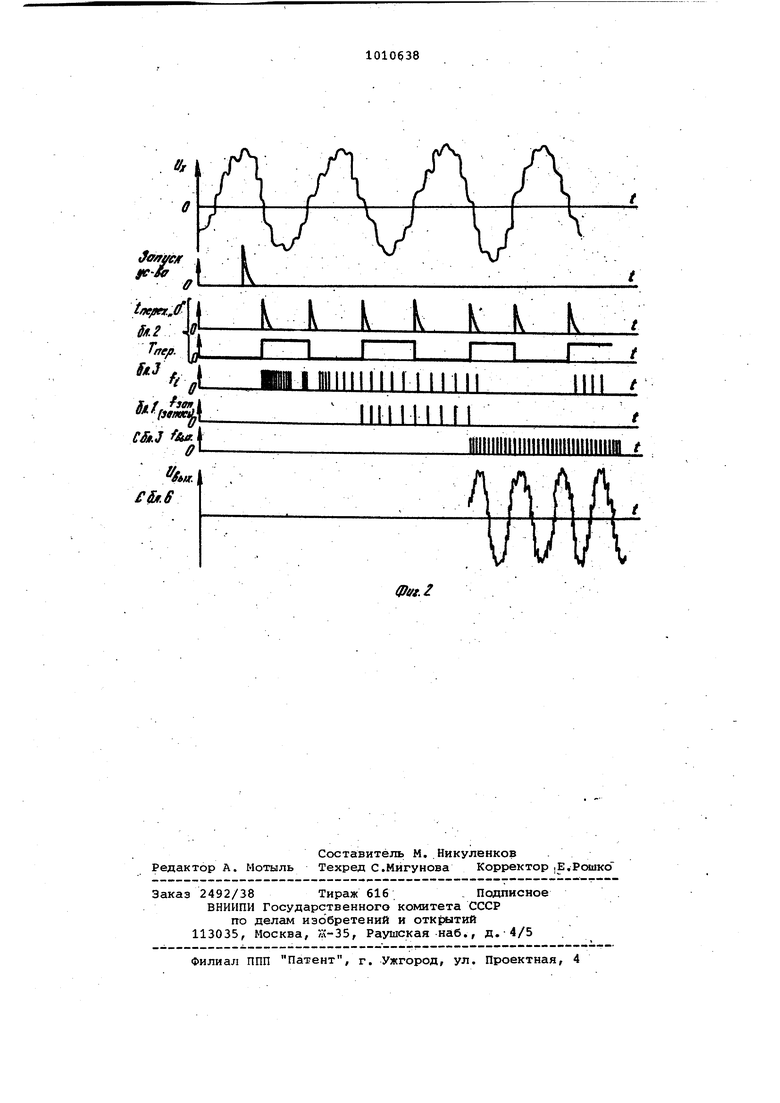

На фиг. 1 представлена блок-схема предлагаемого устройства для сжатия во времени входного сигнала; на фиг, 2 - временные диаграммы, поясняющие работу устройства.

Устройство для сжатия во времени входного сигнала содержит (фиг, 1) оперативный запоминающий блок 1, формирователь 2 импульсов (блок определения периода), блок 3 умножения частоты, блок 4 адресации, хронизатор 5, преобразователь 6 код -аналог, коммутатор 7, регистр 8 последовательного приближения, блок 9 сравнения.

Устройство для сжатия во времени входного сигнала работает следующим образом.

Входной сигнал периодически поступает на вход блока 2 определения периода. В формирователе 2 фиксируется уровень, например нулевое значение, с которым сравнивается входной- сигнал. Три пересечения зафиксированного уровня входным сигналом определяют период входного сигнала.

Преобразователь б, коммутатор 7, регистр 8 и блок 9 в совокупности образуют преобразователь аналог код (не показан).

После запуска устройства и установки в исходное состояние всех его блоков первый и второй выходы блока 3 умножения частоты заперты сигналами хронизатора 5. Как толь.ко в блоке 2 определения происходит пересечение фиксированного уровня напряжения входным сигналом, блок 2 формирует первый импульс .периода входного сигнала, который с второго выхода блока 2 подается на первый вход блока 3 умножения частоты. Одновременно с первого выхода хронизатора 5 на второй вход блока 3 поступает тактовая частота. Начинается автоматическое оп.ределение частотызапуска преобразователя аналог - код, которое длится в течение первого из рассматриваемых периодов входного сигнала. Блок 3 умножения частоты формирует частоту запуска преобразователя аналог - код таким образом, что независимо от частоты входного его период делится на число, не меньше и не больше заданного.

Автоматически эта операция выполняется следующим образом.

В блоке 2 определения периода входного сигнала СФиг. 2) формируется импульс начала периода, который поступает в блок 3 умножения частоты. В блоке 3 формируется ряд частот, каждая из которых, например, вдвое ниже предыдущей. С момента поступления импульса начала периода в блок 3 начинается подсчет наивысшей частоты из указанного ряда частот счетчиком, объем которого равен заданному удвоенному значению числа ординат входного сигнала. В случае, если счетчик числа ординат заполнится до момента прихода импульса конца периода входного сигнала, в блоке 3 происходит перезапись старшего радряда счетчика и понижение в два раза (для приведенного примера) частоты из ряда частот. Такой процесс повторяется многократно до тех пор, пока не придет импульс конца периода входного сигнала из блока 2 в блок 3. С приходом этого импульса в счетчике числа ординат

блока 3 фиксируется искомое число и назначается частота запуска преобразователя аналог-код, которая на. следующем периоде входного сигнала формирует получившее число ординат ВХОДНОГО сигнала.

Формирование частоты запуска преобразователя аналог - код заканчивается с приходом на первый вход блока 3 сигнала конца первого периода входного сигнала. Одновременно с0 15 окончанием первого периода входного сигнала блоком 2 формируется имп-льс начала следующего, второго периода, который с первого выхода блока 2 поступает за первые входы блока 4, хронизатора 5 и на второй вход коммутатора для запуска преобразователя аналог - код.

Импульсы запуска преобразователя аналог - код формируют в блоке 4 адч ресации коды адресов ординат входного сигнала, которые с его выхода подаются на управляющий вход оперативного запоминающего блока 1, В блоке -1 записываются коды адресов

5 ординат входного сигнала в течение второго рассматриваемого периода входного сигнала.

Адреса ординат входного сигнала формируются блоком 4 в то время, коЬ0да на второй вход блока 3 от хронизатора 5 подается разрешающий сигнал по окончанию второго периода входного сигнала.. После окончания второго периода

5 входного сигнала прекращается запуск преобразователя аналог - код, а в оперативном запоминаняцем блоке 1 . накоплены ординаты входного сигнала, относящиеся к одному периоду.

Преобразователь аналог - код ра0ботает следующим образом.

На втором рассматриваемом периоде входного сигнала тактовая частота запуска преобразователя аналог код поступает с первого выхода блока

5 3 умножения частоты иа первый вход регистра 8 последовательного приближения, КОТ01МЛЙ по сигналам блока 9 сравнения формирует импульсы последовательного опроса преобразовате0ля б, .а также результирующий код преобразователя аналог - 1Лэд. С первого выхода блока 2 на второй вход коммутатора 7 на время второго рассматриваемого периода входного сигнала подается управлякяций потенциал,

5 который переключает коммутатор 7 так, что импульсы последовательного опроса при каждом аналого-цифровом прет; образовании от регистра 8 проходят на вход преобразователя 6, выход

0 которого соединен с блоком 9 сравнения.

Таким образом, преобразователь аналог - код работает по принципу поразрядного взвешивания, коды ко5торого из регистра 8 записываются в оперативный запоминающий блок 1, получающий коды адресов из блока 4 адресации. Кодовые команды адресов записи формируются импульсами запус ка преобразователя аналог - код с первого выхода блока 3, После окончания второго рассматриваемого периода входного сигнала блок 2 с первого выхода подаёт на второй вход коммутатора 7 сигнал, по которому первый вход коммутатора запирается, а третий вход от оперативного запоминающего блока 1 отпирается. Кроме того, в блоке 3 с второго выхода через хронизатор 5 на третий вход блока 4 начинают поступать так товые импульсы считывания информации из оперативного зешоминающего блока 1, по которым формируются код адресов считывания в блоке 4. Коды ординат входного сигнала из оперативного запоминающего блока 1 через коммутатор 7 подаются на преобразователь аналог - код б, на выходе которого формируется ступенчатый периодический сжатый во времени сиг нал, по форме повторяющий входной сигнал. Частота выходного сигнала Эависи т от частоты тактовых импульсов считывания из оперативного запоминающего блока 1. Считывание )1Нформации в блоке 1 происходит бел разрушения, циклически период за периодом. Количество ступеней на периоде . сжатого сигнала зависит от количества ординат входного сигнала, которое запоминается блоком 1 и определяет погрешность аппроксимации, характеристики которой могут быть измерены. Процесс выдачи сжатого сигнала происходит до следующего запуска, при котором все изложенные процессы в устройстве повторяются. Временная диаграмма (фиг. 2) показывает входной непрерывный периодический сигнал сложной формы и произвольный во времени по отношению к нему сигнал запуска устройства. В блоке 2 определяются моменты ftieif 9 перехода сигналом U нулевого урсэ ня л формируются импульсы периода входного сигнала . В блоке 3 последовательно во времени формируются частоты, которые .позволяют для каждого периода Tfigp входного сигнала сформировать и записать в блок 1 от N.yj до 2 N ординат, В блоке 3, кроме того, формируется частота вывода кодов ординат из блока 1, которая формирует сжатый выходной сигнал.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для временного сжатия входного сигнала | 1980 |

|

SU888165A1 |

| Устройство для временного сжатия входного сигнала | 1987 |

|

SU1550559A2 |

| Устройство для временного сжатия входного сигнала | 1982 |

|

SU1100632A1 |

| Устройство для сжатия информации | 1982 |

|

SU1043711A1 |

| Устройство для сжатия информации | 1981 |

|

SU972544A1 |

| Цифровой вольтметр | 1982 |

|

SU1064219A1 |

| Цифровой вольтметр | 1981 |

|

SU976394A1 |

| Калибратор напряжения | 1984 |

|

SU1191892A1 |

| Устройство для передачи и приема телеметрической информации | 1985 |

|

SU1275509A1 |

| Цифровой генератор периодических колебаний инфранизких частот | 1980 |

|

SU970631A1 |

yCTPOHci-BO ДЛЯ ОХАТИЯ ВО ВРЕМЕНИ ВХОДНОГО СИГНАЛА, содержащее преобразователь код-аналог, формироо ватель. импульсов, вход которого подключен к входу устройства, первый выход - к первым входам хронизатора и блока адресации, второй выход - к первому входу блока умножения частоты, первый выход которого соединен с вторым входом блока адресации, второй выход - с вторым входом хронизатора, первый выход которого подключен к второму входу блока умйожения частоты, второй выход - к третьему- входу блока адресаций, выход которого соединен с управляющим входом оперативного запоминающего бгока, т л и ч а ющ её с я тем, что, с целью упрощения устройства, в него введены блок сравнения, | коммутатор, регистр последовательного приближения, первый вход которого подключен к первому выходу блока умножения частоты, второй вход-.- к выходу блока сравнения, выход объединен с информационньзм входом.оперативного запоминающего блока и подS ключен к первому входу коммутатора, второй вход которого соединен с первым выходом формирователя импульсов, третий вход - с выходом оператив|К го запоминающего блока, выход через преобразователь код-аналог - с выходом устройства и первым входом блока сравнения, второйвевход которого подключен к входу устройства.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Способ получения водорода или азотоводородных смесей из углеводородов или газовых смесей | 1926 |

|

SU7502A1 |

| Каталог фирмы Брюль и Кьер, Дания , 1979/1980 | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| УСТРОЙСТВО для ВРЕМЕННОГО СЖАТИЯ ВХОДНОГОСИГНАЛА | 0 |

|

SU253456A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Устройство для временного сжатия входного сигнала | 1980 |

|

SU888165A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

Авторы

Даты

1983-04-07—Публикация

1981-08-25—Подача