выполнен на коммутаторах, счетчике адреса записи, счетчике адреса считывания, регистре, формирователе импульсов, триггере, инверторе, элементе сравнения, элементе ИЛИ и элементе И, первые выходы счетчика адреса записи( соединены с первыми входами первого коммутатора и первыми входами регистра, выходы которого соединены с первыми входами элемента сравнения, выход которого соединен с первым входом элемента И, выход элемента И соединен с первым входом элемента ИЛИ, выход которого соединен с первым входом счетчика адреса считывания, первые выходы которого соединены с вторыми входами элемента сравнения и вто.рыми входами первого коммутатора, выход формирователя импульсов соединен с вторым входом элемента ИЛИ, выход триггера соединен с первыми входами второго и третьего коммутаторов, вторые входы которых объединены с вторым входом элемента И и подключены к выходу инвертора, выход второго коммутатора соединен с вторым входом счетчика адреса считывания, выход третьего коммутатора соединен с третьими входами первого коммутатора и элемента сравнения, третий вход третьего коммутатора соединен с шиной логического нуля, второй вход регистра подключен к первому входу блока адресации, вход триггера и третий вход второго коммутатора подключены к второму входу блокаiадресации, четвертый вход первого, коммутатора, объединенные вход инвертора, вход формирователя импульсов и четвертые входы второго и третьего коммутаторов и вход счетчика адреса записи подключены соответственно к третьему, четвертому и пятому вхрдам блока адресации , выход первого коммутатора и первый выход сяетчика адреса записи подключены соответственно к первому и второму выходам блока адресации, выход счетчика адреса считывания соединен с третьим входом элемента И и третьим выходом блока адресации, второй выход счетчика адреса записи соединен с четвертым выходом блока адресации.

3. Устройство по п.1, о т л и ц е е с я тем, что дешифратор выполнен на коммутаторе формирователе импульсов, инверторах, триггерах и элементах И, .выход формирователя импульсов соединен с входом/ первого триг

гера, первый выход которого соединен с первым входом первого элемента И, второй вход которого соединен с выходом первого инвертора, второй выход первого триггера соединен с первыми вводами второго и третьего элементов И, вторые входы которых подключены к соответствующим вы :одам коммутатора, выход второго элемента И соединен с .первым входом четвертогоэлемента И, ;второй вход которого через второй ин вертор соединен с первым входом коммутатора, выход четвертого элемента И через второй триггер соединен с первыми входами пятого и шестого элементов И, выход третьего элемента И Соединен с вторыми входами пятого и шестого элементов И, выходы первого, второго, пятого и шестого элементов И соединены ..с соответствующими выходами дешифратора, объединенные вторые щхог ды коммутатора и четвертого элемента И, третий и четвертый входы коммутатора-.и .объединенные первого инвертора и формирователя импульсов подключены соответственно к первому, второму, третьему и четвертому входам дешифратора.

. 4, Устройство по п.1, о т л и ч аю 1Д е е с я тем, что блок управления выполнен на формирователях импульсов, коммутаторах, генераторе импульсов,, триггерах, инверторе, элемент е И элементе ИЛИ и элементе задержки, выход первого формирователя импульсов сединен с первым входом первого элемента И, второй вход которого соединен с выходом инвертора, выход - с первым входом первого триггера, второй вход которого объединен с первым входом второго триггера и подключен к выходу второго/формирователя импульсов, выход первого триггера соединен с первыми входами элемента ИЛИ, первого и второго коммутаторов, первый выход элемента ИЛИ соединен с первым входом третьего коммутатора и вторым входом второгокоммуtaTOpa,; выход которого соединен с входов элемента задержки, первый выход которого соединен с вторцми входами первого и третьего коммутаторов, выход генератора импульсов соединен с первым входом второго элемента И и .входом третьего формирователя импульсов, выг ход которого соединен с третьим входом первого .и второго коммутаторов и первым входом третьего элемента И; второй-вход которого соединен с выходом второго триггера, второй вход которого подключен к шине Пуск, первого инвертора, вход второго формирователя импульсов, второй вход элемента. ИЛИ и четвертые входы первого и второго коммутаторов подключены к первому входу блока управления, объединенные третий вход третьего коммутатора и пятый вход второго коммутатора подключены к второму входу блока управления, вход первого формирователя импульсов и шестой вход Btoporo коммутатора подключены соответственно к третьему и четвертому ; входам блока управления, выход третьего элемента И, выход третьего коммутатора, выход второго элемента И, второй,.третий и четвертый выходы элемента задержки, выход первого коммутатора подключены соответственно к : первому-седьмому выходам блока управ- ления, ВТОРОЙ выход.элемента ИЛИ ; подключен к второму входу второго. : элемента И и восьмому выходу блока управления.

5. Устройство по П.1, от л и ч ее с я тем, что распределитель выполнен на триггерах, инверторе, элементах И и элементе ИЛИ, первый выход первого триггера соединен с первым входом элемента ИЛИ, выход которого соединен с первым входом первого

элемента И, второй выход первого триггера соединен с первым входом второго элемента И, выход которого соединен с вторым входом элемента ИЛИ, выход инвертора/соединен с вторым входом

второго элемента И и первыми входами второго тригера и третьего элемента И, выход второго триггера соединен с вторым входом третьего элемента И и., первым входом четвертого элемента И, объединённые вторые входы первого и четвертого элементовИ и третий вход третьего элемента И подключены к первому входу распределителя, объединенные входы первого триггера и инвертора и третий вход четвертого элемента И подключены к второму входу распределителя, объединенные третий вход первого элемента И и четвертые входы третьего и четвертого элементов И подключены к третьему входу распределителя, выходы первого, четвертого и третьего элементов И подключены соответственно к первому, второму и третьему входам распределителя.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления параллельным выполнением команд в электронной вычислительной машине | 1982 |

|

SU1078429A1 |

| Устройство для отображения графической информации на экране телевизионного индикатора | 1987 |

|

SU1439672A1 |

| Устройство для вывода графической информации | 1989 |

|

SU1644208A1 |

| Контурная система программного управления | 1989 |

|

SU1681298A1 |

| Устройство для отображения графической информации | 1987 |

|

SU1474724A1 |

| Программируемый контроллер | 1989 |

|

SU1741100A1 |

| Микропрограммный процессор | 1982 |

|

SU1070557A1 |

| Устройство для отображения информации на экране телевизионного индикатора | 1985 |

|

SU1437907A1 |

| Устройство для сопряжения магистрали ЭВМ с периферийными устройствами | 1990 |

|

SU1751775A1 |

| Телевизионный координатор | 1983 |

|

SU1109956A1 |

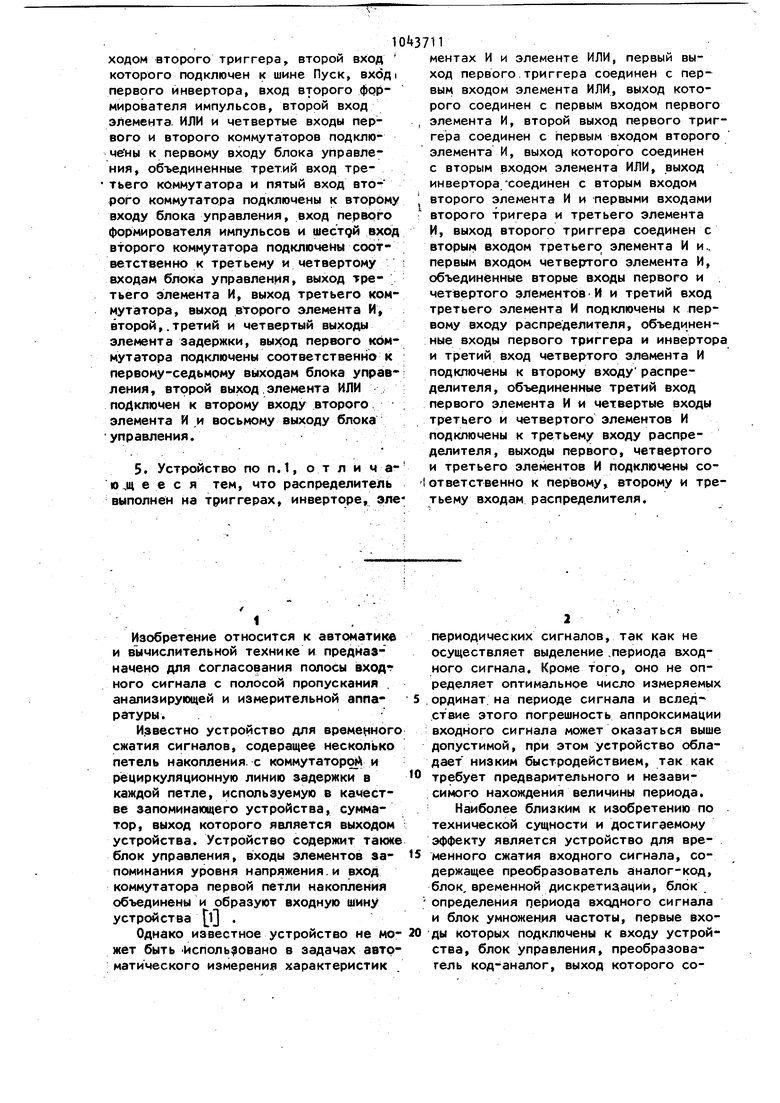

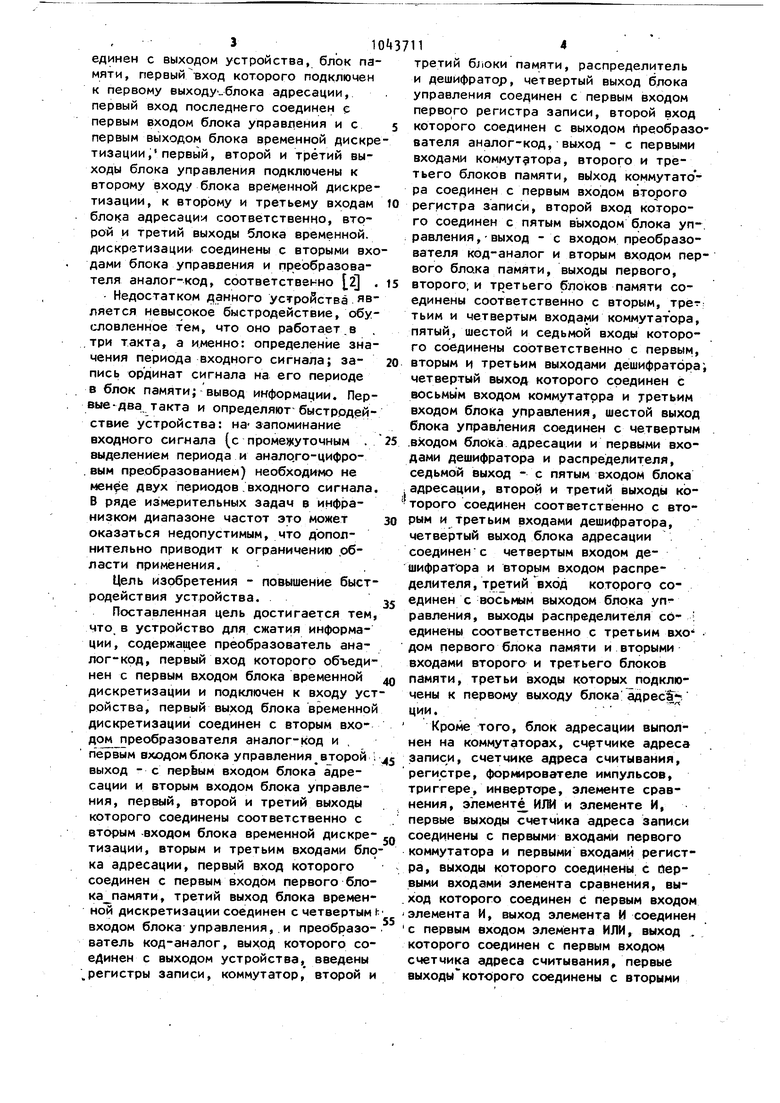

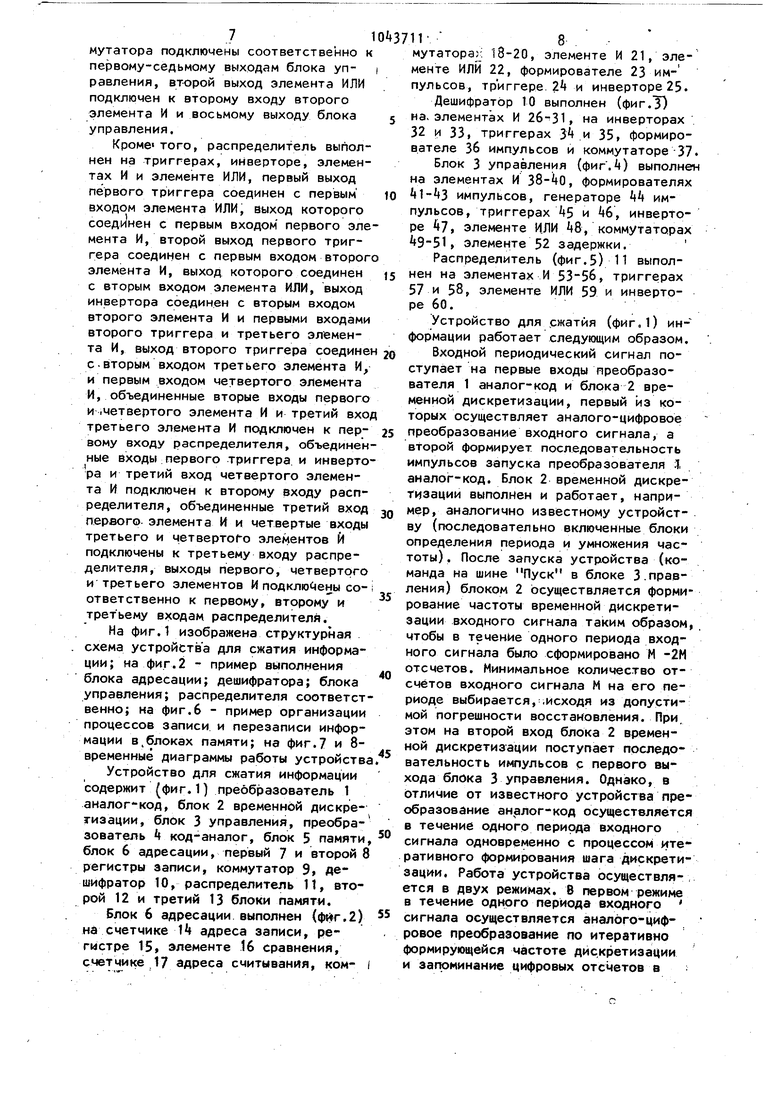

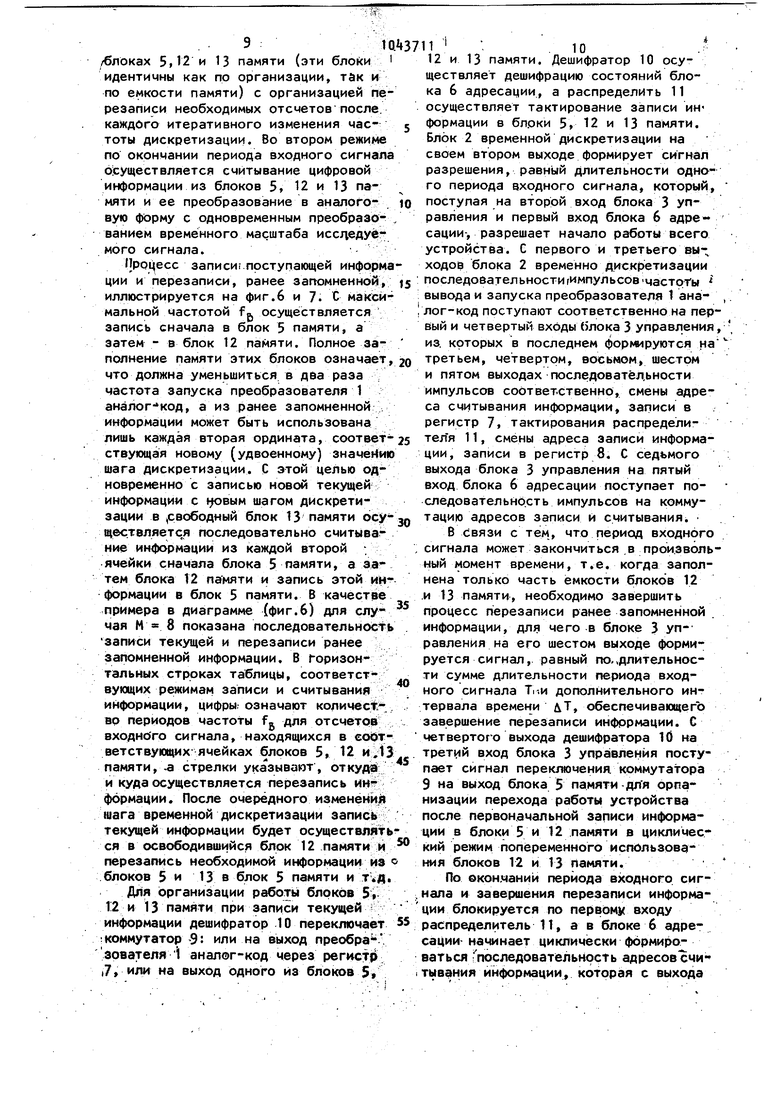

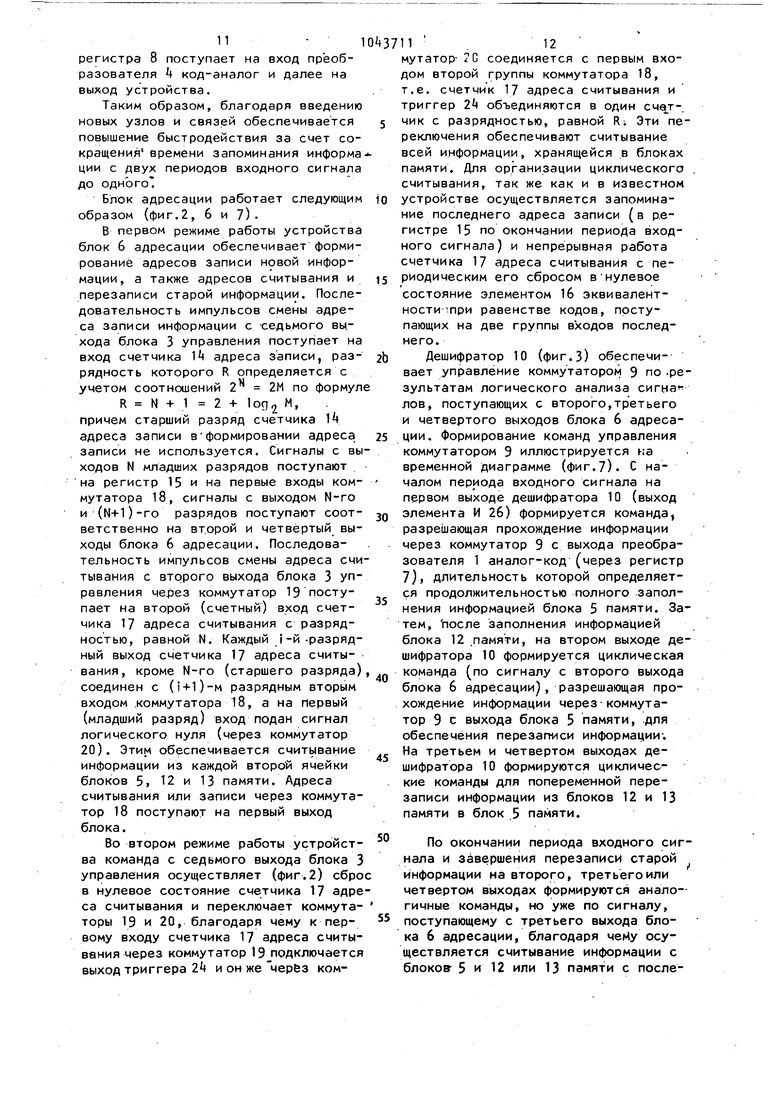

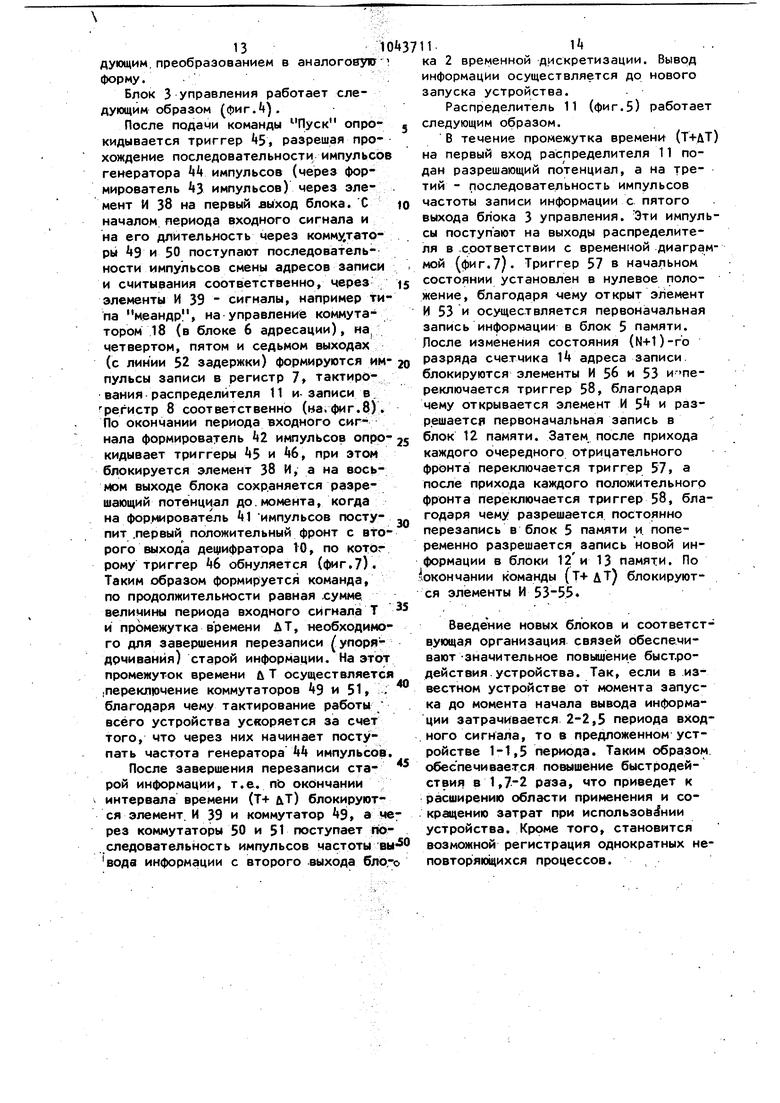

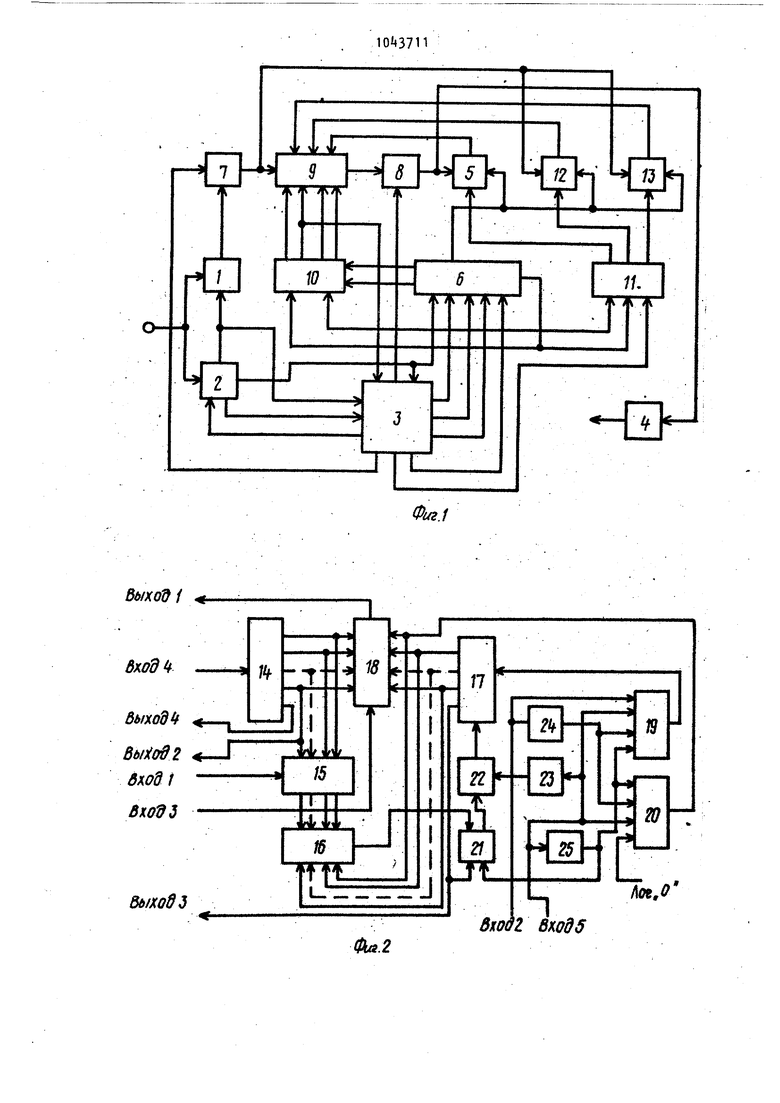

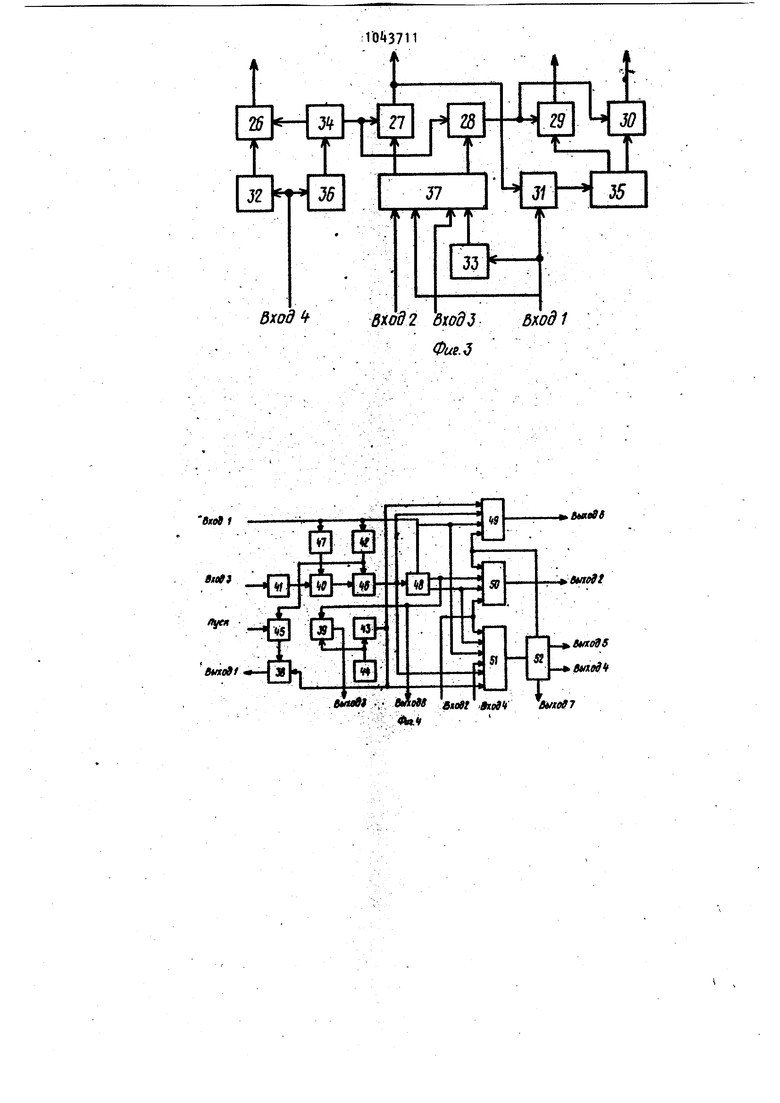

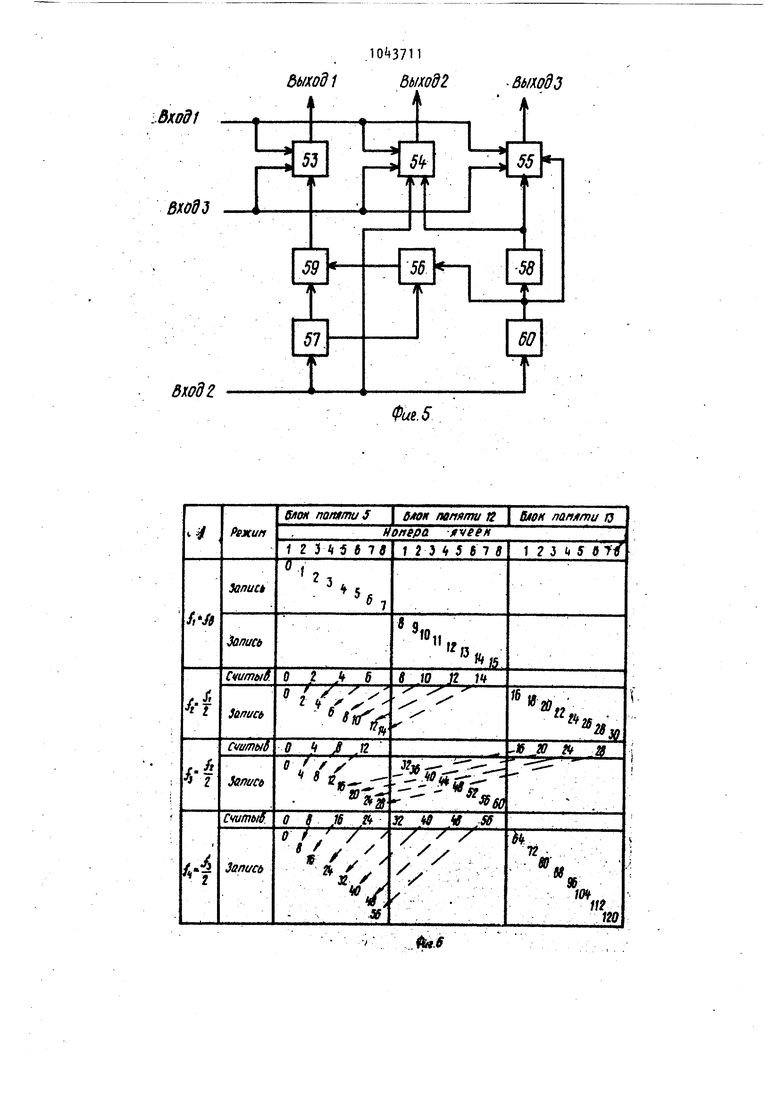

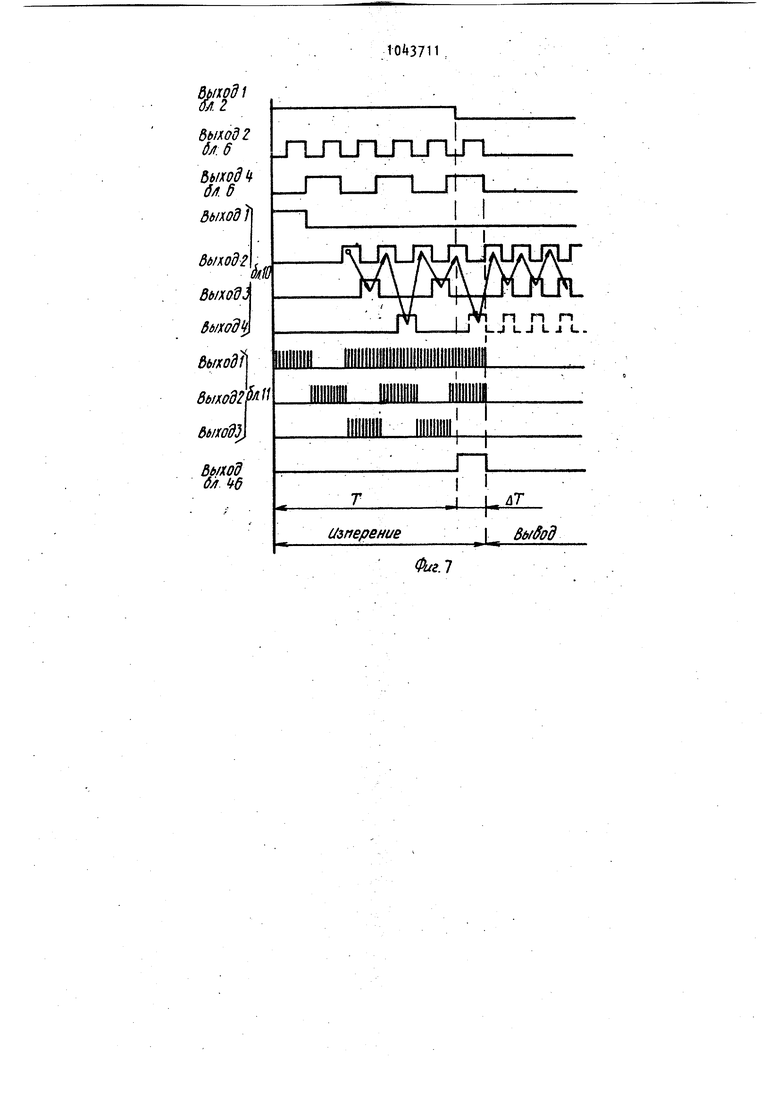

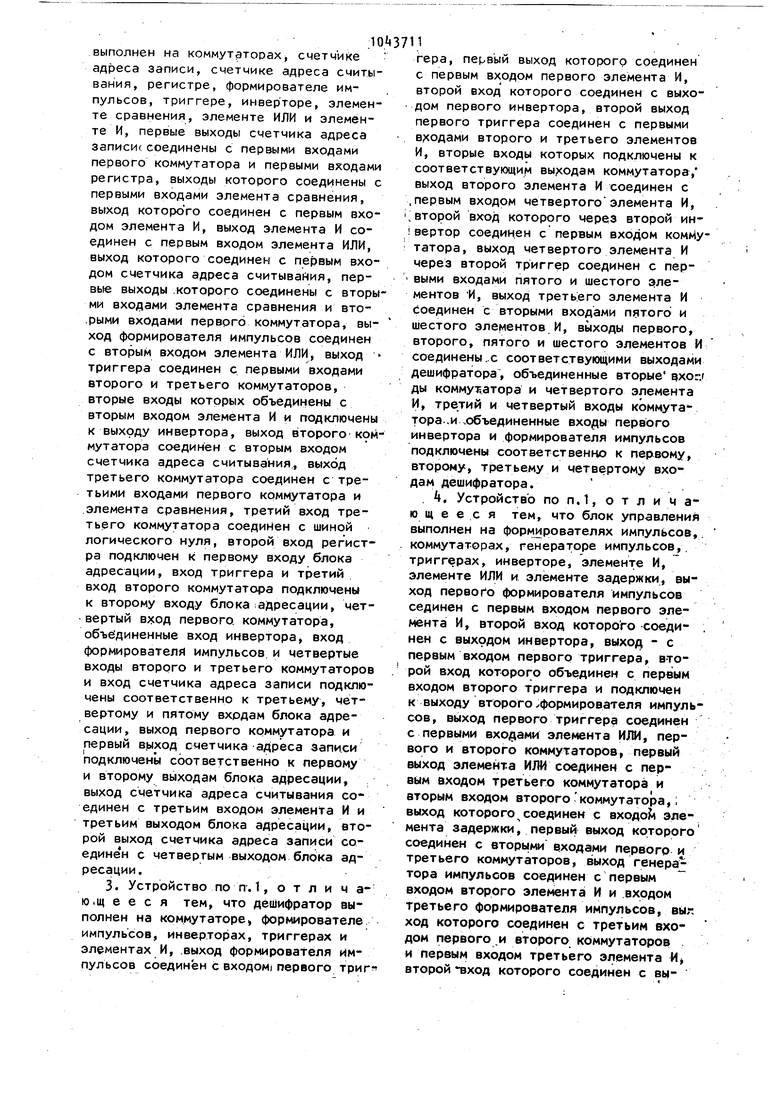

Изобретение относится к автоматике и вычислительной технике и предмазначено для согласования полосы вход ного сигнала с полосой пропускания анализирующей и измерительной аппаратуры. И.звестно устройство для временного сжатия сигналов, содеращее несколько петель накопления, с коммутатором и рециркуляционную линию задержки в каждой петле, используемую в качестве запоминающего устройства, сумматор, выход которого является выходом устройства. Устройство содержит также блок управления, входы элементов запоминания уровня напряжения.и вход коммутатора первой петли накопления объединены и образуют входную шину устройства } Однако известное устройство не может быть Использовано в задачах автоматического измерения характеристик периодических сигналов, так как не осуществляет выделение .периода входного сигнала. Кроме того, оно не определяет оптимальное число измеряемых ординат, на периоде сигнала и вследствие этого погрешность аппроксимации входного сигнала может оказаться выше допустимой, при этом устройство обладает низким быстродействием, так как требует предварительного и независимого нахождения величины периода. Наиболее близким к изобретению по технической сущности и достигаемому эффекту является устройство для временного сжатия входного сигнала, содержащее преобразователь анало -код, блок, временной дискретизации, блок определения периода вхсщного сигнала и блок умножения частоты, первые входы которых подключены к входу устройства, блок управления, преобразователь код-аналог, выход которого соединен с выходом устройства, блок памяти, первый вход которого подключен к первому ВЫХОДУ-блока адресации, первый вход последнего соединен е первым входом блока управления и с первым выходом блока временной дискре тизации первый, второй и третий выходы блока управления подключены к второму входу блока врем.енной дискретизации, к второму и третьему входам блока адресации соответственно, второй и третий выходы блока временной, дискретизации соединены с вторыми вхо дами бпока управления и преобразователя аналог-код, соответственно 2 - Недостатком данного устройства является невысокое быстродействие, обу словленное тем, что оно работает.в .три такта, а именно: определение значения периода входного сигнала; запись ординат сигнала на его периоде в блок памяти; вывод информации. Первые-два такта и определяют быстродействие устройства: на- запоминание входного сигнала (с проме хуточным . выделением периода и аиалого-цифро,вым преобразованием) необходимо не двух периодов.входного сигнала В ряде измерительных задач в инфранизком диапазоне частот это может оказаться недопустимым, что дополнительно приводит к ограничению .области применения., Цель изобретения - повышение быст родействия устройства. Поставленная цель достигается тем что в устройство для сжатия информации, содержащее преобразователь аналог-код, первый вход которого объеди нен с первым входом блока временной дискретизации и подключен к входу ус ройства, первый выход блока временно дискретизации соединен с вторым входом преобразователя аналог-код и , первым входом блока управления второй выход - с перЬым входом блока адресации и вторым входом блока управления, первый, второй и третий выходы которого соединены соответственно с вторым -ВХОДОМ блока временной дискретизации, вторым и третьим входами бло ка адресации, первый вход которого соединен с первым входом первого блока памяти, третий выход блока временной дискретизации соединен с четвертым h входом блока управления,.и преобразователь код-аналог, выход которого соединен с выходом устройства, введены .регистры записи, коммутатор, второй и ff третий блоки памяти, распределитель и дешифратор, четвертый выход блока управления соединен с первым входом первого регистра записи, второй вход которого соединен с выходом hpeo6pa3oвателя анало -код, выход - с первыми входами коммутатора, второго и третьего блоков памяти, вь1ход коммутато ра соединен с первым входом второго регистра записи, второй вход которого соединен с пятым выходом блока управления, выход - с входом преобразователя код-аналог и вторым входом первого блока памяти, выходы первого, второго, и третьего блоков памяти соединены соответственно с вторым, трет тьим и четвертым входами коммутатора, пятый, шестой и седьмой входы которого соединены соответственно с первым, вторым и третьим выходами дешифратора; четвертый выход которого соединен с восьмым входом коммутатора и третьим входом блока управления, шестой выход блока управления соединен с четвертым .входом блока адресации и первыми входами дешифратора и распределителя, седьмой выход - с пятым входом блока адресации, второй и третий выходы которого соединен соответственно с вторым и третьим входами дешифратора, четвертый выход блока адресации соединен с четвертым входом дешифратора и вторым входом распределителя, третий вход которого соединен с восьмым выходом блока управления, выходы распределителя соединены соответственно с третьим вхо дом первого блока памяти и вторыми входами второго и третьего блоков памяти, третьи входы которых подключены к первому выходу блока; адрес ;ции.: Кроме того, блок адресации выполнен на коммутаторах, счетчике адреса записи, счетчике адреса считывания, регистре, формирователе импульсов, триггере, инверторе, элементе сравнения, элементе ИJM и элементе И, первые выходы счетчика адреса записи соединены с первыми входами первого коммутатора и первыми входами регистра , выходы которого соединены с Оервыми входами элемента сравнения, выход которого соединен с первым входом Элемента И, выход элемента И соединен с первым входом элемента ИЛИ, выход . которого соединен с первым входом счетчика адреса считывания, первые выходы которого соединены с вторыми S10 входами элемента сравнения и вторыми входами первого коммутатора, выход формирователя импульсов соединен с . вторым входом элемента ИЛИ, выход триггера соединен с первыми входами второго и третьего коммутаторов, вто рые входы которых ,объединены с вторы входом элемента И и подключены к выходу инвертора, выход второго коммутатора соединен с вторым входом счетчика адреса считывания, выход третьего коммутатора соединен с, тре.тьими входами первого коммутатора и .элемента сравнения, третий вход третьего коммутатора соединен с шиной логи ческого нуля, второй вход регистра подключен к .первому входу бло ка, адресации, вход триггера и третий вход второго коммутатора подключены второму входу блока адресации, мет-. вертый вход первого коммутатора, объ диненные вход инвертора, вход формирователя импульсов и четвертые входы второго и третьего коммутаторов и вход счетчика адреса записи подключены соответственно к третьему, четвертому и пятому входам блока адресации, выход первого коммутатора и первый выход счетчика адреса записи подключены соответственно к первому и второму выходам блока адресации, .выход счетчика адреса считывания соединен с третьим входом элемента И и третьим выходом блока адресации, вто рой выход счетчика адреса записи соединен с четвертым выходом блока адресации. При этом дешифратор выполнен на коммутаторе, формирователе импульсов, инверторах, триггерах и элементах И выход формирователя импуль сов соединен с входом первого триггера, первый выход которого соединен с первым входом первого элементаИ, второй вход которого соединен с выходом первого инвертора, второй выход первого триггера соединен с первыми входами второго и третьего элементов И, вторые входы которых подключены к соответствующим выходам коммутатора, выход второго элемента И соединен с первым входом четвертог элемента И, второй вход которого через второй инвертор соединен с первы входом коммутатора, выход четвертого элемента И через второй триггер соединен с первыми входами пятого и ше того, элементов И, выход третьего эле мента И соединен с вторыми входами 1 .- 6 пятого и шестого элементов И, выходы первого,, второго, пятого и шестого элементов И соединены с соответствующими выходами дешифратора, объединенные вторые входы коммутатора и четвертого элемента И, третий и четвертый входы коммутатора и объединенные входы первого инвертора и формирователя импульсов подключены соответственно к первому, второ.му, третьему и четвертому входам дешифратора. Блок управления выполнен на формирователях импуль..сов, коммутаторах, . генераторе импульсов, триггерах, инверторе, элементах И, элементе ИЛИ и элементе задержки, выход первого фор-, мирователя импульсов соединен с первым входом первого элемента И, второй вход которого соединен с выходом инвертора, выход - с первым входом первого триггера, второй вход которого объединен с первым входом второго ,. триггера и подключен к выходу второго формирователя импульсов, выход первого триггера соединен с первыми входами элемента ИЛИ, первого и второго коммутаторов, первый выход элемента ИЛИ соединен с первым, входом третьего коммутатора и вторым входом второго коммутатора, выход которого соединен с входом элемента задержки, первый вы-, ход которого соединен с вторыми входами первого и третьего коммутаторов, выход генератора импульсов соединен с первым входом второго элемента И и входом третьего формирователя импуль-. сов, выход которого соединен .с. третьим входом первого и второго комму- таторов и первым входом-третьегоэлемента И, второй вход которого соединен с выходом второго триггера, второй вход которого подключен к шине Пуск, вход первого инвертора, вход второ-} го формирователя импульсов, второй вход элемента ИЛИ и черветрые входы первого и второго коммутаторов подключены к первому входу блока управления, объединенные третий вход третьего коммутатора и пятый вход второго коммутатора подключены к второму входу блока управления, вход первого формирователя импульсов и шестой вход второго коммутатора подключены соответственно к третьему и четвертому входам блока управления, выход третьего элемента И, выход третьего коммутатора, выход второго элемента И, второй, третий и четвертый выходы элемента задержки, выход первого коммутатора подключены соответственно к первому-седьмому выходам блока управления, второй выход элемента ИЛИ подключен к второму входу второго элемента И и восьмому выходу блока управления. Кроме того, распределитель выполнен на триггерах, инверторе, элементах И и элементе ИЛИ, первый выход первого триггера соединен с первым входом элемента ИЛИ, выход которого соединен с первым входом первого эле мента И, второй выход первого триггера соединен с первым входом второг элемента И, выход которого соединен с вторым входом элемента ИЛИ, выход инвертора соединен с вторым входом второго элемента И и первыми входами второго триггера и третьего элемента И, выход второго триггера соедине с.вторым входом третьего элемента И, и первым входом четвертого элемента И, объединенные вторые входы первого и четвертого элемента И и третий вхо третьего элемента И подключен к первому входу распределителя, объединен ные входы первого триггера и инверто ра и третий вход четвертого элемента И подключен к второму входу распределителя, объединенные третий вход первого элемента И и четвертые входы третьего и четвертого элементов И подключены к третьему входу распределителя, выходы первого, четвертого и третьего элементов И подклю)ены соответственно к первому, второму и третьему входам распределителя. На фиг.1 изображена структурная схема устройства для сжатия информации; на фиг.2 - пример выполнения блока адресации; дешифратора; блока управления; распределителя соответст венно; на фиг.6 - пример организации процессов записи и перезаписи информации в,блоках памяти; на фиг.7 и 8временныё диаграммы работы устройств Устройство для сжатия информации содержит (фиг.1) преобразователь 1 аналог-код, блок 2 временной дискретизации, блок 3 управления, преобразователь код-аналог, блок 5 памяти блок 6 адресации, первый 7 и второй 8 регистры записи, коммутатор 9, дешифратор 10, распределитель П, второй 12 и третий 13 блоки памяти. Блок 6 адресации выполнен (.2) на счетчике 1 адреса записи, регистре 15, элементе 16 сравнения, счетчике 17 адреса считывания, ком111 8 мутаторах 18-20, элементе И 21, элементе ИЛИ 22, формирователе 23 импульсов, триггере 2 и инверторе 25. Дешифратор 10 выполнен (фиг. на, элементах И , на инверторах 32 и 33, триггерах з4 и 35, формирователе Зб импульсов и коммутаторе 37 Блок 3 управления (фиг. ) выполнен) на элементах И 38-40, формирователях импульсов, генераторе импульсов, триггерах 5 и 46, инверторе 47, элементе КЛИ 48, коммутаторах 49-51, элементе 52 задержки. Распределитель (фиг.5) П выполнен на элементах И , триггерах 57 и 58, элементе ИЛИ 59 и инверторе 60. Устройство для сжатия (фиг,1) информации работает следующим образом. Входной периодический сигнал поступает на первые входы преобразователя 1 аналог-код и блока 2 временной дискретизации, первый из которых осуществляет аналого-цифровое преобразование входного сигнала, а второй формирует последовательность импульсов запуска преобразователя ;1. аналог-код. Блок 2 временной дискретизации выполнен и работает, например, аналогично известному устройству (последовательно включенные блоки определения периода и умножения частоты) . После запуска устройства (команда на шине Пуск в блоке 3.правления) блоком 2 осуществляется формирование частоты временной дискретизации входного сигнала таким образом, чтобы в течение одного периода входного сигнала было сформировано М -2М отсчетов. Минимальное количество отсчётов входного сигнала М на его периоде выбирает с я,-.и сходя из допустимой погрешности восстановления. При, этом на второй вход блока 2 временной дискретизации поступает последовательность импульсов с первого выхода блока 3 управления. Однако, в Отличие от известного устройства преобразование аналог-код осуществляется в течение одного периода входного сигнала одновременно с процессом итеративного формирования шага дискретизации. Работа устройства осуществляется в двух режимах. В первом режиме в течение одного периода входного сигнала осуществляется аналого-цифровое преобразование по итеративно формирующейся частоте дйс.кретизаиии и запоминание цифровых отсчетов в : /блоках 5,12 и 13 памяти (эти блоки идентичны как по организации, так и по емкости памяти) с организацией перезаписи необходимых отсчетов после, каждого итеративного изменения частоты дискретизации. Во втором режиме по окончании периода входного сигнала осуществляется считывание цифровой информации из блоков 5, 12 и 13 памяти и ее преобразование в аналогевую форму с одновременным преобразиванием временного масштаба иссдедувг мого сигнала. Процесс записи; поступающей информа ции и перезаписи, ранее запомненной, иллюстрируется на фиг.6 и 7. С максимальной частотой fjj осуществляется запись сначала в блок 5 памяти, а затем - а блок 12 памяти. Полное заполнение памяти этих блоков означает, что должна уменьшиться в два раза частота запуска преобразователя 1 аналог код, а из ранее запомненной информации может быть использована лишь каждая вторая ордината, соответствующая новому (удвоенному) значению шага дискретизации. С этой целью одновременно с записью новой текущей информации с «рвым шагом дискретизации в рвободный блок 13 памяти осу щвствляетс я последовательно считывание информации из каждой второй ячейки сначала блока 5 памяти, а затем блока 12 памяти и запись этой информации в блок 5 памяти. В качестве примера в диаграмме (фиг.6) для спучая М 8 показана последовательность записи текущей и перезаписи ранее запомненной информации. В горизонтальных строках таблицы, соответствующих режимам записи и считывания информации, ЦИФРЫ; означают количест.-. во периодов частоты fg для отсчетов входноТо сигнала, находящихся в соответствую1ф4Хячейках блоков 5, 12 и,13 памяти, -а стрелки указывают, откуда и куда осуществляется перезапись информации. После очерёдного изменений шага временной дискретизации запись текущей информации будет осуществлять ся в освободившийся блок 12 памяти и перезапись необходимой информации из .блоков 5 и 13 в блок 5 памяти и , Для организации работы блоков 5i 1:2 и 13 памяти при записи текущей информации дешифратор 10 переключает :коммутатор -9: или на выход преобразователя 1 аналог-код через регнст0 |7, или на выход одного из блоков 5, 10 1 12 и 13 памяти. Дешифратор 10 осуществляет дешифрацию состояний блока 6 адресации, а распределить 11 осуществляет тактирование записи ин формации в блоки 5 12 и 13 памяти. Блок 2 временной дискретизации на своем втором выходе формирует сигнал разрешения, равный Длительности одного периода входного сигнала, который, поступая на второй вход блока 3 управления и первый вход блока 6 адресации-, разрешает начало работы всего устройства, е первого и третьего выходов блока 2 временно дискретизации последовательностигимпульсовчастоты вывода и запуска преобразователя 1 ана- , ЛО1-код поступают соответственно на первый и четвертый входы блока 3 управления, из, которых в последнем формируются на третьем, четвертом, восьмом, шестом и пятом выходах последоватёл.ьности импульсов соответственно, смены адреса считывания информации, записи в регистр 7, тактирования распределителя 11, смены адреса записи информации, записи в регистр 8. С седьмого выхода блока 3 управления на пятый вход блока 6 адресации поступает последовательность импульсов на коммутацию адресов записи и считывания В Связи с тем, что период входного сигнала может закончиться ,в прои.звольный момент времени, т.е. когда заполнена только часть ёмкости блоков 12 .и 13 памяти, необходимо завершить процесс перезаписи ранее запомненной информации, для чего в блоке 3 Управления на его шестом выходе формируется сигнал, равный по, .длительности сумме длительности периода входного сигнала Ti-.и дополнительного интервала времени дТ, обеспечивающего завершение перезаписи информации. С четвертого выхода дешифратора 10 на третий вход блока 3 управления поступает сигнал переключения коммутатора 9 на выход блока 5 памяти-для организации перехода работы устройства после первоначальной записи информации в блоки 5 и 12 .памяти в циклический режим попеременного использования блоков 12 и 13 памяти. По екон.чаний периода входного сигнала и завершения перезаписи информации блокируется по первому входу распределитель 11, а в блоке б адресации- начинает циклически формироваться Гпоследовательность адресов счи- тывания информации, которая с выхода 11 регистра 8 поступает на вход преобразователя t код-аналог и далее на выход устройства. Таким образом, благодаря введению новых узлов и связей обеспечивается повышение быстродействия за счет сокращения времени запоминания информа ции с двух периодов входного сигнала до одного Блок адресации работает следующим образом (фиг,2, 6 и 7). В первом режиме работы устройства блок 6 адресации обеспечивает формирование адресов записи новой информации, а также адресов считывания и перезаписи старой информации. Последовательность импульсов смены адреса записи информации с -седьмого выхода блока 3 управления поступает на вход счетчика адреса записи, разрядность которого R определяется с учетом соотношений 2 2М по формул од 2, причем старший разряд счетчика И адреса записи вформировании адреса записи не используется. Сигналы с вы ходов N младших разрядов поступают на регистр 15 и на первые входы коммутатора 18, сигналы с выходом N-ro и (N+I)TO разрядов поступают соответственно на вт.орой и четвертый выходы блока 6 адресации. Последовательность импульсов смены адреса счи тывания с второго выхода блока 3 управления через коммутатор 19 поступает на второй (счетный) вход счетчика 17 адреса считывания с разрядностью, равной N. Каждый i-и-разрядный выход счетчика 17 адреса считывания, кроме N-ro (старшего разряда) соединен с (+1)-м разрядным вторым входом .коммутатора 18, а на первый (младший разряд) вход подан сигнал логического нуля (через коммутатор 20). Этим обеспечивается считывание информации из каждой второй ячейки блоков 5, 12 и 13 памяти. Адреса считывания или записи через коммутатор 18 поступают на первый выход блока. Во втором режиме работы устройства команда с седьмого выхода блока 3 управления осуществляет (фиг.2) сбро в нулевое состояние счетчика 17 адре са считывания и переключает коммутаторы 19 и 20, благодаря чему к первому входу счетчика 17 адреса считывания через коммутатор 19 подключается выход триггера и он же через комПмутатор- С соединяется с первым входом второй группы коммутатора 18, т.е. счетчик 17 адреса считывания и триггер 2 объединяются в один счет-. чик с разрядностью, равной Ri Эти переключения обеспечивают считывание всей информации, хранящейся в блоках памяти. Для организации циклического , считывания, так же как и в известном устройстве осуществляется запоминание последнего адреса записи (в регистре 15 по окончании периода входного сигнала) и непрерывная работа счетчика 17 адреса считывания с периодическим его сбросом внулевое состояние элементом 16 эквивалентности ;при равенстве кодов, поступающих на две группы входов последнего. Дешифратор 10 (фиг.З) обеспечивает управление коммутатором 9 по .результатам логического анализа сигна лов, поступающих с второго,третьего и четвертого выходов блока 6 адресации. Формирование команд управления коммутатором 9 иллюстрируется на временной Диаграмме (фиг.7). С началом периода входного сигнала на первом выходе дешифратора 10 (выход элемента И 26) формируется команда, разрешающая прохождение информации через коммутатор 9 с выхода преобразователя 1 аналог-код (через регистр 7), длительность которой определяется продолжительностью полного заполнения информацией блока 5 памяти. Затем, после заполнения информацией блока 12 .памяти, на втором выходе дешифратора 10 формируется циклическая команда (по сигналу с второго выхода блока 6 адресации, разрешающая прохождение информа.ции через коммутатор 9 с выхода блока 5 памяти, для обеспечения перезаписи информации; На третьем и четвертом выходах дешифратора 10 формируются циклические команды для попеременной перезаписи информации из блоков 12 и 13 памяти в блок 5 памяти. По окончании периода входного сигнала и завершения перезаписи старой информации на второго, третьего или четвертом выходах формируются аналогичные команды, но уже по сигналу, поступающему с третьего выхода блока 6 адресации, благодаря чему осуществляется считывание информации с блоков- 5 и 12 или 13 памяти с последующим.преобразованием в аналоговуяу форму. Блок 3 управления работает следующим образом (фигЛ). После подачи команды Пycк опро кидывается триггер 45, разрешая прохождение последовательности импульсо генератора импульсов (через формирователь З импульсов) через элемент И 38 на первый выход блока. С началом периода входного сигнала и на его длительность через комм таторы kS и 50 поступают последовательности импульсов смены адресов записи и считывания соответственно, через элементы И 39 - сигналы, например ти па меандр , на управление коммутатором 18 (в блоке 6 адресации), на четвертом, пятом и седьмом выходах (с линии 52 задержки) формируются им пульсы записи в регистр 7 тактирования распределителя 11 и- записи в регистр 8 соответственно (на.фиг.8) По окончании периода входного сигнала формирователь k2 импульсов опро кидывает триггеры 5 и 46, при этом блокируется элемент 38 И, а на восьмом выходе блока сохраняется разрешающий потенциал до.момента, когда на фор.мирователь kl импульсов поступит .первый положительный фронт с Bto рого выхода дешифратора 10, по котог рому триггер Ц6 обнуляется (фиг,7). Таким образом формируется команда, по продолжительности равная .сумме величины периода входного сигнала Т и промежутка времени AT, необходимо го для завершения перезаписи (упорядочивания) старой информации. На этот промежуток времени ft Т осуществляется .переключение коммутаторов k3 и 51, / благодаря чему тактирование работы всего устройства ускоряется за счет того, что через них начинает поступать частота генератора (4 импульсов После завершения перезаписи старой информации, т.е. пЬ окончании интервала времени (Т+ лТ) блокируются элемент. И 39 и коммутатор kS, а че рез коммутаторы 50 и 51 поступает по . следовательность импульсов частоты вы вода информации с второго .выхода бло, ка 2 временной дискретизации. Вывод информации осуществляется до нового запуска устройства. Распределитель 11 (фиг.5) работает следующим образом. В течение промежутка времена (Т+ДТ) на первый вход распределителя 11 подан разрешающий потенциал, а на третий - последовательность импульсов частоты записи информации с пятого выхода блока 3 управления. Эти импульсы поступают на выходы распределителя в .соответствии с временной диаграммой (фиг.7). Триггер 57 в начальном состоянии установлен в нулевое положение, благодаря чему открыт элемент И 53 и осуществляется первоначальная запись информации в блок 5 памяти. Лосле изменения состояния (N+1)-rb Разряда счетчика И адреса записи блокируются элементы И 5б и 53 и-переключается триггер 58, благодаря чему открывается элемент И 5 и разрешается первоначальная запись в блок 12 памяти. Затем, после прихода каждого очередного отрицательного фронта переключается триггер 57 а после прихода каждого положительного фронта переключается триггер 58, благодаря чему разрешается постоянно перезапись в блок 5 памяти и. попеременно разрешается запись новой информации в блоки 12и 13 памяти. По окончании команды (+ ДТ) блокируются элементы И 53-55. Введение новых блоков и соответствующая организация связей обеспечивают -значительное повышение быстродействия, устройства. Так, если в известном устройстве от момента запуска до момента начала вывода информации затрачивается 2-2,5 периода входного сигнала, то в предложенном устройстве 1-1,5 периода. Таким образом, обеспечивается повышение быстродействия в 1,7-2 раза, что приведет к расширению области применения и сокращению затрат при использовании устройства. Кроме того, становится возможной регистрация однократных неповторяющихся процессов.

Rxod

ВМЛ9 ... вЛвдв .ixoav

. л . L

J

Biiod2 вкодд: dwdl Фие.5

ttKoSe

I

Otfxef

входд

dxodZ

Фиг. 5

jnJOJ LJTJ-Uri

с/зперение

п n n

J L.J U J L J с.

iiiiHi iiiiHHiii

гт

1I 47

I Выдод Сг San Зап Сг %/; I I I I

ЗапРг

ЗапРг.г

/А

г.8 Сг Зап I г

Авторы

Даты

1983-09-23—Публикация

1982-06-18—Подача