1

(61) 888165

(21)4319673/24-24

(22)19.10.87

(46) 15.03.90. Вкш. № 10

(71)Всесоюзный научно-исследовательский институт электроизмерительных приборов

(72)Г.Г.Живилов

(53)621.398(088.8)

(56)Авторское свидетельство СССР № 888165, кл. G 08 С 19/00, 1978.

(54)УСТРОЙСТВО ДЛЯ ВРЕМЕННОГО СЖАТИЯ ВХОДНОГО СИГНАЛА

(57)Изобретение относится к автоматике и вычислительной технике,предназначено для согласования полосы входного сигнала с полосой пропускания анализирующей и измерительной аппаратуры и является усовершенствованием известного устройства по

чГ/

авт.св. № 888165. Изобретение позволяет за счет автоматического переключения пределов измерения сократить время поиска необходимого предела измерения и тем самым повысить быстродействие устройства. Устройство содержит преобразователь 1 аналог- код, оперативный запоминающий блок 2, преобразователь 3 код-аналог, блок 4 определения периода входного сигнала, блок 5 умножения частоты, блок 6 адресации, блок 7 управления, узел 8 автоматического выбора предела измерений, содержащий аналоговые коммутаторы 9, 10, блок 11 элементов сравнения, блок 12 уставок, блоки 13 и 14 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, цифровой компаратор 15, регистр 16, элемент И 17, триггер 18, дешифратор 19, блок 20 усилителей. 1 з.п. ф-лы, 4 ил.

о SS

(Л

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой вольтметр | 1986 |

|

SU1404967A2 |

| Аналого-цифровой преобразователь | 1986 |

|

SU1478330A1 |

| Многоканальное устройство для сбора данных | 1983 |

|

SU1095163A1 |

| Устройство для автоматического контроля больших интегральных схем | 1986 |

|

SU1529220A1 |

| Устройство для автоматического регулирования температуры | 1988 |

|

SU1645945A1 |

| Система для контроля электрических параметров логических блоков | 1988 |

|

SU1725230A1 |

| Устройство для формирования речевых сообщений | 1979 |

|

SU942118A1 |

| Устройство для сжатия информации | 1987 |

|

SU1529043A1 |

| Многоканальный преобразователь угол-фаза-код | 1983 |

|

SU1120385A1 |

| СТЕНД ДЛЯ ИЗУЧЕНИЯ ЭЛЕКТРОННЫХ СРЕДСТВ АВТОМАТИЗАЦИИ | 2005 |

|

RU2279718C1 |

Изобретение относится к автоматике и вычислительной технике, предназначено для согласования полосы входного сигнала с полосой пропускания анализирующей и измерительной аппаратуры и является усовершенствованием известного устройства по авт.св. N 888165. Изобретение позволяет за счет автоматического переключения пределов измерения сократить время поиска необходимого предела измерения и тем самым повысить быстродействие устройства. Устройство содержит преобразователь 1 аналог-код, оперативный запоминающий блок 2, преобразователь 3 код-аналог, блок 4 определения периода входного сигнала, блок 5 умножения частоты, блок 6 адресации, блок 7 управления, узел 8 автоматического выбора предела измерений, содержащий аналоговые коммутаторы 9, 10, блок 11 элементов сравнения, блок 12 уставок, блоки 13 и 14 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, цифровой компаратор 15, регистр 16, элемент И 17, триггер 18, шифратор 19, блок 20 усилителей. 1 з.п. ф-лы, 4 ил.

Q

8

СЛ СП О СП СП

со

N)

Фыг.1

Изобретение относится к автоматике и вычислительной технике и предназначено для согласования полосы входного сигнала с полосой пропускания анализирующей и измерительной аппаратуры.

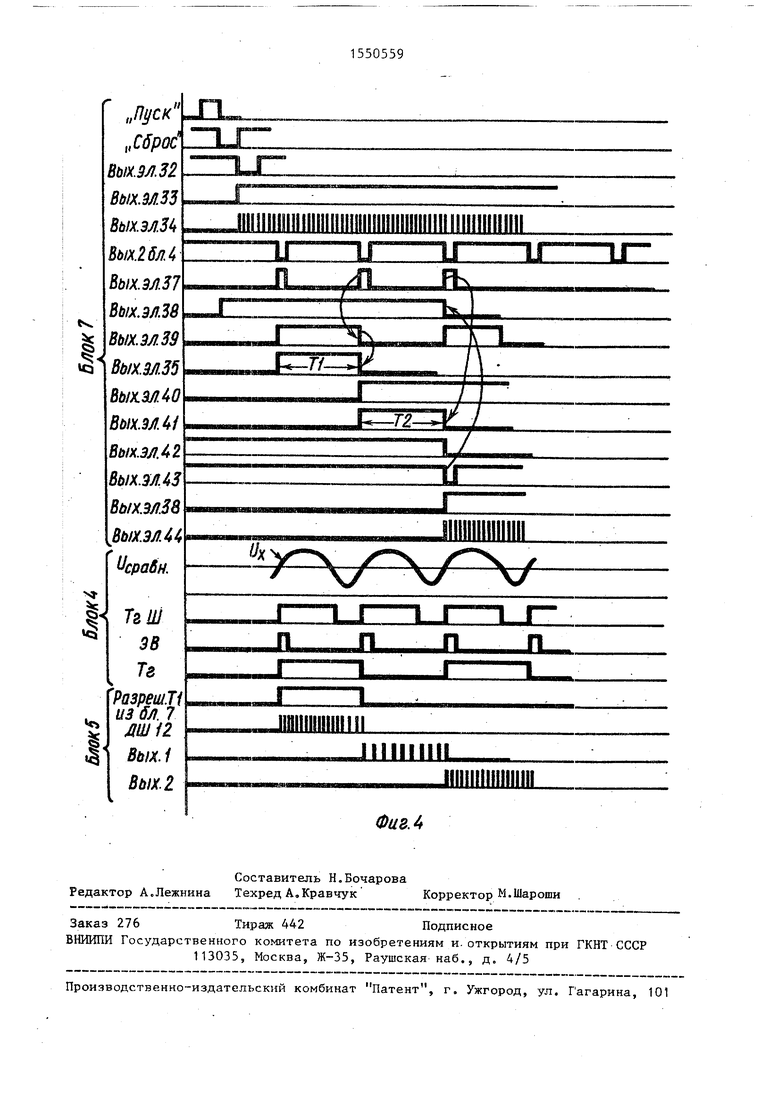

Цель изобретения - повышение быстродействия устройства. На фиг.1 представлена блок-схема предлагаемого устройства;на фиг,2 - iсхема блока адресации; на фиг,3 схема блока управленияj на фиг.4 - временные диаграммы работы блоков 4, 5, 7 устройства. i

Устройство (фиг.1) содержит преобразователь 1 аналог-код, оперативный запоминающий блок 2, преобразователь 3 код-аналог, блок 4 определения периода входного сигнала, блок 5 умножения частоты, блок 6 адресации, блок 7 управления, узел 8 автоматического выбора предела измерения, включающий первый 9 и второй 10 аналоговые коммутаторы, блок 11 элементов сравнения, блок 12 уставок первьй и второй блоки 13 и 14 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, цифровой компаратор 15, регистр 16, элемент И 17, триггер 18, шифратор 19 и блок 20 усилителей.

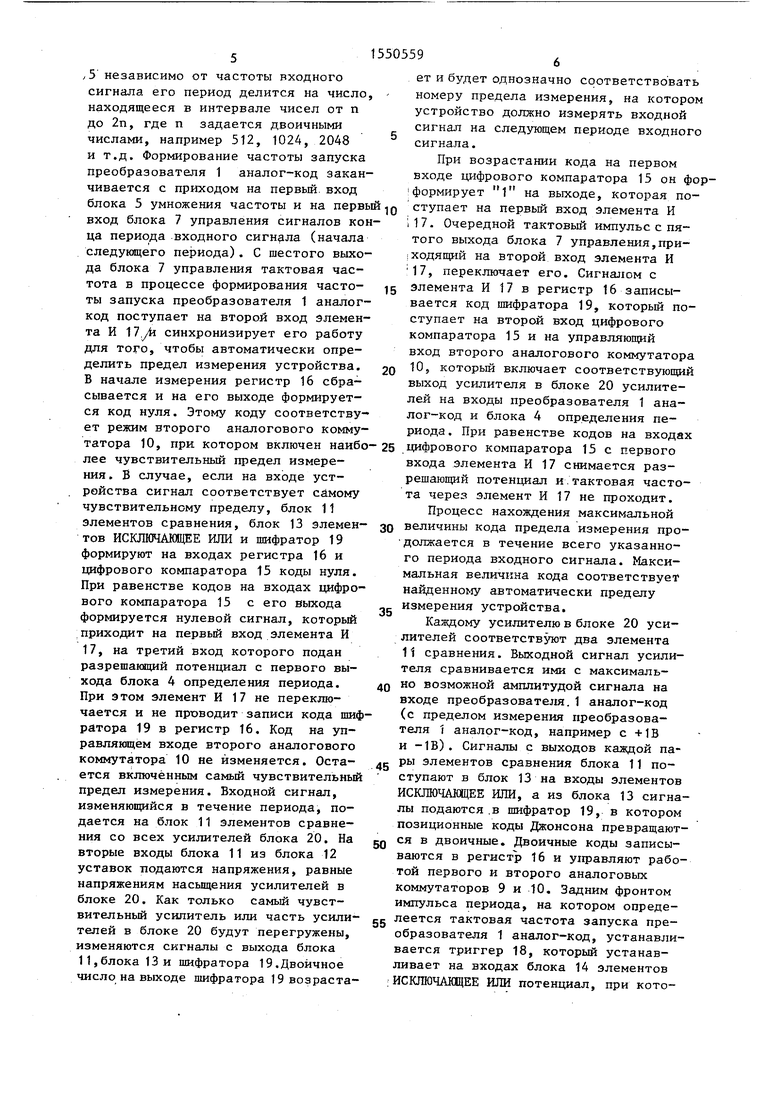

Блок 6 адресации (фиг.2) содержит элемент 21 сравнения, регистр 22, элементы ИЛИ 23 и 24, элементы И 25 и 26, инвертор 27, триггеры 27 и 28 со счетным входом, формирователь 30 |импульса и счетчик 31.

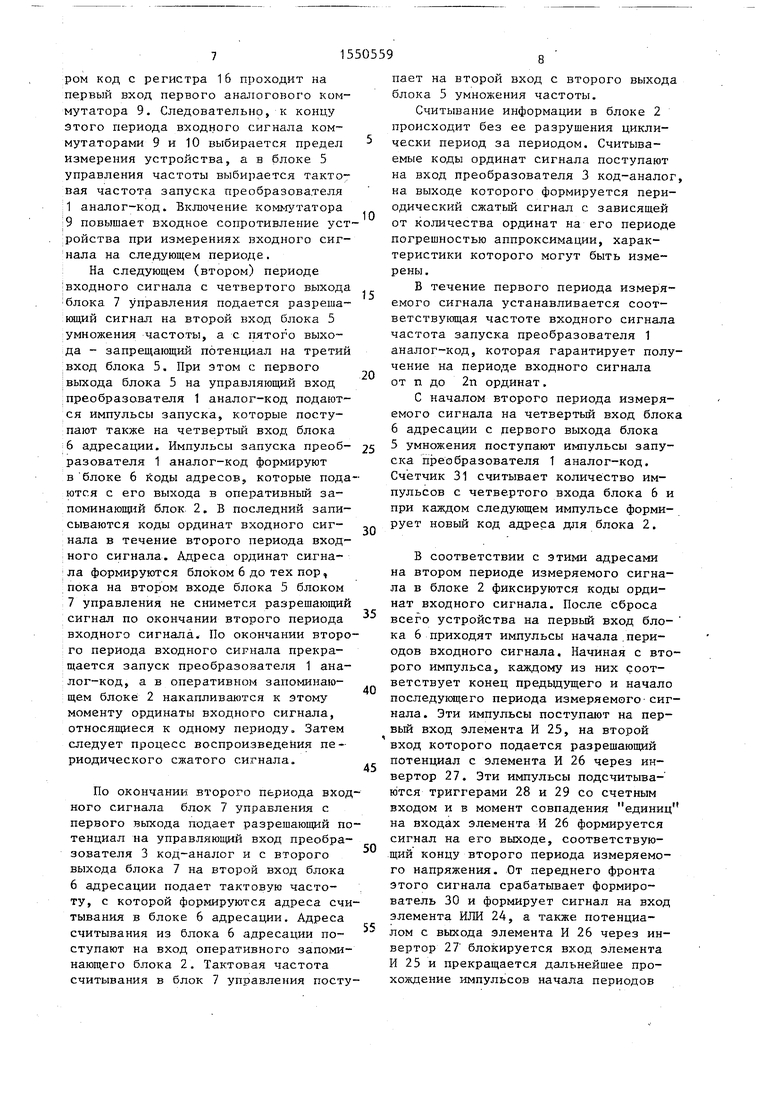

Блок 7 управления (фиг.З) содержит формирователь 32 импульса, триггер 33, элементы И 34 и 35, генерато 36 тактовой частоты, элемент И 37„ триггеры 38-40, элементы И 41 и 42, формирователь 43 импульса, элемент И 44 и формирователь 45 импульса.

Устройство для временного сжатия входного сигнала (фиг.1) работает следующим образом.

После запуска и сброса всех его блоков выходы блока 5 умножения частоты заперты сигналами блока 7 управления. С шестого выхода блока 7 управления не поступают тактовые импульсы на делитель частоты блока 5, а на второй вход блока 5 подается запрещающий потенциал с четвертого выхода блока 7 управления,, Сигналом с триггера 18 блок 14 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ устанавливается так,

0

5

0

5

0

5

0

5

0

5

что его сигналами открываются все ключи первого аналогового коммутатора 9 и на входы усилителей в блоке 20 усилителей подается входной сигнал. Число усилителей в блоке 20 усилителей равно числу пределов измерения устройства. Усилители отличаются один от другого коэффициентом усиления. Выходы усилителей подключены к входам второго аналогового коммутатора 10 и блока 11 элементов сравнения. От воздействия входного сигнала в общем случае часть усили- тепей перегружается (на их выходе формируется сигнал ограничения от перегрузки, который по величине больше номинального сигнала на соответствующем пределе), а часть усилителей оказывается неперегруженными. Из неперегруженных усилителей работать в линейном режиме для проведения измерения устройством для временного сжатия входного сигнала должен усилитель, коэффициент усиления которого отличается в меньшую сторону от ближайшего перегруженного усилителя. Усилители с меньшим коэффициентом усиления работать не должны, так как могут обеспечить измерения только с большей погрешностью.

Второй аналоговый коммутатор 10 перед началом измерения кодом с регистра 16 включен на самый чувствительный предел измерения. Измеряемый сигнал с выхода второго аналогового коммутатора 10 поступает на входы блока 4 определения периода и преобразователя 1 аналог-код. В блоке 4 определения периода выделяются периоды входного сигнала и формируются разрешающие сигналы на его первом и втором выходах.

После запуска устройства импульс начала периода входного сигнала с второго выхода блока 4 определения периода подается на первый вход блока 7 управления, с шестого выхода которого тактовая частота поступает на четвертый вход блока 5 умножения частоты, а с пятого выхода блока 7 подается разрешающий потенциал на третий вход блока 5. С первого выхода блока 4 на первый вход блока 5 подается импульс, по длительности равный периоду входного сигнала. Блок 5 формирует частоту запуска преобразователя 1 аналог-код так, что при двоичной сетке частот в блоке

/5 независимо от частоты входного сигнала его период делится на число, находящееся в интервале чисел от п до 2п, где п задается двоичными числами, например 512, 1024, 2048 и т.д. Формирование частоты запуска преобразователя 1 аналог-код заканчивается с приходом на первый вход

блока 5 умножения частоты и на первый ступает на первый вход элемента И

вход блока 7 управления сигналов конца периода входного сигнала (начала следующего периода). С шестого выхода блока 7 управления тактовая частота в процессе формирования частоты запуска преобразователя 1 аналог- код поступает на второй вход элемента И 17уя синхронизирует его работу для того, чтобы автоматически определить предел измерения устройства. В начале измерения регистр 16 сбрасывается и на его выходе формируется код нуля. Этому коду соответствует режим второго аналогового комму15

20

татора 10, при котором включен наибо- 25 цифрового компаратора 15 с первого

лее чувствительный предел измерения. В случае, если на входе устройства сигнал соответствует самому чувствительному пределу, блок 11 элементов сравнения, блок 13 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ и шифратор 19 формируют на входах регистра 16 и цифрового компаратора 15 коды нуля. При равенстве кодов на входах цифрового компаратора 15 с его выхода формируется нулевой сигнал, который приходит на первый вход элемента И 17, на третий вход которого подан разрешающий потенциал с первого выхода блока 4 определения периода. При этом элемент И 17 не переключается и не проводит записи кода шифратора 19 в регистр 16. Код на управляющем входе второго аналогового коммутатора 10 не изменяется. Остается включенным самый чувствительный предел измерения. Входной сигнал, изменяющийся в течение периода, подается на блок 11 элементов сравнения со всех усилителей блока 20. На вторые входы блока 11 из блока 12 уставок подаются напряжения, равные напряжениям насыщения усилителей в блоке 20. Как только самый чувствительный усилитель или часть усили-gg леется тактовая частота запуска пре- телей в блоке 20 будут перегружены, образователя 1 аналог-код, устанавли- изменяются сигналы с выхода блока вается триггер 18, который устанав- 11,блока 13 и шифратора 19.Двоичное ливает на входах блока 14 элементов число на выходе шифратора 19 возраста- ИСКЛЮЧАЮЩЕЕ ИЛИ потенциал, при котоет и будет однозначно соответствовать номеру предела измерения, на котором устройство должно измерять входной сигнал на следующем периоде входного сигнала.

При возрастании кода на первом входе цифрового компаратора 15 он фор- формирует 1 на выходе, которая по5

0

0

5

входа элемента И 17 снимается разрешающий потенциал и тактовая частота через элемент И 17 не проходит. Процесс нахождения максимальной величины кода предела измерения продолжается в течение всего указанного периода входного сигнала. Максимальная величина кода соответствует найденному автоматически пределу измерения устройства.

Каждому усилителю в блоке 20 усилителей соответствуют два элемента 11 сравнения. Выходной сигнал усилителя сравнивается ими с максималь- 0 но возможной амплитудой сигнала на входе преобразователя.1 аналог-код (с пределом измерения преобразователя 1 аналог-код, например с +1В и -1В). Сигналы с выходов каждой пары элементов сравнения блока 11 поступают в блок 13 на входы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, а из блока 13 сигналы подаются в шифратор 19, в котором позиционные коды Джонсона превращаются в двоичные. Двоичные коды записываются в регистр 16 и управляют работой первого и второго аналоговых коммутаторов 9 и 10. Задним фронтом импульса периода, на котором опреде5

0

ром код с регистра 16 проходит на первый вход первого анапогового коммутатора 9. Следовательно, к концу этого периода входного сигнала коммутаторами 9 и 10 выбирается предел измерения устройства, а в блоке 5 управления частоты выбирается тактовая частота запуска преобразователя 1 аналог-код. Включение коммутатора 9 повышает входное сопротивление устройства при измерениях, входного сигнала на следующем периоде.

На следующем (втором) периоде входного сигнала с четвертого выхода блока 7 управления подается разрешающий сигнал на второй вход блока 5 умножения частоты, а с пятого выхода - запрещающий потенциал на третий вход блока 5. При этом с первого выхода блока 5 на управляющий вход преобразователя 1 аналог-код подаются импульсы запуска, которые поступают также на четвертый вход блока

6адресации. Импульсы запуска преобразователя 1 аналог-код формируют

в блоке 6 коды адресов, которые подаются с его выхода в оперативный запоминающий блок 2. В последний записываются коды ординат входного сигнала в течение второго периода входного сигнала. Адреса ординат сигнала формируются блоком 6 до тех пор, пока на втором входе блока 5 блоком

7управления не снимется разрешающий сигнал по окончании второго периода входного сигнала. По окончании второго периода входного сигнала прекращается запуск преобразователя 1 аналог-код, а в оперативном запоминающем блоке 2 накапливаются к этому моменту ординаты входного сигнала, относящиеся к одному периоду. Затем следует процесс воспроизведения периодического сжатого сигнала.

По окончании второго периода входного сигнала блок 7 управления с первого выхода подает разрешающий потенциал на управляющий вход преобразователя 3 код-аналог и с второго выхода блока 7 на второй вход блока 6 адресации подает тактовую частоту, с которой формируются адреса считывания в блоке 6 адресации. Адреса считывания из блока 6 адресации поступают на вход оперативного запоминающего блока 2. Тактовая частота считывания в блок 7 управления посту0

5

0

пает на второй вход с второго выхода блока 5 умножения частоты.

Считывание информации в блоке 2 происходит без ее разрушения цикли- чески период за периодом. Считываемые коды ординат сигнала поступают на вход преобразователя 3 код-аналог, на выходе которого формируется периодический сжатый сигнал с зависящей от количества ординат на его периоде погрешностью аппроксимации, характеристики которого могут быть измерены.

В течение первого периода измеряемого сигнала устанавливается соответствующая частоте входного сигнала частота запуска преобразователя 1 аналог-код, которая гарантирует получение на периоде входного сигнала от п до 2п ординат.

С началом второго периода измеряемого сигнала на четвертый вход блока 6 адресации с дервого выхода блока 5 5 умножения поступают импульсы запуска преобразователя 1 аналог-код. Счетчик 31 считывает количество импульсов с четвертого входа блока 6 и при каждом следующем импульсе форми- рует новый код адреса для блока 2.

В соответствии с этими адресами на втором периоде измеряемого сигнала в блоке 2 фиксируются коды ординат входного сигнала. После сброса всего устройства на первый вход блока 6 приходят импульсы начала периодов входного сигнала. Начиная с второго импульса, каждому из них соответствует конец предыдущего и начало последующего периода измеряемого сигнала. Эти импульсы поступают на первый вход элемента И 25, на второй вход которого подается разрешающий потенциал с элемента И 26 через инвертор 27. Эти импульсы подсчитываются триггерами 28 и 29 со счетным входом и в момент совпадения единиц на входах элемента И 26 формируется сигнал на его выходе, соответствующий концу второго периода измеряемого напряжения. От переднего фронта этого сигнала срабатывает формирователь 30 и формирует сигнал на вход элемента ИЛИ 24, а также потенциа- 5 лом с выхода элемента И 26 через инвертор 27 блокируется вход элемента И 25 и прекращается дальнейшее прохождение импульсов начала периодов

5

0

5

0

tизмеряемого сигнала на выходы счетных триггеров 28 и 29. Поступивший на вход элемента ИЛИ 24 импульс формирователя 30 производит запись кода счетчика 31 в регистр 22. Этот код соответствует максимальному числу зафиксированных в блоке 2 ординат входного сигнала.

После записи кода в регистр 22 срабатывает элемент 21 сравнения и своим выходным сигналом через элемен ИЛИ 23 сбрасывает счетчик 31 адреса в нуль.

Блок 7 сигналом с шестого выхода, соединенного с четвертым входом блока 5, запирает первый выход блока

5,и частота запуска блока 1 больше не поступает на четвертый вход блока

Снова формируются счетчиком 31 ко ды адресов ординат сигнала, максималный код которых записан в регистр 22. По достижении счетчиком 31 кода, записанного в регистре 22, на вход преобразователя 3 код-аналог последовательно подаются все записанные в блоке 2 коды ординат на одном периоде входного сигнала. Из блока 2 коды считываются без разруше- ния информации. Как только код счетчика 31 становится равным коду регистра 22, срабатывает элемент 21 сравнения и сбрасывает счетчик в нуль. Так как на вход счетчика 31 с

третьего входа блока 6 продолжают поступать счетные импульсы, процесс вывода информации из блока 2 продолжается. Такой процесс происходит циклически, период за периодом, до следующего запуска устройства, при ко- тором произойдет запись нулевого кода в регистр 22.

Блок 7 управления работает следующим образом.

Сигнал Пуск от внешнего устройства (или формируемый кнопкой на передней панели прибора) подается на формирователь 32, с выхода которого снимается сигнал общего сброса,который обнуляет все триггеры и поступает на второй выход блока 7. От заднего фронта сигнала сброса срабатывает формирователь 32, который своим сигналом устанавливает триггер 33. Вы

...

j,

5 0

35

40

«с

0

ходной сигнал триггера 33 поступает на первые входы элементов И 34 и 35. С выхода элемента И 34 на пятый выход блока 7 управления подается тактовая частота, формируемая генератором 36.

В блоке 4 определения периода происходит определение моментов начала одного периода за другим и с его второго выхода импульсы начала периодов измеряемого сигнала поступают на первый вход блока 7, а в нем - на первый вход элемента И 37, на второй вход которого подается разрешаю- .щий потенциал с триггера 38.

Первьй импульс, прошедший через элемент И 37, переключает по счетному входу триггер 39, прямой выход которого подключен к второму входу элемента И 35. Инверсный выход триггера 40 подключен к третьему входу элемента И 35. При переключении трш- гера 39 срабатывает элемент И 35 и .посылает на четвертый выход блока 7 разрешающий потенциал на время первого периода входного сигнала. Разрешающий потенциал с четвертого выхода блока 7 снимается при приходе следующего импульса начала периода на первый вход элемента И 37. Этот импульс сбрасывает триггер 39 и устанавливает по счетному входу триггер 40, который снимает разрешающий потенциал с третьего входа элемента И 35. При этом на входах элемента И 41 оказываются разрешающие потенциалы с прямого выхода триггера 40 и инверсного выхода триггера 39. С выхода элемента И 41 на шестой выход блока 7 поступает, разрешающий по- |тенциал на время второго периода измеряемого сигнала. Разрешающий потенциал с шестого выхода блока 7 снимается при приходе третьего импульса начала периода входного сигнала на первый вход элемента И 37, от которого переключится в 1 триггер 39. Как только переключится триггер 39, на входы элемента И 42 при ;ходят разрешающие потенциалы, от которых на его выходе появляется сигнал, соответствующий концу второго периода измеряемого сигнала. Выходной сигнал элемента И 42 возбуждает формирователь 43, который своим сигналом устанавливает триггер 38. С выхода триггера 38 устанавливается разрешающий потенциал на пепвом выходе блока 7, который подается на преобразователь 3 код-аналог.

С инверсного выхода триггера 38 по второму входу запирается элемент И 37, ас прямого выхода триггера 38 на первый вход элемента И 44 приходит разрешающий потенциал. С второго входа блока 7 на второй вход элемента И 44 приходит частота считывания, которая, пройдя элемент И 44, поступает на третий выход блока 7 и подается на второй вход блока 6 адресации для формирования сжатого во времени сигнала.

формула изобретения

усилителей, блок элементов сравнения, блок уставок, блоки элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, шифратор, цифровой компаратор, регистр, триггер и элемент И, выход первого аналогового коммутатора через блок усилителей соединен с первым входом второго аналогового коммутатора и соответствующими первыми входами блока элементов сравнения, вторые входы которого подключены к соответствующим выходам блока уставок , выходы блока элементов сравнения соединены с соответствующими входами первого блока элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, выходы которого подключены к соответствующим входам шифратора, выход которого соединен с первыми входами цифрового компаратора и регистра, выход регистра является вторым выходом узла и подключен к первому входу второго блока элементов ИСКЛЮЧАЮЩЕЕ ИЛИ и вторым входам цифрового компаратора и второго аналогового коммутатора, выход которого является первым выходом узла, выход цифрового компаратора соединен с первым входом элемента И, выход которого соединен с вторым входом регистра, выход триггера соединен с вторым входом второго блока элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого соединен с первым входом первого аналогового коммутатора,второй вход которого является первым входом узла, первый вход триггера и третий вход регистра объединены и являются вторым входом узла, второй вход элемента И является третьим входом узла, второй вход триггера и третий вход элемента И объединены и являются четвертым входом узла.

л

6SSOSSI

Авторы

Даты

1990-03-15—Публикация

1987-10-19—Подача