(54) УСТРОЙСТВО ДЛЯ СЖАТИЯ ИНФОРМАЦИИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сжатия информации | 1987 |

|

SU1529043A1 |

| Устройство для сжатия информации | 1982 |

|

SU1043711A1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ ИНФОРМАЦИИ В АДАПТИВНЫХ ТЕЛЕМЕТРИЧЕСКИХ СИСТЕМАХ | 1995 |

|

RU2103745C1 |

| УСТРОЙСТВО АВТОМАТИЧЕСКОГО ПОИСКА КАНАЛОВ РАДИОСВЯЗИ | 2014 |

|

RU2563145C1 |

| Многоканальное устройство для регистрации | 1985 |

|

SU1322156A1 |

| ДОПЛЕРОВСКИЙ ИЗМЕРИТЕЛЬ СОСТАВЛЯЮЩИХ ВЕКТОРА СКОРОСТИ, ВЫСОТЫ И МЕСТНОЙ ВЕРТИКАЛИ ДЛЯ ВЕРТОЛЕТОВ И КОСМИЧЕСКИХ АППАРАТОВ ВЕРТИКАЛЬНОЙ ПОСАДКИ | 1995 |

|

RU2083998C1 |

| УСТРОЙСТВО АВТОМАТИЧЕСКОГО ПОИСКА КАНАЛОВ РАДИОСВЯЗИ | 2011 |

|

RU2450447C1 |

| Устройство для сжатия информации | 1988 |

|

SU1550558A1 |

| Устройство для отображения радиолокационной информации на экране электронно-лучевой трубки | 1989 |

|

SU1691880A1 |

| Цифровой вольтметр | 1981 |

|

SU976394A1 |

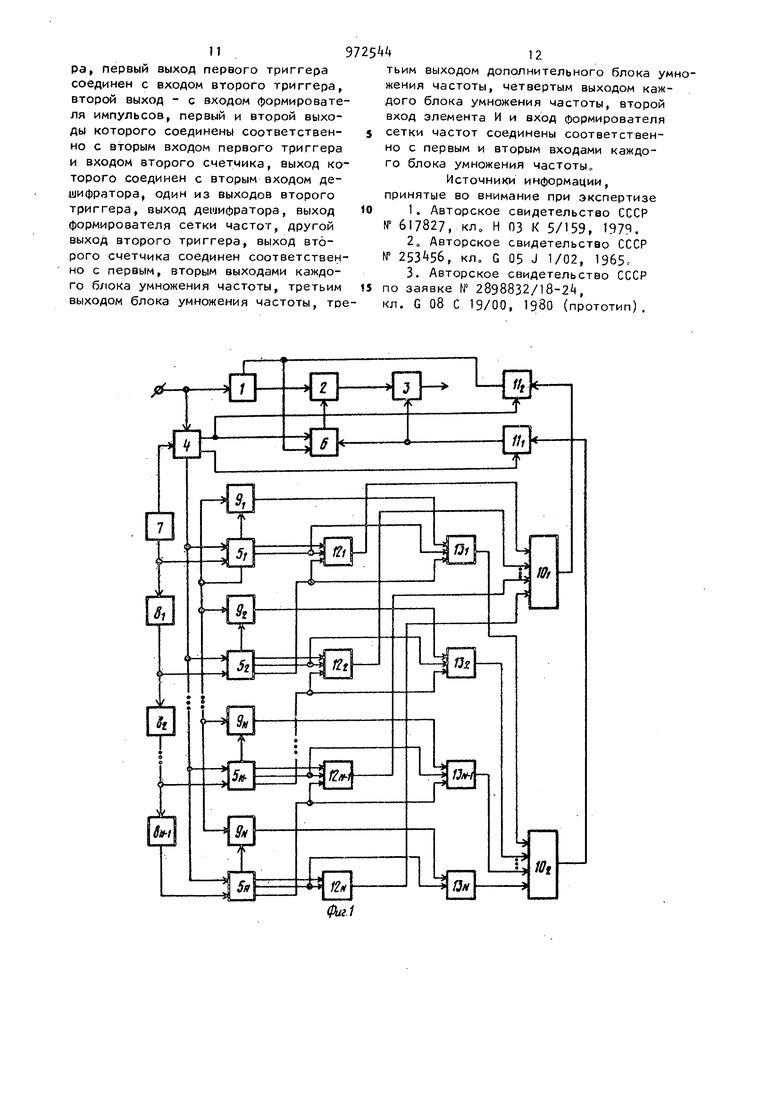

Изобретение относится к автоматике и вычислительной технике и предназначено для анализа сигналов в реальном масштабе времени, согласования полосы сигнала с полосой пропускания анализирующей и измерительной аппаратуры и пр„ Известно устройство для временного сжатия сигналов, состоящее из нескольких узлов накопления с коммутатором и рециркуляционной линии задержки в каждом узле, используемой в качестве запоминащего блока сумматора, выход которого является выходом устройства, блок управления входы элементов запоминания уровня напряжения и вход коммутатора перво го узла накопления объединены и образуют входную шину устройства 1. Однако это устройство не может быть использовано для измерения характеристик периодических .сигналов, так как не осуществляет выделение периода входного сигнала. Устройств автоматически не определяет оптимальное число фиксируемых точек за один период входного сигнала и, следовательно, в 1Уироком диапазоне частот изменяющаяся погрешность аппроксимации входного сигнала может оказаться выше допустимой. Это сужает частотный диапазон сжимаемых входных сигналов, что является недостатком устройства« Известно также устройство для временного сжатия входного сигнала, содержащее блоки упрвления и блок памяти, выполненные с применением магнитострикционных :линий задержки блока управления с выходами преобразователя аналог-код, а выходы соединены с преобразователем код-аналог t2. Недостаток такого устройства заключается в том, что оно не может быть использовано для измерения характеристик периодических сигналов, так как оно не осуществляет выделение периода входного сигнала. Как и в других известных устройствах, при сжатии периодических сигналов этим устройством, изменяется погрешность аппроксимации входного си1- нала в зависимости от его частотного диапазона Наиболее близким по технической сущности к предлагаемому является устройство для временного сжатия вхо ного сигнала, содержащее преобразователь, аналог-код, информационный вход которого соединен с входом устройства, а выход подключен к информационному входу блока памяти, выход пос/.еднего соединен с информационным входом преобразователя код-аналог, выход которого подключен к выходу устройства, вход блока определения периода подключен к входу устройства первый выход соединен с первым входом блока умножения частоты, а второ выход подключен к первому входу блока адресации, выход которого соединен с адресным входом блока памяти, управляющий вход преобразователя ана

лог-код объединен со вторым входом блока адресации, первый выход блока управления соединен со вторым входом блока умножения частоты 31.

Известное устройство может быть использовано для измерения характеристик периодических сигналов инфразвукового диапазона.частот приборами звукового диапазона частот, так как осуществляет запоминание в цифровой форме исследуемого сигнала на его периоде с последующим переносом спектра. Устройство может быть использовано для измерения средних, средних по модулю, среднеквадратических значений напряжения, коэффициента гармоник, коэффициента формы и др.

К недостаткам известного устройства следует отнести практическую невозможность его использования для проведения спектрального и гармонического анализа инфразвуковых сигналов, так как масштаб преобразования спектра -неизвестен. Масштаб преобразования может быть определен путем вычисления отношения периодов входного и преобразованного (сжатого во времени) сигналов, однако его использование для названных целей чрезвычайно неудобно, так как его величина может принимать любые нецелочисленные значения, что вызывает необходимость проведения дополниХОД формирователя управляющих сигналов соединен с вторым входом блока умножения частоты, второй выход формирователя управляющих сигналов соединен с первым входом формирователя адреса, второй вход которого соединен с управляющим входом преобразователя аналог-код, выход - с адресным входом блока памяти, введены делители частоты, дешифраторы, дополнительные блоки умножения частоты, первая и вторая группы элементов И, элементы ИЛИ и ключи, второй выход синхронизатора соединен с управляющим входом формирователя управляющих сигналов, третий выход которого соединен с первым входом первого ключа, выход которого соединен с третьим входом формирователя адреса и управляющим

5 входом преобразователя код-аналог, первые выходы всех блоков умножения частоты соединены с первыми входами соответствующих элементов И первой и второй группы, вторые выходы - с

0 вторыми входами соответствующих элементов И первой группы, третий выход блока умножения частоты соединен с объединенными первыми входами всех дешифраторов, третьи выходы дополнительных блоков умножения частоты соединены с объединенными третьими входами соответствующих элементов И первой группы и вторыми входами соответствующих элементов И тельных вычислений для идентификации полученных результатов,. Цель изобретения - расширение области применения устройства за счет автоматического частотного масштабирования при преобразовании исследуемого сигнала для обеспечения спектрального анализа инфразвуковых периодических сигналов анализаторами спектра звукового диапазона частот. Эта цель достигается тем, что в устрог ство для сжатия информации, содержащее синхронизатор, первый выход которого соединен с первым входом блока умножения частоты, преобразователь аналог-код, информационный вход которого объединен с информационным входом формирователя управляющих сигналов и подключен к входу устройства, выход преобразователя аналог-код соединен с информационным входом блока памяти, выход которого соединен с информационным входом преобразователя код-аналог, выход которого соединен с выходом устройства, первый вывторой группы, четвертые выходы всех блоков умножения частоты соединены с вторыми .входами соответствующих дешифраторов, выходы которых соединены с третьими входами соответствующих элементов И второй группы, выходы элементов И первой группы соединены с соответствующими входами первого эле мента ИЛИ, выход которого соединен с первым входом второго ключа, второ вход второго ключа соединен с вторым выходом формирователя управлящих си налов, выход,- с управляющим входом преобразователя аналог-код и вторым входом формирователя ддреса, выходы элементов И второй группы соединены с соответствующими входами второгр элемента ИЛИ, выход которого соединен с вторым входом первого ключа, первый выход синхронизатора соединен с входом первого делителя частоты, выход каждого делителя частоты соеди нен с входом последующего делителя частоты и первым входом соответствующего дополнительного блока умножения частоты, вторые входы которых объединены и подключены к первому вы ходу формирователя управляющих сигналов. Причем блок умножения частоты содержит формирователь импульсов, формирователь сетки частот, дешифратор, триггер, счетчик и элемент И, выход формирователя сетки частот соединен с первым входом дешифратора, выход которого соединен с первым входом элемента И, выход которого через первый счетчик соединен с пераым вхо дом первого триггера, первый выход первого триггера соединен с входом второго триггера, второй выход - с входом формирователя импульсов, первый и второй, выходы которого соединены соответственно с вторым входом первого триггера и входом вто рого счетчика, выход которого соединен с вторым входом дешифратора, оди из выходов второго триггера, выход дешифратора, выход формирователя сет ки частот, другой выход второго Риг гера, выход второго счетчика соединен соответственно с первым, вторым выходами каждого блока умножения частоты, третьим вы.ходом блока умножения частоты, третьим выходом дополнительного блока умножения частоты, четвертым выходом каждого блока умножения частоты, второй вход элемента И и вход формирователя сетки частот соединены соответственно с первым и вторым входами каждого блока умножения частоты На фиг. 1 изображена функциональная схема предлагаемого устройства, на фиг, 2 - пример выполнения блока умножения частоты Устройство для сжатия информации содержит преобразователь 1 аналогкод, блок 2 памяти, преобразователь 3 код-аналог, формирователь k управляющих сигналов определения периода, N блоков умножения частоты, где N - количество десятичных масштабов преобразования, формирователь 6 адреса, синхронизатор 7, N-1- делителей 8.,-В.частоты, N дешифраторов , элементы ИЛИ , ключи 11i, ТЦ, две группы по N элементов И 121-12, 13i-13N. Блок 5 умножения частоты содержит формирователь 1 + сетки частот, дешифратор 15, первый счетчик 16, триггер 17, формирователь 18 импульсов, второй счетчик 19, триггер 20 и элемент И 21. Устройство работает следующим образом , Входной периодический сигнал по-. ступает на преобразователь 1 аналогкод и на формирователь t, на выходах последнего после запуска синхронизатором 7 формируются сигналы разрешения: на первом выходе- на длительность первого периода входного си( нала; на втором выходе - на длительность второго периода-, на третьем выходе - на считывание информации из блока 2 памяти после окончания второго периода и до следующего запуска устройства;, Таким образом, работа предлагаемого устройства осуществляется в три этапа. На первом этапе (первый период входного сигнала) осуществляется формирование частоты запуска преобразователя 1 аналог-код и частоты считывания информации из блока 2 памяти и тактирования преобразователя 3 код-аналог о На первые входы блоков умножения частоты поступает сигнал разрешения их работы,благодаря чему в каждом блоке умножения частоты из сетки частот, формируемой на формирователе 1 сетки частот, осуществляется выбор такой частоты, которая обеспечивает деление одного периода на число, равное числу ординат и находящееся в пределах 79 от d до 2с(. Это осуществляется следу ющим образом. После запуска устройст ва на счетчик 16 через элемент И 21 и дешифратор 15 поступает максимальная частота из формирователя 1 сетки частот После первого переполнени счетчика 16, Тов. набора числа ot, триггер 17 устанавливается в единичное состояние, а после второго переполнения, т-о-е набора числа 2oL, в нулевое состояние. По последнему переходу срабатывает формирователь 18 импульсов, который добавляет единицу к содержимому счетчика 19 и устанавливает триггер 17 в единичное состояние. Наиболее удобна реализация при использовании двоичной сетки частот, в том случае формирователь 1 + сетки просто реализуется на двоичном счетчике, частоты следования импульсов с соседних выходов которого отличаются в два раза. При двойном переполнении счетчика 1б в два раза уменьшается частг)та с выхода дешифратора 15, а состояние счетчика 16 и триггера 17 соответствует числу, равному ot. Таким образом осуществляется замена числа 2о1и частоты fj на число с1и частоту f.j4.-)f i/2| причем это про ИСХОДИТпосле каждого двойного переполнения счетчика 16, благодаря -чему и осуществляется выбор частоты запуска преобразователя 1 аналог-код Для обеспечения удобства проведения спектрального анализа с помощью предлагаемого устройства частота запуска преобразователя 1 анало - КОД f,j- и частота запуска преобразователя 3 код-аналог fj должны соот-. носиться следующим образом..f/f- 1 О где ,2,...,N. Формирование указанной сетки частот осуществляется с помощью N блоков 5-)-5N умножения частоты и (N-I) делителей частоты причем последние в этом случае имеют коэффициент деления . Благодаря этому на соседних формирователях Tt сетки частот идентичные, частоты коатны десяти. Все блоки умножения частот начинают работать одновременно и выбор Частот fj и f; осуществляется следующим образом. После того как счетчик 16 первого блока 5 умножения частоты переполнится первый раз, срабатывает триггер 20 и включает соответствующие элементы И 12 и 13i 48 обеих групп, а так как на третьих входах последних такие имеется разрешающий сигнал то через них и через элементы ИЛИ 1П, 10 на 11 поступают частоты fj i . ,,того как счетчик 16 второго блока Si умножения частоты переполнится первый раз, срабатывает соответствующий триггер 20 и включает соответствующие элементы И 122) 13 1 обеих групп, а первые элементы И 12, 132 обеих Групп выключает. Через второй элемент И 122 первой группы поступает частота fj, а через второй элемент И 13 второй группы поступает частота f:, причем их отношение равно f;/f; 10. Аналогичные изменения происходят при переполнении счетчика 16 i-ro блока 5i умножения частоты, причем выполняется соотношение f|/f; in . Выполнение этого соотношения обеспечивается выполнением oтнoшeния f|i .ipin i( и тем, что все частоты f; поступают только из первого блока 5 умножения частоты,, Таким образом, в течение первого периода входного сигнала осуществляется выбор частот fl и f|. ,. На втором этапе работы устройства (второй период входного сигнала) на блоки 5 -5|vi умножения частоты поступает запрет их работы, а на формирователь 6 адреса и второй вход второго ключа 11 поступает сигнал разрешения с второго выхода формирователя 0 С выбранной частотой f; осуществляется запуск преобразователя 1.анало -код и запись полученных выбранных значений входного сигнала в блок 2 памяти. По окончании второго периода сигнала в блоке 2 памяти оказываются заполненными от ot до 2(Апыборочных значений, второй ключ закрыт, а первый ключ 11 открывается сигналом разрешения с третьего выхода формирователя , Начинается третий этап работы устройства - считывание информации из блока 2 памяти и ее преобразование в аналоговую форму в преобразователе 3. Частота f поступает на тактирование формирователя 6 и преобразователя 3 код-аналог с выхода первого ключа 11). Считывание информации происходит непрерывно до следующего запуска устройства. Начало третьего этапа работы означает конец преобразования временного (спектрального) масштаба входного периодического сигнала. Таким образом, с помощью введения новых узлов и связей осуществляется преобразование временного (спек трального) масштаба исследуемого сигнала с коэффициентом, кратным К) благодаря чему достигается качествен но новый эффект: возможность применения подобных устройств для практического спектрального (гармонического) анализа инфразвуковых периодических сигналов спектроанализаторами звукового диапазона частот. Дополнительно предлагаемое устройство может использоваться для аналогичных целей при корреляционном анализе, а также для исследования амплитудно-ча стотных характеристик различных технических устройств,. В связи с изложенным можно констатировать значительное расширение области применени предлагаемого устройства. формула изобретения 1, Устройство для сжатия информации, содержащее синхронизатор, первый выход которого соединен с первым входом блока умножения частоты, преобразователь аналог-код, информацион ный вход которого объединен с информационным входом формирователя управ ляющих сигналов и подключен к входу устройства, выход преобразователя анало -код соединен с информационным входом блока памяти, выход которого соединен с информационным входом пре образователя код-аналог, выход которого соединен с выходом устройства, первый выход формирователя управляю,щих сигналов соединен с вторым входом блока умножения частоты, второй вь|Ход формирователя управляющих сигнсзлов соединен с первым входом формирователя адреса, второй вхо которого объединен с управляющим вхо дом преобразователя аналог-код, выход - с адресным входом блока памяти отли чающееся тем, что, с целью расширения области применения устройства, в него введены делители частоты, дешифраторы, дополнительные блоки умножения частоты, первая и вторая группы элементов И, элементы ИЛИ и ключи, второй выход синхронизатора соединен с управляюиАи входом формирователя управляющих сиг налов, третий выход которого соединен с первым входом первого ключа, выход которого соединен с третьим входом формирователя адреса и управляю(цим входом преобразователя код-аналог, первые выходы всех блоков умножения частоты соединены с первыми входами соответствующих элементов И первой и второй группы, вторые выходы - с вторыми входами соответствующих элементов И первой группы, третий выход блока умножения частоты соединен с объединеннь1ми первыми входами всех дешифраторов, третьи выходы дополнительных блоков умножения частоты соединены с объединенными третьими входами соответствующих элементов И первой группы и вторыми входами соответствующих элементов И второй группы, четвертые выходы всех блоков умножения частоты соединены с вторыми входами соответствующих дешифраторов, выходы которых соединены с третьими входами соответствующих элементов И второй группы, выходы элементов И первой группы соединены с соответствующими входами первого элемента ИЛИ, выход которого соединен с первым входом второго ключа, второй вход второго ключа соединен с вторым выходом формирователя управляющих сигналов, выход - с управляюсцим. входом преобразователя аналог-код -и вторым входом формирователя адреса, выходы элементов И второй группы соединены с соответствующими входами второго элемента ИЛИ, выход которого соединен с вторым входом первого ключа, первый выход синхронизатора соединен с входом первого делителя частоты, выход каждого делителя частоты соединен с входом последующего делителя частоты и первым входом соответствуЮ1цего дополнительного блока умножения частоты, вторые входы которых объединены и подключены к первому выходу формирователя управляющих сигналов о 2о Устройство по п, 1, отличающееся тем, что блок умножения частоты содержит формирователь импульсо9 формирователь сетки частот, дешифратор, триггер, счетчик и элемент И, выход формирователя сетки частот соединен с первым входом дешифратора, выход которого соединен с первым входом элемента И, выход которого через первый счетчик соединен с первым входом первого триггеpa, первый выход первого триггера соединен с входом второго триггера, второй выход - с входом формирователя импульсов, первый и второй выходы которого соединены соответственно с вtopым входом первого триггера и входом второго счетчика, выход которого соединен с вторым входом дешифратора, один из выходов второго триггера, выход дешифратора, выход формирователя сетки частот, другой выход второго триггера, выход второго сметчика соединен соответственно с первым, вторым выходами каждого блока умножения частоты, третьим выходом блока умножения частоты, третьим выходом дополнительного блока умжения частоты, четвертым выходом каждого блока умножения частоты, второй вход элемента И и вход формирователя сетки частот соединены соответственно с первым и вторым входами каждого блока умножения частоты

Источники информации, принятые во внимание при экспертизе

1, Авторское свидетельство СССР W 617827, кл„ Н ПЗ К 5/159, 1979.

2„ Авторское свидетельство СССР № , кло G 05 J 1/02, 1965с

дшод1

/

Вымдб

Авторы

Даты

1982-11-07—Публикация

1981-04-23—Подача