Ю

СО

| название | год | авторы | номер документа |

|---|---|---|---|

| Детектор квазиравновесия | 1980 |

|

SU938163A1 |

| Квазиуравновешенный мост для раздельного измерения одного из параметров нерезонансных трехэлементных двухполюсников | 1981 |

|

SU978054A1 |

| Устройство для контроля параметров комплексных сопротивлений | 1976 |

|

SU664121A1 |

| Преобразователь напряжения | 1990 |

|

SU1814177A1 |

| Преобразователь параметров трехэлементных двухполюсников | 1981 |

|

SU1000933A1 |

| ЦИФРОВОЙ РАДИОПЕЛЕНГАТОР | 1997 |

|

RU2115135C1 |

| Устройство контроля каналов связи | 1988 |

|

SU1578820A1 |

| Устройство для контроля восприимчивости радиоприемников по побочным каналам приема | 1986 |

|

SU1383511A1 |

| Устройство для измерения влажности нефти и нефтепродуктов | 1985 |

|

SU1257496A1 |

| Устройство для раздельного из-МЕРЕНия пАРАМЕТРОВ КОМплЕКСНыХВЕличиН | 1979 |

|

SU815678A1 |

1. Детектор квазиравновесия, содержащий первый и второй ключи, выход первого ключа через последовательно соединенные интегратор и нуль -орган подключен к входу блока управления, второй вход которого подсоединен к опорному входу устройства, а пернвый и второй выходы соединены с управ ляющими входами соответственно первого и второго ключей, вход и выход второго ключа подключены соответственно к выходу генератора импульсов и к входу счетчика, отличающийся тем, что, с целью повыщения точности yci ройства, в него введены амплитудный преобразователь, блок выделения HeHaMe ряемой составляющей сигнала, выход которого соединен с первым входом первого ключа, первый вход - с информационным входом устройства, со вторым входом первого ключа и с третьим входом блока управления, а второй вход - с опорным входсйл устройства И через ам S плитудный преобразователь - с третьим входом первого ключа, а у травляющий вход - с третьим выходе блока управ

ч.

Известен детектор квазиравновесия, содержащий два.сох ласующих блока, выходы которых соответственно через первый и второй двухполупериодньгр выпряМигели соединены с соответствующими входами вычитающего блока, выход которого .подключен к сигнальному входу интегратора, выход которого подсоединен к сигнальному входу блока сравнения, управляющие входы интегратора и блока сравнения соединень с выходом времязадающего блока .

Указанное устройство сравнивает модули двух гармонических сигналов одичаковой частоты, но не позволяет CJWBгивать раздельно синфазные и квадрягурные составляющие этих сигналов.

ляемый фазовращатель, делитель напряжения и нуль-орган, второй вход которого является первым входом блока, а выход соединен со вторым входом делителя напряжения, выход которого является выходом блока, вход управляемого фазовращателя является вторым входом блока, а управляющие входы управляемого фазовращателя и делителя напряжения являются управляющим входом блока.

fi. Детектор по п. 3, о т л и ч а ющийся т ем, ч то блок компенсации неизмеряемой составляющей сигнала со-, держит последовательно соединенные, управляемый фазовращатель, делитель напряжения и нуль-орган, а также блок вычитания, первый вход которого соединен с вторым входом нуль-чзргана и является первым входом блока, второй вход соединен с выходом делителя напряжения а выход является выходом блока, причем выход нуль-органа подключен к второму входу делителя напряжения, управляющий вход которого соединен с управляющим входом управляемого фазовращателя и является управляющим входом блока, вход управляемого фазовращателя является вторым входом блока.

Кроме того, сигнал на выходе детектора имеет аналоговую форму, что требует дополнительного аналого-цифрового преобразования для случая экстраполяционного формирования регулирующих воздействий для. уравновещивания, например, мостовой измерительной цепи.

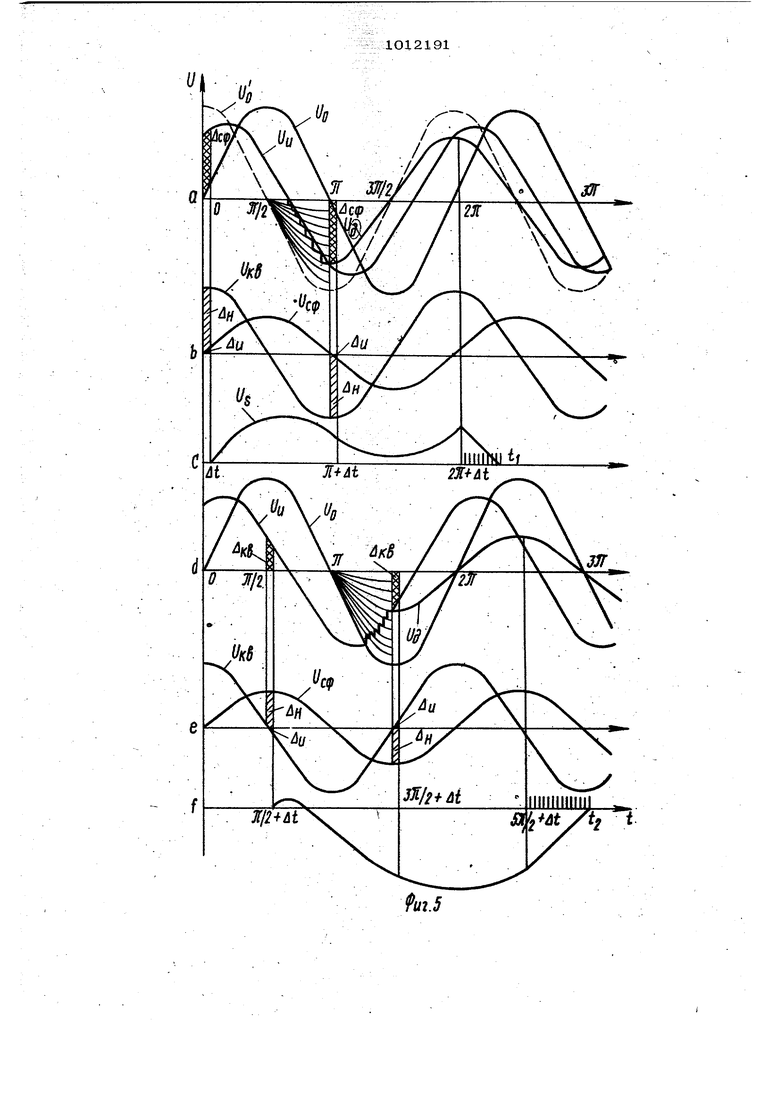

Известно устройство для контроля параметров комплексных сопротивлений, параметров комплексных сопротивлений,содержащее генератор синусоидального напря жения.выход которого соединен с входами первичнохю измерительного преобразовате пя и формирователя импупьсов,выход которого подключен к первому входу блока управления, выходы которого подсоединены соответственно к управляющим входам первого, второго и третьего ключей и первому входу блока запоминания, первый и второй выходы которого соединены с сигнальным входом второго ключа и первым входом первого ключа, второй и третий входы которого подключен соответственво к выходам источника опорного напряжения/в перьичного измерительного преобразователя, а выход - к входу интегратора, первый и второй выходы крторого подсоединены к второму входу блока запоминания и через нуль-орган к второму входу блока управления соответственно, выход генератора импульсов через третий ключ соединен со входом счетчика . Данное устройство позволяет получать итифровую информацию об отношении соотавляюпщх одного из сигналов (с выхода первичного измерительного преобразователя) ко второму, взятому за опорный (сигналу с ш 1хода генератора синусоидального напряжения). Однако устройство обладает низкой точностью, так как вследствие задержек срабатывания формирователя импульсов и трехпозиционного ключа выходные напряжения интегратора в конце первого такта интегрирования со ответсгвенно для синфазной и квадратурной составляющих будут равны не % - ° f«Vb.,-C05C.0)I C05VfCOS4-l siviQBivie . ти„ siwCtftO) cosifsine где Т - период синусоидального напряж&ния;( - амплитуда информационного - постоянная времени интегратора; 1/ - фазовый сдвиг между опорным и информационным гармоническими сигналами; & - фазовая погрешность от задержек. Таким образсм, в сигналах интегратора присутствуют ка5 измеряемая соста&ляюшая, так и неизмеряе«{ая. Косинусная составляющая погрешностей несущественна, поскольку она лишь незначительно ме няет напряжение интегратора, а при приг пятом способе двухтактного интегрирования это не сказывается на конечном результате. Влияние синусной погрешности, особенво в случаях, когда измеряемая составляющая намного меньше неизмеряемой, играет определяющую роль. Кроме того, дополнительная погрешность вызвана тем, что напряжения на выходах г&нератора синусоидального напряжения и сточника образцового напряжения и источника образцового напряжения вследствие влияния различных дестабилизируюих факторов могут изменяться незавси симо друг от друга. Цель изобретения - повышение точности. Указанная пиль достигается т&л, что в детектор квазиравновесйя,сс«ержащий первый и второй ключи, выход первого ключа через последовательно соединенные интегратор и нуль-орган подключен к первому входу блока управления, второй вход которого подсоединен к опорному входу устройства, агпервый и второй выходы соединены с управляющими входами соответственно первого и второго ключей, вход р выход второго ключа подключенысоответственно к выходу генератора импульсов и к входу счетчика, введены амплитудный преобразователь, блок выделения неизмеряемой составляющей сиг нала, выход которого соединен с первым входгал первогх) ключа,первый вход-си - фогыационным входом устройства.ср вторым входом первого ключа и с третьим входом блока управления, а второй вход - с опорным входом устройства и через амплитудный преобразовав-: тель - с третьим входом переюго ключа, . а управляющий вход - с третьим выхоа 4 блока, управления, причем блок выделения измеряемой составляющей сигнала содержит последовательно соединенные управляемый фазовращатель, делитель напряжения и нуль-орган, второй вход которого является первым входом блока, а выход соединен со вторым входом де.лителя напряжения, выход которого является выхоДся 4 блока, вход управляемого фазовращателя является BTopi iM вхопом блока, а зтаравпяющие входы управляемого фазовращателя и делителя напряжения являются управляющ1Ш( входом блока. В детектор i квазиравнрвесия введевьп амплитудный преобразователь в блок компенсации неизмеряемой составляющей сигнала, выход которого подключен к первсыу входу первого кгаоча, первый вход - к йнформаиионнсилу входу устрой, ства и к третьему, входу блока унравленкя, второй вход - к опорному входу устройства и через амплитудный преобразователь - к второму входу первого ключа, а управляющий вход - к третьему выходу блока управления, прнчем б1кж компенсации невзмеряемой составляющей 510 сигнала содержит последовательно соеаиненные управляемый фазовращатель, делитель напряжения и нуль-орган, а также блок вычитания, первый вход которого соединен с вторым входом нуль-органа и является первым входом блока, второй вход соединен с выходом делителя напряжения, а выход является выходам блока, причем выход нуль-органа подключен к второму входу делителя напряжения, управляющий вход которого соединен с управляющим входом управляемого фазовращателя и является управляющим входом блока, вход управляемого фазовращателя является вторым входом блока. .-На фиг. 1 -дана блок-схема первого варианта детектора квазиравновесия, первый вариант; на фиг. 2 - блок-схема . блока выделения неизмеряемой составляющей сигнала; на фиг. 3 - блок-схема второго варианта детектора квазиравновесия; на фиг. 4 - блок-схема блока компенсации -неизмеряемой составляющей сигнала; на фиг. 5 и 6 - временные диаграммы, поясняющие работу соответственно первого и второго вариантов детектора KI азиравновесия для случая нахождения .вектрра информационного гармонического Iсигнала, описываемого уравнением 0 .-( ( Ч), в первом квадранте относительно вектора опорного гармош ческого сигнала и ц 0 Sin Ш-Ь, где и на и Uoa амплитуды информациовн ного и опорного сигналов; (JU - частота; ф - фазовый сдвиг сигнала U.. относительно сигнала U о Детектор квазиравновесия (фиг. 1) содержит блок выделения неизмеряемой составляющей 1 сигнала, амплитудный преобразователь 2,1, генератор имрульсов 3.1, блок управления 4.1, ключи S.1 и 6.1, интегратор 7.1, нуль-орган 8.1и счетчик 9.1. Выход счетчика является выходом устройства. Блок выделе ния неизмеряемой составляющей 1 сигнала содержит управляемый фазовращатель 1О.1, дискретный делитель напряжения 11.1, нуль-орган 12.1. Детектор квазиравновесия (фиг. 3) содержит блок компенсации неизмеряемой составляющей сигнала 13, амплитудный преобразователь 2.2, генератор импульсов 3.2, блок управления 4.2, ключи 5.2и 6.2, интегратор 7.2, нуль-орган 8.2 И счетчик 9.2. Выход счетчика является выходе устройства. Блок компенсации неизмеряемой составляющей ,13 сигнала содержит управляемый фазовращатель 10.2, дискретный делитель напря916жения 11.2, нуль-орган 12.2, блок вычитания 14. Детектор квазиравновесия согласно nepBCTvjy варианту работает следующим образом. Информационный гармонический сигвал О ц поступает одновременно на первые входы блока выделения неизмеря&мой составляющей 1 сигнала, ключа 5.1 и блока управления 4.1. Опорный гармонический сигнал DO (фиг. 5, строка а) поступает одновременно на вход амплитудного преобразователя 2.1 и вторые входы блока выделения неизмеряемой соо- тавляющей 1 сигнала и блока управления 4.1. Блок управления 4.1 управляет работой блока выделения неизмеряемой соо тавляющей 1 сигнала и ключами 5,1 и 6.1 в зависимости от того, в каком квадранте находится вектор сигнала Оц относительно вектора сигнала UQ и отношение амплитуды какой составляющей сигнала Uvi к амплитуде сигнала UQ нужно определить. При определении от- ношения амплитуды синфазной соотгиаляющей сигнала Uu к амплитуде сш нала UQ на первом такте преобразования сигнаЯ управления открывает ключ 5.1 на время от О до IZT при и 37С/2 21С fi на время от It до 2ТС при V 37c/2. Однако вследствие задержек дЧ срабатывания ключа имеет место фазовая погрешность & и напряжение UM через ключ 5.1 поступает на интегратор 7;1 в течение интервала времени от () до (). Выходное напряжение интегратора (фиг. 5, строка с) в конце первого такта интегрирования принимает значение Тс.-- - cos cose- 5iv,4Bi.. Как видно из временных диаграмм (Фиг. 5, строки а, в) основную часть погрешности Лсф преобразования на перBOM такте составляет погрешность от не«.,«,„„,.,.,. « ио взмеряемой (квадратур,ной} составляющей сигнала, Лц- SinVfcoseОдновременно опорный сигнал OQ проходит через управляемый фазовращатель 10.1 и дискретный делитель напряжения 11.1 иа один из входов нуль-органа 2.1, на второй вход которого подаетя сигнал Оц Упра вляемый фазовращатель 0.1 сдвигает фазу сигнала (Jo на зК/2 при 0 и на при ТГ-с , а коэффициент передачи дискретного делителя 11.1 возрастает от О до 1 при 0 rtfV:7r/2 , ,и убывает от 1 до О при П и 3ltJ/2 2К. На фиг. 5 фаза сигнала GO повернута на 3Tli2 относительно сигнала UQ- С момента времени, равного ., сигнал с выхода делителя 11.1 сравнивается с сигналом 0ц и в каждый их равенства до момента Римпульс с выхода нуль-органа 12.1 изменяет коэффициент передачи дискрет ного делителя 11.1 на величину шага дискретности. В результате, начиная с м лента 7Г, сигнал Ug (фиг. 5 строка а) на выходе делителя становится близки к неизмеряемой (квадратурной) UKB (фиг. 5, строка в) составляющей сигнала (Jj, (отличается не более, чем на шаг дискретности сигнала 0л с выхода дела теля 11.1). . Во второй такт интегрирования (в и тервал вретлени от ТРн- до ) с выхода блока 1 выделения неизмеряемой составляющей через ключ В.1 на интегратор 7.1 подается сигнал Ug, которы компенсирует на интеграторе ошибку Silfi4siM0 AH. так как интеграл №(, от гармонической функшга за период ра; вен нулю. В результате на интеграторе CXJSVfcos© : остается напряжение JTuM пропорциональное амплитуде -ZKf, синфазной составляющей. В третьем такте производится разряд интегратора постоя иным напряже нием Ua которое подается от амплитудного преобразователя 2.1 через ключ 5.1 и равно амплитуде Uod опорного напряжения. В результате любое изменение опорного напряжения приводит к соответствующем изменению напряжения разряда, а отношение UQ jUU ocTaeTCH постоянным. На- пряжение на выходе интегратора линейно взметнется ро нулевого значения в момент v , что фиксируется нул1у-органс 1 8.1, импульс с выхода которого подается на блок управления 4.1. Сигнал с блока управления открывает ключ 6.1 на время с момента (2lt+u.-t) до момента fc , а в счетчик 9.1 записывается числ равное количеству импульсов за интер&а времени ()3 и пропорциональное от ношению U.(a| U . При определении отношения амлитуды .UttftO квадратурной составляющей сигнала 0ц (фиг. 5 строка d ,) к амплитуде сигнала Ug по сигналу с выхода блока управления 4.1 открывается ключ 5.1 на время от (7С/2 + М ) до ЗТС/2- -ДЬ1 так йак имеют место временньш задерж.ки. Выходное напряжение интегратора (фиг. .5 строка ) в конце первого такта интегрирования принимает значение ьКак видно из временных диаграмм (фиг. 5 строки d , е) основную часть погрешности А|св преобразования на перветл такте составляет погрешность От неизмеряемой (синфазной) составляющей сигнала UH ,COs4siMP Одновременно опорный сигнал (JQ проходит через управляемый фазовращатель 1О.1 и дискретный делитель напряжения 11.1 на один из входов 12.1,. на второй вход которого подается сигнал Цц. По сигналу с выхода блока управления 4.1 управляемый фазовращатель 1О.1 поворачивает фазу сигнала UQ на Я при 1172 4V3 ТЧ2 и оставляет прежнюю фазу при 0 и 31С72 У 2lt. Дискретный делитель напряжения 11.1 в течение интервала времени oTlZT до изменяет свой коэффициент передачи, причем коэффициент передачи увеличивается от О до 1 при 7С72 «/ 7Ги 25Г и уменьщается от 1 до О при и Tt -37f/2. С момента времени, равного Jt, сигнал Оц с выхода делителя напряжения 11.1 сравниваетрся с сигналом Uv« и в каждый момент их равенства до момента 31С/2 импульс с выхода нул1г-органа 12 изменяет коэффвциент передачи дискретного делителя la пряжения 11 ..1 на величину шага дискретности. В результате, начиная с момев та , сигнал Ua Фиг. 5 строка {J ) на ш 1ходе делителя становится близок к неизмеряемой (синфазной) составляющей Осф (фиг. 5, строка е) сигнала Uvi (отличаегся не более, чем на шаг дискретности сигнала с выхода делителя 11.1). Во второй такт интегрирования (в тервал времени от ui, до + Ь) с выхода блока 1 выделения невэмеряемой составляющей через ключ 5.1 на интегратор 7.1 подается снгвал Ug , который компенсирует на интеграторе - , Т IIошибку ii COS siH9 ™ иит;вгрец1 от гармонической функции за период равен нулю. В р)езультате та .интe.rJ aтope 1 ivi fcostfs остается напряжение TUw пропорционадьное амплитуде кваДратурной составляющей сигнала. В трегь л такте производится разряд интегратора 7.1 постоянным напряжением (Jg, которое подается от амплитудного преобразователя 2.1 через ключ 5.1 и равно амплитуде Uoa опорного напряжения. Момент -tg равенства нулю напряже ния интегратора фиксируется нуль-органе 8.1, и сигнал с вы хода блока управлени 4,1 открывает ключ 6.1 на время с момента ( i-A.fe) до .-tg, а в счетчик 9.1 записывается число, равное ву импульсов за интервал времени (f-) и пропорциональное отно кь шение -рр- Uod IДетектор квазиравновесия по второму варианту (фиг. 3) работает следуюппшг , образсы. Ии4юрмаци6нный сигнал Uu (фиг. 6 строка а) поступает на первый вход блока управления 4.2 и на первый вход блока компенсации неизмеряемой составляющей 13, т.е. одновременно на nep№ie входы блока вычитания 14 и )гана 12.2. Опорный гармошиескй сигнал Uo (фиг. 6 Строка а) поступает одновре менно на вход амплитудного преобразователя 2.2, второй вход блока управления 4.2 и второй вход блока компенсации неизмеряемой составляющей 13 сй1 нала, т.е. через последовательно соединенны е управляемый фазовращатель 1О.1 и дискретный делитель напряжения 11.2, на вторые входы блока вычитания 14 и нуль-органа 13. Блок управления- 4.2 управляет работой блока компенсации неизмеряемой составляющей 13 сигнала в ключами 5.2 и 6.2 в зависимости or того, в каком квадранте находится вектор сигнала UQ относительно векторе сигнала Оц и отношение амплитуды какой составляющей сигнала Uy к амплитуде сигнала U нужно определить. При определении отнощения амплитуды ОкбО квадратурной составляющей сигнала {Ji, к амппигуде сигнала UQ по сигналу с выхода блока управления 4.2 фазовращателя 1О.2 поворачивает фазу сигнала f при и оставляет прежнюю фе1зу при 0 и . Дискретный делитель напряжения 11.2 в„.течение интервапа времени от О до 91.10 изменяет свой коэффшгаент передачи, причем коэффициент передачи увепичивается от О до 1 при V 7ZrH 3C/2 / 2 и уменьшается от 1 до О при и 7C-cS 3 /2. Нульорган 12.2 сравнивает сигнал Уц с сигналом и (фиг. 6 строка а) с выхода дискретного делителя напряжения 11.2, и в моменты их равенства импуль сы с выхода нуль-органа, поступая на второй управляющий вход дискретного делителя напряжения 11.2, вызывая изменение его коэффициента передачи на единицу дискретности. В результате к моменту времени сигнал на выходе дискретного делителя напряжения 11.2 устанавливаетсяблизким к величине ) синфазной составляющей сигнала Uj (отличается не более, 4®vi на единицу дискретности), а сигнал Up (фиг. 6 строка в) на выходе блока вычитания 14 близок к величине квадратурной соотавляющей ,ь сигнала UM , причем сигНал OQ 0 , а сигнал Up . . Сигнал /Up с выхода олока вычитания 14 через ключ 5.2 поступает ш вход интегратора 7.2 в течение интервала, времени от ( 7С-/2 +Д -fe ) до (.3ifc/2 +A-fe) опорного сигнала (вследствие временных задержек блока управления 4.2 и ключа 5.2). В результате имрет место фазовая погрешность & 27Г, где Т - период колебаний сигнала Uo и выходное значение сигнала (фиг. 6 строка с) на выходе интегратора 7.2 в конце первого такта интегрирования будет отпичаться от Ч не более, чем на -(фиг. 6 строка в), где Л - к6л11чество дискретных значений коэффициента передачи дискретного делит&ля напряжения 11.2. Если неизмеряемая составляющая не компенсировалась, потррешнрсть возросла бы на -.сииО Чфиг. 6 строка а). ш ВЬ второй такт интегрирования (с момента + Д-t) по сигналу с блока управления 4.2 производится разряд и гегратора постоянным напряжением Од , которое подается через ключ 5.2 с выхо да амплитудного преобразователя 2.2 и пропорЙионально амплитуде dog опорного напряжения UQ. В результате любое изменение опорного напряжения приведет к пропорциональному изменению напряжений разряда, а отнощениеЦд | UQ.Jx:тaнeтcя по111стоянным. Напряжение на выходе интегра тора пинейно уме.ньшается во втором такте интегрирования до нулевого значения в момент -t , что фиксируется нульорганом 8.2, импульс с выхода которого подается на блок управления 4.2. Сигнал с блока управления 4.2 открывает ключ 6.2 на время с момента . до момента Ч-и , а в счетчик 9.2 записывается число, равное количеству импульсов с выхода генератора ИМПУЛЬСОВ 3,2 за интервал времени ,. Hdo И пропорциональное отноше При определении отношения амплитуды Uc(bq синфазной составляющей сигнала (jj к амплитуде сигнала (Jo о сигналу с выхода блока управления 4.2 управляемый фазовращатель iO.2 поворачивает фазу сигнала DO на Rv2 при /t Х 21С и на при а дискретный делитель напряжения 11.2 в течение интервала времени от до /ZT дискретно изменяет коэффициент передачи, причем коэффициент передачи увеличивается от О до 1 при иЯГ 3ЙГ/2, и уменьшается от 1 до нуля при f 3В72 Ф 27Г. Нуль-орган 12.2 сравнивает сигнал Цц (Фиг. 6 строка ) с сигнале выхода дискретного делителя напряжения 11.2, и в моменты их равенства импульс с выхода нуль-органа, поступая на второй управляющий вход Дискретного делителя напр1яжения 11.2, вызывает изменение его коэффициента передачи на величину един1шы дискретности. В результате к моменту време ни 1Г сигнал на выходе дискретного дела теля напряжения 11.2 близок к величине квадратурной составляющей сигнала JJ (отличается не более, чем на единицу дискретности), а сигнал Up (фиг. 6 стро ка е) на выходе блока разности 14 близок к величине синфазной составл5;ющей Осф сигнала Оц, причем сигнал 0 на выходе дискретного делителя 11.2 на91пряжениями JO сигнал (А на выходе блока вычитания 147/Up0. Сигнал Up с выхода вычитаний 14 через ключ 5.2 поступает на вход интегратора 7.2 в течение интервала времени от до 2If опорН9го сигнала. Если вследствие задержек срабатывания блока управления 4.2 и ключа 5.2 имеет местч фазовая погрешность &, сигнал Ор интегрируется в течение интервала времени от (1Г+Л-Ь) до (2ГЛГ+ь±). Выходное значение сигнала с выхода интегратора в конце первого такта интегрирования. -ти не более. будет отличаться от , foc д 21ГС где и - количество чем на дискретньтх значений дискретного делите ля напряжения 11.2. Погрец1ность измеряемой составляющей и неизмеряемой составляющей в случае отсутствия ее компенсации показаны на фиг. соответст-к венно в строках 6 и d . Во втором такте интегрировашга (с момента 21СЧ-Д-Ь) производится разряд интегратора постоянным напряжением Ut|) которое подается через ключ 5.2 с выхоДа амплитудного преобразоватем 2,2 И пропорционально амплитуде UQQ опорного напряжения. Напряжение на-вы ходе внт гратора линейно изменяется во втором такте, а его окончание b.j. определяется моментом перехода через нулевой уровень сигнала Up . с помощью нупь-орггнна 8.2. Длительнтсть второго такта, а следовательно, и число в счетчике 9.2, пропорционально отношению Осфа Таким образом, как первый,так в второй варианты детектора квазиравшЗвесия уменьшают погрешности от вевэмеря лых составляющих входного гармо нического сигнала, что позволяет повалсить точность контрольно-взмеритепьной аппаратуры, что.особенно важно а АСУТШ

8x.1

8i2

Вых.

Упр. иг.2

W

(Jo

/J

Uu

Uo

W.2

7T

/7A fc./5

гг

t.i

n

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| АМПЛИТУДНО-ДИФФЕРЕНЦИАЛЬНЫЙ НУЛЬ-ОРГАН | 0 |

|

SU387330A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для контроля параметров комплексных сопротивлений | 1976 |

|

SU664121A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1983-04-15—Публикация

1981-11-02—Подача