дами выходных элементов И групп, пятый выход блока синхронизации соединен с первыми управляющими входами реверсивных,счетчиков, отличающ е е. с я тем, что, с целью расширения функциональных возможностей путем оперативного изменения порядка упорядочивания чисел, устройство дополнительно содержит п управляемых элементов И, п дополнительных элементов ИЛИ, причем информационные входы управляемых элементов И соединены с соответствующими выходами соответствующих реверсивных счетчиков, шестой выход блока синхронизации соединен с вторыми управляющими входами реверсивных счетчиков, седьмой и восьмой выходы блока синхронизации, соединены с управляющими входами элементов И-НЕ и управляемых элементов И соответственно, выходы которых через соответствующие дополнительныеэлементы ИЛИ соединены с вторыми управляющими входами соответствующих выходных элементов И групп.

2.. Устройство по п. 1, о т л и ч а ющ.ее с я тем, что блок синхронизации содержит формирователи импульсов, элементы задержки, триггеры элементы ИЛИ, И-НЕ, И, НЕ, счетчик, генератор тактовых импульсов, управляющий триггер, причем вход блока синхронизации соединен с входом установки в единичное состояние первого триггера, входом первого формирователя импульсов и входом первого элемента задержки, выход которого соединен с входом второго формирователя импульсов, выход которого соединен с входом установки в нулевое состояние первого триггера, входом

второго элемента задержки и единичным входом второго триггера, выход второго элемента задержки соединен с входом второго формирователя импульсов, выход которого соединен с нулевым входом второго триггера и входом третьего элемента задержки, выход которого соединен с входом третьего формирователя импульсов, выход которого соединен с первым входом элемента ИЛИ, выход элемента ИЛИ соединен с единичным входом третьего триггера и через четвертый элемент задержки и четвертый формирователь импульсов с входом запуска генератора тактовых импульсов и нулевым входом третьего триггера, выходы счетчика соединены с входами элемента И-НЕ, выход которого соединен с входом останова генератора тактовых импульсов, прямые выходы первого, второго и третьего триггеров, соединены с первым, третьим и четвертым выходами блока, выход первого формирователя соединен с вторым выходом блока, прямой и инзерсный выходы управляющего триггера соединены с первыми входами соответственно второго и третьего элеvieHTOB И, вторые входы которых соеди.5ены с выходами первого элемента И, зыходы второго и третьего элементов Л являются соответственно пятым и лестым выходами блок.а, входы установки в нулевое и единичное состояния управляющего триггера соединены с кодовой шиной управления устройства, прямой выход управляющего триггера соединен через элемент НЕ сседьмым выходом блока, а инверсный выход соединен с восьмым выходом блока синхронизации.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для упорядочивания чисел | 1980 |

|

SU932487A1 |

| Устройство для упорядочивания чисел | 1983 |

|

SU1144103A1 |

| Устройство для упорядочивания чисел | 1984 |

|

SU1241228A1 |

| Устройство для сортировки двоичных чисел | 1984 |

|

SU1182509A1 |

| Устройство для сортировки массивов чисел | 1988 |

|

SU1624440A1 |

| Устройство для сортировки двоичных чисел | 1982 |

|

SU1049900A1 |

| Устройство для упорядочивания чисел | 1984 |

|

SU1246089A1 |

| Устройство для деления в системе остаточных классов | 1983 |

|

SU1141400A1 |

| Устройство для сортировки чисел | 1986 |

|

SU1394214A1 |

| Устройство для цифрового функционального преобразования | 1981 |

|

SU993271A1 |

1. УСТ ЙСТВО ДЛЯ УПОРЯДО7 ЧИВАНИЯ ЧИСЕЛ, содержащее п групп входных элементов И, п входных рёгистров, п групп элементов И перезаписи, п -.1 групп по 1( в каждой группе схем сравнения ,п- 1 групп по 1с в каждой группе триггеров, блок синхронизации, г элементов ИЛИ, h реверсивных счетчиков, п элементов И-НЕ, группы элементов заД(жки, блок памяти,, группу выходных элементов ИЛИ, п групп выходных элементов И, причем кодовая шина чисел устройства соединена с информационными входами входных элементов И групп, выходы элементов И каждой группы соединены с информационными входами соответствующего входнрго регистра, выходы разрядов каждого регистра соединены с информационными входами элементов И перезаписи соответствующей группы и информационными входами выходных элементов И .соответствующей группы, вьлходы элементов И перезаписи каждой

1

Изобретение относится к области вычислительной техники, в частности, к устройствам автоматической сортировки и формирования заданной последовательности кодов обрабатываемых массивов цифровой информации сравнением числовых значений кодов и может быть использовано в устройствах автоматической обработки цифровой информации и .дискретной автоматики,

Известно устройство сортировки и системы обработки данных, позволяющее формировать заданную последова-. тельность элементов, упорядочено размещенных от элементов низшего порядка до элементов высшего порядка. Устройство Содержит память для хранений подлежащих йортировке кодов чисел.

несколько буферных регистров, каждый из которых обеспечивает запоминание кода одного числа, несколько схем сравнения, каждая из которых служит для сравнения кода числа, считанного из буферного регистра, с кодом числа считанным из памяти, и для формирования в каждой схеме сравнения выходных сигналов Больше и Равно, меньше. В устройстве предусмотрено несколько узлов адресации для хранения адресов кодов чисел в адресной последовательности, в которой адреса кодов чисел соответствуют кодам чисел хранящимся в буферных регистрах, Для подключения буферных регистров к схемам сравнения предусмотрено несколько селекторов, к.ожлии из которых управляется адресом кода числ хранимым в соответствующем узле адресации. Узел передачи состоит из нскольких схем передачи, каждая из кторых включается между соответствующим одним узлом адресации и соседним с ним узлом, адресации с целью селективной передачи адресов кодов чисел между узлами адресации при формировании соответствующей схемой сравнения выходного сигнала Больше. Узел передачи содержит блок для передачи адреса каждого кода числа из памяти в любой из узлов адресации, которому соответствует выходной сигнал Больше на одном плече связанной с ним схемы сравнения и сигнал Равно, меньше на другом плече. Указанный узел передачи упорядочивает адресную последовательность адресов кодов чисел.Выходной узел служит для считывания кодов чисел из буферных регистров, выбранных селекторами, в установленном порядке адресов кодов .

.Недостатком известного устройства являются низкие функциональные возможности, выражающиеся в ограниченности числа вариантов упорядочивания кодов чисел массива, что не позволяет формировать последовательность кодов чисел, расположенных в порядке их убывания.

Известнотакже устройство для сортировкиmn-разрядных чисел, содержащее п регистров, выходы каждого из которых соединены с входами схем сравнения, другие Бх.ор}л которых подключены к выходам регистра результата, выходные шины схем сравнения соединены через переключатели с входами элемента ИЛИ, элемента И, тригге|1) и узлы запрета. Выход равенства ка:ждой схемы cpafeнения соединен, с управляющим входом соответствующего узла запрета, другие входы которого подключены к управляющим шинам устройства, а выход - к одному из входов первого элемента И, другой вход котброго соединен с выходной шиной устройства, а выход - с управляющим вхдом схемы сравнения. Выход элемента ИЛИ соединен с входом триггера, другой вход которого соединен с шиной тактовых сигналов, а выходы через переключатель - с входом второго элемента И, другой вход которого соединен с управляющей шиной устройства, а выход - с входом устаHOBkH в нулевое состояние регистра результата. Входы поразрядного управления регистра результата подключены к выходам коммутатора, .вход которого соединен с шиной тактовых .сигналов, а входы установки в единичное состояние разрядов ре1-истра результата .подключены к управляющей шине устройства 12 Э.Недостатком данного устройства являются низкие функциональные возможности, заключающиеся в невозможности оперативного изменения порядка размещения чисел в упорядочиваемом массиве.

Наиболее близким к предложенному является устройство для упорядочивания, чисел, содержащее п групп вход ных элементов И,п входных регистров, п групп элементов И перезаписи, п-1 групп по 1с в каждой группе схем сравнения, п-1 групп по в кеждоЛ группе триггеров, блок синхронизации, группу из элементов ИЛИ,п реверсивных счетчиков,п элементов И-НБ элементы задержки, п групп выходных элементов И, группу элементов ИЛИ, блок памяти, Информационные входы устройства соединены с информационными входами входных элементов И групп, выходы элементов И каждой i-и группы, где i 1,2,,.,,п подключены к «н.формационным входам 1 -го входного регистра, выходы каждого -го входного регистра соединены с информационными входами элементов И перезаписи i-H группы,, выходы элементов И перезаписи каждой (i- 1)-й группы подключены к первым информационным входам схем сравнения i-и группы, выходы Больше, и Равно, меньше каждой j-й схемы сравнения z-и группы, где 1 1,2,...,(п .- Z ); 2 1,2,.,,п- 1, соединены с входами установки в единичное и нулевое состояние соответственно J-ro триггера 2-й группы. Вторые информаг ционные. входы каждой j-й схемы сравнения z-й группы подключены к Bbdtoдам элементов И перезаписи (i +1)-й группы, прямой выход каждого j-ro триггера первой группы соединен с. первым входоА ( j+ 1)-гЬ элемента ИЛИ инверсный выход первого триггера первой группы подключен к первому .входу первого элемента ИЛИ, инверсные выходы, второго, третьего,.,., (п - 1)-го триггеров первой группы соединены через первый, второй,..., (п - 2)-и элементы зад ержки первой группы с.вторым, третьим, ..., (п - 1)-м входами первого элемента ИЛИ, прямой выход каЬкдого j-го триггера каждой 2-й группы через j-й эле-, мент задержки z-й группы подключен к j-му входу i-го элемента ИЛИ, инверсный выходкаждого j-го триггера каждой z-й группы соединен через (п - )-й элемент задержки с (h-i+j )-м входом ( t- 1) го элемента ИЛИ. Выход кеикдого -го элемента ИЛИ подключен к информационному входу 1-го реверсивного счетчика, выходы каждого 1-го реверсивного счетчика соединены с входами

i -го элемента И-НЕ. Выходы каждого i -го входного регистра подключены к информационным входам выходных элементов И i-и группы, выход каждого 1-го элемента И-НЕ соединен с первым управляющим входом выходных элементов И i-и группы. : Выходы выходных элементов И групп оедйнены с входами эЛементов -ИЛИх группы,выходы которых подключены к входам блока памяти. Управляющий вход устройства соединен с входом блока синхронизации, первый выход которого подключен к управляющим входам входных элементов И групп, второй выход соединен с управляющими входами элементов И перезаписи, а третий, четвертый и пятый выходы блока синхронизации соответственно подключены к управляющим входам выходных элементов И групп, реверсивных счетчиков и входных регистров,

В данном устройстве с помощью схем сравнения осуществляется попарное одновременное сравнение каждого из кодов в упорядочиваемом массиве с последующими кодами чисел.

Число схем сравнения равно числу сочетаний из количества кодов чисел в анализируемом массиве по два. Результаты сравнения кодов чисел преобразуются с помощью триггеров, элементов задержки и элементов ИЛИ в число-импульсные коды, записываемые в реверсивные счетчики. Количество посылок в число-импульсных кодах равно числу случаев, когда данное число оказывается больше чисел из упорядочиваемого массива. Последовательным анализом указанных выше число-импульсных кодов с помощью реверсивных счетчиков и узлов анализа нулевых состояний {.элементы И-НЕ) последовательно выбирают числа по значениям этих кодов (рангов ) и выдают через элементы ИЛИ в блок памяти в убывающем порядке З.

Недостатком такого устройства являются низкие функциональные возможности, заключающиеся в невозможности оперативного изменения порядка размещения кодов чисел в упоряочиваемом массиве.

Цель изобретения расширение функиональных возможностей путем опеативного изменения порядка размеения кодов в упорядочиваемом массие.

Поставленная цель достигается ем, что устройство для упорядочиания чисел, содержащее п групп входых элементов И, г входных регист- . ов, п групп элементов И перезаписи, п - 1 групп.по k в каждой группе хем сравнения, п - 1 групп по с в аждой группе триггеров, блок синронизации , п элементов ИЛИ,,п реверсивных счетчиков,п элементов И-НЕ, группы элементов задержки, блок памяти, группу выходных элементов ИЛИ, п групп выходных элементов И,причем кодовая шина чисел устройства соединена с информационными входами входных элементов И групп, выходы элементов И каждой группы соединены с информационными входами соответствующего входного регистра, выходы разрядов каждого регистра соединены с информационными входами элементов И перезаписи соответствующей группы и информационными входами выт ходных элементов И соответствующей группы, выходы элементов И перезаписи каждой ( i - 1)-й (...) группы соединены с первой группой информационных входов схем сравнения i-и группы, выходы Больше и Равно, меньше каждой схемы сравнения соединены соответственно с - . входами установки в единичное и нулевое состояние соответствующего триггера, вторая группа информационных входов каждой j-й схемы сравнения z-й группы, где ,2,... , t l,2,..;,n- 1, соединена с выходами.элементов И перезаписи + 1,-й группы, прямой выход каждого j-ro триггера первой группы соединен с первым входом (j+ 1 -го элемента ИЛИ, инверсный.выход первого триггера первой группы соединен с первым входом первого элемента ИЛИ, инверсные выходы второго третьего,..., П - 1 -го триггеров первой группы соединен{л через первый, второй,...,п- 2 -и элементызадержки первой группы с вторьлм, третьим,...,(л- 1)-м входами первого элемента ИЛИ, прямой выход каждого j-ro триггера каждой i-й груп- пы через j-й элемент задержки z-й группы соединен с j-м входом i-to элемента ИЛИ, инверсный выход каждого j-ro триггера каждой ±-й группы соединен через ( )-й элемент задержки с ( )-м.входом (i - 1)-го элемента ИЛИ, выход каждого элемента ИЛИ соединен с информационным входом соответствующего реверсивного счетчика, выходы каждого реверсивного счетчика соединены с соответствующими входами элементов -И-НЕ, выходы выходных элементов И групп соединены с соответствующими входами выходных элементов ИЛИ группы, выходы которых соединены с входами блока памяти, кодовые шины управления устройства соединены с входами блока синхронизации, первый выход которого соединен с управляющим входом входных элементов И групп второй выход соединен с управляющими входами входных регистров, третий выход соединен с управляющими входами элементов И перезаписи групп, четвертый выход блока синхронизации соединен с первыми управляющими входами выходных элементов и групп, пятый выход блока синхронизации соединен с первыми управляющими входами реверсивных счетчиков, дополнительно содержит п управляемых элементов И, п дополнительных элементов ИЛИ, причем информационные входы управляемых элементов И соединены с соответствующими выходами соответствующих реверсивных счетчиков, шесто выход блока синхронизации соединен вторыми управляющими реверсивных счетчиков, седьмой и восьмой выходы блока синхронизации соединен с управляющими входами элементов И-НЕ и управляемых элементов И соответственно, выходы которых чере соответствующие дополнительные элементы ИЛИ соединены с вторыми управляющими входами соответствующих выходных элементов И групп.

Блок синхронизации содержит формирователи импульсов, элементы задержки, триггеры, элементы ИЛИ, И-Н НЕ, И, счетчик, генератор тактовы с. импульсов, управляющий триггер,причем, вход блока синхронизации со динен с входом установки в единичное состояние первого триггера входом

.первого формирователя импульсов и входом первого элемента задержки, выход KOTQporo соединен с входом второго формирователя импульсов, выход которюго соединен с входом установки в нулевое состояние первого триггера, входом второго элемента задержки и единичным входом второго триггера, выход второго элемента задержки соединен с входом второго формирователя импульсов, выход которого соединен с нулевым входом второго триггера и входом третьего элемента задержки, выход которого соединен с входом третьего формирователя импульсов, выход которого соединен с первым входом элемента ИЛИ, выход элемента ИЛИ соеди-нен с единичным входом третьёгб триггера и через четвертый элемент задержки и четвертый формирователь импульсов с входом запуска генератора тактовых импульсов и нулевым входом третьего триггера, выходы счетчика соединены с входами элемента И-НЕ, выход которого соединен с входом останова генератора

.тактовых импульсов, прямые выходы первого, второго и третьего триггеров соединены с первым, третьим и четвертым выходами блока, выход первого формирователя соединен с вторым лыходом блока, прямой и инверсный выходы управляющего триг. гера соединены с перзъаля входами

соответственно второго и третьего элементов И,- вторые входы которых

соединены свыходами первого элемента И, выходы второго и третьего элементов И Являются соответственно пятым и шестым выходами блока, входы установки в нулевое и единичное состояния управляющего тригге{4а соединены с кодовой шиной управления устройства, прямой выход управляющего триггера соединен через элемент НЕ с седьмьвл

0 выходом блока, а инверсный выход соединен с воськым выходом блока синхронизации.

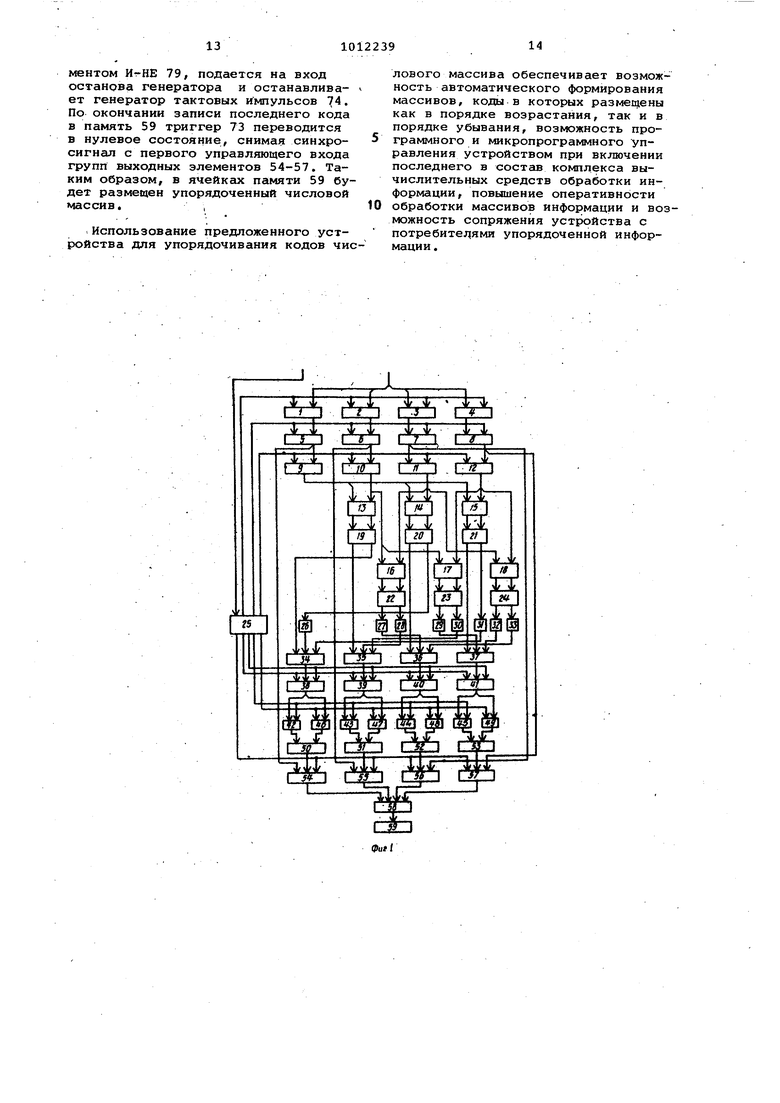

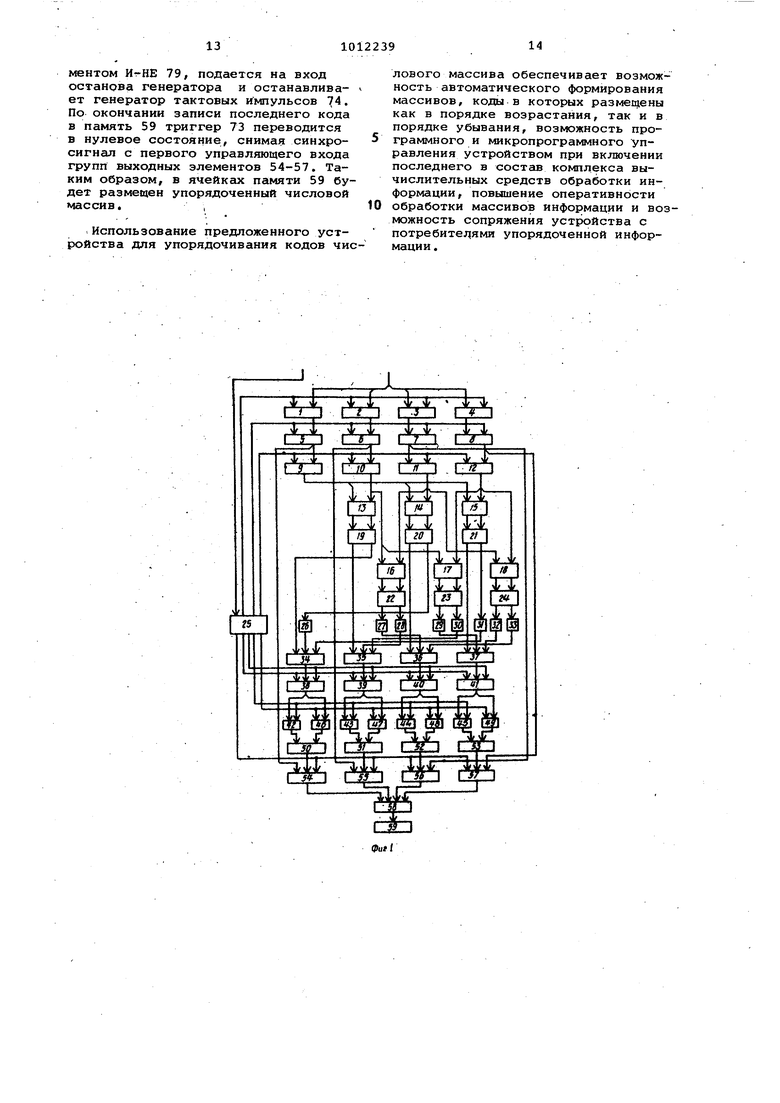

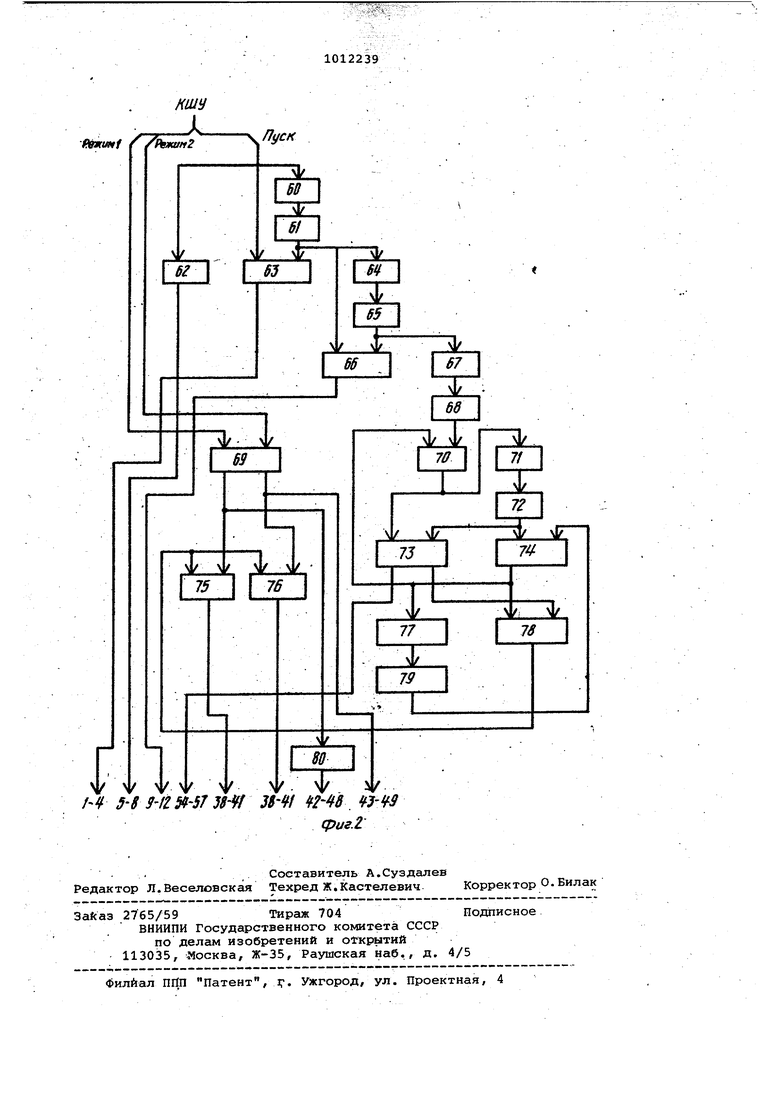

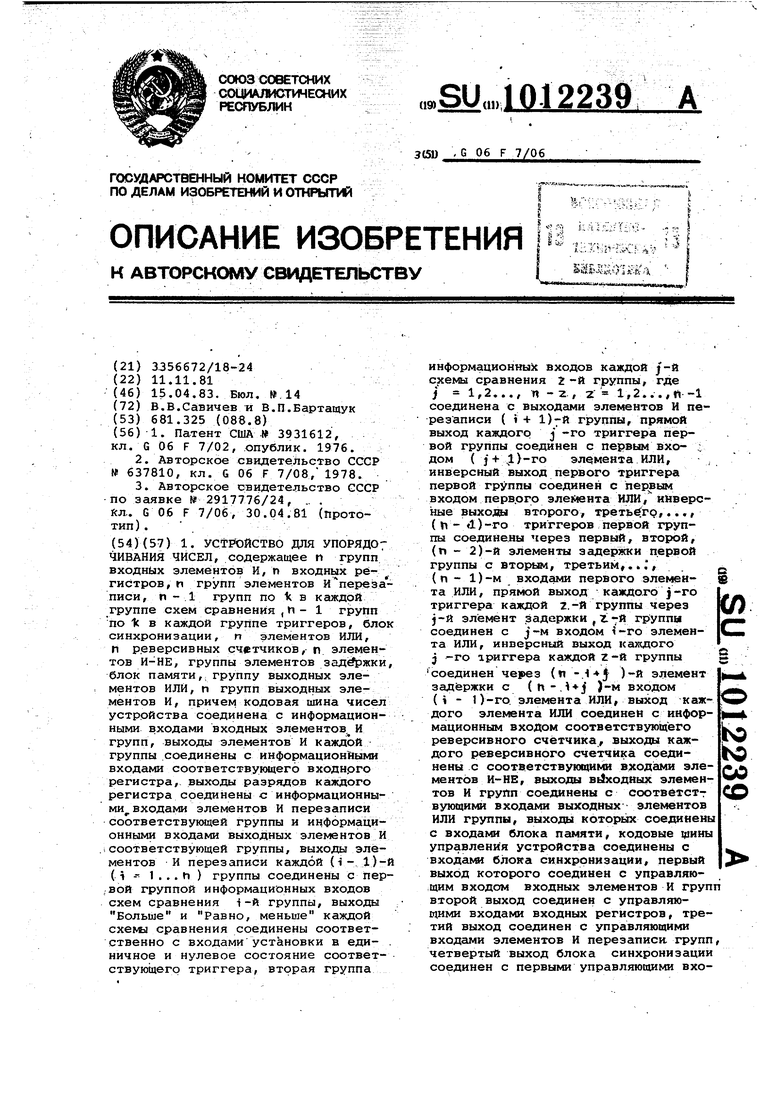

На фиг. 1 представлена структурная схема устройства длд случая упо- . рядочения четырех кодов числового

5 массива; на фиг. 2 - структурная схема блока синхронизации, устройство содержит группы входных элементов И 1-4, вхфдные регистры 5 - 8, группы элементов И пе0ре записи 9-12, группы но три, две одной в каждой группе схем cfiaBjieния 13-15, .16-17 и 18, группы по три, два, одному в каждой группе триггеров 19-21, 22-23 и 24, блок

5 синхронизации 25, элементы задержки 26-33, группы, группу элементов ИЛИ 34-37, реверсивные счетчики 38-41 элементы И-НЕ 42-45, уп авляемыё элементы И 46-49, группу элементов

0 ИЛИ 50-53, группу выходных элемен-. тов И 54-57, группу элементов ИЛИ 58, блок памяти 59..

Блок синхронизации 25 содержит элемент задержки 60, формирователи

5 импульсов 61 и 62, триггер 63,- элемент задержки 64, формирователь импульсов 65, триггер 66, элемент задержки 67, формирователь импульсов 68, управляющий триггер 69, элемент ИЛИ 70, элемент задержки 71, форми0рователь импульсов 72, триггер 73, генератор тактовых импульсов (ГТИ) 74, элемент И 75, элемент И 76, реверсивный счетчик 77, элемент И 78, элемент.И-НЕ 79, элемент НЕ 80.

5 Устройство реализует метод полного упорядочивания массива числовой информации с использованием матрицы бинарных отношений и формированием число-импульсных кодов, оп0ределяющих порядок выдачи чисел. Устройство для упорядочивания кодов числового массива может ра- . ботать в режиме упорядочивания кодов числового массива в убывающем по5рядке (режим 1) и режиме упорядочивания кодов числового массива в возрастающем порядке (режим 2).

Режим упорядочивания устанавливается с помощью управляющего триг0гера 69. При подаче управляющего сигнала Режим 1 на единичны вход триггера 69 осуществляет : размещение кодов числового массива в блоке памяти 59 в убывающем порядке, при подаче сигнала .Режим 2

5 на в.ход установки в нулевое состоя ние триггера 69 размещение кодов числового массива в блоке памяти 59 осуществляется в возрастающем порядке, В исходном состоянии входные регистры 5-8, триггеры 19-24, реверсивные счетчики 38-41, регистры блока памяти 59 могут быть обнулены (после включения устройства ил хранить информацию, сохранившуюся после предыдущего такта работы. Перед началом работы устройства в очередном такте необходимо установить режим упорядочивания, для чего по кодовой шине управления на триггер 69. необходимо подать сигнал Режим 1 или Режим 2. Триггер 69, возбужденный по единичному или нулевому входу, обеспечивает коммутацию элементов И 75 и 76, выдав тактовые импульсы или на обратный (режим 1) или на прямой (режим 2) управляющие входы реверсивных счетчиков 38-41, а также управление эле ментами И-НЕ 42-45 и элементами И 46-49, снимая запрет с управляющего входа элементов И-НЕ 42-45 или выдавая разрешающий сигнал на элементы 46-49. После установки режима упорядочивания по кодовой шине управления поступает сигнал Пуск, по котором начинается работа устройства. По сигналу Пуск наВыходе формирователя импульсов 62 вырабатывается синхросигнал, поступающий на. второй выход блока синхронизации 25 по которому обнуляются входные регистры 5-8. Одновременно сигнал Пуск поступает на вход установки в нулевое состояние триггера 63 и вход элемента задержки 60. Триггер 63, переведенный в единичное состояние, на первом выходе блока 25 .синхронизации формирует синхросигнал, выдаваемый на управляющие входы элементов И 1-4 и разрешающей запись кодов чисел массива во входные регистры 5-8. Через интервал времени, определяемый задержкой элемента 60 if обес печивающий прием по кодовой шине числа и запись во входные регистры 5-8 кодов числа, триггер .63 переводится в нулевое состояние. Одновременно триггер 66 переводится в единичное состояние, формируя на третьем выходе блока синхронизации 25 синхросигнал перезаписи, который поступает на управляющие входы групп элементов И перезаписи 9 12. По этому синхросигналу коды чисел упорядочиваемого массива, хранимые во входных регистрах, одновременно выдаются в схемы сравнения 13-18. Длительность синхроимпульса перейаписЦ обусловливается временем задержки в элементе задержки 64 и определяется временем прохождения сигнала через элемент И, схему сравнения, а также временем срабатывания триггера знака. Каждая из схем сравнения 13-18 обеспечивает сравнение двух кодов числового массива и выделение разностного сигнала. Операция сравнения кодов чисел реализуется вычитанием анализируемых кодов с последующим анализом знака разности. Соотношение Больше представляется высоким потенциалом на выходе знакового разряда формируемой разности, а соотношение Равно, меньше,. - низким потенциалом. Результаты сравнения чисел фиксируются триггерами 19 - 24 и преобразуются с помощью элементов задержки 26-33 и элементов ИЛИ 34 37 в число-импульсные коды, количё.ство посылок в которых равно числу случаев, когда данное число оказывается больше чисел из рассматриваемого массива. По окончании срабатывания триггеров 19-24 сигналом, задержанным элементом задержки 64, обнуляется триггер 66. Элемент задержки 67 обеспечивает задержку на время формирования число-импульсных кодов и их записи в реверсивные счетчики 38-41. Длительность задержки может быть определена из формулы , где Смд, - время распространения сигнала в элементе ИЛИ; тг - время срабатывания триггера реверсивного счетчика; п - число упорядочиваемых кодов массива. Формирование число-импульсных кодов, характеризующих место числа в упорядоченном массиве, осуществляется с помощью реверсивных счетчиков 38 41. Сигналы сравнения с выходов триггеров 19 - 24 . элементы ИЛИ 34 37 последовательно поступают на входы реверсивных счетчиков и переводят в единичные состояния соответствующие триггеры. Последовательная запись сигналов, необходима я для обеспечения устойчивого срабатывания триггеров, осуществляется элементами задержки 26-33, подключаемыми к входам элементов ИЛИ 34-37, начиная со второго. При упорядочивании кодов числового массива в убывающем порядке выборка числа для его выдачи осуществляется по нулевому состоянию реверсивного счетчика. Анализ нулевого состояния реверсивного счетчика и его фиксация осуществляется элементами И-НЕ 42-45. Сигналы на выходе элементов и-НЕ 42-45 формируются при усл вии отсутствия на управляющих входа элементов запрещающего сигнала, пос тупающего с седьмого выхода блока синхронизации 25, соединенного чере элемент НЕ 80 с единичным выходом Триггера 69. Разрешающий сигнал, сформированный на выходе элементов И-НЕ 42-45, через элементы ИЛИ 50 53 поступает на второй управляющий вход групп выходных элементов И 54-5 При упорядочивании кодов числового массива в возрастающем порядке выборка числа дляего выдачи осуществляется по состоянию.счетчика, соответствующему минимальному числу массива. Данное состояние определяется как код числа, меньшего числа упорядочиваемых кодов на единицу, и фиксируется с помощью элементов И 46-49. Информационные входы элементов И 46-49 подключаются к.прямым выходам триггеров счетчиков, которые для заданного числа кодов масс ва должны находиться в единичном состоянии, и инверсным выходам три геров , которые должны находиться . в нулевом состоянии. Управляющие в ды элементов И 46-49 подключены к восьмому выходу блока синхронизации 25, с которого поступает управ ляющи й сигнал, формируемый триггером 69, находящимся в нулевом состоянии , Разрешающий сигнал, сформирован ный на выходах элементов И 46-49, через элементы ИЛИ 50 и 51 посту-, пает также на второй управляющий .вход групп выходных элементовИ54Сигнал, задержанный элементом задержки 67 и усиленный формирователем импульсов 68, через элемент ИЛИ 70 поступает на вход триггера 73 и переводит гЪ в единичное состояние. Триггер 73 на четвер м выходе блока синхронизации 25 формирует синхроимпульс, обеспечиваю щий управление группами выходных элементов И 54-57. Длительность синхроимпульса определяется временем записи кода числа в блок памяти 59.. При наличии на входах одной из групп выходных элементов И 54-57 разрешающего сигнала, поступающего с выхода элементов ИЛИ 50-53, и синхроимпульса с четвертого выхода блока синхронизации 25 наибольший код числа с выхода соответствующего входного регистра через одну из групп выходных элементов И 54-57 и группу элементов ИЛИ 58 поступае на вход блока памяти 59 для записи По окончании синхроимпульса,ког да т иггер переведен в нулевое сос тояние, запускается генератор такт вых импульсов 74. Импульс с выхода генератора тактовых импульсов 74 через элемейт И 78, на второй вход которого подан разрешающий потенциал с инверсного выхода триггера 73, и через элемент И 75 или элемент И 76 (в зависимости от режима упорядочивания ) поступает на обратный или прямой выходы реверсивных счетчиков 38-41. При упорядочивании кодов числового массива в убывающем порядке импульс с выхода ГТИ 74 поступает через элемент И 75, возбужденный по второму входу напряжением с прямого выхода триггера 69, на обратные входы реверсивных счетчиков 38 41 одновременно в виде -сигнала -1 уменьшая содержимое счетчика на единицу. Для одного из реверсивных счетчиков 38-41 состояние которого стало нулевым, соответствующий из элементов И-НЕ 42-45 формирует сигнал, который через один из элементов ИЛИ 50-53 поступает на вторые входы одной из групп выходных элементов И 54-57, разрешая выдачу очередного кода числа в память 59. При этом синхроимпульс, управляющий группами выходных элементов И 54-57 формируется на четвертом выходе блока синхронизации 25 триггером 73, переведенным в единичное.состояние импульсом с выхода ГТИ 74 через . элемент ИЛИ 70. В случае упорядочивания кодов числового массива в убывающем порядке импульс с выхода ГТИ 74 поступает через элемент И 76, возбузкденный по второму входу напряжением Ъ ин-. версного выхода триггера 69, на прямые входы реверсивных счетчиков 38-41 одновременно-в виде сигнала +1, увеличивая содержимое чиков на единицу. Для одного из реверсивных счетчиков 38-41, состояние которого соответствует минимальному числу м ccивa соответствующий элемент И 46-49 формирует разрешающий сигнал, который через один из элементов ИЛИ 50-53 поступает на вторые входы одной из групп выходных элементов И 54-57, разрешая выдачу очередного кода числа в память 59. Импульс с выхода генератора тактовых импульсов 74 поступает одновременно на обратный вход реверсивного счетчика 77, уменьшая содержимое счетчика на единицу. Реверсибный счетчик 77 обеспечивает подсчет числа сформированных такэговыос импульсов, т.е. числа кодов, выданных в память 59. После выдачи последнего кода упорядочиваемого массива содержимое реверсивного счетчика 77,становится равным нулю. Данное состояние счетчика фиксируется элементом И-НЕ 79. Сигнал, формируемый элементом ИГ-HE 79, подается на вход останова генератора и останавливает генератор тактовых импульсов 74. По окончании записи последнего кода в память 59 триггер 73 переводится в нулевое состояние, снимая синхросигнал с первого управляющего входа групп выходных элементов 54-57. Таким образом, в ячейках памяти 59 будет размещен упорядоченный числовой массив. I

Использование предложенного устройства для упорядочивания кодов числового массива обеспечивает возможность автоматического формирования массивов, коды в которых размещены как в порядке возрастания, так и в порядке убывания, возможность программного и микропрограммного управления устройством при включении последнего в состав комплекса вычислительных средств обработки информации, повышение оперативности обработки массивов информации и возможность сопряжения устройства с потребите; ями упорядоченной информации .

L

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Патент США | |||

| 3931612, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Планшайба для точной расточки лекал и выработок | 1922 |

|

SU1976A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Кл, | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1983-04-15—Публикация

1981-11-11—Подача