ничным выходом второго командного триггера и первым входом второго эл мента ИЛИ, вход первого элемента НЕ через генератор одиночного импульса соединен с единичным входом первого командного триггера и выходом элемента задержки, вход которого соеди нен с единичным входом третьего командного триггера и вторыми входами четвертого и пятого элементов ИЛИ, выход пятого элемента ИЛИ соединен нулевьм входом первого команднбго триггера, единичный и нулевой выходы которого соединены соответственно с первыми входами пятого и шесто го элементов И, вторые входы кото рых соединены соответственно с выходом второго элемента НЕ и единичным выходом третьего командного триггера, вход второго элемента НЕ соединен с выходом первого элемента И, нулевой выход третьего командного триггера соединен с вторым входо третьего элемента ИЛИ, первый и второй входы седьмого элемента И соединены соответственно с единичным выходом второго командного триггера и нулевым выходом триггера знака, нулевой вход которого соединен с выходом седьмого элемента ИЛИ первый вход которого соединен с вто рым входом шестого элемента ИЛИ, входом сброса реверсивного счетчика адреса и входом элемента задержки, единичный вход триггера пе, реполнения соединен с выходом восьйрго элемента И, первый и второй входы которого соединены соответственно с единичным выходом первого командного триггера и первым входом девятого элемента И, второй вход которого соединен с входом второго формирователя импульсов и первым входом десятого элемента И, выход которого соединен с вторым входом седьмого элемента ИЛИ, третий вход которого соединен с выходом первого элемента ИЛИ, выход девятого элемен та И соединен с единичным входом триггера знака, а также блок местного управления, содержащий первый, второй триггеры, счетчик тактов нул визации, дешифратор, генератор импульсов, первый, второй, третий, четвертый, пятый, шестой, седьмой элементы задержки, формирователь им пульсов, первый, второй, третий, че вертый, пятый, шестой, седьмой, восьмой, девятый, десятый, одиннад00цатый, двенадцатый, тринадцатый элементы И, первый, второй, третий, четвертый элементы ИЛИ, НЕ, причем первые входы элементов И с первого по пятый соединены с единичным выходом первого триггера, второй вход первого элемента И соединен с первым входом первого элемента ИЛИ. второй вход которого соединен с нулевым выходам первого триггера, нулевой вход которого через формирователь импульсов соединен с первым выходом дешифратора, вход которого соединен с выходом счетчика тактов нулевизадии, последний выход дешифратора соединен с первым входом шестого элемента И, второй вход которого через первый элемент задержки соединен с первыми входами седьмого и восьмого элементов И, вторые входы которых соединены соответственйо с первыми входами первого и шестого элементов И, первьш вход восьмого элемента И соединен через второй элемент задержки с выходом третьего элемента задержки, вход которого соединен с выходом четвертого элемента задержки, единичный выход второго триггера соединен с первым входом девятого элемента И и с входом генератора импульсов нулевизации, выход которого через пятый элемент задержки соединен с вторым входом девятого элемента И, выход которого соединен с входом счетчика тактов нулевизации, вход сброса которого через шестой элемент задержки соединен с выходом второго элемента ИЛИ и с нулевым входом второго триггера, единичный вход которого соединен с единичным входом первого триггера и с первым входом третьего элемента ИЛИ, второй вход и выход которого соединены соответственно с выходом девятого элемента И и входом четвертого элемента задержки, выход шестого эл.емента И соединен с первыми входами десятого и одиннадцатого . элементов И и первым входом второго элемента ИЛИ, выход десятого элемента И соединен с входом седьмого элемента задержки и с первым входом четвертого элемента ИЛИ, второй вход которого соединен с вькодом одиннадцатого элемента И, выход восьмого элемента И соединен с первыми входами двенадцатого и тринадцатого элементов И, вторые входы которых соединены соответственно с выходом и

входом элемента НЕ, вход делителя (Устройства соединен с первым информационным входом первого мультиплексора, второй информационный вход которого соединен с информационным входом стековой памяти и выходом буферного регистра, информационный вход которого соединен с адресным входом блока хранения констант нулевизации и выходом сумматора-вычитателя по основаниям Р,- , первый и второй информационные входы которого соединены соответственно с выходами второго и третьего мультиплексоров, первый второй и третий информационные входы второго мультиплексора соединены соответственно с вькодами регистра делимого, регистра-делителя и блока хранения констант нулевизации, первый, второй, и третий информационные, входы третьего мультиплексора соединены соответственно с выходами регистра делителя стековой памяти и сумматора-вычитателя по основаниям р. , выход первого мультиплексора соединен с информационным входом регистра делителя, выход блока хранения констант частного соединен с информационным входом сумматора частного, вход Пуск устройства соединен с единичным входом третьего командного триггера блока управления и вторым входом второго элемента РШИ блока местного управления адресные входы блока хранени констант частного и стековой памяти со- единеиы с выходами группы реверсивного счетчика адреса, вход сброса сумматора частного соединен с входом записи регистра делимого, выходом первого элемента задержки блока управления и третьим входом четвертого элемента ИЛИ блока местного управления, первый и второй управляю щие входы первого мультиплексора соединены соответственно с выходами генератора одиночного импульса и первого элемента НЕ блока управлени первый, второй и, третий управляющие входы второго мультиплексора соединены соответственно с выходами четвертого и третьего элементов И и нулевым выходом первого триггера блока местного управления, первый

второй и третий управляющие входы третьего мультиплексора соединены соответственно с выходами второго и первого элементов И и нулевым выходом первого триггера блока местно- го управления, входы записи регистра делителя и буферного -регистра соединены соответственно с выходами етвертого элемента ИЛИ и седьмого элемента И блока местного управления, входы приема, записи, вьгаитания и сложения сумматора-вычитателя по основаниям Р соединены соответст- венно с выходами четвертого и третьего элементов задержки, выходами первого элемента ШШ и пятого элемента И блока местного управления, вход элемента НЕ которого соединен с младшим разрядом выхода сумматоравычитателя по основаниям , входы разрешения блока хранения констант нулевизации и блока хранения констант частного соединены соответственно с выходом дешифратора блока местного управления и нулевым выходом триггера знака блока управления, вход режима стековой памяти соединен с выходом одиннадцатого элемента И блока местного управления, входы записи и сложения сумматора частного соединены соответственно с вьрсодами десятого элемента И и седьмого элемента задержки блока местного управления, единичные выходы первого и второго командных триггеров, выходы первого элемента ИЛИ, шестого элемента И, третьего элемента ИЛИ, седьмого элемента И, нулевой выход триггера переполнения, выход пятого элемента И блока управления соединены соответственно с вторыми входами пятого и первого элементов И, первШм входом третьего элемента ШШ, вторыми входами четвертого, третьего, десятого, одиннадцатого и второго элементов И блока местного управления, выходы шестого, десятого, двенадцатого и тринадцатого элементов И блока местного управления соединены соответственно с вторым входом четвертого элемента И, нулевым входом третьего командного триггера, вторыми входами десятого и восьмого элементов И блока управления.

f

Изобретение относится к вычислительной технике и может быть исполь. зовано для выполнения операций деления в ЭВМ, использующих систему остаточных классов (СОК), в частности в системах автоматизированного управления и цифровой обработки сигналов .

Известно устройство для деления чисел, содержащее регистр делимого, регистр делителя, регистр частного, сумматор, блок управления, блок деления на два, блок формирования дополнения, блок формирования цифр частного и элемент сравнения 1 ),

Недостаток данного устройства невысокое быстродействие.

Наиболее близким по технической сущности к изобретению является устройство для деления, содержащее регистр делимого, регистр делителя, блок выбора элементарного делителя, блок вычисления итерации, блок конца итерации, блок конца деления, сумматор, блок умножения, блок вычита(ния , блок анализа произведения, блок режима работы сумматора, причем выход регистра делимого подключен к первому входу блока вычисления итерации, второй вход которого подключен к шине позиционного признака делимого, выход регистра делителя к входу блока выбора элементарного делителя, к третьему входу блока вычисления итерации и к первому вхо,ду блока умножения, выход блока элементарного делителя - к четвертому входу блока вычисления итерации, пя.тым входом подключенного к шине позиционного признака делителя и к второму входу блока умножения, третий вход которого подключен к первому входу сумматора, первому входу блока вычитания, первому входу блока конца деления, к выходу блока вычисления итерации и к входу блока конца итерации, выходом подключенного к второму входу блока конца деления и шестому входу блока вычисления итераций, выход блока конца деления подключен к четвертому входу

.блока умножения, к первому входу блока анализа произведения, к второму входу блока вычитания и к второму входу сумматора, выход блока умножения - к второму входу блока анализа произведения, выход которого подключен через блок режима ра4002

боты сумматора к третьему входу блока вычитания, выходом подключенного к седьмому входу блока вычисления итерации, выход сумматора соединен выходом устройства 2,

Недостатком известного устройств является невысокое быстродействие, обусловленное использованием итерационного алгоритма деления.

Целью изобретения являете повышение быстродействия.

Поставленная цель достигается тем, что устройство для деления в системе остаточных классов, содержащее регистр делимого, регистр делителя, сумматор-вычитатель по осно ваниям P(i l5,...h, п- количество оснований), сумматор частного, причем вход регистра делимого и выход сумматора частного являются соответственно входом делимого и выходо частного устройства, содержит первый, второй и третий мультиплексоры буферный регистр, блок хранения констант нулевизации, блок хранения констант частного,.стековую память, блок управления, содержащий реверсивный счетчик адреса, генератор тактовых импульсов, генератор одиночного импульса, первый и второй элементы НЕ, первый, второй, третий четвертый, пятый, шестой, седьмой, восьмой, девятый и десятый элементы И, первый, второй, третий, четвер1тый, пятый, шестой и седьмой элементы ИЛИ, первый, второй и третий

командные триггеры, триггеры переполнения и знака, элемент задержки, первый и второй формирователи импульсов, причем выходы группы реверсивного счетчика адреса подключены к соответствующим входам первого элемента И, выход генератора тактовых импульсов - к первым входам второго и третьего элементов И, выходы которых подключены соответственно, к входам вычитания и сложения реверсивного счетчика адреса и к первому и второму входам первого элемента ИЛИ, вход генератора тактовых импульсов - к выходу второго элемента ИЛИ, первым входом соединенного с вторым входом второго элемента И, второй вход второго элемента ИЛИ соединен с единичным выходом первого командного триггера,-с первым входом третьего элемента ИЛИ и с . вторым входом третьего элемента И, третий вход которого соединен с нулевым выходом триггера переполнения, выход первого, элемента И - с первым входом четвертого эл.емента И, выходом соединенного с первым входом четвертого элемента ИЛИ, выход которого соединен с нулевым входом второго командного триггера, единичным входом соединенного с первым входом пятого элемента ИЛИ и вьпсо- дом первого формирователя импульсов вход которого соединен с единичным выходом триггера переполнения, нулевым входом соединенного с выходом шестого элемента ИЛИ, первый вход которого соединен через второй формирователь импульсов с единичным выходом второго командного триггера и первым BXOfi;oM второго элемента ИЛ вход первого элемента НЕ через генератор одиночного импульса с единичньм входом первого командного триггера и выходом элемента задержки, входом соединенного с единичным входом третьего командного триггера и вторыми входами четвертого и пятого элементов ИЛИ, выход пятого элемента ИЛИ соединен с нулевым вхо дом первого командного триггера, единичный и нулевой выходы которого соединены соответственно с первыми входами пятого и шестого элементов И, вторыми входами соединенных соот ветственно с выходом второго элемен та НЕ и единичным выходом третьего командного триггера, вход второго элемента НЕ соединен с выходом зле- мента И, нулевой выход третьего командного триггера - с вторым входом третьего элемента ИЛИ, первый и вто рой входы седьмого элемента И - соответственно с единичным вькодом второго командного триггера и нулевым выходом триггера знака, нулевой вход которого соединен с выходом седьмого элемента ИЛИ, первым входом соединенного с вторым входом гаестого элемента ИЛИ, входом сброса реверсивного счетчика адреса и входом элемента задержки, единичный вход триггера переполнения соединен с выходом восьмого элемента И, первый и второй входы которого соединены соответственно с единичным выходом первого командного триггера и первым входом девятого элемента И, вторым входом соединенного с вхо дом второго формирователя импульсов и первым входом десятого элемента И, выход которого соединен с бторьм входом седьмого элемента ИЛИ, треть им входом соединенного с выходом первого элемента ИЛИ, выход девятого элемента И соединен с единичным входом триггера знака, а также блок местного управления, содержащий первый и второй триггеры, счетчик тактов нулевизации, дешифратор, генератор импульсов, первый второй, третий, четвертьй, пятый, шестой и седьмой элементы задержки, формирователь импульсов, первый, второй, . третий, четвертьиЧ, пятьй, шестой, седьмой, восьмой, девятьй, десятый, одиннадцатый, двенадцатьп и тринадцатый элементы И,первый, второ, третий н четвертыйэлементы ИЛИ, элемент НЕ, причем первые входы эле-, ментов И с первого по пятый соединены с единичным выходом первого триггера, второй вход первого элемента И - с первым входом первого элемента ИЛИ, второй вход которого соединен с нулевым вькодом первого триггера, нулевым входом соединенно-. го через формирователь импульсов с первым выходом дешифратора, вход которого соединен с выходом счетчика тактов нулевизации, последний выход дешифратора - с первым входом шестого элемента И, вторым входом соединенного через первый элемент . задержки с первыми входами седьмого и восьмого элементов И, вторые входы которых соединены соответственно с первыми входами первого и шестого элементов И, первый вход восьмого элемента И - через второй элемент задержки с выходом третьего элемента задержки, входом соединенного с выходом четвертого элемента задержки, единичный выход второго триггера соединен с первым входом девятого элемента И и с входом генератора импульсов нулевизации, выход которого через пятый элемент задержки соединен с вторым входом девятого элемента И, выходом соединенного с входом счетчика тактов нулевизации, вход сбросакоторого через шестой элемент задержки соединен с выходом второго элемента ШШ и с нулевым входом второго триггера, единичным входом соединенного с единичным входом первого триггера и с первым входом третьего элемента ИЛИ, второй вход и выход которого соединен соответственно с вькодом девятого элемента И и входом четвертого эле мента задержки, выход шестого .элем та И - с первыми входами десятого и одиннадцатого элементов И и первьш входом второго элемента ИЛИ, выход десятого элемента И - с входом седьмого элемента задержки и с первым входом четвертого элемент ИЛИ, вторым входом соединенного с выходом одиннадцатого элемента -И, выход восьмого элемента И соединен с первыми входами Двенадцатого и тринадцатого элементов И, вторые входы которых соединены соответственно с выходом и входом элемента НЕ, вход делителя устройства - с первым информационным входом первого мультиплексора, вторым информ ционным входом соединенного с информационным входом стековой памяти и выходом буферного регистра, информационный вход которого соединен с адресным входом блока хранения констант нулевизации и выходом сумматора-вычитателя по основаниям Р. первый и второй информационные вход которого соединены соответственно с выходами второго и третьего мультиплексоров, первый, второй и третий информационные входы второго мульти плексора - соответственно с вьгходами регистра делимого, регистра делителя и блока хранения констант ну левизации, первый, второй и третий информационные входы третьего мультиплексора - соответственно с выходами регистра делителя стековой памяти и сумматора-вычитателя по основаниям Р; , выход первого мультиплексора - с информационным входом регистра делителя, выход блока хранения констант частного .- с информа ционным входом сумматора частного, вход Пуск устройства - с единичны входом третьего командного триггера блока управления и вторым входом второго элемента ИЛИ блока местного управления, адресные входы блока хранения констант частного и стековой памяти - с выходами группы реверсивного счетчика адреса, вход сброса сз мматора частного - с входо записи регистра делимого, выходом первого элемента задержки блока управления и третьим входом четвертого элемента ИЛИ блока местного управления, первый и второй управляющие входы первого мультиплексора - . соответственно с выходами генератора одиночного импульса и первого элемента НЕ блока управления, первый, второй и третий управляющие входы второго мультиплексора - соответственно с выходами четвертого и третьего элементов И и нулевым выходом первого триггера блока местного управления, первый, второй и третий управляющие входы третьего мультиплексора - соответственно с выходами второго и первого элементов И и нулевым выходом первого триггера блока местного управления, входы записи регистра делителя и буферного регистра - соответственно с выходами четвертого элемента ИЛИ и седьмого элемента И блока местного управления, входы приема зяписи, вычитания и сложения сумматора-вычитателя по основаниям - соответственно с выходами четвертого и третьего элементов задержки, выходами первого элемента ИЛИ и пятого элемента И блока местного управления, вход элемента НЕ которого соединен с младшим разрядом выхода сумматора-вычитателя по основаниям Р. , входы разрешения блока хранения констант нулевизации и блока хранения констант частного соответственно с выходом дешифратора блока местного управления и нулевым выходом триггера .знака блока управления, вход режима стековой памяти с выходом одиннадцатого элемента И блока местного управления, входы за-. писи и сложения сумматора частного соответственно с выходами десятого элемента И и седьмого элемента задержки блока местного управления, единичные выходы первого.и второго командных триггеров, выходы первого лемента ИЛИ, щестого элемента И, . ретьего элемента ИЛИ, седьмого элеента И. нулевой выход триггера пееполнения и выход пятого элемента И лока управления соединены соответтвенно с вторыми входами пятого . первого элементов И, первым входомретьего элемента ИЛИ, вторыми вхоами четвертого, третьего, десятого, диннадцатого и второго элементов И лока местного управления, выходы естого, десятого, двенадцатого и ринадцатого элементов И блока местого управления - соответственно с

вторым входом четвертого элемента И, нулевым входом третьего командного | триггера, вторыми входами десятого и восьмого элементов И блока управления.

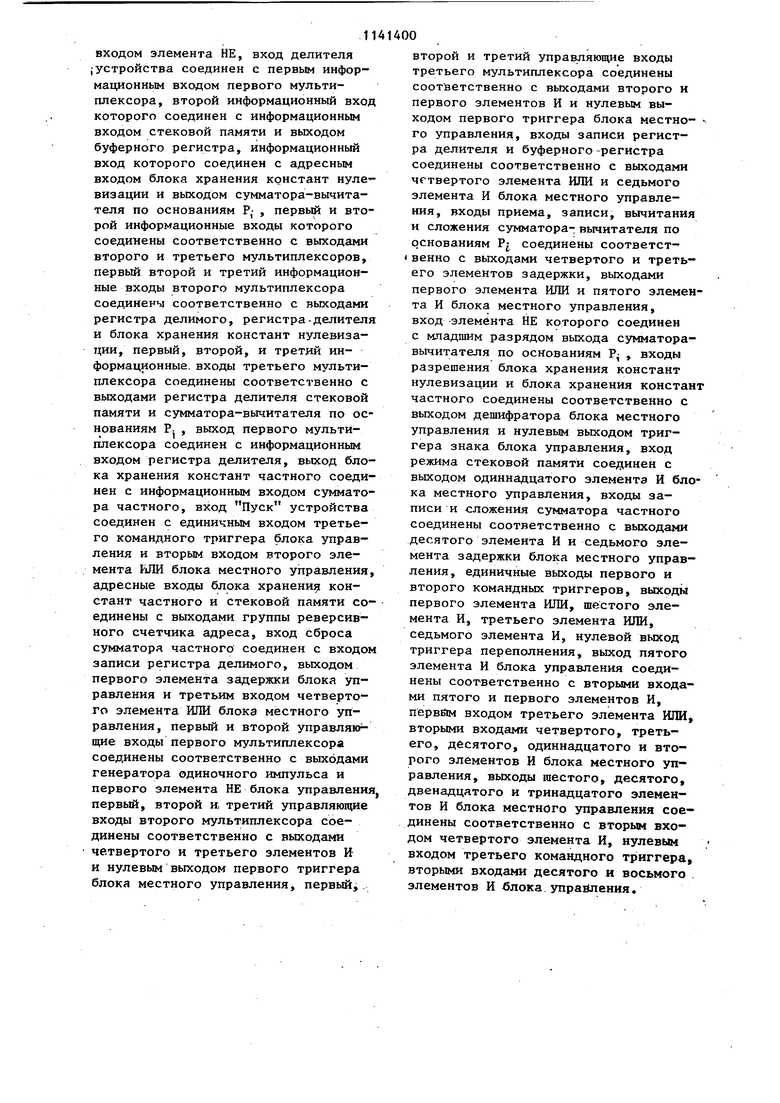

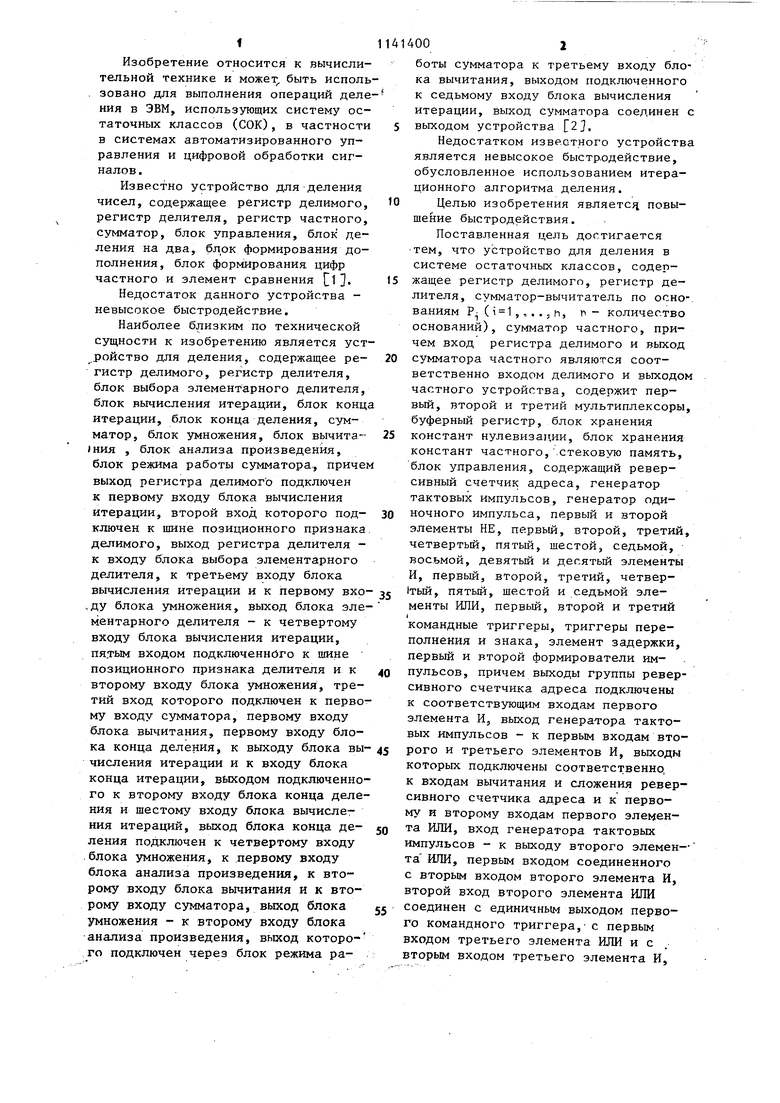

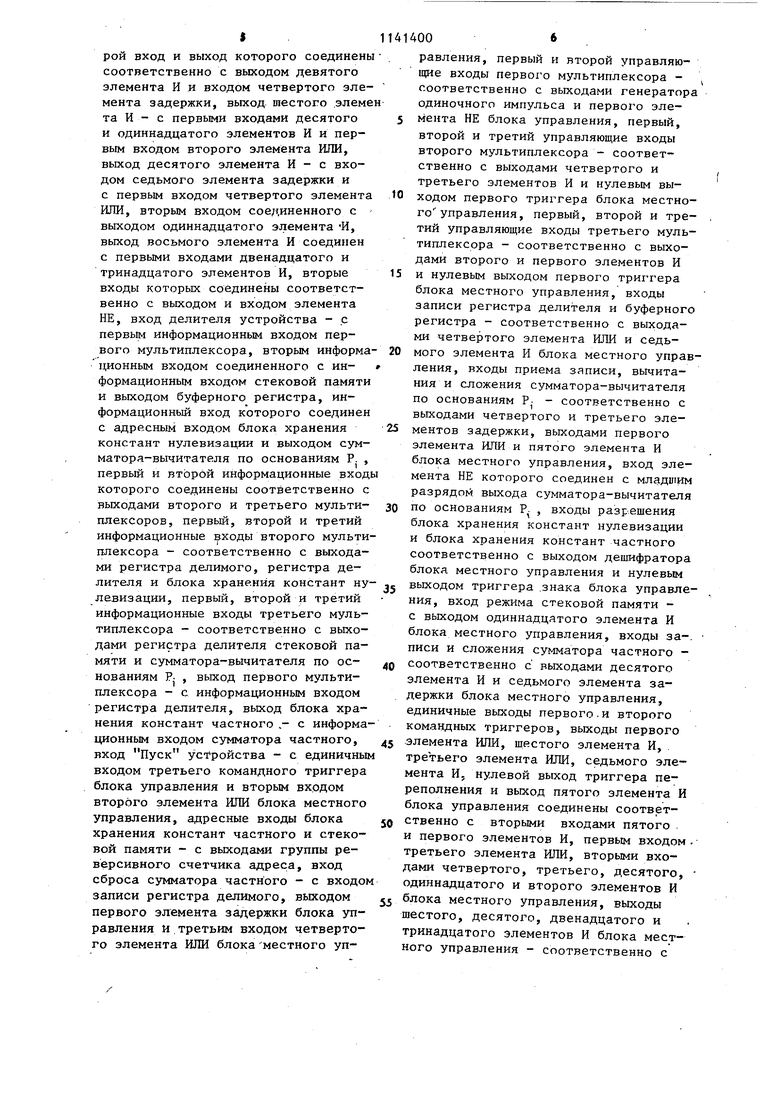

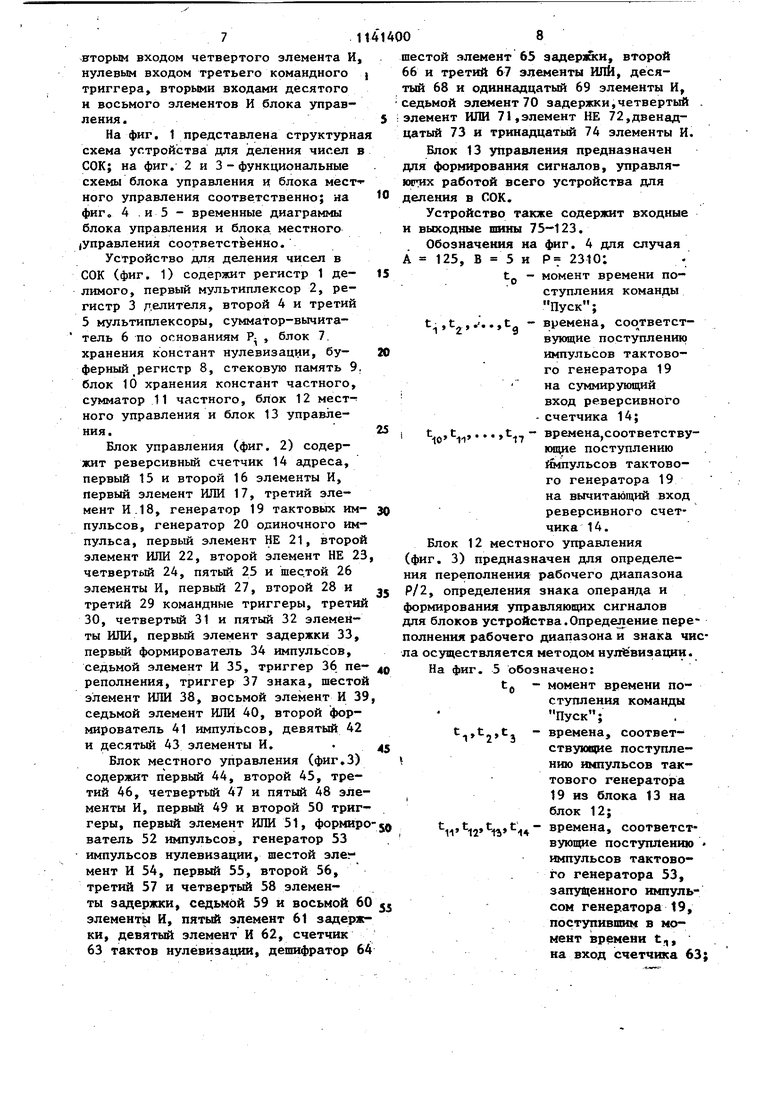

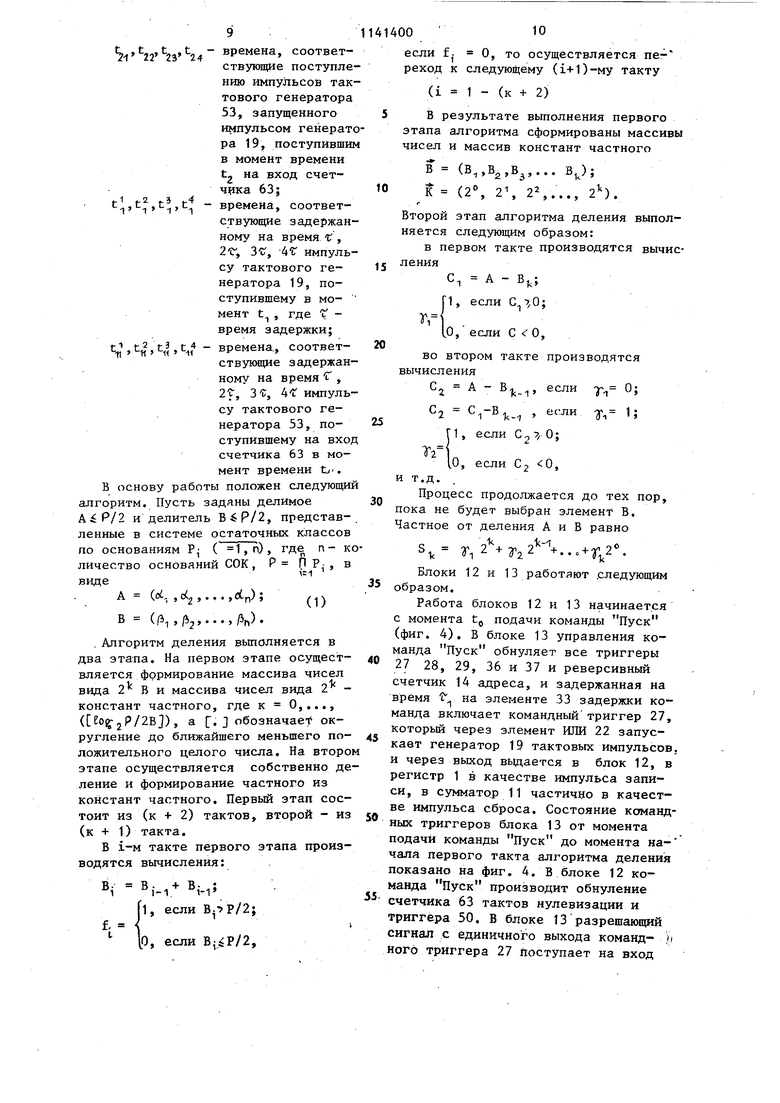

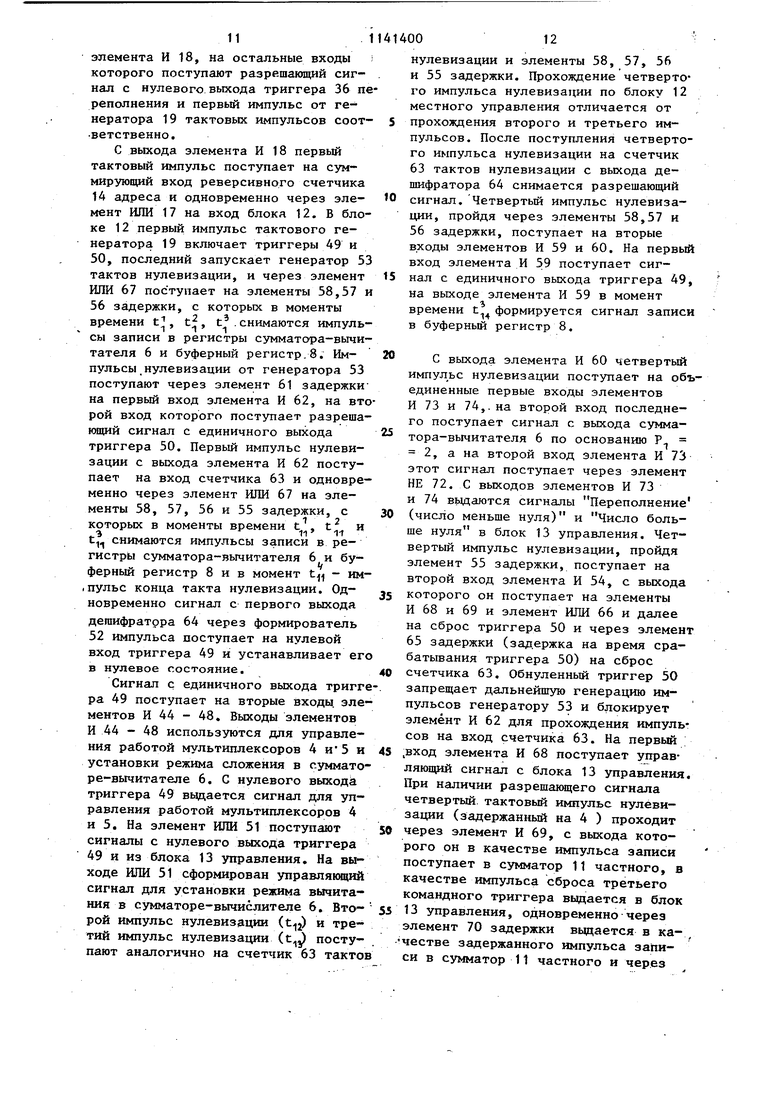

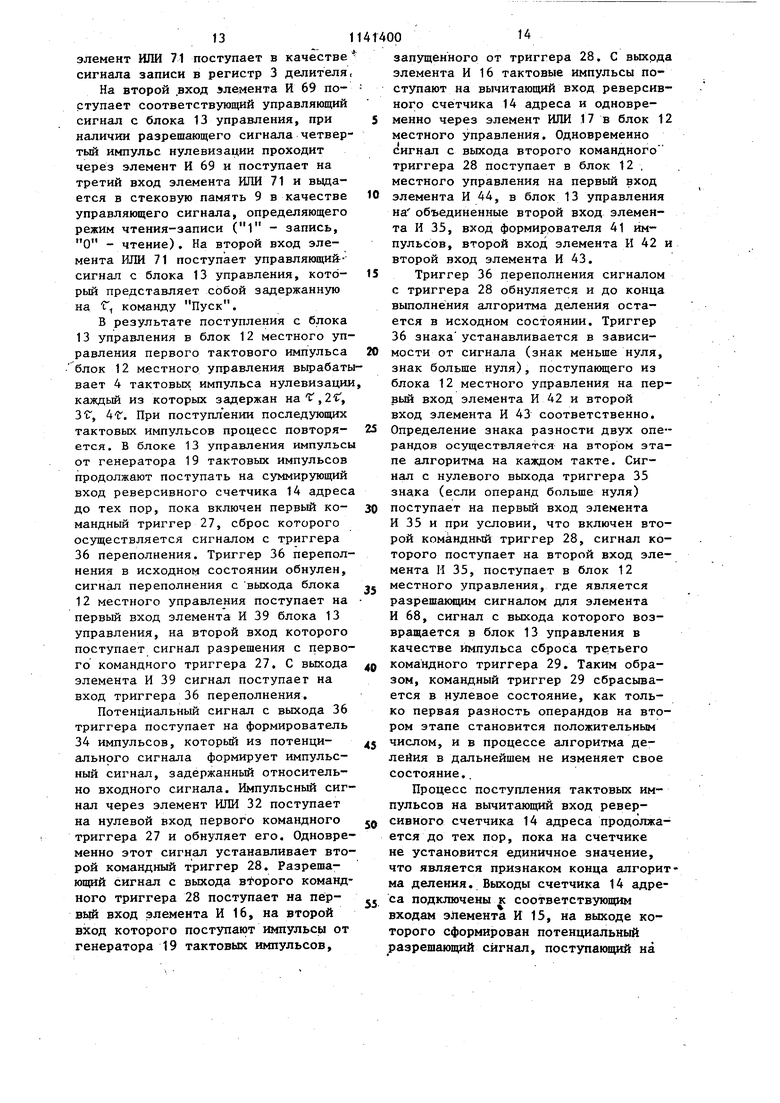

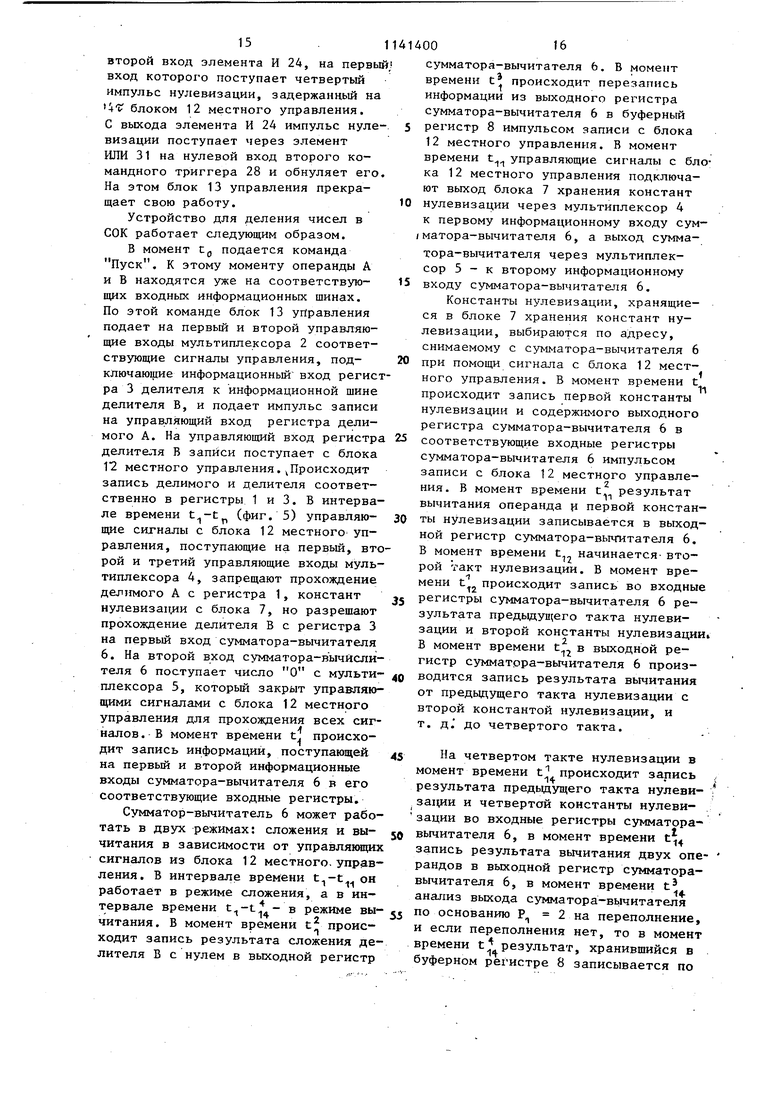

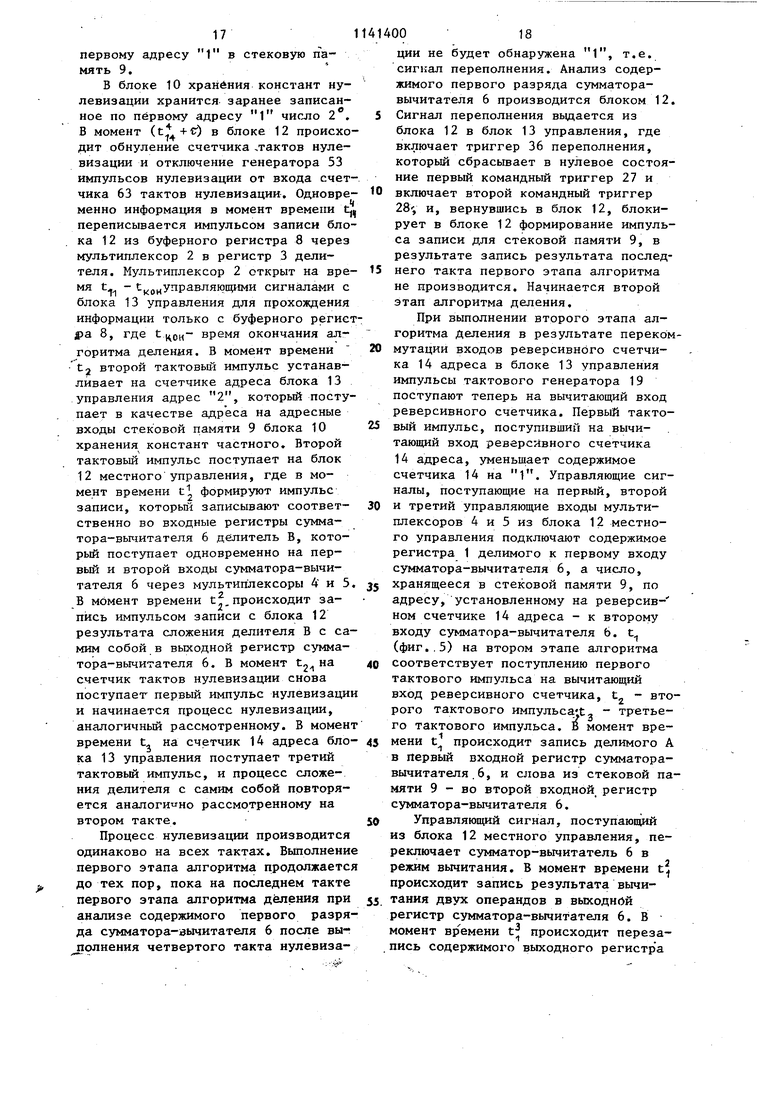

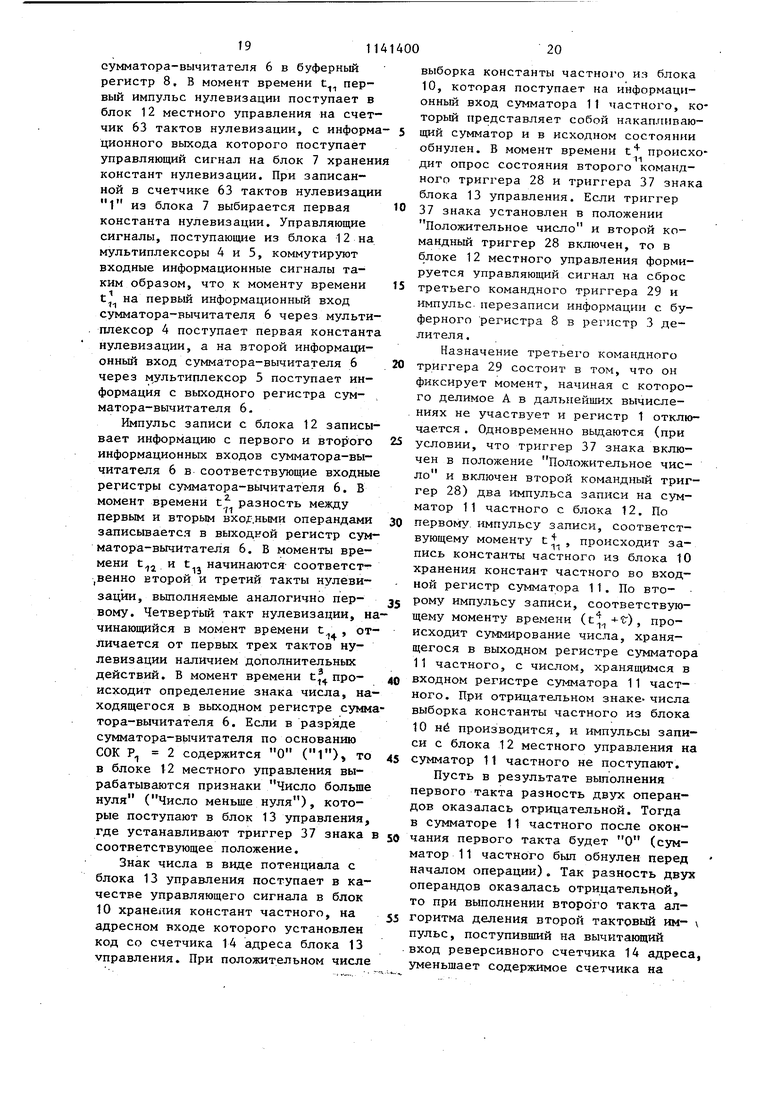

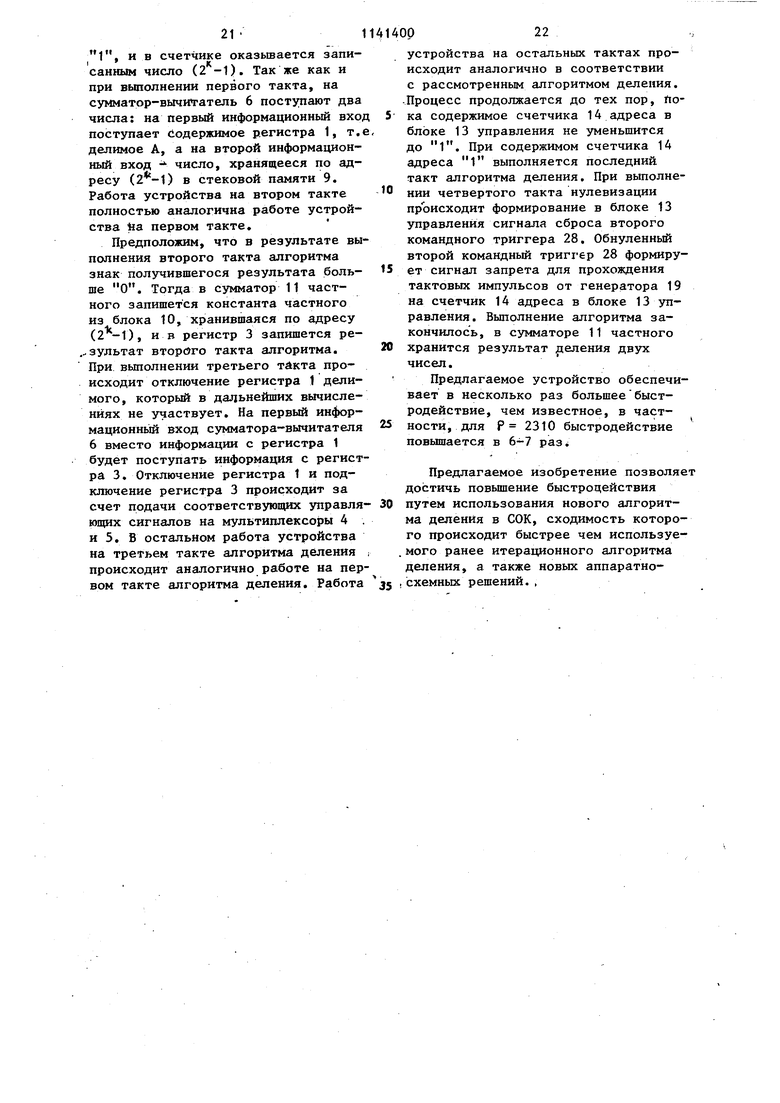

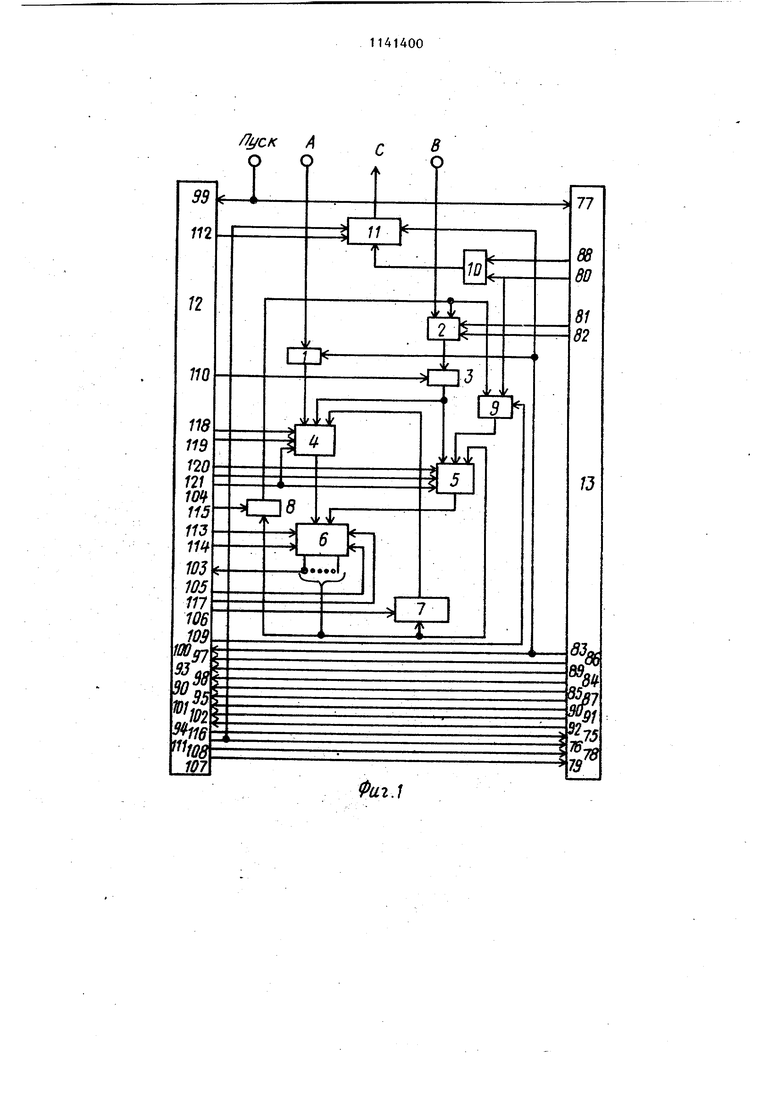

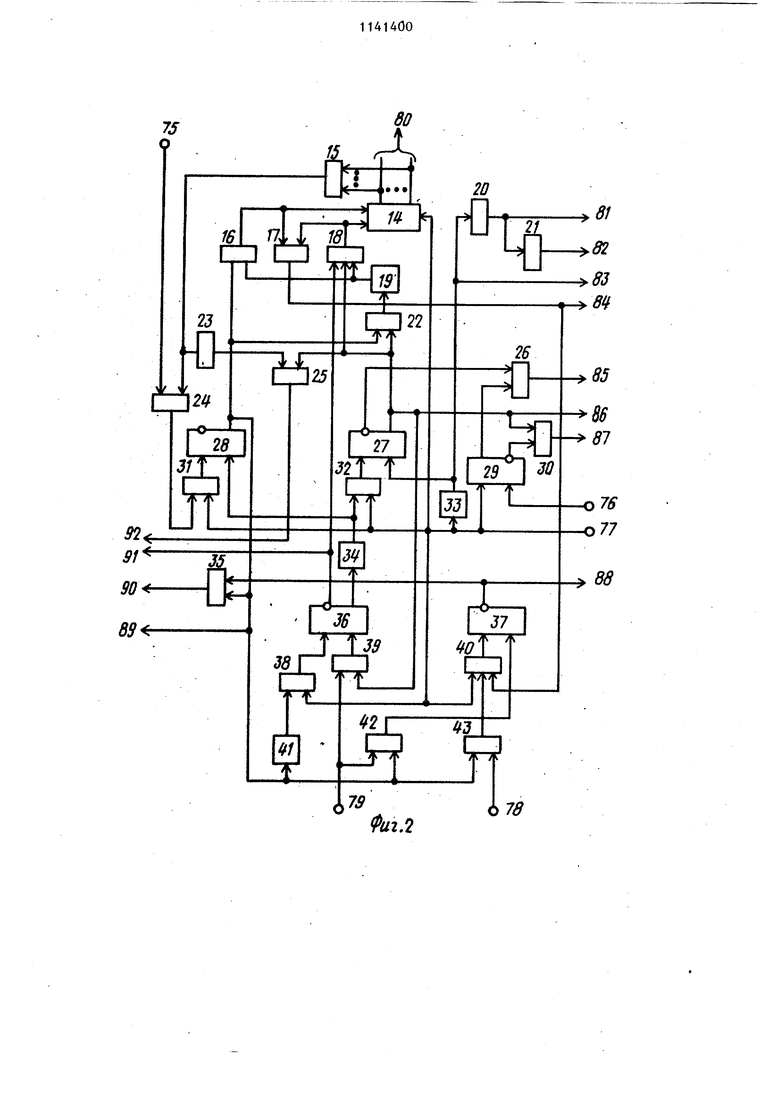

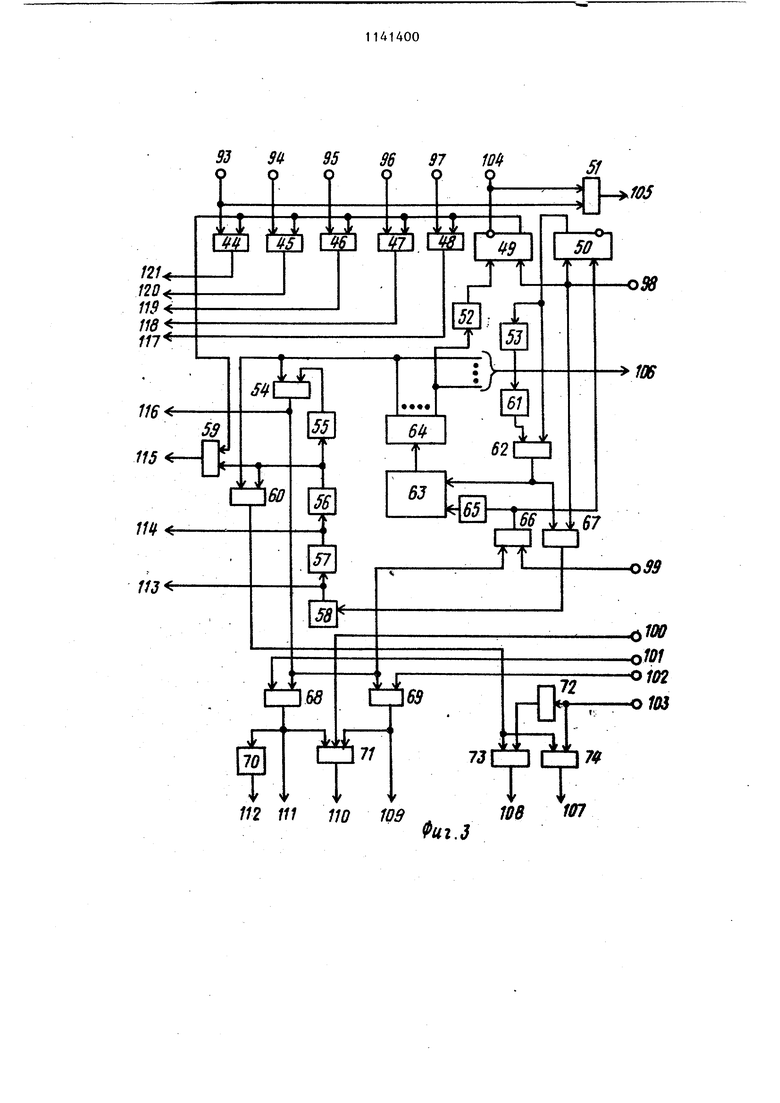

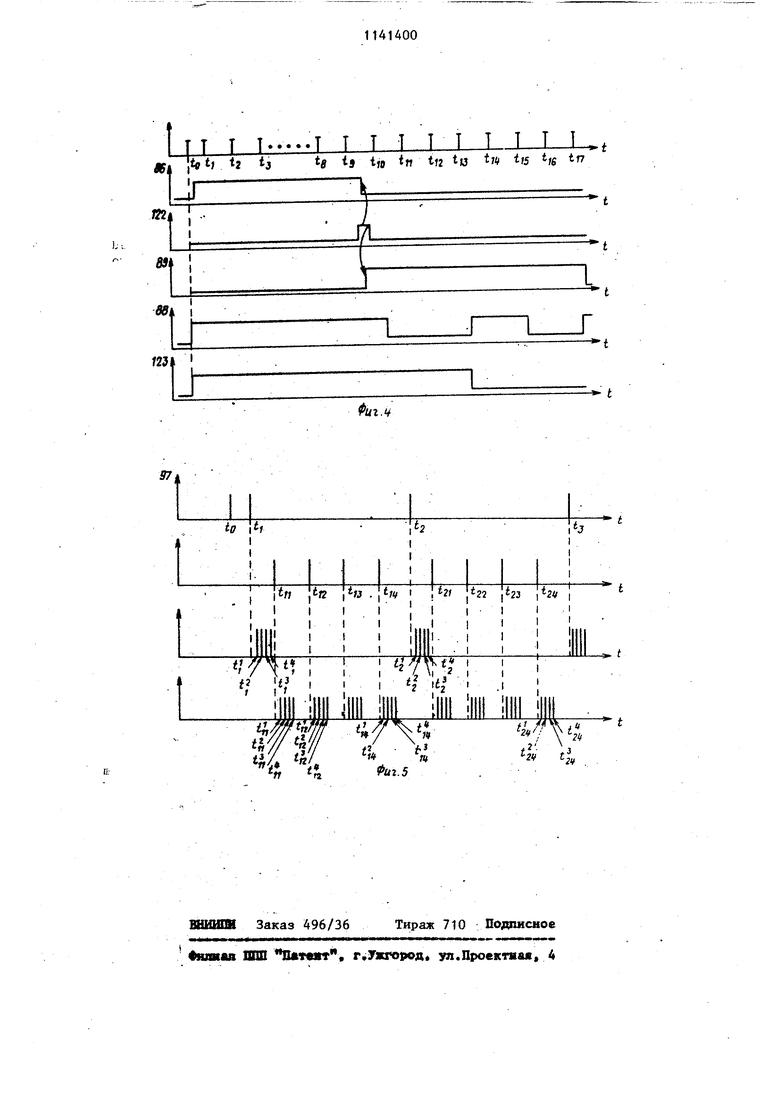

На фиг. 1 представлена структурная схема устройства для деления чисел в СОК; на фиг. 2 и 3 - функциональные схемы блока управления и блока местного управления соответственно; на фиг. 4 .и 5 - временные диаграммы блока управления и блока местного (Управления соответственно.

Устройство для деления чисел в СОК (фиг. 1) содержит регистр 1 делимого, первый мультиплексор 2, регистр 3 делителя, второй 4 и третий 5 мультиплексоры, сумматор-вычитатель 6 по основаниям Р- , блок 7. хранения констант нулевизации, буферный регистр 8, стековую память 9, блок 10 хранения констант частного, сумматор 11 частного, блок 12 местного управления и блок 13 управления .

Блок управления (фиг. 2) содержит реверсивный счетчик 14 адреса, первый 15 и второй 16 элементы И, первый элемент ИЛИ 17, третий элемент И. 18, генератор 19 тактовых импульсов, генератор 20 одиночного импульса, первый элемент НЕ 21, второй элемент ИЛИ 22, второй элемент НЕ 23 четвертый 24, пятый 25 и шес.той 26 элементы И, первый 27, второй 28 и третий 29 командные триггеры, третий 30, четвертый 31 и пятый 32 элементы ШШ, п&рвыА элемент задержки 33, первый формирователь 34 импульсов, седьмой элемент И 35, триггер 36 переполнения, триггер 37 знака, шестой элемент ШШ 38, восьмой элемент И 39 седьмой элемент ИЛИ 40, второй формирователь 41 импульсов, девятый 42 и десятый 43 элементы И.

Блок местного управления (фиг.З) содержит первый 44, второй 45, третий 46, четвертый 47 и пятый 48 элементы И, первый 49 и второй 50 триггеры, первый элемент ШШ 51, формиро ватель 52 импульсов, генератор 53 импульсов нулевизации, шестой элег мент И 54, первый 55, второй 56, третий 57 и четвертый 58 элементы задержки, седьмой 59 и восьмой 60 элементы И, пятый элемент 61 задержки, девятый элемент И 62, счетчик 63 тактов нулевизации, дешифратор 64

шестой элемент 65 задерябси, второй 66 и третий 67 элементы ИЛИ, десятый 68 и одиннадцатый 69 элементы И, седьмой элемент 70 задержки,четвертьй . элемент ШШ 71,элемент НЕ 72,двенадцатый 73 и тринадцатый 74 элементы И.

Блок 13 управления предназначен для формирования сигналов, управляН)рт1х работой всего устройства для деления в СОК.

Устройство также содержит входные и выходные шины 75-123.

Обозначения на фиг. 4 для случая А 125, В 5 и Р 23101

tp - момент времени поступления команды

t,t ,...,t - времена, соо тветствукидие поступлению импульсов тактового генератора 19 на суммирующий

вход реверсивного - счетчика 14;

Ч ,соответствукицие поступлению импульсов тактового генератора 19 на вычитающий вход реверсивного счетчика 14.

Блок 12 местного управления (фиг. 3) предназначен для определения переполнения рабочего диапазона Р/2, определения знака операнда и формирования управляющих сигналов ля блоков устройства.Определение переолнения рабочего диапазона и знака чиса осуществляется методом нулевизации. На фиг. 5 обозначено:

tjj - момент времени поступления команды

t,t2,tj - времена, соответствующие поступлению импульсов тактового генератора

I19 из блока 13 на

блок 12;

112 г 14 времена, соответствующие поступлению импульсов тактового генератора 53, запуа енного импульсом генератора 19, поступившим в момент времени t,,, на вход счетчика 63; 9 1 2 23Ч4 времена, соответствующие поступле нию импульсов так тового генератора 53, запущенного импульсом генерат ра 19, поступивши в момент времени t u. на вход счетч ка 63; t t t t времена, соответ - -ствующие задержан ному на времялг, Z-D; З-гг, 4f импуль су тактового генератора 19, поступившему в МОмент t время задержки; п к -4 Ц времена., соответствующие задержан ному на время Т, Zt, З-С, 4f импуль су тактового генератора 53, поступившему на вхо счетчика 63 в момент времени . Б основу работы положен следующи алгоритм. Пусть заданы делимое и делитель , представленные в системе остаточных классов по основаниям ( Г, ri) , где пличество оснований СОК, виде А (d, ,(2,.,.,с(.п); В (fi ,,..., An) . Алгоритм деления вьтолняется в два этапа. На первом этапе осуществляется фррмирование массива чисел вида 2 Б и массива чисел вида 2 констант частного, где к О,,.,, (Ео -2Р/2Б), а . обозначает округление до ближайшего меньшего положительного целого числа. На второ этапе осуществляется собственно де ление и формирование частного из констант частного. Первый этап состоит из (к + 2) тактов, второй - из (к + 1) такта. В i-M такте первого этапа производятся вычисления: в в,.,+ и, если IP, если , 00 если f- 0, то осуществляется переход к следующему (i+1)-My такту (i 1 - (к + 2) В результате выполнения первого этапа алгоритма сформированы массивы чисел и массив констант частного В (В,3,В,.,. В); К (2 Второй этап алгоритма деления выполняется следующим образом: в первом такте производятся вычие ления С, А - В если Ц,0; о, если С О, во втором такте производятся вычисления С, А г-1 0; с,-в., 1 1; 1, если С о 7/ О; 10, если С2 0, и т.д. . Процесс продолжается до тех пор, пока не будет выбран элемент В. Частное от деления А и Б равно у/2Чу,... + Г1,2. Блоки 12 и 13 работают .следующим образом. Работа блоков 12 и 13 начинается с момента tg подачи команды Пуск (фиг. 4). Б блоке 13 управления команда Пуск обнуляет все триггеры 27 28, 29, 36 и 37 и реверсивный счетчик 14 адреса, и задержанная на время 1 на элементе 33 задержки команда включает командныйтриггер 27, который через элемент ИЛИ 22 запусает генератор 19 тактовых импульсов, через выход вьщается в блок 12, в егистр 1 в качестве импульса запии, в сумматор 11 частично в качесте импульса сброса. Состояние командых триггеров блока 13 от момента одачи команды Пуск до момента наала первого такта алгоритма делений оказано на фиг. 4. В блоке 12 коанда Пуск производит обнуление четчика 63 тактов нулевизации и риггера 50. В блоке 13 разрешающий игнал с единичного выхода команд- }i ого триггера 27 поступает на вход элемента И 18, на остальные входы которого поступают разрешающий сигнал с нулевого выхода триггера 36 пе реполнения и первый импульс от генератора 19 тактовых импульсов соответственно. С выхода элемента И 18 первый тактовый импульс поступает на суммирующий вход реверсивного счетчика 14 адреса и одновременно через элемент ИЛИ 17 на вход блока 12. В блоке 12 первый импульс тактового генератора 19 включает триггеры 49 и 50, последний запускает генератор 53 тактов нулевизации, и через элемент ИЛИ 67 поступает на элементы 58,57 и 56 задержки, с которых в моменты времени t, t, t.снимаются импульсы записи в регистры сумматора-вычитателя 6 и буферный регистр.8. Импульсы нулевизации от генератора 53 поступают через элемент 61 задержки на первый вход элемента И 62, на вто рой вход которого поступает разрешающий сигнал с единичного выхода триггера 50, Первый импульс нулевизации с вькода элемента И 62 поступает на вход счетчика 63 и одновременно через элемент ШШ 67 на злементы 58, 57, 56 и 55 задержки, с которых в моменты времени , t снимаются импульсы записи в регистры сумматора-вычитателя 6 и буферный регистр 8 и в момент t - им,пульс конца такта нулевизации. Одновременно сигнал с первого выхода дешифратора 64 через формирователь 52 импульса поступает на нулевой вход триггера 49 и устанавливает ег в нулевое состояние. Сигнал с единичного выхода тригг ра 49 поступает на вторые входы, эле ментов И 44 - 48. Выходы элементов И 44 - 48 используются для управления работой мультиплексоров 4 и5 и установки режима сложения в сз ммато ре-вычитателе 6. С нулевого выход триггера 49 ввдается сигнал для управления работой мультиплексоров 4 и 5. На элемент ШШ 51 поступают сигналы с нулевого выхода триггера 49 и из блока 13 управления. На выходе ИЛИ 51 сформирован управляющий сигнал для установки режима вычитания в сумматоре-вычислителе 6, Вто- рой импульс нулевизации () и третий импульс нулевизации () поступают аналогично на счетчик 63 такто 1 012 нулевизации и элементы 58, 57, 56 и 55 задержки. Прохождение четвертого импульса нулевизации по блоку 12 местного управления отличается от прохождения второго и третьего импульсов. После поступления четвертого импульса нулевизации на счетчик 63 тактов нулевизации с выхода дешифратора 64 снимается разрешающий сигнал. Четвертый импульс нулевиза- ции, пройдя через элементы 58,57 и 56 задержки, поступает на вторые входы элементов И 59 и 60. На первый вход элемента И поступает сигнал с единичного выхода триггера 49, на выходе элемента И 59 в момент времени t формируется сигнал записи В буферный регистр 8. С выхода элемента И 60 четвертый импул ьс нулевизации поступает на объединенные первые входы элементов И 73 и 74,. на второй вход последнего поступает сигнал с выхода сумматора-вычитателя 6 по основанию Р 2, а на второй вход элемента И 73 этот сигнал поступает через элемент НЕ 72, С выходов элементов И 73 и 74 вьщаются сигналы Переполнение (число меньше нуля) и Число больше нуля в блок 13 управления. Четвертый импульс нулевизации, пройдя элемент 55 задержки, поступает на второй вход элемента И 54, с выхода которого он поступает на элементы И 68 и 69 и элемент ШШ 66 и далее на сброс триггера 50 и через элемент 65 задержки (зад.ержка на время срабатывания триггера 50) на сброс счетчика 63. Обнуленный триггер 50 запрещает дальнейшую генерацию импульсов генератору 53 и блокирует элемент И 62 для прохождения импульсов на вход счетчика 63. На первый ,вход элемента И 68 поступает управляющий сигнал с блока 13 управления. При наличии разрешающего сигнала четвертый тактовый импульс нулевизации (задержанный на 4 ) проходит через элемент И 69, с выхода которого он в качестве импульса записи поступает в сумматор 11 частного, в качестве импульса сброса третьего командного триггера вьщается в блок 13 управления, одновременно через элемент 70 задержки выдается в качестве задержанного импульса записи в сумматор 11 частного и через

элемент ИЛИ 71 поступает в качестве сигнала записи в регистр 3 делителя

На второй вход элемента И 69 поступает соответствующий управляющий сигнал с блока 13 управления, при наличии разрешающего сигнала четвертый импульс нулевизации проходит через элемент И 69 и поступает на третий вход элемента ИЛИ 71 и выдается в стековую память 9 в качестве управляющего сигнала, определяющего режим чтения-записи (1 - запись, О - чтение), На второй вход элемента ИЛИ 71 поступает управляю1ций сигнал с блока 13 управления, который представляет собой задержанную на Г команду Пуск.

В результате поступления с блока 13 управления в блок 12 местного управления первого тактового импульса блок 12 местного управления вырабатывает 4 тактовых импульса нулевизации каждый из которых задержан Haf.Zt, 3, 4f. При поступлении последующих тактовых импульсов процесс повторя- ется. В блоке 13 управления импульсы от генератора 19 тактовых импульсов продолжают поступать на суммирующий вход реверсивного счетчика 14 адреса до тех пор, пока включен первый командный триггер 27, сброс которого осуществляется сигналом с триггера 36 переполнения. Триггер 36 переполнения в исходном состоянии обнулен, сигнал переполнения с выхода блока 12 местного управления поступает на первый вход элемента И 39 блока 13 управления, на второй вход которого поступает сигнал разрешения с первого командного триггера 27. С выхода элемента И 39 сигнал поступает на вход триггера 36 переполнения.

Потенциальный сигнал с выхода 36 триггера поступает на формирователь 34 импульсов, который из потенциального сигнала формирует импульсный сигнал, задержанный относительно входного сигнала. Импульсный сигнал через элемент ИЛИ 32 поступает на нулевой вход первого командного триггера 27 и обнуляет его. Одновременно этот сигнал устанавливает второй командный триггер 28. Разрешающий сигнал с выхода второго командного триггера 28 поступает на пёрвый вход элемента И 16, на второй вход которого поступают импульсы от генератора 19 тактовых импульсов.

запущенного от триггера 28. С выхрд элемента И 16 тактовые импульсы поступают на вычитающий вход реверсивного счетчика 14 адреса и одновременно через элемент ИЛИ 17 в блок 1 местного управления. Одновременно сигнал с выхода второго командного триггера 28 поступает в блок 12 , местного управления на первый вход элемента И 44, в блок 13 управления на объединенные второй вход элемента И 35, вход формирователя 41 импульсов, второй вход элемента И 42 второй вход элемента И 43.

Триггер 36 переполнения сигналом с триггера 28 обнуляется и до конца вьшолнёния алгоритма деления остается в исходном состоянии. Триггер 36 знака устанавливается в зависимости от сигнала (знак меньше нуля, знак больше нуля), поступакнцего из блока 12 местного управления на первый вход элемента И 42 и второй вход элемента И 43 соответственно. Определение знака разности двух операндов осуществляется на втором этапе алгоритма на каждом такте. Сигнал с нулевого выхода триггера 35 знака (если операнд больше нуля) поступает на первый вход элемента И 35 и при условии, что включен второй ком 1ндный триггер 28, сигнал которого поступает на второй вход элемента И 35, поступает в блок 12 местного управления, где является разрешающим сигналом для элемента И 68, сигнал с выхода которого возвращается в блок 13 управления в качестве импульса сброса тре;тьего командного триггера 29. Таким образом, командный триггер 29 сбрасывается в нулевое состояние, как только первая разность операндов на втором этапе становится положительным числом, и в процессе алгоритма делейия в дальнейшем не изменяет свое состояние..

Процесс поступления тактовых импульсов на вычитающий вход реверсивного счетчика 14 адреса продолжается до тех пор, пока на счетчике не установится единичное значение, что является признаком конца алгоритма деления. Выходы счетчика 14 адреса подключены к соответствующим входам элемента И 15, на выходе которого сформирован потенциальный разрешающий сигнал, поступающий на 15 . 1 второй вход элемента И 24, на первый вход которого поступает четвертый импульс нулевизации, задержанный на W блоком 12 местного управления. С выхода элемента И 24 импульс нулевизации поступает через элемент ИЛИ 31 на нулевой вход второго командного триггера 28 и обнуляет его. На этом блок 13 управления прекращает свою работу. Устройство для деления чисел в СОК работает следующим образом. В момент tg подается команда Пуск. К этому моменту операнды А и В находятся уже на соответствующих входных информационных шинах. По этой команде блок 13 управления подает на первый и второй управляющие входы мультиплексора 2 соответствующие сигналы управления, подключающие информационный вход регист ра 3 делителя к информационной шине делителя В, и подает импульс записи на управляющий вход регистра делимого А. На управляющий вход регистра делителя В записи поступает с блока 12 местного управления.Происходит запись делимого и делителя соответственно в регистры 1 и 3. В интервале времени (фиг. 5) управляющие сигналы с блока 12 местного управления, поступающие на первый, вто рой и третий управляющие входы мультиплексора 4, запрещают прохождение де;1лмого А с регистра 1, констант нулевизап,ии с блока 7, но разрешают прохождение делителя В с регистра 3 на первый вход сумматора-вычитателя 6. На второй вход сумматора-вычйсли теля 6 поступает число О с мульти плексора 5, который закрыт управляю щими сигналами с блока 12 местного управления для прохождения всех сиг налов. В момент времени t. происходит запись информации, поступающей на первый и второй информационные входы сумматора-вычитателя 6 в его соответствующие входные регистры. Сумматор-вьгчитатель 6 может рабо тать в двух режимах: сложения и вычитания в зависимости от управляющи сигналов из блока 12 местного, управ ления. В интервале времени он работает в режиме сложения, а в интервале времени - в режиме вы читания. В момент времени t происходит запись результата сложения де лителя В с нулем в выходной регистр 0 6. В момент сумматора-вычитателя 3 информации из выходного регистра сумматора-вычитателя 6 в буферный регистр 8 импульсом записи с блока 12 местного управления. В момент времени t управляющие сигналы с блока 12 местного управления подключают выход блока 7 хранения констант нулевизации через мультиплексор 4 к первому информационному входу сумматора-вычитателя 6, а выход сумматора-вычитателя через мультиплексор 5 - к второму информационному входу сумматора-вычитателя 6. Константы нулевизации, хранящиеся в блоке 7 хранения констант ну- левизации, выбираются по адресу, снимаемому с сумматора-вычитателя 6 при помощи сигнала с блока 12 местного управления. В момент времени t происходит запись первой константы нулевизации и содержимого выходного регистра сумматора-вычитателя 6 в соответствующие входные регистры сумматора-вычитателя 6 импульсом записи с блока 12 местного управлеВИЯ. в момент времени t результат вычитания операнда н первой константы нулевизации записывается в выходной регистр сумматора-вьпштателя 6. В момент времени t начинается- второй такт нулевизации. В момент времени t происходит запись во входные регистры сумматора-вычитателя 6 результата предьщущего такта нулевизации и второй константы нулевизации. В момент времени t,, в выходной регистр сумматрра-вычитателя 6 производится запись результата вычитания от предыдущего такта нулевизации с второй константой нулевизации, и т. д. до четвертого такта. На четвертом такте нулевизации в момент времени t происходит запись результата предыдущего такта нулевизации и четвертой константы нулевизацин во входные регистры сумматоравычитателя 6, в момент времени t запись результата вычитания двух операндов в выходной регистр сумматоравычитателя 6, в момент времени t анализ выхода сумматора-вычитателя по основанию Р 2 на переполнение, и если переполнения нет, то в момент времени t результат, хранившийся в буферном регистре 8 записывается по

171

первому адресу 1 в стековую память 9.

В блоке 10 хранения констант нулевизации хранится- заранее записанное по первому адресу 1 число 2 . В момент () в блоке 12 происходит обнуление счетчика ,тактов нулевизации и отключение генератора 53 импульсов нулевизации от входа счетчика 63 тактов нулевизации. Одновременно информация в момент времени tj, переписывается импульсом записи блока 12 из буферного регистра 8 через мультиплексор 2 в регистр 3 делителя. Мультиплексор 2 открыт на время t - t д yпpaвляющими сигналами с блока 13 управления для прохождения информации только с буферного регист|)а 8, где ,H время окончания алгоритма деления. В момент времени

tj второй тактовый импульс устанавливает на счетчике адреса блока 13 управления адрес 2, который поступает в качестве адреса на адресные входы стековой памяти 9 блока 10 хранения констант частного. Второй тактовый импульс поступает на блок 12 местного управления, где в момент времени t формируют импульс записи, KOTopbrii записывают соответственно во входные регистры сумматора-вычитателя 6 делитель В, который поступает одновременно на первый и второй входы сумматора-вычи- тателя 6 через мультиплексоры 4 и 5. В момент времени t,происходит запись импульсом записи с блока 12 результата сложения делителя В с самим собой в выходной регистр сумматора-вычитателя 6. В момент tj на счетчик тактов нулевизации снова поступает первый импульс нулевизации и начинается процесс нулевизации, аналогичный рассмотренному. В момент времени ц на счетчик 14 адреса блока 13 управления поступает третий тактовый импульс, и процесс сложения делителя с самим собой повторяется аналогично рассмотренному на втором такте.

Процесс нулевизации производится одинаково на всех тактах. Выполнение первого этапа алгоритма продолжается до тех пор, пока на последнем такте первого этапа алгоритма деления при анализе содержимого первого разряда сумматора-вычитателя 6 после вы 1олнения четвертого такта нулевиза4140018

ции не будет обнаружена 1, т.е. сигнал переполнения. Анашиз содержимого первого разряда сумматоравычитателя 6 производится блоком 12. 5 Сигнал переполнения выдается из блока 12 в блок 13 управления, где включает триггер 36 переполнения, который сбрасьшает в нулевое состояние первый командный триггер 27 и 0 включает второй командный триггер 28, и, вернувшись в блок 12, блокирует в блоке 12 формирование импульса записи для стековой памяти 9, в результате запись результата последнего такта первого этапа алгоритма не производится. Начинается второй этап алгоритма деления. При выполнении второго этапа алгоритма Деления в результате переком20 мутации входов реверсивного счетчика 14 адреса в блоке 13 управления импульсы тактового генератора 19 поступают теперь на вычитающий вход реверсивного счетчика. Первый тактовый импульс, поступивший на вычитающий вход реверсивного счетчика 14 адреса, уменьшает содержимое счетчика 14 на 1. Управляющие сигналы, поступающие на первый, второй

30 и третий управляющие входы мультиплексоров 4 и 5 из блока 12 местного управления подключают содержимое регистра 1 делимого к первому входу сумматора-вычитателя 6, а число,

J5 хранящееся в стековой памяти 9, по адресу, установленному на реверсивном счетчике 14 адреса - к второму входу сумматора-вычитателя 6. t (фиг..5) на втором этапе алгоритма

40 соответствует поступлению первого тактового импульса на вычитающий вход реверсивного счетчика, t - второго тактового импyльcat, - третьего тактового импульса. В момент времени t происходит запись делимого А в первый входной регистр сумматоравычитателя . 6 , и слова из стековой памяти 9 - во второй входной регистр сумматора-вычитателя 6.

50 Управляющий сигнал, поступающий из блока 12 местного управления, переключает сумматор-вычитатель 6 в режим вычитания. В момент времени t происходит запись результата вычи55. тания двух операндов в выходной регистр сумматора-вычитателя 6. В момент времени t происходит перезапись содержимого выходного регистра сумматора-вычитателя 6 в буферный регистр 8, В момент времени t первый импульс нулевизации поступает в блок 12 местного управления на счетчик 63 тактов нулевизации, с информа ционного выхода которого поступает управляющий сигнал на блок 7 хранени констант нулевизации. При записанной в счетчике 63 тактов нулевизации 1 из блока 7 выбирается первая константа нулевизации. Управляющие сигналы, поступающие из блока 12 на мультиплексоры 4 и 5, коммутируют входные информационные сигналы таким образом, что к моменту времени t на первый информационный вход сумматора-вычитателя 6 через мульти плексор 4 поступает первая констант нулевизации, а на второй информациoHHbrii вход сумматора-вычитателя 6 через мультиплексор 5 поступает информация с выходного регистра сумматора-вычитателя 6. Импульс записи с блока 12 записы вает информацию с первого и второго информационных входов сумматора-вычитателя 6 в соответствующие входны регистры сумматора-вычитателя 6. В момент времени t разность между первым и вторым входными операндами записывается в выходной регистр сум матора-вычитателя 6. В моменты времени и t , начинаются- соответст- ,венно второй и третий такты нулевизации, вьшолняемые аналогично первому. Четвертый такт нулевизации, н чинающийся в момент времени t , от личается от первых трех тактов нулевизации наличием дополнительных действий. В момент времени t происходит определение знака числа, на ходящегося в выходном регистре сумм тора-вычитателя 6. Если в разряде сумматора-вычитателя по основанию СОК РТ 2 содержится О (1), то в блоке 12 местного управления вырабатывсштся признаки Число больше нуля (Число меньше нуля), которые поступают в блок 13 управления, где устанавливают триггер 37 знака соответствующее положение. Знак числа в виде потенциала с блока 13 управления поступает в качестве управляющего сигнала в блок 10 хранения констант частного, на адресном входе которого установлен код со счетчика 14 адреса блока 13 управления. При положительном числе выборка константы частного из блока 10, которая поступает на информационный вход сумматора 11 частного, который представляет собой накап-пивающий сумматор и в исходном состоянии обнулен. В момент времени t происходит опрос состояния второго командного триггера 28 и триггера 37 знака блока 13 управления. Если триггер 37 знака установлен в положении Положительное число и второй командный триггер 28 включен, то в блоке 12 местного управления формируется управляющий сигнал на сброс третьего командного триггера 29 и импульс, перезаписи инфop faции с. буферного регистра 8 в регистр 3 делителя. Назначение третьего командного триггера 29 состоит в том, что он фиксирует момент, начиная с которого делимое А в дальнейших вычислениях не участвует и регистр 1 отключается . Одновременно выдаются (при условии, что триггер 37 знака включен в положение Положительное число и включен второй командный триггер 28) два импульса записи на сумматор 11 частного с блока 12. По первому импульсу записи, соответствующему моменту t j , происходит запись константы частного из блока 10 хранения констант частного во входной регистр сумматора 11. По вто- рому импульсу записи, соответствующему моменту времени (), происходит суммирование числа, хранящегося в выходном регистре с мматора 11 частного, с числом, хранящимся в входном регистре сумматора 11 частного. При отрицательном знаке- числа выборка константы частного из блока 10 не производится, и импульсы записи с блока 12 местного управления на сумматор 11 частного не поступают. Пусть в результате вьтолнения первого такта разность двух операндов оказалась отрицательной. Тогда В сумматоре 11 частного после окон- чания первого такта будет О (сумматор 11 частного бьш обнулен перед началом операции). Так разность двух операндов оказалась отрицательной, то при выполнении второго такта алгоритма деления второй тактовый им- v пульс, поступивший на вычитающий вход реверсивного счетчика 14 адреса, уменьшает содержимое счетчика на 21 1, и в счетчике оказьшается записанным число (). Так же как и при выполнении первого такта, на сумматор-вычиЧатель 6 поступают два числа: на первый информационный вхо поступает содержимое регистра 1, т. делимое А, а на второй информахцюнный вход - число, хранящееся по адресу () в стековой памяти 9. Работа устройства на втором такте полностью аналогична работе устройства йа первом такте. Предположим, что в результате вы полнения второго такта алгоритма знак получившегося результата больше О. Тогда в сумматор 11 частного запишется константа частного из блока 10, хранившаяся по адресу (2-1), ив регистр 3 запишется ре-зультат второго такта алгоритма. При выполнении третьего такта происходит отключение регистра 1 делимого, который в дал1ьнейших вычислениях не участвует. На первый информационный вход сумматора-вычитателя 6 вместо информации с регистра 1 будет поступать информация с регист ра 3. Отключение регистра 1 и подключение регистра 3 происходит за счет подачи соответствующих управля ющих сигналов на мультиплексоры 4 и 5. В остальном работа устройства на третьем такте алгоритма деления происходит аналогично работе на пер вом такте алгоритма деления. Работа 0 устройства на остальных тактах происходит аналогично в соответствии с рассмотренным алгоритмом деления. Процесс продолжается до тех пор, Пока содержимое счетчика 14 адреса в блоке 13 управления не уменьшится до 1. При содержимом счетчика 14 адреса 1 выполняется последний такт алгоритма деления. При выполнении четвертого такта нулевизации происходит формирование в блоке 13 управления сигнала сброса второго командного триггера 28. Обнуленный второй командный триггер 28 формирует сигнал запрета для прохождения тактовых импульсов от генератора 19 на счетчик 14 адреса в блоке 13 управления. Выполнение алгоритма закончилось, в сумматоре 11 частного хранится результат f eлeния двух чисел. Предлагаемое устройство обеспечивает в несколько раз большеебыстродействие, чем известное, в частности, для Р 2310 быстродействие повышается в 6-7 раз Предлагаемое изобретение позволяет достичь повьш1ение быстродействия путем использования нового алгоритма деления в СОК, сходимость которого происходит быстрее чем используеого ранее итерационного алгоритма еления, а также новых аппаратносхемных решений.,

Фаг.1

Фаг.Ч

93 9D- 95 96 97 10 О ООо оо

5f

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для цифрового преобразования координат | 1982 |

|

SU1019445A1 |

| Устройство для деления | 1984 |

|

SU1259251A1 |

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ ТЕЛЕВИЗИОННОГО ИЗОБРАЖЕНИЯ С ИЗМЕНЕНИЕМ МАСШТАБА УПРАВЛЯЕМОГО ФРАГМЕНТА | 1993 |

|

RU2065206C1 |

| Процессор быстрого преобразования Фурье | 1988 |

|

SU1667101A1 |

| ЦИФРОВОЕ ПРОГНОЗИРУЮЩЕЕ УСТРОЙСТВО | 2011 |

|

RU2446454C1 |

| Устройство для сложения чисел в модулярной системе счисления | 1986 |

|

SU1322278A1 |

| Параллельно-последовательный аналого-цифровой преобразователь | 1985 |

|

SU1305851A1 |

| АДАПТИВНОЕ ЦИФРОВОЕ ПРОГНОЗИРУЮЩЕЕ И ДИФФЕРЕНЦИРУЮЩЕЕ УСТРОЙСТВО | 2011 |

|

RU2475831C1 |

| Устройство для воспроизведения аналогового сигнала | 1988 |

|

SU1524175A1 |

| Устройство для распаковки команд | 1990 |

|

SU1702367A1 |

УСТРОЙСТВО ДЛЯ ДЕЛЕНИЯ В СИСТЕМЕ ОСТАТОЧНЫХ КЛАССОВ, содержащее регистр делимого, регистр делителя, сумматор-вычитатель по основаниям P,-(i 1, . .., г, где п - количество оснований), сумматор частного, причем вход регистра делимого и выход сумматора частного являются соответственно входом делимого и выходом частного устройства, отличающееся тем, что, с целью повышения быстродействия, .оно срдержит первый, второй и тр.етий мультиплексоры, буферный регистр, блок хранения констант нулевизации, блок хранения констант частного, стековую память, блок управления, содержащий реверсивный счетчик адреса, генератор тактовых импульсов, генератор одиночного импульса, первый, второй элементы НЕ, первый, второй, третий четвертый, пятый, шестой, седьмой, восьмой, девятый, десятый элементы И, первый, второй, третий, четвертый, пятый, шестой, седьмой элементы ИЛИ, первь1й, второй, третий командные триггеры, триггеры переполнения и знака, элемент задержки, первый, второй формирователи импульсов, причем выходы группы реверсивного счетчика адреса подключены к соответствующим входам первого элемента И, выход генератора тактовых импульсов подключен к первым входам второго и третьего элементов И, выходы которых подключены соответственно к входам вычитания и сложения реверсивного счетчика адреса и к первому и второму входам первого элемента ИЛИ, вход генератора тактовых импульсов подключен к выходу второго элемента ИЛИ, первый вход которого соединен с (Л вторым входом второго элемента И, второй вход второго элемента ИЛИ соединен с единичным выходом первого командного триггера, с первым входом третьего элемента ИЛИ и с вторым входом третьего элемента И, третий вход которого соединен с нулевым 4iii S выходом триггера переполнения, выход перв.ого элемента И соединен с первым входом четвертого элемента И, выход которого соединен с первым входом четвертого элемента ИЛИ, выход которого соединен с нулевым входом второго командного триггера, единичный вход которого соединен с первым входом пятого элемента ИЛИ и выходом первого формирователя импульсов, вход которого соединен с единичным выходом триггера переполнения, нулевой вход которого соединен с выходом шестого элемента ИЛИ, первый вход которого соединен через второй формирователь импульсов с еди

112 111 по 109 W8 IffJ

Фиг.З

.T Т Т Т Т I Т Т Т 1 ,,

I Ь 4 t tn tfz to t74i tf5 t,g tT7

tj tj

8H

i.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для регистрации информации | 1976 |

|

SU656080A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для деления | 1975 |

|

SU579614A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-02-23—Публикация

1983-07-29—Подача