(54) УСТРОЙСТВО ДЛЯ ЦИФРОВОГО ФУНКЦИОНАЛЬНОГО

1

Изобретение относится к авток{атике и вычислительной технике и может быт использовано о составе гибридных вь числительных систем, а также для выполнения функциональных преобразований в измери1:ельной технике.

Известно устройство для аппроксимации функций, содержащее реверсивный счетчик, управляемый делитель частоты, блок вычитания кодов, блок деления и регистры узловых значений ординат и текущего интервала Cl 3

Недостатком устройства является невозможность осуществления операции функционального преобразования.

Наиболее близким к предлагаемо является устройства для функциональн« го преобразования цифровых сигналов, . содержащее реверсивный счетчик, выходы которого являются выходами устройства, и регистр, соединенный информационными Входами и с шиной ввода аргумента а вытсодамв с входами дешифратора, под ключ енно1Ю выходами через блок ПРЕОБРАЗОВАНИЯ

памяти к первой группе входов блока вычитания кодов, выход обнуления которого соединен с первым входом элемента И, .подключенного вторым входом к выходу генератора импульсов, а выходом к сигнальному входу управляемого делит© ля частоты, блок вычитания кодов второй грутшой входов соединен с выходами р версиБного счетчика, выходами кода ности с управлшощими входами управляв мого делителя частоты выходом заака разности с входом управления реверсом реверсивного счетчика, а выходом обнуления с управляющим входом регистра

,5 и с входом стробир жаниа управляемого делителя частоты, подк1воченного выходом к счетному входу реверсивного счет чика С2 3 .

Недостатком известного устройства

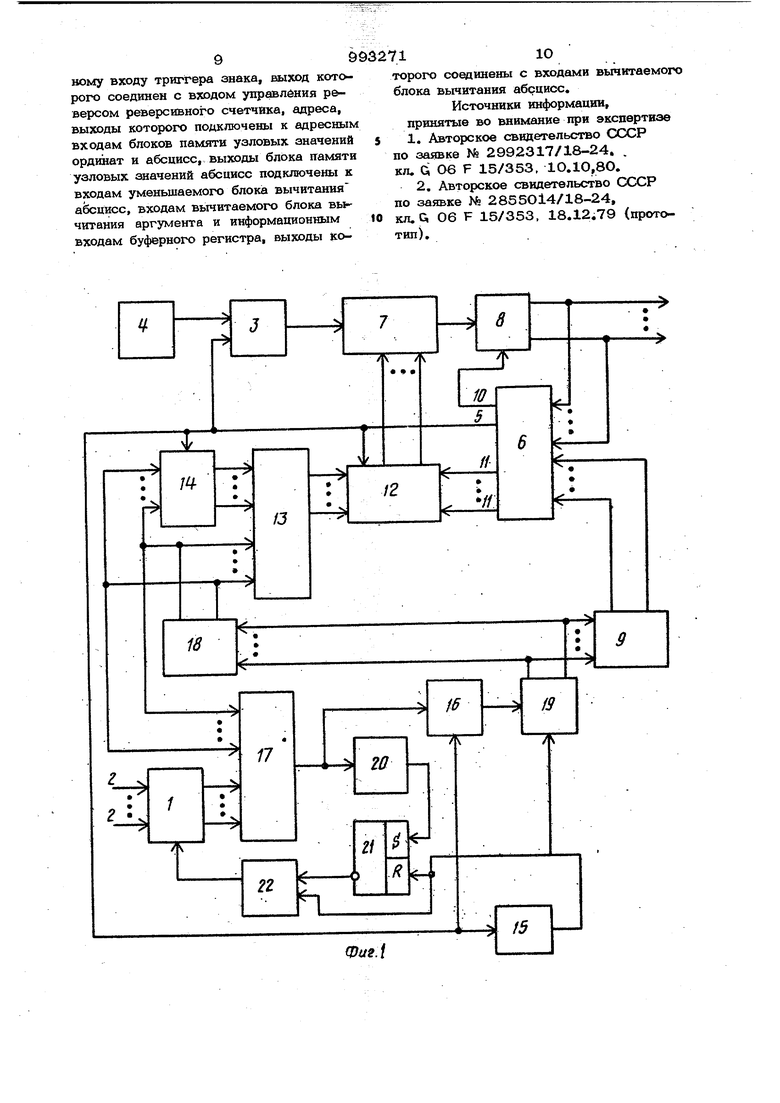

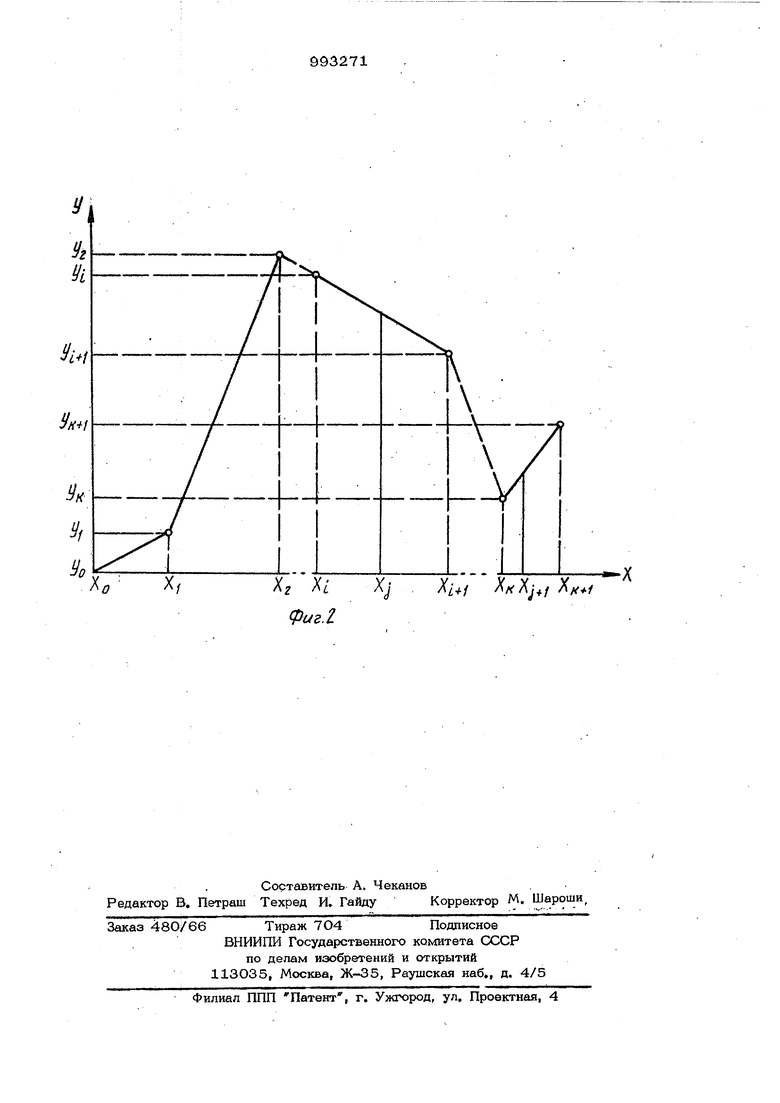

20 5т.ляется пониженная точность функционального преобразования, обусловленная .равномерным расположением узлов аппроксимаци-и на интервале представления функции.. Цель изобретения - повышение точности функционального преобразования путем произвольного задания интервалов аппроксимации. При этом в зависимости от фивида фунюдии можеп быть достигнуто сокращение необходимого числа интервалов аппроксимации, что приводит к умень шению времени воспроизведения функции. Поставленная цель достигается тем, что в устройство для цифрового функционального преобразования, содержащее регистр аргумента, генератор импульсов, первый элемент И, блок вычитания ординат, управляемый делитель частоты, реверсивный счетчик результатов и блок памя1И узловых значений ординат, причем информационные входы регистра аргумента соединены с входами устройства первый вход первого элемента И соединен с выходом генератора импульсов, а второй вход - с выходом обнуления блока вычитания ординат, выход первого элемента И соединен с сигнальным входом управляемого делителя частоты, выход которого соединен со счетным вхо- дом реверсивного счетчика результата, выходы которого соединены с выходами устройства и входами вычитаемого блока вычитания ординат, выход знака разности которого соединен с входом управления реверсом реверсивного счетчика результата, выходы блока памяти узловых значений ординат подключены к входам уменьшаемого блока вычитания ординат, введены блок вычитания абсцисс блок вычитания аргумента, реверсивный счетчик адреса, элементзадержки, формирователь импульсов, триггер разрешен приема аргумента, второй элемент И. тр триггер знака, блок памяти узловых значений абсцисс, буферный регистр и блок деления, причем выходы кода разности блока вычитания ординат соединены с входами делимого блока деления, выходы которого соединены с управляющими вхо дами управляемого делителя частоты, входы кода делителя блока деления подключены к выходам блока вычитания абсцисс, выход обнуления блока вычитания ординат соединен с входами синхронизе - ции блока деления, буферного регистра, и триггера знака, а также с вторым входом первого элемента И, и через эле мент задержки со счетным входом ревер сивного счетчика адреса, первым входом второго элемента И и входом установки в ноль триггера разрешения приема аргумента, вход установки в единицу котог рого соединен с выходом формирователя импульсов, а инверсный выход соединен с вторым входом второго элемента И, выход которого подключен к входу синхронизации регистра аргумента, выходь. которого соединены с входами уменьшаемого блока вычитания аргумента, выход кода знака которого подключен к ходу форм1ирователя импульсов и информационному входу триггера знака, выход которого соединен с входом управления реверсом реверсивного счетчика адреса, выходы которого подключены к адресным входам блоков памяти узловых значений ординат и абсцисс, выходы блока памяти узловых значений абсцисс подключены к входам уменьшаемого блока вычитания абсцисс, входам вычитаемого блока вычитаемого аргумента и информационным входам буферного регистра, выходы которого соединены с входами вычитаемого блока вычитания абсцисс. На фиг. 1 представлена блок-схема устройства для цифрового функционального преобразования} на фиг. 2 - несколько участков функции с произвольным заданием интервалов аппроксимации Устройство содержит регистр 1 аргумента, щину 2 ввода аргумента. Первый элемент И 3 генератор 4 импульсов, выход 5 обнуления блока 6 вычитания ординат, управляемый делитель 7 частоты, реверсивный счетчик 8 результата, блок 9 памяти узловых значений ординат, выходы 1О знака разности, блока 6, выходы 11 кода разности блока 6, блок 12 деления, блок 13 вычитания абсцисс, буферный регистр 14, элемент 15 задержки, триггер 16 знака, блок ; 17 вычитания аргумента, блок 18 памяти узловых значений абсцисс, реверсивный счетчик 19 адреса, формирователь 20 .импульсов, триггер 21 разрешения приема аргумента, второй элеме гг И 22, Устройство работает следующим образом. В блок 9 памяти узловых значений ординат заносятся ординаты узловых точек функции преобразования /j(.ji . В блок 18 памяти узловых значений абсцксс заносятся абсциссы узловых точек функции преобразования, причем в первую ячейку блоков 9 и 18 памяти заносится нулевой код. По выходному коду реве1 сивного счетчика 19, разрядность которого определяется количеством узловых точек, хранимых в блоках 9 и 18 памяти, находятся коды ординаты и абсциссы соответствующего значения функции преобразования. Блоки 6 и 13 вычитания определяют разность между поступившим и предыдущим значениями ординат и абсцисс соответственно. С помощью блока 12 деления и управляемого делителя 7 частоты с.втоматичёски устанавливается коэффициент наклона интерполирующих отрезков, причем коэффициент передачи делителя 7 частоты на каждом интервале аппроксимации пропорционален отношению предьщушее и поступивгде . шее значения ординат; - предыдущее и поступившее из блока 18 памян ти значения абсцисс. В исходном состоянии реверсивные счетчики 8 и 19, регистр 1 аргумента, буферный регистр 14, триггер 16 знака и триггер 21 установлены в нуль. Таким образом, по нулевому кеду счетчика 19 из первых йгчаек блоков 9 и Г 18 памяти извлекаются нулевые коды и на выходе 5 обнуления блока 6 вычитания ординат формируется передний фронт сигнала сравнения. Сигнал сравнения с выхода 5 обнуления блока 6 поступает на второй вход элемента И 3, закрывая его на время установки коэффициента деления делителя 7 частоты, н управляющий вход буферного регистра 1 разрешая прием кода абсцисс из блока 18 памятиj на вход синхронизации блок 12 деления, разрешая вычисление новог коэффициента передачи делителя 7 частоты, на вход синхронизации триггера 16 знака, разрешая передачу знака, управляющего реверсом счетчика 19, и на вход элемента 15 задержки, задерживаю щего передний фронт сигнала сравнения на время, необходимое для перезаписи кода абсциссы с блока 18 памяти и буферный регистр 14. По задержанному переднему фронту сигнала сравнения с выхода элемента 15 задержки открывается элемент И 22 разрешая приём кода первого аргумента Х; , И переводит счетчик 19 в следующее состоящие, В блоке 17 вычитания кодов формируется знак разности кодов аргумента Xj и абсциссы Хд с выхода блока 18 памяти. По коду счетчика 19 из блоков 9 и 18 памяти извлекаются коды ординаты -ц. и абсциссы х первог участка аппроксимации. При этом блоком 6 вычисляется разность кодов -j jj между значением блока 9 и счетчиком 8, а блоком 13 - разность кодов между значением, блока 18 памяти и буферного регистра 14. Блок деления вычисляет код X -Хо управляющий коэффициентом передачи делителя 7 частоты на первом участке аппроксимации. После поступления на вторую группу входов блока 6 кода ординат первого участка аппроксимации v на выходе 5 блока вырабатывается задний фронт сигнала сравнения, задержанный на время, необходимое для установки коэффициента передачи в делителе 7 частоты. По заднему фронту сигнала сравнения открывается элемент И 3 и импульсы с выхода генератора 4 импульсов поступают на счетный вход реверсивного счетчика 8. По задержанному элементом 15 задержки заднему 4Ч5Онту сигнала сравнения триггер 21 переводится в еди- ничное состояние, закрывая элемент И 22 и запрещая прием очередного аргумента до момента отработки поступившего аргумента х . Таким образом происходит ступенчато-линейная интерполяция функции на первом интервале ахшроксимации, причем частота импульсов с выхода генератора 4, поступающая на счетчик 8, определяется коэффициентом деления делителя 7 частоты. При совпадении кода счетчика 8 и ко-, да - на выходе 5 обнуления блока 6 формируется очередной импульсный сигнал, по переднему фронту которого Ьлемент И 3 закрывается, в буферный регистр 14 записывается код х абсциссы из блока 18 памяти. По э ержанному элементом 15 задержки переднему фроату сигнала сравнения счетчик 19 переходит в следующее состояние и из блоков 9 к 18 памяти извлекаются коды ординаты 2 и абсциссы Xg второго участка аппроксимации. Блок 12 деления вычисляет новый код, управляющий коэ(| фициентом передачи делителя 7 частоты, и начинается ступенчато-линейная интерполяция второго участка аппроксимации. При достижении счетчиком 8 кода у. на выходе обнуления блока 6 формирует ся передний .фронт сигнала сравнения, по которому элемент И 3 закрывается и код X . с выхода блока 18 памяти переписьюается в буферный регисгтр 14. По задержанному элементом 15 задержки переднему фронту сигнала сравнения счетчик 19 переводится в следующее состояние и из блоков 9 н 18 памяти извлекаются коды . и Х ординаты и абсциссы. Блок 12 деления вычисляет код, управляющий коэффициентокв передачи делителя 7 частоты на данном участ ке аппроксимации. При этом на выходе знака разности блока 17 вычитания а{ гумента изменяется знак, в результате чего срабатывает формирователь 2О ик пульсов, и устанавливает триггер 21 в нулевое состояние. Таким образом, по совпадению единичных кодов на входах элемент И 22. открьюается и разрешает прием очередного значения аргумента j+l в регистр 1. По заднему фронту сигнала сравнения открывается элемент И-З, и импульсы с выхода генератора 4 поступают на счетный вход счетчика 8. Задержанный элементом 15 задержки задний фронт сигнала сравнения переводит триггер 21 в . единичное состояние и закрывает элемент И 22, На выходе блока 17 вычитшгая ,})Ормируется знак разности -Х .По достижении счетчиком 8 кода : на выходе 5 блока 6 появляется очередной импульсный сигнал, по переднему фронту которого в триггер 16 знака записьтается знак разности кодов + , подготавл1тая 19 к работе на следующих участках аппроксимации. Таким образом, происходит ступенчато-линейная интерполяция функций в зависимости от кода поступив шего аргумента. На последующих участках аппроксима ции устройство работает аналогично. Вы ходной код счетчика при необходимости может быть преобразован в аналоговый сигнал, цифро-аналоговым преобразовате лем. При изменении знака крутизны фун ции в узловых точках разность кодов . изменяет знак и признак знака крутизны с выхода 1О блока 6 управляет реверсом счетчика 8, Таким образом, в предлагаемом уст ройстве по сравнению с известным повы шается точность функционального преобразования за счет произвольного задания интервалов аппроксимации, а также уменьшается время воспроизведения ряда функций вследствие минимизации необходимого коли 1ества участков аппроксимации. Ф о р мула изобретения 1. Устройство для цифрового функционального преобразования, содержащее регистр аргумента, генератор импyльcoв первый элемент И, блок вычитания ординат, управляемый делитель частоты, реверсивный счетчик результата и блок памяти узловых значений ординат, причем информационные входы регистра аргумента соединены с входами устройства, первый вход первого элемента И соединен с выходом генератора импульсов, а второй-ВХОД - с выходом обнуления блока вычитания ординат, выход первого элемента И соединен с сигнальным вхо- . дом управляемого делителя частоты, выход которого соединен со счетным входом реверсивного счетчика результата, выходы которого соединены с выходами устройства и входами вычитаеКюго блока выч№тания ординат, выход знака разности которого соединен с входом управления реверсом реверсивного- счетчика результата, выходы блока памяти узловых значений ординат подключены к входам уменьшаемого блока вычитания ордиНат, отличающееся тем, что, с целью повышения точности фушщионального преобразования, в него дополнительно введены блок вычитания абсцисс, блок вычитания аргу тента, реверсивный счетчик адреса, элемент задержки, формирователь импульсов, триггер разрешения приема аргументов, второй элемент И, триггер знака, блок памяти узловых значений алсцисс, буферный регистр и блок деления, причем выходы кода разности блока вычитания ординат соединены с в входами делимого блока деления, выходы которого соединены с управляющими входами управляемого делителя частоты, входы кода делителя блока деления подключены к выходам блока вычитания аб сцисс, выход обнуления блока вычитания ординат соединен с входами синхронизации блока деления, буферного регистра и триггера знака, а также с вторым входом первого элемента И и через элемент задержки со счетным входом реверсивного счетчика адреса, первым входом второго элемента И и входом установки в ноль триггера разрешения приема аргумента, вход установки в единицу которого подключен к выходу формирователя импульсов, а инверсный вход соединен с вторым входом второго элемента И, выход которого подключен к входу синхронизации регистра аргумента, выходы которого соединены с входами уменьшав мого блока вычитания аргумента, выход кода знака которого подключен к входу формирователя импульсов и информационному входу триггера знака, выход которого соединен с входом управления реверсом реверсивного счетчика, адреса, выходы которого подключены к адресным входам блоков памяти узловых значений ордгашт и абсцисс, выходы блока памяти узловых значений абсцисс подключены к входам уменьшаемого блока вычитания абсцисс, входам вычитаемого блока вььчитания аргумента и информационным входам буферного регистра, выходы которого соединены с входами вычитаемог блока Вычитания абсцисс.

Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР по заявке Me 2992317/18-24. . кл. G Об F 15/353, 1О.10,8О.

2. Авторское свидетельство СССР по заявке № 2855О14/18-24, кл.С, 06 F 15/353. 18.12.79 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Функциональный преобразователь | 1982 |

|

SU1037272A1 |

| Цифровой функциональный преобразователь | 1983 |

|

SU1098006A1 |

| Функциональный преобразователь | 1984 |

|

SU1176344A1 |

| Функциональный преобразователь | 1985 |

|

SU1249547A1 |

| Функциональный преобразователь | 1981 |

|

SU960836A1 |

| Функциональный преобразователь | 1983 |

|

SU1115069A1 |

| Функциональный преобразователь | 1984 |

|

SU1211756A1 |

| Устройство для цифрового функционального преобразования | 1981 |

|

SU985792A1 |

| Функциональный преобразователь | 1981 |

|

SU1018127A1 |

| Устройство для аппроксимации функций | 1980 |

|

SU934481A1 |

Авторы

Даты

1983-01-30—Публикация

1981-08-03—Подача