ю

4 tJ

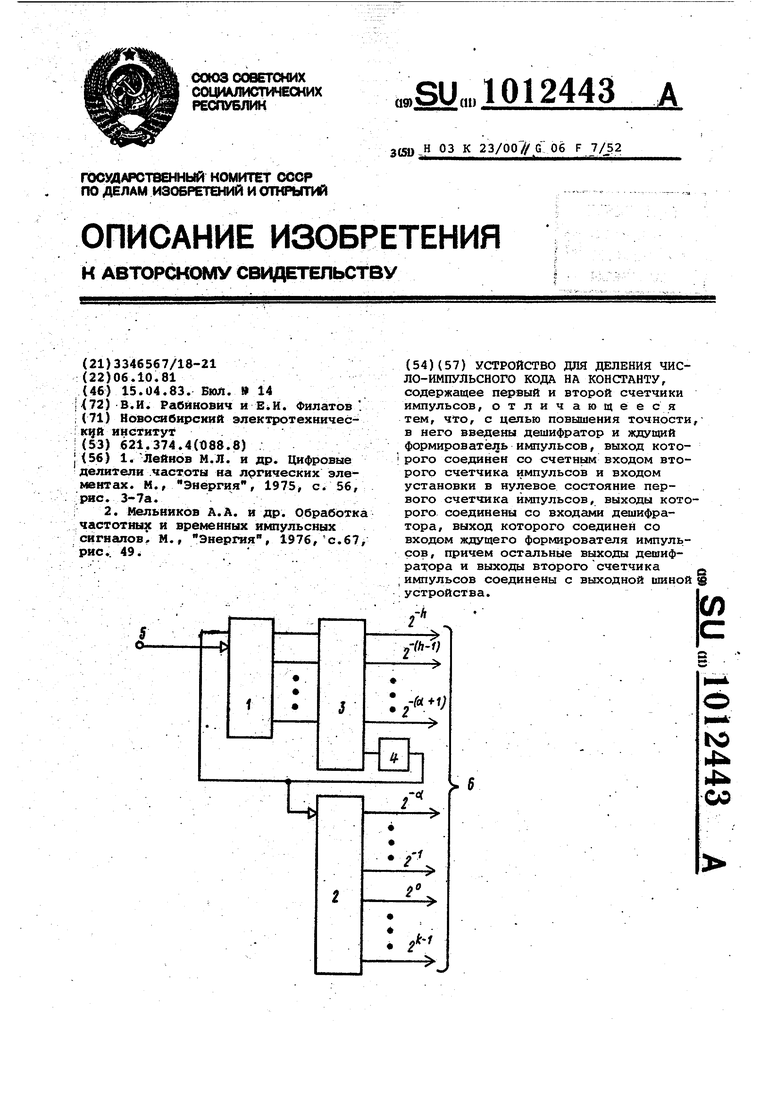

00 Изобретение относится к импульсной технике и предназначено для ис пользования в цифровой аппаратуре. Известно устройство для деления число-импульсных последовательностей на константу, содержащее пересчетные блоки на основе триггерных устройств С1 Недостатком такого устройства является низкая точность вычислений что обусловлено трудностями точной идентификации дробной части результата, остающейся в делителе. По это причине вычисление осуществляется, как правило, с точностью до целого. Наиболее близким по технической сущности к предлагаемому является устройство, содержащее два счетчика регистр, группу элементов И, триггер и ключевую схему, первый вход которой соединен со- входной шиной устройства и счетным входом первого счетчика, второй вход соединен с выходом триггера, а выход - со счет ным входом второго разряда первого .счетчика, установочные входы всех разрядовкоторого подключены к выхо дам соответствующих разрядов регист ра, а вторые входы соединены с выходами первого счетчика, счетным входом второго счетчика и входом установки в нулевое состояние триггера, единичный вход кЬторого подкл чен ко входу запуска устройства .2 Недостатком известного устройств является низкая точность, так как абсолютная погрешность не может быть снижена до значений, меньших по модулю 0,5, что крайне но для большого числа практических задач. Цель изобретения - повышение точ кости устройства. Поставленная цель достигается тем, что устройство для деления число-импульсного кода на константу содержащее первый и второй счетчики импульсов, введены дешифратор и ждущий формирователь импульсов, выход которого соединен со счетным входом второго счетчика импульсов и входомустановки в нулевое состояние первого счетчика импульсов, выходы которого соединены со входами дешифратора, выход которого соединен со входом ждущего формирователя импульсов, а остальные выходы дешиф ратора и выходы второго счетчика импульсов соединены с выходной шино устройства. На чертеже представлена структур ная схема предлагаемого устройства. Устройство для деления число-импульсного кода на константу содержит первый счетчик 1, второй счетчик 2, дешифратор 3, ждущий формиро ватель 4 ИМПУЛЬСОВ, входную шину-5 и выходную шину б. Устройство работает следующим образом. Пусть задана некоторая допустимая абсолютная погрешность Aqj вычисления частного Z -я-. Выберем целое число h такое, что приближение дробной части частного Z h - разрядным двоичным кодом будет иметь погрешность Д«у., Тогда искомым приближением частного будет дробь X )z ,;,. t z:1 П1 а разность E... (2, будет равна числу единиц, содержащемуся в дробной части приближения. Представим делимое в виде х pN+r, где р 0,1,2..., а г - 0,1,2,..., N - 1. Тогда выражение (2) примет вид .±.p, -P-24Ent 2 lp2 -Ent ft.2 .2. (3, Равенство (3) справедливо, так как Ent Ifj по определению равно нулю. Поскольку г может принимать N значений (О, 1, 2, ..., N -1), то и выражение С 3 ), равное дробной части искомого приближения;, пробегает не более N значений. Целая часть приближения возрастает на единицу при каждом очередном изменении г с N- 1 на 0. Представим дополнительно делитель в виде N jp.2, в котором oL - целое неотрицательное число, а -у - ближайшее нечетное число в двоичном разложении делителя. В этом случае в дробной части приближения можно выделить h - 6i младших разрядов, которые пробегают JT значений от О до N - 1, а ot показывает число старших разрядов дробной части, содержимое которых возрастает на единицу каящый раз, когда у изменяется с N-2 - 1 на 0. Делимое х в число-импульсном коде со входа 5 поступает на счетный вход двоичного счетчика 1, число разрядов п которого выбирается равным п 3 8о«у,-yf , означает ближайшее большее или равное целое число. Первые состояний включая нулевое) счетчика 1 лешифрируются с) помощью дешифратора 3, на выходах которого формируются при этом коды значений {h -ot) разрядов дй обной .

части, определяемые для каждого из й1 состояний с помощью заранее составленных таблиц. После;а;ую1цее (у + 1)-ое состояние счетчика 1. является переходным. Когда устанавливается данное состояние, что также идентифицируется дваифратором 3, срабатывает ждущий формирователь 4 короткого импульса, выходной сигнал которого возвращает счетчик 1 в нулевое состояние, а к содержимому счетчика 2 добавляется единица, В счетчике 2формируются значения оС старших разрядов дробной части и k

- (Е„ t -5- ) разрядЬв целой

tiactu результат и.

Дешифратор может быть реализован как на.микросхемах малого уровня интеграции (при небольших -j) , так и на больших интегральных схемах, например программируемых логических матриц (при больших величинах Tf)

Число термов 1 схем совпадения ) первого яруса ПЛМ определяет диапазон возможных,значений коэффициентов деления, а число схем ИЛИ .второго яруса - максимальную разрядность h - dL. При этом одна из выходных схем ИЛИ ПЛМ должна использоваться для трансляции на выход .дешифратора 3 единичного состояния схемы совпадения, дешифрирующей 11Г 1)ое переходное состояние счетчика 1. Дли построения счетчиков 1,2 также могут быть использованы микросхемы .повышег ного уровня интеграции, в результате суммарные аппаратурные Затраты для реализации устройства невелики.

Предлагаемое устройство может л иметь любую наперед заданную абсолютную погрешность вычислений. Например, при h - 10 устройство обеспечивает выигрыш в точности в 512 раз, что существенно расширяет возможнос± применения его в цифровой аппаратуре

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для деления чисел | 1981 |

|

SU1013948A1 |

| СПОСОБ ОПРЕДЕЛЕНИЯ ВЕСОВЫХ ХАРАКТЕРИСТИК ДОСТОВЕРНОСТИ ДЛЯ ОБРАБОТКИ ПРИНЯТЫХ МНОГОПОЗИЦИОННЫХ СИГНАЛОВ | 2007 |

|

RU2339164C1 |

| Диапазонный измеритель временных интервалов последовательного счета | 1985 |

|

SU1307440A1 |

| Делитель частоты следования импульсов с дробным коэффициентом деления | 1988 |

|

SU1529451A1 |

| Цифровой измеритель отношения временных интервалов | 1984 |

|

SU1226399A1 |

| Преобразователь двоичного кода в код с произвольным весом младшего разряда | 1985 |

|

SU1325708A1 |

| Способ измерения частоты импульсного сигнала и устройство для его осуществления | 1980 |

|

SU911359A1 |

| Устройство для преобразования частоты следования импульсов | 1978 |

|

SU764114A1 |

| Делитель частоты с дробнымпЕРЕМЕННыМ КОэффициЕНТОМ дЕлЕНия | 1979 |

|

SU849493A1 |

| Делитель частоты следования импульсов с дробным коэффициентом деления | 1983 |

|

SU1150756A1 |

УСТРОЙСТВО ДЛЯ ДЕЛЕНИЯ ЧИСЛО-ИМПУЛЬСНОГО КОДА НА КОНСТАНТУ, содержащее первый и второй счетчики импульсов, отличающееся тем, что, с целью повышения точности, в него введены дешифратор и ждущий формирователь импульсов, выход которого соединен со счетным входом второго счетчика импульсов и входом установки в нулевое состояние первого счетчика импульсов, выходы которого соединены со входами дешифратора, выход которого соединен со входом ждущего формирователя импульсов, причем остальные выходы дешифратора и выходы второго счетчика ,импульсов соединены с выходной шиной в устройства.ллл. rk ел

Авторы

Даты

1983-04-15—Публикация

1981-10-06—Подача