Изобретение относится к цифровой вычислительной технике, к цифровой измерительной аппаратуре и может быть использовано для преобразования кода числа в соответствии с программируемым значением отношения результата и исходного числа.

Цель изобретения - повышение, точности и быстродействия преобразователя.

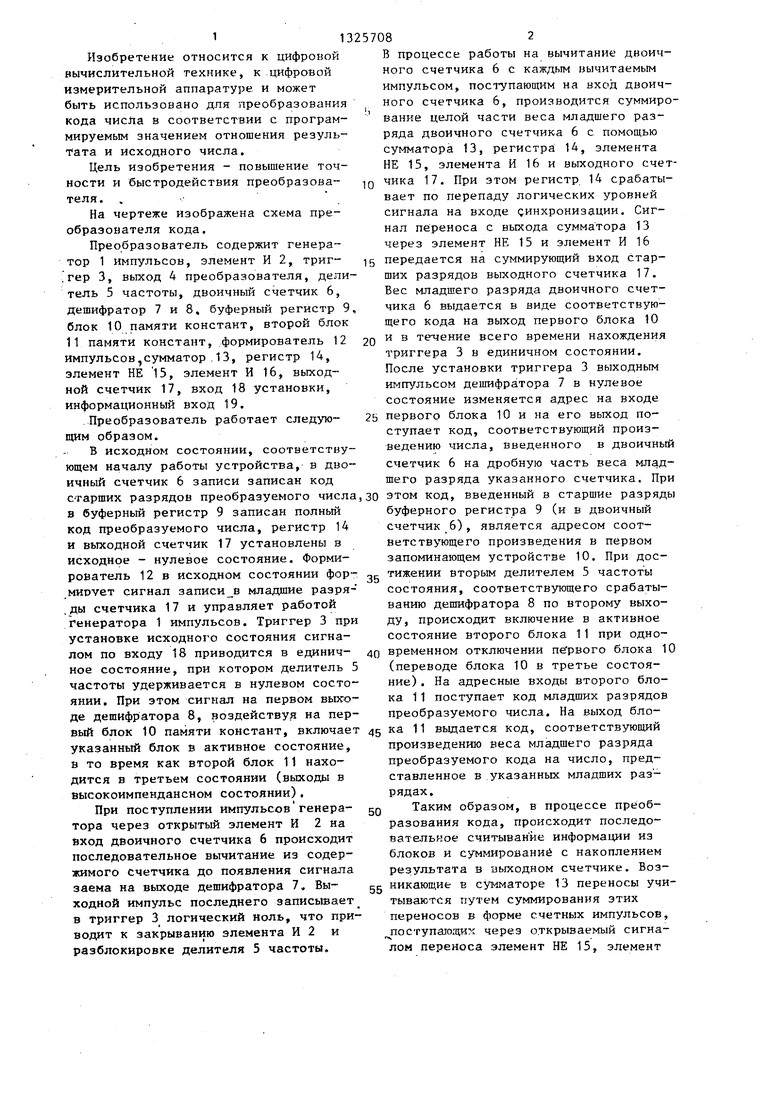

На чертеже изображена схема преобразователя кода.

Преобразователь содержит генератор 1 импульсов, элемент И 2, триг- .гер 3, выход 4 преобразователя, делитель 5 частоты, двоичный счетчик 6, дешифратор 7 и 8. буферный регистр 9 блок 10 памяти констант, второй блок 11 памяти констант, формирователь 12 импульсов,сумматор . 13, регистр 14, элемент НЕ 15, элемент И 16, выходной счетчик 17, вход 18 установки, информационный вход 19.

.Преобразователь работает следующим образом.

В исходном состоянии, соответствующем началу работы устройства, в двоичный счетчик 6 записи записан код

старших разрядов преобразуемого числа,ЗО этом код, введенный в старшие разряды

в буферный регистр 9 записан полный код преобразуемого числа, регистр 14 и выходной счетчик 17 установлены в исходное - нулевое состояние. Формирователь 12 в исходном состоянии фор- g тижении вторым делителем 5 частоты

мирует сигнал записи в младшие разряды счетчика 17 и управляет работой Генератора 1 импульсов. Триггер 3 при установке исходного состояния сигналом по входу 18 приводится в единичное состояние, при котором делитель 5 частоты удерживается в нулевом состоянии. При этом сигнал на первом выходе дешифратора 8, воздействуя на первый блок 10 памяти констант, включает указанный блок в активное состояние, в то время как второй блок 11 находится в третьем состоянии (выходы в высокоимпендансном состоянии),

При поступлении импульсов генератора через открытый элемент И 2 на вход двоичного счетчика 6 происходит последовательное вычитание из содержимого счетчика до появления сигнала заема на выходе дешифратора 7, Выходной импульс последнего записывает в триггер 3 логический ноль, что приводит к закрыванию элемента И 2 и разблокировке делителя 5 частоты.

В процессе работы на вычитание двоичного счетчика 6 с каждым вычитаемым импульсом, поступающим на вход двоичного счетчика 6, производится суммирование целой части веса младшего разряда двоичного счетчика 6 с помощью сумматора 13, регистра: 14, элемента НЕ 15, элемента И 16 и выходного счетчика 17. При этом регистр 14 срабатывает по перепаду логических уровней сигнала на входе синхронизации. Сигнал переноса с выхода сумматора 13 через элемент НЕ 15 и элемент И 16

передается на суммирующий вход старших разрядов выходного счетчика 17. Бес младшего разряда двоичного счетчика 6 выдается в виде соответствующего кода на выход первого блока 10

и в тет1ение всего времени нахождения триггера 3 в единичном состоянии. После установки триггера 3 выходным импульсом дешифратора 7 в нулевое состояние изменяется адрес на входе

первого блока 10 и на его выход поступает код, соответствующий произведению числа, введенного в двоичный счетчик 6 на дробную часть веса младшего разряда указанного счетчика. При

буферного регистра 9 (и в двоичный счетчик 6), является адресом соответствующего произведения в первом запоминающем устройстве 10. При доссостояния, соответствующего срабатыванию дешифратора 8 по второму выходу, происходит включение в активное состояние второго блока 11 при одно40 временном отключении первого блока 1 (переводе блока 10 в третье состояние) . На адресные входы второго блока 1 1 поступает код младших разрядов преобразуемого числа. На выход бло45 ка 11 выдается код, соответствующий произведению веса младшего разряда преобразуемого кода на число, представленное в указанных младших разрядах.

gQ Таким образом, в процессе преобразования кода, происходит последовательное считывание информации из блоков и суммирование с накоплением результата в выходном счетчике. Возgg никающие в сумматоре 13 переносы учитываются путем суммирования зтих переносов в форме счетных импульсов, поступающих через о.ткрываемый сигналом переноса элемент НЕ 15, элемент

И 16 на суммирующий счетный вход старших разрядов счетчика. В выходном счетчике 17 в конце работы устройства: образуется преобразованный

ч код, который выдается на выход 4. Преобразование заканчивается в момент переключения делителя 5 частоты из состояния, при котором возбужден второй выход дешифратора 8, в следующее состояние. При этом по перепаду сигнала на первой входе формирователя 12 на его выход выдается единичный сигнал, который, поступив на вход генератора 1 импульсов, блокирует выдачу тактовых импульсов, поскольку младшая часть счетчика 17 во время преобразования находится в режиме записи, то состояние регистра 14 оказывается пере. писанным в соответствующие разряды счетчика 17. Следующий цикл преобразования начинается после прихода очередного импульса на вход 18 установки исходного состояния.

Структура предлагаемого преобразователя позволяет за счет расширени числа выходов дешифратора 8 и соответствующего числа блоков памяти констант увеличить секционирование выходного счетчика. Наличие счетных цчепей в младпшх разрядах выходного счетчика 17 позволяет принимать дополнительную поправку в число-импуль ном коде от независимого источника.

Пример. Пусть отношение весо младших разрядов результату преобразования и входного кода составляет 0,3346652, а преобразуемое число представлено 16-разрядным двоичным крдом. В первом блоке 10 памяти констант хранятся веса младшего разряда двоичного счетчика 6. Исходя из имеющейся элементной базы запоминающих устройств (микросхемы 556РТ7) с орга низацией 2048x8 выбирают вариант с 8-разрядным сумматором 13. Определяют максимальное число младших разрядов входного кода, которые можно преобразовать непосредственно во втором блоке 11 памяти.

Максимальное число, код которого с учетом восьми выходных разрядов блока памяти, можно непосредственно

использовать °в качестве 1дреса во втором блоке 11 памяти, код числа равен 761,95553. Это число соответствует девяти разрядам преобразуемого двоичного кода, так как ем

10

15

20

-,

45

325708

кость десяти разрядов составляет 1024, Таким образом, девять младпшх разрядов входного кода, записанные в буферном регистре 9, преобразованы в код с новым весом разряда непосредственно с помощью второго блока 11 памяти.

Оставшиеся семь старших разрядов преобразуемого кода также записываются в буферный регистр 9 и адресуют в первый блок 10 памяти. Определяют вес младшего разряда двоичного рядного счетчика 6, в который также записываются старшие семь разрядов преобразуемого кода. В преобразуемом коде этот разряд является десятым, т.е. имеет вес 512 единиц младшего разряда преобразуемого кода. С .учетом требуемого соотношения весов результата преобразования и исходного кода получают вес младшего разряда двоичного счетчика 6, равный 171,34858. В первом блоке 10 памяти заносится код 25 числа 171 во все ячейки, соответству- щие единичному состоянию триггера 3.- В процессе вычитания из содержимого двоичного счетчика 6 произведено суммирование чисел 171 столько раз, сколько соответствует введенному в счетчик 6 исходному коду, т.е. происходит умножение на 171 и результат зафиксируется в счетчике 17 результата. При установке триггера 3 в нулевое состояние на выход первого запоминающего устройства поступает одно из произведений

30

35

П . N -0,34858,

где П - произведение;

N- - число, представленное в

старших семи разрядах преобразуемого кода (максималь-. ное значение N „акс 127; 0,34858 - дробная часть веса младшего разряда старших семи разрядов преобразуемого числа.

Для максимального числа на выходе первого запоминающего устройства 10 сформирован код целой части числа, равный 44,26966.

Дробная часть при этом отброшена и входит в погрешность преобразования.

Из примера видно, что максимальное . значение погрешности в предлагаемом устройстве не превысит двух единиц младшего разряда результата преобразования, которое возникает при отбра

сыванин дробных частей для чисел, представленных в первом блоки 10.(при нулевом состоянии триггера 3), а также для чисел, представленных во втором блоке памяти. Время преобразова- НИН в предлагаемом устройстве при

частоте 1 МГц составляет около 130 мкс

/

Формула изобретения

Преобразователь двоичного кода в код с произвольным весом младшего разряда, содержащий вькодной счетчик, регистр, сумматор, первый блок памяти констант, двоичный счетчик, первый и второй дешифраторы, генератор импульсов, первый и второй элементы И, первые входы которых соединены с выходом генератора импульсов, разряд- ньй выход сумматора соединен с ин- формационньм входом регистра, выход которого соединен с первым входом сумматора, выход первого элемента И соединен со счетным входом Двоичного счетчика, выход которого соединен с входом первого дешифратора, выход выходного счетчика является выходом преобразователя, вход установки которого соединен с входами сброса выходного счетчика, двоичного счетчика и рб гистра, отличающийся тем, что, с целью повышения точности и быстродействия, в него введены второй блок памяти констант, буферный регистр, делитель частоты, формирователь импульса, элемент НЕ и триггер)вход установки которого сое

Редактор В. Бобкова

Составитель Н. Шелобанова

Техред И.Попович Корректор В. Бутяга

Заказ 3125/56Тираж 901Подписное

ВПИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

динен с входом установки преобразователя и входами сброса формирователя Импульса и буферного регистра, выходы которого соединены с адресными входами первого и второго блоков памяти констант, входы управления выдачей которых соединены соответственно с первым и вторым выходами второго дешифратора, вход которого соединен с выходом делителя частоты, информационный вход которого соединен с выходом генератора импульсов, с тактовыми входами, регистра и первого дешифратора, выходы которых соответственно соединены с информационными входами выходного счетчика и входом сброса триггера, выход которого соединен с управляющим входом делителя частоты, вторым входом первого элемента И и. входом старшего разряда адреса первого блока памяти констант, выход которого соединен с вторым входом сумматора и выходом второго блока памяти констант, выход переноса сумматора через элемент НЕ соединен с вторым входом второго элемента И, выход которого соединен со счетным входом выходного счетчика, вход записи которого соединен с выходом формирователя, управляющий вход которого соединен с вторым выходом дешифратора, а выход формирователя соединен с управляющим входом генератора импульсов, информационный вход преобразователя соединен- с информационными входами двоичного счетчика и буферного регистра.

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь двоичного кода в двоично-десятичный код угловых единиц | 1980 |

|

SU970354A1 |

| Преобразователь двоичного кода в двоично-десятичный код угловых единиц | 1986 |

|

SU1349008A2 |

| Преобразователь двоичного кода | 1984 |

|

SU1208607A1 |

| Преобразователь последовательного двоичного кода в параллельный двоично-десятичный код | 1982 |

|

SU1084780A1 |

| Преобразователь двоичного кода в двоично-десятичный код угловых единиц | 1984 |

|

SU1266008A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1981 |

|

SU1013942A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1982 |

|

SU1042010A1 |

| Преобразователь двоично-десятичного кода в двоичный код | 1990 |

|

SU1725399A1 |

| Преобразователь двоичного кода в двоично-десятичный код | 1985 |

|

SU1305869A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1989 |

|

SU1667259A1 |

Изобретение относится к вычислительной технике и цифровой измерительной аппаратуре и может быть использовано для преобразования кода с программируемым отношением результата и исходного числа. Целью изобретения является повышение точности и быстродействия преобразователя. Поставленная цель достигается тем. что в преобразователь, содержащий выходной счетчик 17, регистр 14, сум- ,матор 13, первый блок 10 памяти констант, двоичный счетчик 6, первый 7 и второй 8 дешифраторы, генератор 1 импульсов, первый 2 и второй 16 элементы И,введены второй блок 11 памяти констант, буферный регистр 9, делитель 5 частоты, элемент НЕ 15, формирователь 12 и триггер 3. Причем выходы блоков 10 и 11 памяти констант подключены к входам сумматора 13, выход переполнения которого через элементы НЕ 1 5 и И 16 подключен к счетному входу выходного счетчика 17, информационный вход которого соединен с выходом регистра 14. Адресные входы блоков памяти констант 10 и 11 соединены с выходом буферного регистра 9, а выход триггера 3 управляет старшим адресным входом первого блока 10 памяти констант. 1 ил. а (Л

| Преобразователь двоичного кода в двоично-десятичный код | 1976 |

|

SU744545A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Преобразователь двоичного кода в двоично-десятичный код угловых единиц | 1984 |

|

SU1266008A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1987-07-23—Публикация

1985-12-23—Подача