СП

INS

;о ел

| название | год | авторы | номер документа |

|---|---|---|---|

| ЛИНЕЙНО-КРУГОВОЙ ИНТЕРПОЛЯТОР | 1991 |

|

RU2010293C1 |

| Измеритель частоты | 1989 |

|

SU1691768A1 |

| Цифровой делитель частоты с дробным коэффициентом деления | 1978 |

|

SU892441A1 |

| Умножитель частоты | 1978 |

|

SU765818A1 |

| Программируемый делитель частоты | 1976 |

|

SU657615A1 |

| Синтезатор частот | 1984 |

|

SU1293841A1 |

| Преобразователь угла поворота вала в код | 1991 |

|

SU1833966A1 |

| Умножитель частоты | 1983 |

|

SU1151959A1 |

| Делитель частоты с дробным коэффициентом деления | 1986 |

|

SU1347184A1 |

| АВТОМАТИЧЕСКИЙ СЛЕДЯЩИЙ ДЕЛИТЕЛЬ ПЕРИОДОВ ИМПУЛЬСНЫХ СИГНАЛОВ | 1992 |

|

RU2105410C1 |

Изобретение относится к импульсной технике и может быть использовано в устройствах автоматики и вычислительной техники и в синтезаторах частоты. Цель изобретения - расширение диапазона изменения коэффициента деления за счет обеспечения возможности деления на коэффициент, меньший единицы при одновременном упрощении устройства-достигается путем введения в делитель частоты счетчиков 10, 11 импульсов, регистра 12 памяти и образования новых функциональных связей. Кроме того, делитель частоты содержит генератор 1 импульсов, регистры 2, 3 памяти, сумматоры 4, 5, делитель 6 частоты, блок 7 сравнения, счетчик 8 импульсов, шины 9, 13, 14, 15 выходную, входную, разрешения, задания коэффициента деления соответственно. 1 з.п. ф-лы, 2 ил.

./

Изобретение относится к импульсной технике и может быть использовано в устройствах автоматики и вычислительной техники и в синтезаторах частоты.

Цель изобретения - расширение диапазона изменения коэффициента деления за счет обеспечения возможности деления на коэффициент, меньший единицы при одновременном упрощении устройства.

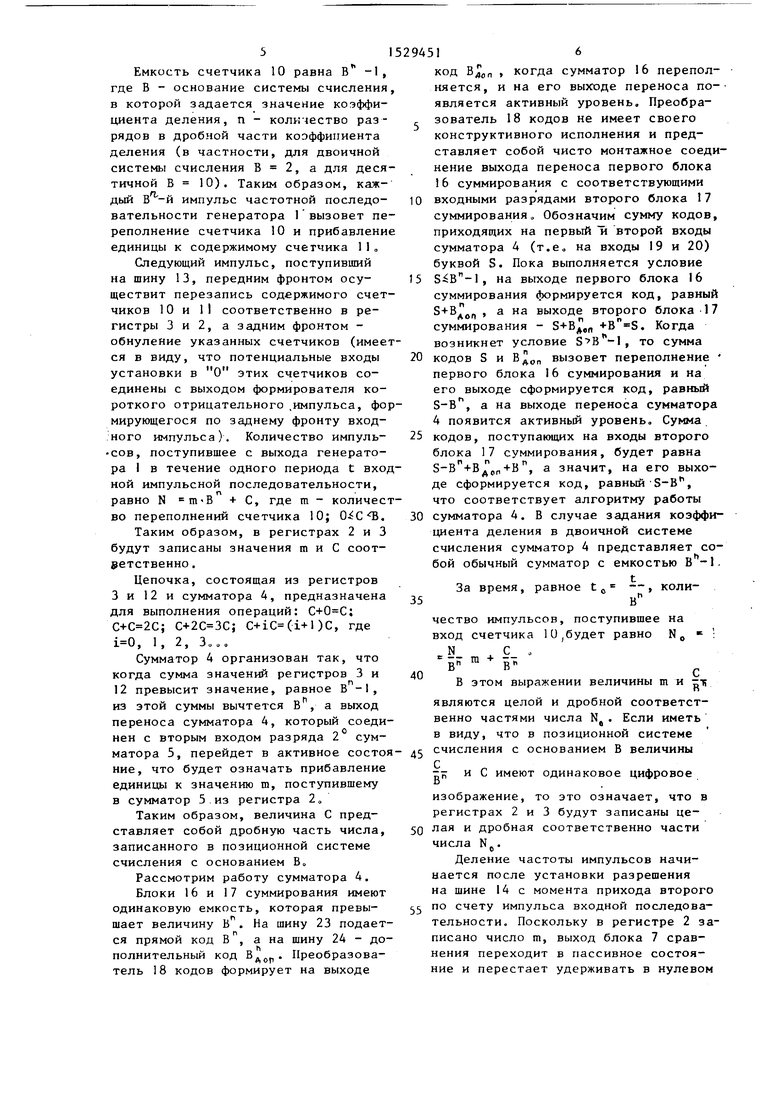

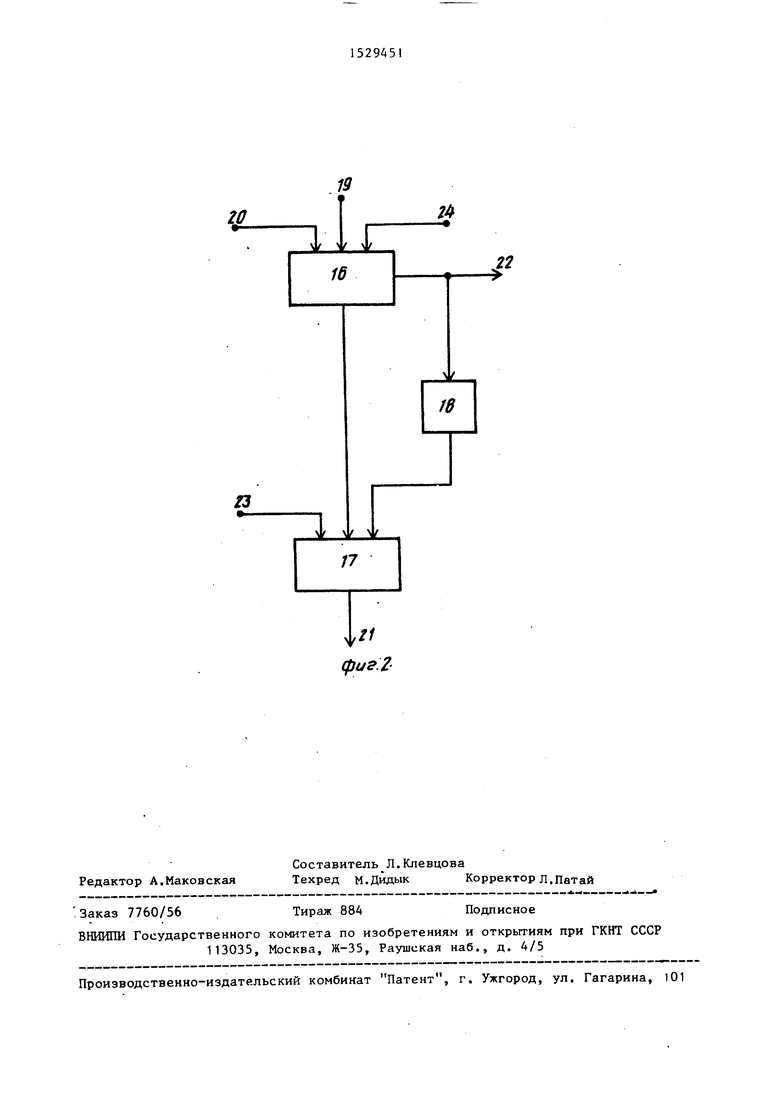

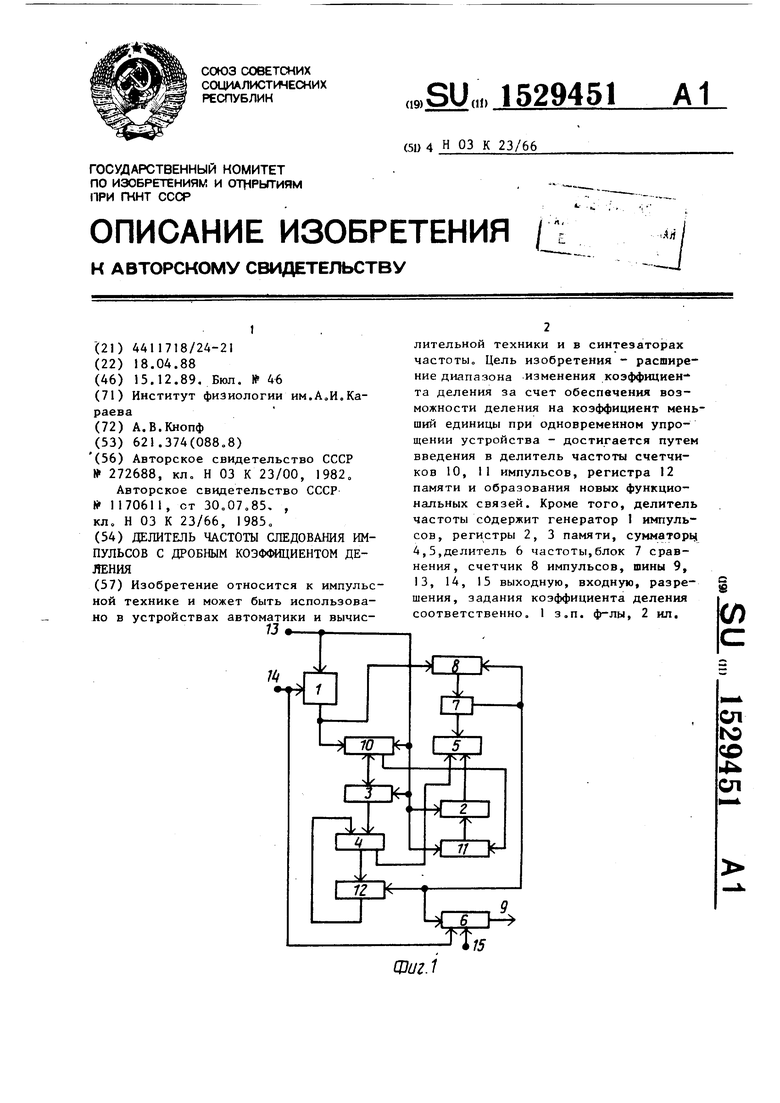

На фиГо приведена структурная схема делителя; на фиг с 2 - структурная схема первого сумматора

Делитель частоты следования импульсов с дробным коэффициентом .деления содержит генератор 1 импульсов, первый 2 и второй 3 регистры памяти, первый 4 и второй 5 сумматоры, дели- тель 6 частоты, блок 7 сравнения, первый счетчик 8-импульсов и выходную шину 9, причем информационный выход второго регистра 3 памяти соединен с первым входом первого суммато- ра 4, второй вход и выход блока 7 сравнения соединены соответственно с информационным выходом и входом установки нуля первого счетчика 8 импульсов, второй 10 и третий 11 счет- чики импульсов, третий регистр 12 памяти, входную шину 13, шину 14 разрешения и шину 15 задания коэффициента деления, причем входная шина 13 соединена с входом запуска генератора

1импульсов, входами записи первого

2и второго S регистров памяти и входами установки в О второго и третье- го счетчиков импульсов, шина 14 разрешения соединена с входом установки в О делителя 6 частоты и входом разрешения генератора 1 импульсов, выход которого соединен с суммирующими входами первого 8 и второго 10 счетчиков импульсов, информационный выход второго счетчика 10 соединен с вхйдом второго регистра 3 памяти, втрой вход и выход первого сумматора 4 соединены соответственно с выходом и информационным входом третьего ре- гистра 12 памяти, а выход переноса с вторым входом второго сумматора 5, выход импульсов переполнения второго счетчика 10 импульсов соединен с суммирующим входом третьего- счетчика 11 импульсов, информационный выход которого соединен с информационным входом первого регистра 2 памяти, выход которого соединен с первым вхо

Q

., ,

5

дом второго сумматора 5, выход которого соединен с первым информационным ВХОДОМ блока 7 сравнения, выход которого соединен с входом записи третьего регистра 12 памяти и счетным входом делителя 6 частоты, установочный вход которого соединен с шиной 15 задания коэффициента деления, а выход - с выходной шиной 9 устройства.

Первый сумматор 4 содержит первый 16 и второй 17 блоки суммирования, преобразователь 18 кодов, первый 19 и второй 20 входы, выход 21, выход 22 переноса, первую 23 и вторую 24 кодовые шины, причем первый 19 и второй 20 входы и вторая кодовая шина 24 соединены соответственно с первым, вторым и третьим входами первого блока 16 суммирования, выход которого соединен с первым входом второго блока 17 суммирования, а выход переноса - с выходом 22 переноса первого сумматора 4 и входом преобразователя 18 кодов, выход которого соединен с вторым входом второго блока 17 суммирования, третий вход которого соединен с первой кодовой шиной 23, а выход 21 - с выходом первого сумматора 4 о

Делитель работает следующим образом

Перед началом деления счетчики 8, 10 и 11 и регистры 2, 3 и 12 обнуляются (шина начальной установки на схеме не показана). Делитель 6 частоты также находится в нулевом состоянии, так как на шине 14 отсутствует сигнал разрешения.

Входная последовательность импульсов с частотой f поступает на шину 13. Генератор 1 импульсов находится в ждущем режиме, запуск его можно осуществить только при наличии сигнала разрешения на шине 14„

После подачи сигнала разрешения первый же импульс входной последовательности своим задним фронтом запускает генератор 1. Импульсы генератора 1 с частотой F, большей, чем входная частота f, начинают поступать на суммирующие входы счетчиков 8 и 10„ Поскольку на оба входа блока 7 сравнения поступают равные одно другому (нулевые) значения, с его выхода снимается сигнал установки в О счетчика 8 и последний не осуществляет счет импульсов генератора 1 .

Емкость счетчика 10 равна в -1, где В - основание системы счисления в которой задается значение коэффициента деления, п - количество разрядов в дробной части коэффициента деления (в частности, для двоичной системы счисления В 2, а для десятичной В 10). Таким образом, каждый импульс частотной последовательности генератора 1 вызовет переполнение счетчика 10 и прибавлени единицы к содержимому счетчика 11

Следующий импульс, поступивший на шину 13, передним фронтом осуществит перезапись содержимого счетчиков 10 и II соответственно в регистры 3 и 2, а задним фронтом - обнуление указанных счетчиков (имееся в виду, что потенциальные входы установки в О этих счетчиков соединены с выходом формирователя короткого отрицательного ,импульса, фомирующегося по заднему фронту входного импульса). Количество импуль- сов, поступившее с выхода генератора I в течение одного периода t входной импульсной последовательности, равно N т В + С, где m - количесво переполнений счетчика 10; .

Таким образом, в регистрах 2 и 3 будут записаны значения m и С соответственно ,

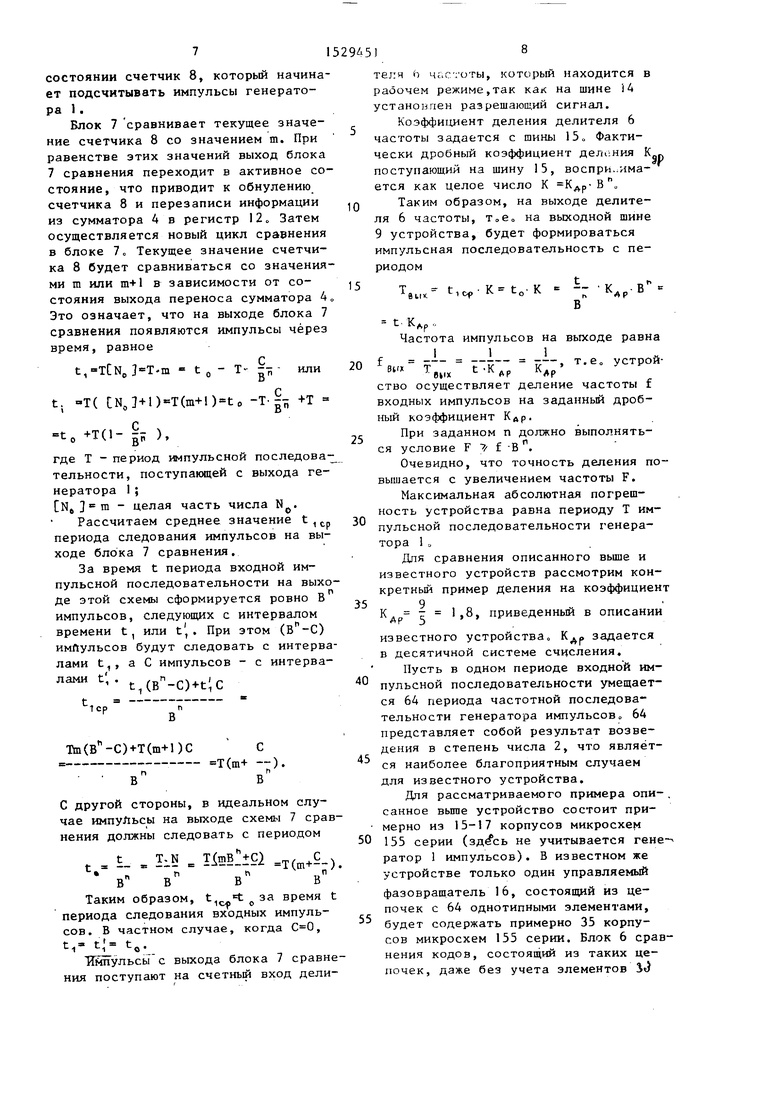

Цепочка, состоящая из регистров 3 и 12 и сумматора 4, предназначена для выполнения операций: C+iC(i+l)C, где , 1, 2, 3„„о

Сумматор 4 организован так, что когда сумма значений регистров 3 и 12 превысит значение, равное В -I, из этой суммы вычтется В , а выход переноса сумматора 4, который соединен с вторым входом разряда 2 сумматора 5, перейдет в активное состояние, что будет означать прибавление единицы к значению т, поступившему в сумматор 5.из регистра 2

Таким образом, величина С представляет собой дробную часть числа, записанного в позиционной системе счисления с основанием В

Рассмотрим работу сумматора 4.

Блоки 16 и 17 суммирования имеют одинаковую емкость, которая превышает величину В . На шину 23 подается прямой код в , а на шину 24 - дополнительный код . Преобразователь 18 кодов формирует на выходе

код , когда сумматор 16 переполняется, и на его выходе переноса появляется активный уровень. Преобразователь 18 кодов не имеет своего конструктивного исполнения и представляет собой чисто монтажное соединение выхода переноса первого блока 16 суммирования с соответствующими

0 входными разрядами второго блока 17 суммирования о Обозначим сумму кодов, приходящих на первый Ti второй входы сумматора 4 (т.е„ на входы 19 и 20) буквой S. Пока выполняется условие

5 , на выходе первого блока 16 суммирования формируется код, равный S+B , а на выходе второго блока 17 суммирования - . Когда возникнет условие , то сумма

0 кодов S и Вдо„ вызовет переполнение первого блока 16 суммирования и на его выходе сформируется код, равный S-B, а на выходе переноса сумматора 4 появится активный уровень Сумма

5 кодов, поступающих на входы второго блока 17 суммирования, будет равна 5-в - -Вд5р+В, а значит, на его выходе сформируется код, равный , что соответствует алгоритму работы

0 сумматора 4. В случае задания коэффициента деления в двоичной системе счисления сумматор 4 представляет собой обычный сумматор с емкостью В -1.

5

За время, равное t,, - колив

чество импульсов, поступившее на вход счетчика 1 Отбудет равно N N С

5 ™ 1

в этом выражении величины m и -т;

п

являются целой и дробной соответственно частями числа N. Если иметь в виду, что в позиционной системе 5 счисления с основанием В величины (

-f; И С имеют одинаковое цифровое ь

изображение, то это означает, что в регистрах 2 и 3 будут записаны це0 лая и дробная соответственно части числа Np.

Деление частоты импульсов начинается после установки разрешения на шине 14 с момента прихода второго

5 по счету импульса входной последовательности. Поскольку в регистре 2 записано число т, выход блока 7 сравнения переходит в пассивное состояние и перестает удерживать в нулевом

71529

состоянии счетчик 8, который начинает подсчитывать импульсы генератора 1 .

Блок 7 сравнивает текущее значение счетчика 8 со значением т. При равенстве этих значений выход блока 7 сравнения переходит в активное состояние, что приводит к обнулению счетчика 8 и перезаписи информации Q из сумматора 4 в регистр 12о Затем осуществляется новый цикл сравнения в блоке 7 о Текущее значение счетчика 8 будет сравниваться со значениями m или т+1 в зависимости от состояния выхода переноса сумматора 4 Это означает, что на выходе блока 7 сравнения появляются импульсы через время, равное

t,.m t - Т- т;

или

1ср

t; Т( CNj-H)T(m+l)to -T. -t-T

t, +Т(1- IK ),

где Т - период импульсной последова- тельности, поступающей с выхода генератора 1 ; NJ m - целая часть числа N.

Рассчитаем среднее значение t , периода следования импульсов на выходе блока 7 сравнения.

За время t периода входной импульсной последовательности на выходе этой схемы сформируется ровно в импульсов, следую1цих с интервалом времени t, или t , , При этом () имПульсов будут следовать с интервалами t,, а С импульсов - с интерва- лами t; , )+t;c

t.

C)+T(m+l)C

В

Т(т+ -).

h

В

С другой стороны, в идеальном случае импуЛьсы на выходе схемы 7 сравнения должны следовать с периодом

, . I.N ИшвЧс .г(ш.5-), в в в в

Таким образом, t за время t периода следования входных импуль- сов, В частном случае, когда , ti t{ t,,

Ийпульсы с выхода блока 7 сравнения поступают на счетный вход дели

Q

5

18

телч (т час готы, который находится в рабочем режиме,так как на щине 14 устаноипен разрешающий сигнал,

Коэффициент деления делителя 6 частоты задается с шины 15о Фактически дробный коэффициент деления К поступающий на шину 15, воспри.има- ется как целое число К Кдр-В.

Таким образом, на выходе делителя 6 частоты, Тое,, на выходной шине 9 устройства, будет формироваться импульсная последовательность с периодом

-: .р-в

в

эр

йчк ticf к - to к

0

5

О

0

5

0

t. к

f,f Частота импульсов на выходе равна

:

BM)i т устрой вИХ

ство осуществляет деление частоты f входных импульсов на заданный дробный коэффициент Кдр.

При заданном п должно выполняться условие F f -В .

Очевидно, что точность деления повышается с увеличением частоты F.

Максимальная абсолютная погрешность устройства равна периоду Т импульсной последовательности генератора 1 о

Для сравнения описанного выше и известного устройств рассмотрим конкретный пример деления на коэффициент

9 К 7 1,8, приведенный в описании

Г Э

известного устройства. Кд задается в десятичной системе счисления.

Пусть в одном периоде входной импульсной последовательности умещается 64 периода частотной последовательности генератора импульсов о 64 представляет собой результат возведения в степень числа 2, что является наиболее благоприятным случаем для известного устройства.

Для рассматриваемого примера опи-. санное выгае устройство состоит примерно из 15-17 корпусов микросхем 155 серии ( не учитывается гене- ратор 1 импульсов), В известном же устройстве только один управляемый

фазовращатель 16, состоящий из цепочек с 64 однотипными элементами, будет содержать примерно 35 корпусов микросхем 155 серии. Блок 6 сравнения кодов, состоящий из таких цепочек, даже без учета элементов 5

сравнения будет содержать примерно 33 корпуса микросхем 155 серии„

В том случае, когда в одном периоде входной последовательности уместится количество импульсов генератора, не равное 2, где ,1,2, 3,..,, известное устройство еще более усложняется за счет усложнения блока 3 сумматоров и элементов 36,

Итак, описанный выше делитель значительно проще известного, и зто преимущество будет тем больше, чем большее количество импульсов генератора уложится в одном периоде входной частотной последовательности

Другое преимущество описанного делителя заключается в том, что ой позволяет осуществить деление частоты импульсов на коэ4)фициент меньший единицы, т.е. на выходе делителя будут появляться импульсы с частотой большей, чем входная. А это означает, что описанный делитель может работать как умножитель частоты следо- вания импульсов.

Формула изобретения

памяти, входная шина, шина разрешения и шина задания коэффициента деления, причем входная шина соединена с

Q

5

0 5

0 Q г

5

0

входом запуска генератора импульсов, входами записи первого и второго регистров памяти и входами установки в О второго и третьего счетчиков импульсов, шина разрешения соединена с входом установки в О делителя частоты и входом разрешения генератора импульсов, выход которого соединен с суммирующими входами первого и второго счетчиков импульсов, информационный выход второго счетчика импульсов соединен с входом второго регистра памяти, второй вход и выход первого сумматора соединены соответственно с выходом и информационным входом третьего регистра памяти, а выход переноса - с вторым входом второго сумматора, причем выход переполнения второго счетчика импульсов соединен с суммирующим входом третьего счетчика импульсов, информационный выход которого соединен с информационным входом первого регистра памяти, выход которого соединен с первым входом второго сумматора, выход которого соединен с первым информационным входом блока сравнения, выход которого соединен с входом записи третьего регистра памяти и счетным входом делителя частоты, установочный вход которого соединен с шиной задания коэффициента деления а выход - с выходной шиной делителя.

е

1

f(

16

5

Л

//

(puff.ZРедактор А.Маковская

Составитель Л.Кпевцова

Техред М.ДЙдык Корректор л.Патай

Заказ 7760/56

Тираж 884

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат Патент, г. Ужгород, ул. Гагарина, 101

24

22

f f

Подписное

| ФУНКЦИОНАЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ ЧАСТОТЫ В НАПРЯЖЕНИЕ ПОСТОЯННОГО ТО'КА | 0 |

|

SU272688A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Делитель частоты следования импульсов с переменным коэффициентом деления | 1983 |

|

SU1170611A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1989-12-15—Публикация

1988-04-18—Подача