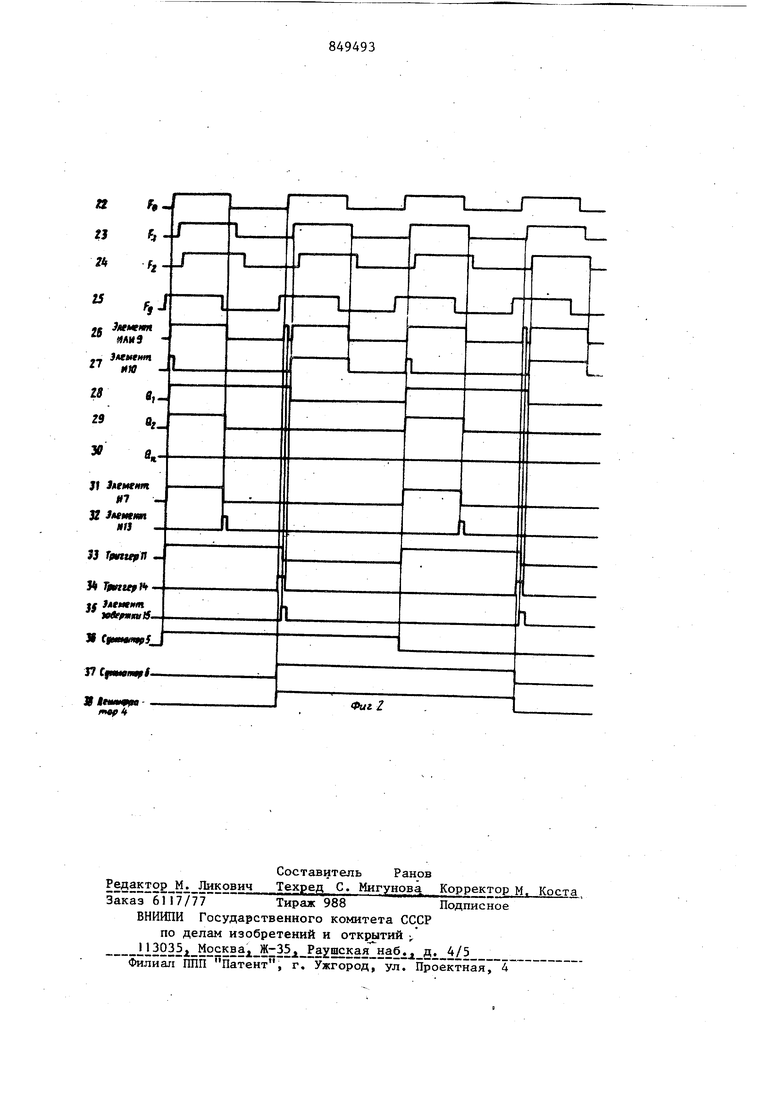

(54) ДЕЛИТЕЛЬ ЧАСТОТЫ С ДРОБНЫМ ПЕРЕМЕННЫМ Изобретение относится к импульсной технике и может быть использовано в автоматике и вычислительной технике. Известен делитель частоты с дробным переменным коэ(})фициентом деления, содержащий формирователь импульсов, схемы И, детектор заполнения, счетчик задающее устройство, схемы установки целых и дробных долей, триггер сдвига и элементы И-ИЛИ СЧ Недостатком известного устройства является невозможность получения любого коэ(|)фициента в случайном порядке. Известен делитель частоты с дробным переменным коэффициентом деления, содержащий генератор импульсов, фазосдвигающий элемент, дешифратор частот счетчик дробного коэффициента деления, программный блок, цифровой компаратор счетчик целого числа, элемент ИЖ, переключатель и блок элементов И, первые входы которых соединены с выходами фазосдвигающего элемента, вход коКОЭФФИЦИЕНТОМ ДЕЛЕНИЯ торого соединен с выходом генератора импульсов, выходы дешифратора частот соединены со вторыми входами блока элементов И, выходы которых соединены со входами элемента ИЛИ . Недостатком известного устройства является невозможность получения любого коэффициента деления в случайном порядке, так как коэффициент деления определяется программным устройством, а также ограниченной величиной целой и дробной частей коэффициента деления. Цель изобретения - расширение диапазона регулирования коэффициента д ления. . Поставленная цель достигается тем, что в делитель частоты с дробным переменным коэффициентом деления, содержащий генератор импульсов, фазосдвигающий элемент, дешифратор частот, счетчик целой части коэффициента деле.ния, элемент ИЛИ и блок элементов И, первые выходы которых соединены с выходами фазосдвигающего элемента, вход которого соединен с выходом генератора импульсов, выходы дешифратора частот соединены со вторыми входами блока элементов И, выходы которых соединены со входами элемента ИЛИ, введены накапливающий сумматор, регистр хранения кода частот, элемент задержки, три элемента И, элемент НЕ, два триггера, первая и вторая , группы шин, которые соединены с информационныг- и входами соответственно накапливающего сумматора и счетчика целой части коэффициента деления, тактовый вход, вход управления записи и выходы которого соединены соответственно с выходами первого, второго и входами третьего элементов И, выход третьего элемента И соединен с пе вым входом второго элемента Икс первым входом первого триггера, прямой выход которого соединен с тактовым входом накапливающего сумматора и с первым входом второго триггера, прямой выход которого соединен со входом управления записи регистра хранения кода частот и через элемент задержки со вторым входом первого триггера, инверсный выход которого соединен с первым входом первого эле мента И, второй вход которого соединен с выходом элемента ИЛИ, со- ёторы входом второго триггера и через элемент НЕ со вторым входом второго эле мента И, выходы накапливающего сумма тора соединены с информационными вхо дами регистра хранения кода частот, выходы которого соединены со входами дешифратора частот. На фиг. 1 изображена структурная схема предлагаемого устройства; на фиг. 2 - временная диаграмма работы предлагаемого устройства. Устройство содержит генератор 1 импульсов, фазосдвигакщий элемент 2, блок элементов. ИЗ, дешифратор 4 частот, накапливающий сумматор 5, регистр 6 хранения кода частот, элемент И 7. счетчик 8 целой части коэф фициента деления, элемент ИЛИ 9, эле мент И 10, триггер II, элемент НЕ 12 элемент И 13, триггер 14, элемент 15 задержки, тактовые входы 16 и 17 соответственно накапливающего сумматора 5 и счетчика 8 целой части коэф фициента деления, входы 18 и 19 упра ления записи соответственно регистра 6 хранения кода частот и счетчика 8 34 целой части коэффициента деления группы шин 20 и 21. Выход генератора 1 импульсов соединен со входом фазосдвигающего элемента 2, выходы которого соединены с первыми входами блока элементов И 3, вторые входы которых соединены с выходами дешифратора 4 частот, входы которого соединены с выходами регистра 6 хранения кода частот, информационные входы которого соединены с выходами накапливающего сумматора 5, информационные входы которого соединены с группой шин 20, группа щин 21 соединена с информационными входами счетчика 8 целой части коэффициента деления, выходы которого соединены со входами элемента И 7, выход которого соединен с первым входом элемента И 13 и с первым входом триггера 11, прямой выход которого соединен с тактовым входом 16 накапливающего сумматора 5 и с первым входом триггера 14, прямой выход которого соединен со входом I8 управления записи регистра 6 хранения кода частот и со входом элемента 15 задержки , выход которого соединен со вторым входом триггера 11, инверсный выход которого соединен с первым входом элемента И 10, второй вход которого соединен с выходом элемента ИЛИ 9, со вторьм входом триггера 14 и со входом элемента НЕ 12, выход которого соединен со вторым входом элемента И 13, выход которого соединен со входом I9 управления записи счетчика 8 целой части коэффициента деления, тактовый вход которого соединен с выходом эл емента И 10, выходы блока элементов И 3 соединены со входами элемента ИЛИ 9. На фиг. 2 обозначено: 22-25 - сигналы на выходах фазосдвигающего элемента 2; 26 и 27 - сигналы на выходах соответственно элементов ИЛИ 9 и И 10; 28-30 - сигналы на выходах счетчика 8 целой части коэффициента деления; - сигналы на выходах соответственно элементов И 7, 13 и триггеров П и 14; 35-38 - сигналы на выходах соответственно элемента 15 задержки, накапливающего сумматора 5, регистра 6 хранения кода частот 6 и дешифратора 4 частот. Устройство работает следующим образом. Импульсы генератора 1 поступают на вход фазосдвнгающего элемента 2 где преобразуются в импульсы с частотами F , F, , F,.. . F , равными частоте генератора 1, но сдвинутыми относительно друг друга на 1/т часть привода (фиг. 2, диаграммы 22-25). Эти частоты поступаю на соответствующие элементы блока элементов И 3, число которых соответствует числу m частот, формируемых в фазосдвигагацем элементе 2. Величина m ограничивается быстродей ствием элементной базы и рабочей частотой. Блок элементов И 3 пропускает на свои выходы одну из частот, выбранную дешифратором 4 частот, состояни которого задается накапливающим сум матором 5 через регистр 6 хранения кода частоты. Число разрядов накапливающего су матора 5 должно обеспечивать набор выходов дешифратора частот 4 и опре деляется формулой , причем округляется в большую сторону. Накапливающий сумматор 5 обеспечивает цикличность переключения кодов дешифратора 4 частот при переходе с данной частотой на другую во время деления на дробный коэффициент в за висимости от его величины. Например при m равном 10, когда частоты Fg , F , Fr. , .. ., Е сдвинуты на 1/10 пер ода и заданной дробной части коэффи циента деления 0,3, смена частот пр исходит в следукнцем порядке: 2. ь 9 ч Z и т.д. Для обеспечения цикличности переключения дешифратора 4 частот при любом в исходном состоянии в накапливающий сумматор 5 записывается число, равное , а потом эт число прибавляется всякий раз по си налу переноса со старшего разряда. При дополнительной записи не требуется. При постоянной дробной части коэффициента деления накапливающий сумматор 5 суммирует число, находящееся в нем, с числом, поступающим, на его входы в виде кода дробной части коэффициента. Для рассмотренного примера каждой 1/т части перио да соответствует код 0001, для 3/т - , для 6/т - 0110 и т.д. Суммирование производится всякий раз после завершения цикла деления 3 импульсом с выхода триггера 11, переключаемого элементом И 7, опознающим окончание счета счетчиком 8. Сумма . на выходе накапливающего сумматора 5 каждый раз увеличивается на величину дробной части коэффициента деления, в результате чего дешифратор 4 частот производит подключение очередного элемента блока элементов ИЗ, т.е. разрешает прохождение через необходимый элемент импульсов частоты, сдвинутой по отношению к предьщущей на необходимую часть дериода, что и образует дробную часть коэффициента деления. При смене дробной части коэффициента деления работа делителя не нарушается. Импульсы последовательности выбранной частоты с элемента ИЛИ 9 поступают на выход элемента И 10, открытого уровнем логической I со второго выхода триггера 11, и далее на счетный вход счетчика 8, который переключается до полного касьш1ения, которое опознается элементом И 7. Величина целой части коэффициента деления задается кодом, подаваемым на установочныевходы счетчика 8 целой части коэффициента. По группе шин 21 коэффициент деления задает запись в счетчик 8 числа -1-К, где п - число разрядов счеччика К - целая часть коэффициента деления. На временной диаграмме (фиг. 2) коэффициент деления , 1, К 2. К может принимать значения от 1 до . К-м импульсом счетчик 8 наполняется до насьш ения, появившийся импульс опознания с элемента И 7 проходит на выход и одновременно переключает триггер 11, который разрешает суммирование накапливающему сумматору 5, закрывает элемент И 10 уровнем логического о со второго выхода, запрещает прохождение (К+1) импульса старой последовательности и подготавливает к переключению триггера 14, подавая на его Д-вход уровень огической 1 фиг. 2). По окончанию К-го импульса элеент И 13 вьщает на счетчик 8 импульс аписи целой части коэффициента (фиг. 2), котЬрым в счетчик 8 заисьлвается число N. После чего счетик 8 готов к повторению цикла делеия. 78 (К+1)-ым импульсом с элемента ИЛИ 9 триггер 14 переключается и с первого CBoeio выхода вьщаег импульс перезаписи на регистр 6 хранения и через элемент 15 задержки (фиг. 2) устанавливает триггер 11 в исходное состояние, что приводит к открыванию элемента И 10. Дешифратор 4 частот переключает элементы блока элементов И 3, и следующий импульс новой импул сной последовательности, сдвинутой по отношению к предыдущему на заданн часть периода, поступает на счетный вход счетчика 8 и цикл деления повторяется сначала. Таким образом, триггеры 11 и I4 выполняют функцию защиты делителя от ложных срабатываний при делении на дробный коэффи1щент. Регистр 6 хранения кода чатоты хранит код выбранной частоты в период формирования накапливающим сумматором 5 кода новой частоты и переключается по переднему фронту (К+I)-импульса, т.е. не менее чем за 1/т часть периода до прихода следующей импульсной последовательности (фиг. 2). Величина задержки элемента 15 задержки выбирается таким образом, чтобы обеспечить открывание элемента И IО после переключения элементо блока элементов ИЗ, т.е. она должна быть больше суммарной задгржки элемента ИЛИ 9, элемента из блока элементов И 3, дешифратора 4 частот и регистра 6 хранения кода част Данный делитель с дробным переме ным коэффициентом деления имеет зна чительно больший диапазон регулирования коэффициента деления как цело так и дробной части, чем известные, а также позволяет изменять коэффициент деления в любом случайном порядке, причем делитель защищен от с ев при смене коэффициента деления. Формула изобретения Делитель частоты с дробным переменным коэффициентом деления, содер жащий генератор импульсов, фазо3сдвигающий элемент, дешифратор частот, счетчик целой части коэффициента деления, элемент ИЛИ и блок элементов И, первые входы которых соединены с выходами фазосдвигающего элемента,-ВХОД которого соединен с выходом генератора импульсов, выходы дешифратора частот соединены со вторыми входами блока элементов И, выходы которых соединены со входами элемента ИЛИ, отличающийс я тем, что, с Целью расширения диапазона регулирования коэффициента деления, в него введены накапливающий сумматор, регистр хранения кода частот, элемент задержки, три элемента И, элемент НЕ, два триггера, первая и вторая группа шин, которые соединены с информационными входами соответственно накапливающего сумматора и счетчика целой части коэффициента деления, тактовый вход, вход управления записи и выходы которого соединены соответственно с выходами первого, второго и входами третьего элементов И, выход третьего элемента И соединен с первым входом второго элемента И и с первым входом первого триггера, прямой выход которого соединен с тактовым входом накапливающего сумматора и с первым входом второго триггера, прямой выход которого соединен со входом управления записи регистра хранения кода частот и через элемент задержки со вторым входом первого триггера, инверсный выход которого соединен с первым входом первого элемента И, второй вход которого соединен с выходом элемента ИЛИ, со вторым входом триггера и через элемент НЕ со вторым входом.второго элемента И, выходы накаштивающего сумматору соединены с информационными входами регистра хранения кода частот, выходы которого соединены со входами дешифратсра частот. Источники информации, принятые во внимание при экспертизе 1 , Авторское свидетельство СССР № 453803, кл. Н 03 К 23/00, 1974. 2. Авторское свидетельство СССР № 621102, кл. Н 03 К 23/00, 1977.

| название | год | авторы | номер документа |

|---|---|---|---|

| Делитель частоты следования импульсов | 1982 |

|

SU1150755A1 |

| Делитель частоты следования импульсов с дробным переменным коэффициентом деления | 1980 |

|

SU949821A1 |

| Устройство для коррекции шкалы времени | 1987 |

|

SU1432451A2 |

| Делитель частоты следования импульсов с переменным коэффициентом деления | 1978 |

|

SU786010A1 |

| Устройство для коррекции шкалы времени | 1990 |

|

SU1709268A1 |

| Делитель частоты следования импульсов с переменным коэффициентом деления | 1981 |

|

SU1010729A1 |

| Умножитель частоты следования периодических импульсов | 1980 |

|

SU980094A1 |

| Делитель частоты следования импульсов с дробным переменным коэффициентом деления | 1982 |

|

SU1077053A1 |

| Цифровой умножитель частоты | 1979 |

|

SU788363A1 |

| Устройство для коррекции шкалы времени | 1991 |

|

SU1781669A1 |

Авторы

Даты

1981-07-23—Публикация

1979-10-08—Подача