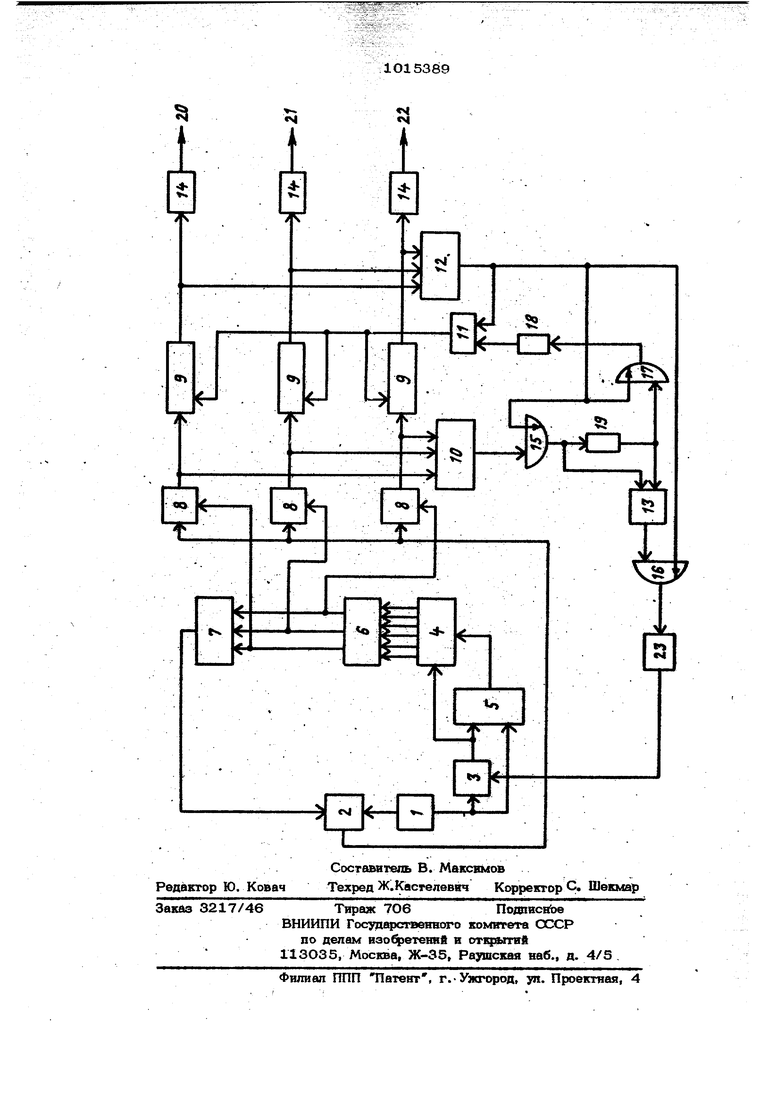

Изобретение относится к вычислительной технике, в частности к устройствам контроля логических схем, и может быть применено для контроля приборов систем автомагического управления. Известно устройство для контроля мажоритарных схем, содержащее генератор тактовых импульсов, соединенньтй выходом с входом элемента И, компаратор, первый выход которого является выходом устройства, а ваеоды которого соединены с соответствукяцими выходами шифратора, исчетчик импульсов Cl 3 Устройство позволяет контролировать мажоритарные схемы, фиксируя сам факт неисправности,но обдадает низкой достоверностью контроля, так как вы Дача сигнала неисправности производится после однократного анализа. Наиболее близким к предлагаемому i по технической суишости является устройство для контроля мажойитарныхбиоков, содержащее генератор тактовых иклульсов, соединенный с элементом И, компаратор, первый выход которого является выходом устройства, а входы соединены с соответствующими выходами шифратора, счетчик импузтьсЬв, соединенный с сумматорол по модулю два, реверсивным распределителем и узлом сброса С21 . Недостатками данного устройства являются его низкие функциональные возможности, так как устройс тво не позволяет определить по какому входу неисправен мажоритарный блок а также низкая достоверность контколя, проявлякяпая ся в том, что в предессе работы происхо дит накопление счетчиком сигналов ощиб ки, в результате чего за Неисправность мажоритарного блока принимается трехкратный сбой устройства при разных коМ бинаииях сигналов, на входах мажоритарного блока. Цель изобретения - повышение .достоверности контроля мажоритарных схем и расширение функциональных возможностей устройства. Поставленная цель достигается тем, что в устройство для контроля мажоритарных блоков, содержащее генератор тактовых импульсов, соеди) первым выходом с первым входом первого элеме та И и первым входом сумматора по модулю два, второй вход которого соединен с вьосодом первого элемента И и первым входом реверсивного распределителя, а выход - с вторым вкодом реверсивного распределителя, выходы которого подключены к соответствующим входам шифратора, выходы ши4Ч}атора соединены с соответствующими входами Мажоритарногоблока, выход которого подключен к первому входу компаратора, второй вход которого соединен с вторым выходом гене- ратора тактовых импульсов, введень : вторые элементы И, элементы ИЛИ, элементы ЗАПРЕТ, элементы задержки, Элемент НЕ « первые и вторые счетчики, суммиру}юпше входы первых счетчиков подключены к выходам соответствующих вторых эле- ментов И и входам первого элемента ИЛИ, выход которого подключен к входу первого элемента .ЗАПРЕТ, первые входы вторых элементов И подключены соотвегстведно к первому, второму и третьему выходам шифратора, а вторые входы - к выхо-. ду компаратора, выходы первых счетчиков подключены к суммирующим входам соответствующих вторых счетчиков и к входам второго элемента ИЛИ, выход которого соединен с первым входом третьего элемента ИЛИ и с запркещаюшимн входами первого, второго и третьего элементов ЗАПРЕТ, выход первого элемента ЗАПРЕТ соединен с первым входом четвертого эдемекта ИЛИ и через первый элемент задержки - с входом третьего элемента ЗАПРЕТ и с вторым входом че твертого элемента ИЛИ, ввдсод которого подключен к входу второго элемента ЗАПРЕТ, выход которого соеданен через элемент НЕ с входом первого Элемента И, а выход третьего элемента ЗАПРЕТ через второй элемент задержки подключен к второму входу третьего элемента ИЛИ, выход которого соединен с входами установки нуля первых счетчиков. На чертеже приведена блок-схема предлагаемого устройства. Устройство содерисит генератор 1 так-, товых импульсов, компаратор 2, лерилй элемент И 3, верси&шлй распределитель 4, сумматор 5, шифратор 6, мажоритарг ный блок 7, вторые элементы И 8, первые счетчики 9, первый элемент ИЛИ 1О, третий элемент ИЛИ 11, второй эле- мент ИЛИ 12, четвертый элемент ИЛИ 13, вторые счетчики 14, первый, второй и третий элементы ЗАПРЕТ 15 - 17 , соответственно J второй элемент 18 задержки, первый элемент 19 задержки, выходы 20 - вторых счетчиков и элемент НЕ 23. Счетчики 9 и 14 служат для подсчета числа отказов мажоритарного блока 7, причем счегчик 9 подсчитьшает число отказов за один цикл проверки мажоритарно;го блока, а счетчик 14 - за весь период. Элементы 18 и 19 задержки слз/жат для задержки восодных сигналов на время, равное двум тактам генерато ра 1 импульсов. Устройство работает следукшвм образом. Перед работой устройство должно быт приведено в исходное состояние, при кот ром счетчики 9 и 14 обнулены (цепи об иуления на чертеже не показашл), а на выходе элемента НЕ 23 {жсутствует высокий потенциал, отк;я 1Вакхций элемент И 3 по nepuoMjr .вход. тактовый импульс .гевератс 1 через открынгийся элемент ИЗ поступвет на вход ревер сивного рв(гпределнтёля 4, с первого кан лакоторого шифратором 6 формируется дервь1й такт ,тест6вого набора - включае ся первый канал мажоритарного Спока 7, 9 также открывается по первому входу элемент И 8 первого канала. При правильной pa.6piie мажоритарный блок 7 не выдает С9пгнала и компаратор 2отсутст &ием сигнал1а на своем выходе подтве{я1Ц1ает пр1авильность работы мажоритарного 6ifoiia 7, пра этом элемент И 3 остается открытым, а сумматор 5 по модутпо два закрыт, так как на его .обоих входах присутствуют высокие, потешшалы с генератЬра 1 и элемента ИЗ. Во время де1К:твия второго тактового RMnynibca шифратором б формируется второй такт -теста, при. котором включаюгся 1 в 2 каналы мажрригарвого Спока 7 и открываются по одному из входов элемента И 3 первого и в-горого карала. Аналогичным образом-формируются лоследукяквё тестового набора, прифм на 3-ем такте включается 2 канал мажсфита1Яйк го бЬока 7, на 4-ом- 2 3каналы, на - 3 какая и на 6-ом 1 и 3 каналы. П{Я1. -неисправном мйжоротариом блоке 7 устройство работает следующим о р&зом.. Щ)еддоложим, например, что имеется неисправность типа обрыв в 1-ом канале мажорита|рного блока 7. На втором такте шифратор 6 включает 1 и 2 канал мажоритарно1ч блока 7 и открьтает по одному из входов элементы И 8 первого и второго канала, а сигнала на выходе мажоритарного блока 7 нет. На выходе юмпаратора 2 появится сигнал ошибка, который через открывшиеся элементы t И 8 запишет по в пе{шый и второй счетчики 9 и .через элементы ИЛИЮ, ЗАПРЕТ 15, ИЛИ 13 и ЗАПРЕТ 16 снимет сигнал с выхода элемента НЕ 2, . одновременно поступая на вход элемента 19 задерж|си. Элемент И 3 закрывается по одному из. Екодов и сумматор 5 выдает сигнал на второй вход распределителя 4 импульсов, .который вновь переключится на первый канал, .рлее устройст во будет работать как на первом такте . работы. По истечении третьего такта четвертым тактовым .импульсом щифратор 6 вновь включит 1 и 2 канал мажоритарного блока и- начнется второй цикл проверки.ЕСли на выходе мажоритарного бяока 7 сигнал вновь будет отсутствовать, то второй сигнал ошибкис вызсода компаратора 2 через элементы И 8 первого и второго канала запишет еще по -Л. В первый и второй счетчики 9, на ъька/лщ который появится сигнал перепоонения. Данный сигнал через элементы ИЛИ 12 и 11 обнулит счетчики 9, одновременш записывая в счётчики 14 первого и второго каналов и по запрещающему входу элементы ЗАПРЕТ 15-17. , лы, появищшеся на выходах элемента ИЛИ Ю и элемента 19 задержки, будут блокированы, п оэтому следующим такто1вым импульсом генератора 1 6 включЕП для проверки канал мажо.рктарного блока 7, как при нормальной работе мажоритарного блока. Если же на втором цикле проверки мажоритарный блок выдаст сигнал исправности, то к концу 4-го такта сигнал с выхода элемента 19 задержки поступит на вход элемента 18 задержки н юрез открытый элемент ЗАПРЕТ 16 вновь закроет элемент И 3, переключая шифратор 6 вновь на первый канал мажоритарного блока. На пятом такте вновь будет проверяться 1 канал. По истечении 5-го такта шестым тактовым импульсом генерепора 1 шифратор 6 опять включит 1 и 2 канеирл и начнется третий цикл проверки мажоритарного блока 7. Если на данном цикле мажоритарный блок 7 вновь подтвердит свое исправное состояние, то появившийся к концу 6-го.такте импульс на выходе элемента 18 задержки через элемент ИЛИ 11 обнулит счетчик 9, а первый сигнал ошибки булет принят за сбой. .ЕСЛИ же иа третьем цикле проверки мажоритарный блок будет неисправен, то сигнал ошибки с выхода компаратора 2 через элементы И 8 и второго каналов запишет вторую , переполняя

счетчики 9 первого и второго каналов и })стройство будет работать вышеописанным образом.

При входной ком наоии, соответствук щей 6-му такту нормальной работы уст- 5 ройсгва.-Иогда будут проверяться 1 и 3 каналы мажоритарного блока, ситуация повторяется с той лишь разницей, что будут туткрыты по одному из заходов элементы И 3 первого и третьего каналов. Снг- нал неисправности с выхода компаратора 2 будет поступать на вкод первого и третьего счетчика 9, а к концу цикла проверки данной входной ком&тацпн вторая будет записана в счетчик 14

первого канала, и на его выходе появнтся сигнал .переполнения, указывающий номер неисправного канала мажоритарного блока 7. В двух других счетчиках 14 будет записано по . В том случае, если у .мажоритарной схемы неисправно более 1- канала;: то сигнал переполнения будет присутствовать на выходах всек трек счетчиков 14.

Таким , благодаря Введению новых элементов и логических связей удается повысить достоверность контроля мажоритарных блоков, исключив накопление сигналов свиибкн при разных входных ком надиях на входах блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля мажоритарных схем | 1983 |

|

SU1117643A1 |

| Устройство для контроля мажоритарных схем | 1977 |

|

SU705451A1 |

| СИСТЕМА СВЯЗИ | 2003 |

|

RU2249914C2 |

| Устройство для дистанционного контроля дуплексных стационарных радиостанций | 1986 |

|

SU1403384A1 |

| Устройство для диагностирования технических объектов | 1981 |

|

SU1070561A1 |

| Устройство телеконтроля объектов железнодорожной автоматики | 1985 |

|

SU1234267A1 |

| Диспетчерский полукомплект телемеханического устройства | 1975 |

|

SU556479A1 |

| Устройство для контроля состояния станций радиорелейной линии связи | 1977 |

|

SU743215A1 |

| Устройство для обнаружения поврежденного участка телеграфного тракта | 1981 |

|

SU1042194A2 |

| Устройство для приема и передачи цифровой информации | 1981 |

|

SU959131A1 |

УСТРОЙСТВО ДЛЯ КОНТРОЛЯ МАЖОРИТАРНЫХ ВЛОКОВ, .рДержйшее генератор тактовых импульсов, соединенный первым выхрдом с первым входом первого элемента И и первым входом cjTvDviaTopa по модулю два, второй вход которого соединен с в псодом первого элемента И и первым .входом реверсивного распределителя, а выход - с вторым Екодом реверсивного распределителя, выходы которого подключены к соответстьвующим входам шифратора выходы шифратора соединены с соответствующими входе ми мажоритарного блока, выход которого подключен к первому нходу компаратора, второй вход которого соединен с вторым выходом генератора тактовых импульсов, отличающееся тем, что, с целью повышения достоверности контроля, в него введены вторые элементы И, элементы ИЛИ, элементы ЗАПРЕТ, элементы задержки, элемент НЕ и первые и вторые счетчики,, суммируюшие входы первых счетчиков подключены к выходам соответствующих вторых элементов И и входам первого. элемента ИЛИ, выход которого подключен к входу, первого элемента ЗАПРЕТ, первые входы вторых элементов И подключены соответственно к первому, второму и третьему выходам шифратора, а вторые входь к выходу компаратора, выходы первых счетчиков подключены к суммирующим входам соответствукяцих вторых счетчиков и к входам второго элемента ИЛИ, выход которого соединен с первым вхо1Дрм третьего элемента ИЛИ и с запреi щаюшими входами первого, второго и (Л третьего элементов ЗАПРЕТ, выход первого элемента ЗАПРЕТ соединен с первым входом четвертого элемента ИЛИ н через первый элемент задержки - с входом третьего элемента ЗАПРЕТ и с вторым входом четвертого элемента ИЛИ, выход которого подключен к входу . второго элемента ЗАПРЕТ, выход которого соединен через элемент НЕ с вхоел дом первого элемента И, а выход тре00 тьего элемента ЗАПРЕТ через второй сх элемент задержки подключен к второму со входу третьего элемента ИЛИ, выход которого соединен с входами установки нуля первых счетчиков.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для контроля дискретных логических схем | 1973 |

|

SU451994A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для контроля мажоритарных схем | 1977 |

|

SU705451A1 |

Авторы

Даты

1983-04-30—Публикация

1981-12-23—Подача