(54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ДИСКРЕТНЫХ ЛОГИЧЕСКИХ СХЕМ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля дискретных блоков | 1977 |

|

SU746524A1 |

| Устройство для контроля логических блоков | 1978 |

|

SU723578A1 |

| Устройство для контроля цифровых узлов | 1982 |

|

SU1164711A1 |

| Устройство для контроля мажоритарных схем | 1983 |

|

SU1117643A1 |

| Устройство для автоматизированного контроля параметров реле | 1985 |

|

SU1265704A1 |

| Устройство для контроля логических схем | 1976 |

|

SU590743A1 |

| Устройство для контроля счетчиков импульсов | 1985 |

|

SU1248061A1 |

| Устройство сравнения | 1983 |

|

SU1171749A2 |

| Устройство для контроля логических схем | 1986 |

|

SU1383236A1 |

| Устройство для управления фотоколориметрическим газоанализатором | 1982 |

|

SU1092468A1 |

1

Изобретение относится к области вычислительной техники.

Известны устройства для контроля дискретных логических схем, содержащие двоичный счетчик, вход которого подклю- jBH к генератору импульсов, а присоединены ко входам разделительных схем выходы которых соединены с выходами устройства, триггер неисправности с индикаторными элементами на выходах и первым элементом И на нулевом входе, первый вход которого подключен через формирователь стробирующих импульсов к генератору импульсоэ а второй вход соединен с выходом первого элемента ИЛИ, подключенного первым входом к выходу компаратора, входы которого подключены ко входам устройства через схему контроля уровней и преобразователь уровней.

Известные устройства не позволяют обнаруживать неисправности замыкания входов проверяемой схемы, реализующей логическую функцию И.

В предложенном устройстве указанный недостаток устранен благодаря тому, что

оно содержит элемент ИЛИ-НЕ и вторрй элемент ИЛИ, входы которых соединены с выходами соответствующих разделительных схем, и второй элемент И, входы которого соединены с выходами второго элемента ИЛИ и элемента ИЛИ-НЕ, а выход подключен ко второму входу первого элемента ИЛИ.

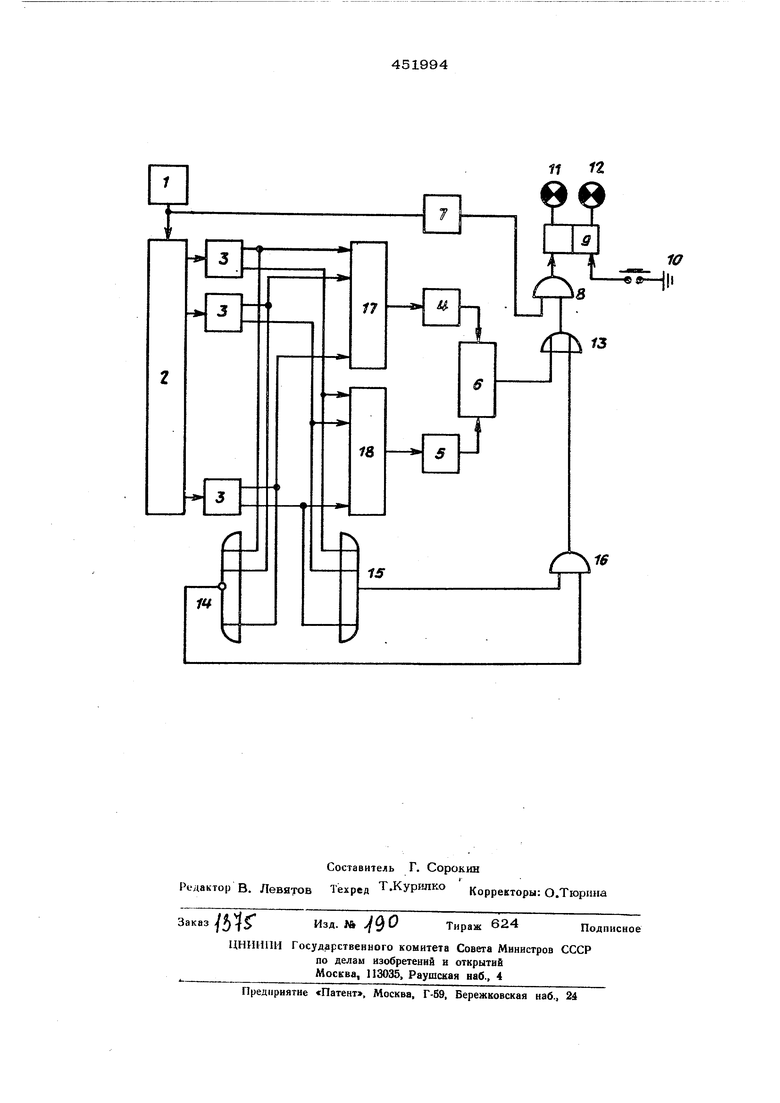

Блок-схема устройства для контроля дискретных логических схем приведена на чертеже.

Устройство содержит генератор импульсов 1, двоичный счетчик 2 с количеством разрядов, равным максимальному числу входов проверяемой логической схемы, разделительные схемы 3, схему контроля уровней 4, преобразователь уровней 5, компаратор б, формирователь стробирующих импульсов 7, элемент И 8, триггер неисправности 9, кнопку Пуск 10, индикаторные элеметы 11, 12 соответственно Исправно и Отказ, элемент ИЛИ

13, элемент ИЛИ-НЕ 14, элемент ИЛИ

15 и элемент И 16.

Устройство работает следующим образок.

При работе устройства используется принцип сравнения работы проверяемой схемы 17 и эталонной схемы 18 при всех возможных комбинациях входных сигналов. Если хотя бы при одной из входных комбинаций уровни напряжений на выходах схем 17, 18 не совпадают, это фиксируется включением индикаторного элемента Отказ 12ч В противном же случае (про- Веряемая схема 17 исправлена, и выходные уровни совпадают при всех входных комбинациях) будет включен индикаторный элемент исправлено 11 ,

Кнопкой Пусйк 10 триггер неисправ- ности 9 устанавливается в нулевое состояние; соответствующее зажиганию индикаторного элемента Исправлено Ц. Дво ичный счетчик 2 запускается от генератора импульсов 1.

Тестовые комбинации с двоичного счетчика 2 поступают на соответствующие входы схем 18 и 17 по отдельным шинам. Без Э1юго разделения устройство не обеспечит регистрацию даже такого типа не- исправности, как замыкание на землю одного из входов проверяемой схемы 17, поскольку в этом случае нормальная работа эталонных схем 18 будет невозможна.

Схема контроля уровней 4 определяет, находится ли выходное напряжение проверяемой схемы 17 в допустимых пределах, причем проверка осуществляе1х:;я как по низкому, -гак и по высокому уровню. Кроме юго, схема контроля уровней 4 осуществ- ляет согласование выхода проверяемой схемы J 7 с цифровым входом KOMuajjaTopa б. Для Э-1-ОЙ же пели чхэлько по отношению к эталонной схеме 18 служит преобразователь уровней 5. Компаратор G сравнивает вуяходные сигналы схем 18 и 17 и в случае их 1есовпадения в момент прихода стр бирующего импульса с формирователя стро- бирующих импульсов 7 опрокидывает триг- гер неиси|}гшиости 9 в состояние, соотвеа- ствук)|цие свечению индика горного элемента ЧХгказ 12.

Элементы 14, 15 и 16 предназначены для o6iiapy/KtMiHH отказов тина электрнче- f;KOiO з; ммкания мелшу логическими BXij Лс)Ми 11рове1)яемой схем1л 17. При проверки t:AeMbi, у К0п)рон два ИJИ1 6 ijiee входов элек 1|)иче1;ки Зс мкиуты между собой, некоторые luci-oBbie им 1ул11с;ов на н-Хгидах 17 и 18 не будут совпадать.

В эти моменты на выходе элемента И 1 появятся сигналы, которые через элементы 13 и8 приводят к срабатыванию триг гера неисправности 9.

При нажатии на кнопку Пуск 1О -фиггер неисправности 9 устанавливается в положение, соответствующее включению индикаторного элемента 1 Йсправно 11. Если проверяемая схема 17 исправлена, то триггер неисправности 9 будет оставаться в этом положении и после отпускания кнопки Пуск 10. Если проверяемая схема 17

неисправна при некоторых комбинациях сигналов, подаваемых на входы 17 и 18 от двоичного счетчика 2, выходные уровни обеих схем не будут совпадать, в результате чего в момент прихода стробирующе- го импульса (необходимого для устранения влияния переходных процессов на результат сравнения) триггер неисправности 9 перейдет в положение, при котором загорится индикаторный элемент Отказ 12, и останется в нем до следующего нажатия на кнопку Пуск 1О.

Предмет изобретения

Устройство для контроля дискретных логических схем, содержащее двоичный счетчик, вход которого подключен к генератору импульсов, а выходы присоединены ко входам разделительных схем, выходы которых соединены с выходами устройства, триггер неисправности с индикаторными элементами на выходах и первым элементом И на нулевом входе, первый входкоюрого подключен через формирователь стробирующих импульсов к генератору импульсов, а второй вход соединен с выходом первого элемента .ИЛИ, подключенного первым входом к выходу компаратора, входы коюрого подключены ко входам устройства через с:хему контроля уровней и преобразователь уровией, отличающ е е с и тем, что, с целью повышения надежности работы ус-фойства, оно содержит элемент ИЛИ-ПЕ и второй элемент ИЛИ , входы которых соединены с выходами соответсгвувчцих разделительных г;хем, а также второй элемент И, входы ко-гарого соединены с выходами второго элемента ИЛИ и элемента ИЛИ-ПЕ, а выход подключен ко второму входу первого элемента ИЛИ. , ff Г2 O ,,

Авторы

Даты

1974-11-30—Публикация

1973-05-08—Подача