Изобретение относится к измериг тельной технике и предназначено д|1Я обеспечения индикации формы, ypOBf ней, фазовых соотношений многока-i нальных сигналов. .j

Известна схема осциллографа с i матричным экраном. В этом устройстве входы X и У подключены через сортг ветствующие аналого-цифровые прео разователи (ЛЦП, схемы адресации к матричному экрану, в узлах шин : Ю которого находятся светоэлементы.i При подаче периодических сигналов| на X и У входы на экране высвечи.вается светящееся изображение IlDi

Однако в данном устройстве ин-| 15

дицироваться могут трлько периоди

ческие сигналы, однократные сигна|

лы на экране видны не будут, так j

как осциллограф не имеет памяти, i

Известна схема осциллографа с 20 матричным экраном и памятью, В | этом устройстве вход соединен через АЦП, схему адресации, память, вых4дйые каскады с горизонтальными ши- i нами матричного экрана. Блок синх-| 25 ронизации связан с входом устройст ва, ,а его выходы подключены к вхо-1 дам коммутатора, у которого выходь соединены с адресными входами памяти и через выходные каскады с вертикаль-ЗО ными 1иинами матричного экрана. В режиме записи входной сигнал череё АЦП и схему адресации записываете в память. Причем память содержит столько ячеек памяти, сколько узлов с находится на матричном экране. Эщ ячейки распределены по строкам и I . столбцам, при этом отдельная состМвляющая входного сигнала записыва- ется в соответствующий столбец паН мяти, возводя в состояние 1 ячей- О ку памяти j номер строки которой сс|ответствует. уровню входного сигнала. После записи входного сигнала pac-j положение ячеек памяти/ имеющих состояние 1, соответствует форме I 45 входного сигнала. В режиме индика-ции из памяти цоследовательно тываются по столбцам состояния яче1ек памяти, зажигая соответствующие ячейки матричного экрана, на котором 50 высвечивается форма входного сиг- ; ; нала Г2.3... ,

Недостатками этого устройства я|вяются большой объем памяти (число| чеек памяЕТи равно числу узлов матН „ ицы экрана), а также невозможност|ь ндикации многоканальной информаци

Известен осциллограф с матричный экраном, аналогичный описанному устойству, в который введены цифровы|е элементы, обеспбчивгиощиё полуавтом|а- 60. тическое измерение характеристик | сигнала например амплитуды и длир ельности временных интегралов {3Jj.

Данный осциллограф имеет недостатки I присущие устройству Г21. : 5

Наиболее близким к предлагаемому является матричный осциллограф, имеющий К входов, которые через усилители соединены с входами соответствующих К компараторов. Другие входы компараторов, соединены с входом цифро-аналогового преобразователя (ЦАП), а выходы через одновибраторы соединены с входами элемента ИЛИ, выход которого, в свою очередь, соединен с входами элементов И, расположенных в узлах матрицы экрана, у которых входы подключены к входам соответствующих триггеров. Выходы триггеров подключены к оветоэлементам. Кроме того, выход генератора или синхронизатора через счетчик подключен к входу ЦАП и входу дешифратора, выходы которого образуют WT горизонтальных шин матрицы экрана, нулевая шина соединена через элемент И с входом счетчика, выход которого подключен к входу другого дешифратора, выходы второго дешифратора образуют вертикальные шины матрицы экрана. Каждая шина подключна к другим входам триггеров, расположенных в соответствующем столбце матрицы экрана.

В режиме записи усиле.нные К входных сигналов сравниваются в компараторах с линейно возрастающим сигналом на выходе ЦАП. В моменты равенства одного из входных сигналов и сигнала ЦАП на выходе компаратора образуется перепад напряжения, запускающий одновибратор. Импульс одновибратора через элемент ИЛИ пОcdrynaeT на входы всех элементов И матрицы. Но проходит он только на один из этих элементов, который положен в точке пересечения шин матрицы, имеющих в данный моМент логические единицы. При этом триггер, подключенный на выходе данного элемента И, устанавливается в 1 и зажигает световой элемент. По вертиЧ кали данный световой элемент расположен на уровне, соответствующем со.стоянию счетчика, подключенного на вход ЦАП, т.е. на уровне, соответствующем входному сигналу. Ito гориэонтали световой элемент расположен на уровне, определяемом числом на выходе счетчика дешифратора ,верти-. каль.ных шин. Данное число возраста ет линейно во времени, поэтому по горизонтали место горящего светоэлемента соответствует данной временной координате входного сигнала. При равенстве уровней другого входного сигнала и сигнала на выходе ЦАП загорается другой световой элемент, расположенный вдоль выбранной вертикальной шины матрицы. Таким обра зом, К входных сигналов зажигают К световых элементов вдоль одной вертикальной шины. В следуюащй момент времени, когда чцсло на выходе счетчика.дешифратора вертикйльных шин возрастает на единицу, зажгутся световые элементы в следующей вертикальной шине и такДалее. После окончания процесса записи на экране матрицы горят световые элементы, .. описывающие в совокупности форму К входных сигналов. Это изображение хранится неограниченно долго, пока включено питание схем. По желанию процесс записи можно повторить, запустив в работу счетчик дешифратора вертикальных цшн 43.

Недостатком данного устройства является сложность матричного экрана, так как для матрицы и 100 требуются 10000 отдельных триггеров 10000 элементов И и 40000 подводящих к ним проводов. Кроме того, данное устройство не обеспечивает изменение скорости записи входных сигналов, т.е. временной масштаб изображения всегда постоянен.

, Причем данное устройство не имее возможности индицировать уровни вхоных сигналов и их фазовые соотнршеНИЯ.- . :: . - . . .;

Цель изобретения-упрОшение осциллографа и расширение области применения за счет обеспечения возможт ности осциллографирования уровней , входных сигналов и их фазовых соотношений. . .; . ; - ;; ;., , .

Поставденная цель достигается тем, что ВТ матричный/осциллограф, содержащий первый компаратор, выход которого соединён с первым входом ; триггера, последовательно соединенныв первый счетчик,:цифро-аналоговы преобразователь и второй кЬмпаратор выход второго счетчика соединен с входом первого одновйбратора, выход которого соединён со вторым . входом триггера, блок синхронизации входы первого компаратора являются первым и вторым входами осциллографа соответственно, вертикальные шины матричной панели которого соединены с выходами деойфратора, . вход которого соединен с выходом второго счетчика, второй рдновибратор, вход которого соединен с выхо.дом первого счетчика, соединенным с входом второго, счетчика, и детейторы, введены после довательно соединенные измеритель периода входного сигнала и делитель частота, два коммутатора, регистр, блок памяти и третий компаратор, выход которого соединен с информационным входснч регистра, тактовый вход которого соединен с выходом второго коммутатора, первый вход которого соединен с выходом делителя частоты, а второй вход - с первым выходом блока синхронизации, второй выход которого соединен с первым входом измерителя периода входного сигнала

а третий выход - со вторым входом делителя частоты, второй вход измерителя периода входного сигнала соединен с выходом первого компаратора, выход триггера соединен с четвертым входом второго коммутатора и-первым входом блока памяти, второй вход которого соединен с ВЕЛХОДОМ в-торого счетчика, третий вход - с выходом первого .счетчика, четвертый вход 0с выходом второго компаратора, выход блока памяти соединен с первым входом третьего компара тора, второй вход которого соединен с выходом первого счетчика, выход первого коммутатора соединен со вторым

5 входом второго компаратора, выход второго счетчика соегданен с первым входом первого коммутатора, второй и третий входы которого являются третьим и четвертым взводами осцил0лографа соответственно, четвертый вход первого коммутатора соединен со вторым входом цифро-аналогового преобразователя и входом блока синх.ронизации и является пятым входом

5 осциллографа, входаг одной группы первого коммутатора соединены свыходами детекторов, входы которых и входы другой группы первого коммутатора являются входами группы ос0циллографа.

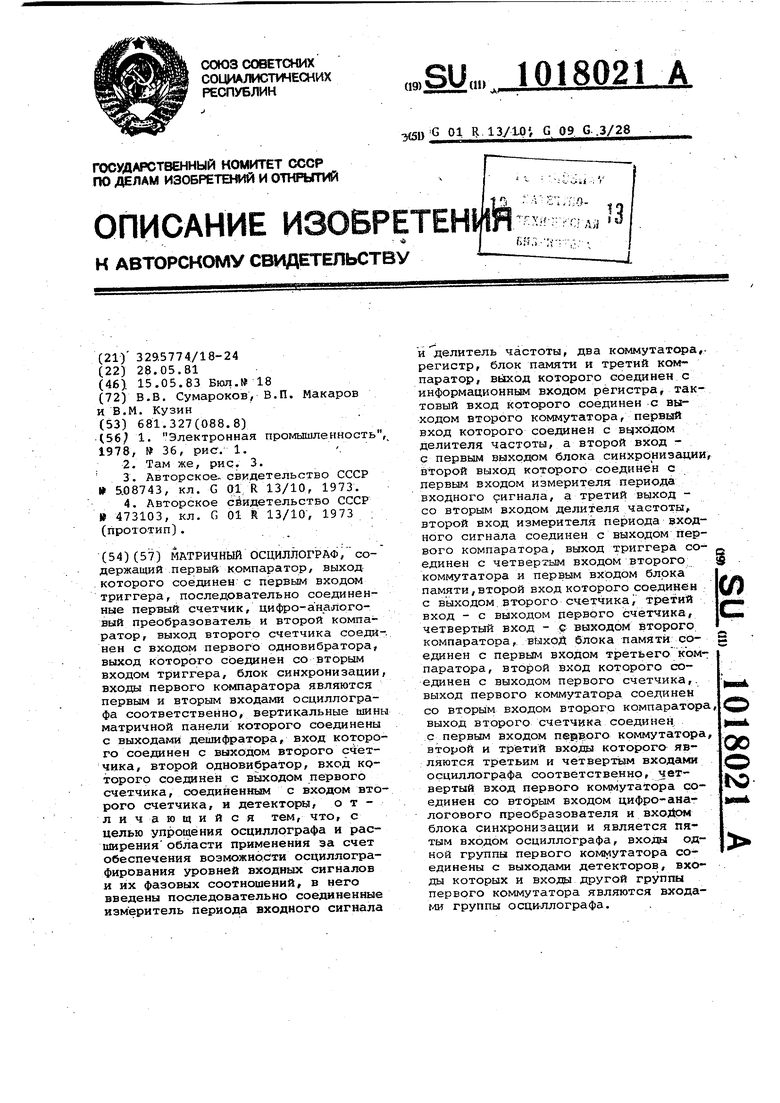

На чертеже представлен матричный осциллограф. .

Осциллсэграф содержит первый компаратор 1, второй компаратор .2, изиерительЗ.периода входного сигнала,

5 делитель 4. ч-астоты, триггер 5, блок б; синхронизации, первый и второй од. н6вибрато1 н 7,8, первый коммутатор 9, второй коммутатор 10, первцй и вто-рой счетчики 11, 12 соотвйетственно,

0 .детекторы 13, цифро-аналоговый пре- . образователь 14, блок памяти 15, третий компаратор 16, регистр 17, де.ип1фратор 18, элементы индикации матричной панели 19 горизонтальные

5 и ве ртикальные шины панели 20 и 21 соответственно, первый и второй вхо ды осциллографа 22 и 23, третий вход.осциллографа Номер формы 24, четвертый вход осциллографа Уровень/форма 25, пятый вход. Фаза

0 2ь, входы группы 27 осциллографа. Осциллограф работает следующим образом..

В режиме записи формы одного из входных сигналов,вход 25 коммутато5ра 9 устанавливается в положение форма, а на вход 24 Номер осциллографа подается сигнал,в ви дё кода, подключающий выбранный вход осциллографа через коммутатор

0 9 к входу компаратора 2. Одновременно на вход 23 осциллографа Опорный сигнал подается опорный сигнал. Этим сигналом может быть лю.бой из П входных сигналов осциллографа или любой внешний сигнал, относительно

5 которого необходимо произвести запись формы. Опорный сигнал сравнивается на входах компаратора 1 с постоянным сигналом и на выходе ком паратора 1 образуютсй прямоугольные импульсы, период которых равен периоду повторения опорного сигнала. Передний фронт одного из импульсов; устанавливает триггер 5 в состояние логической единицы, переведя ; блок памяти 15 в режим записи. Пе-: риод сигнала на выходе компаратораi 1 измеряет измеритель S, число с i его выхода подается на вход делител 4 частоты, в результате чего на выг ходе делителя 4 получаются сигналы;, которые имеют период в к.п. раз меньший периода опорного сигнала. ; Эти импульсы через коммутатор 10 поступают на вход счетчика 11. Сиг|нал выхбда счетчика преобразуется с помощью ЦАП 14 в аналоговый вид,; .затем он сравнивается с входным сигналом осциллографа на входах компаратора 2. В момент равенства обоих сигналов на выходе компаратора 2 образуется перепад напряжения,; который поступает на тактовый вход блока памяти 15. При этом в блок па мяти 15 записывается цифровое слойо с выхода счетчика 11, которое по значению равно уровню входного сигнала осциллографа. При достижении выходным сигналом счетчика 11 сво- его максимума, на его выходе образуется импульс, который увеличивает выходной сигнал счетчика 12 на единицу. Этот выходной сигнал изменяет адрес ячейки блока памяти 15, в которую затем записывается новое число, равное входному сигналу в следующий момент времени. В конце процесса записи в блоке памяти 15 оказываются записанными YfV слов, характеризующих выбранный входной сигнал осциллографа в течение целевого периода опорного сигнала. Если вход опорного сигнала соединен с выбранным входом осциллографа, то в памяти запишется информация о входном сигнале, начиная с; начала его периода и кончая его концом. В конце процесса записи на вЬходе счетчика 12 образуется импульс запускающий одновибратор 8, которЦй генерирует длительный импульс, сбрасывающий триггер 5 в ноль, прекращая тем самым, режим записи в блок паг мяти 15. После окончания импульса; одновибратора 8 триггер 5 остаетс|я в нулевом состоянии, пока компара;тор 1 в начале периода опорного сигнала не установит триггер 5 в состояни)е 1, и вновь начинается запись входного сигнала. В режиме индикации на выходе три гера 5 имеет место логический , который переводит блок памяти 15;в режим считывания, запрещает повторный запуск одновибратора 8 во время режима считывания, подключает на выход коммутатора 10 импульсы с другого выхода блока синхронизатора, имеющи,е постоянную частоту. При этом, эти импульсы запускают счетчик 11, с выхода которого сигнал поступает на вход цифрового компаратора 16, на другой вход которого поступает сигнал с выхода блока памяти 15, причем номер ячейки блока памяти определяет число на его адресном входе, которое образуется выходным сигналом счетчика 12. Первоначальное число это равно нулю, при этом на выходе блока памяти имеет место сигнал о начальной выборке запомненного сигнала. При возрастании от нуля выходного сигнала счетчика 11 на выходе компаратора 16 имеет место логическая единица, которая записывается последовательно в ячейки памяти регистра 17 в темпе поступления импульсов на его тактовый вход. Логическая единица записываемого сигнала поступает в верхнюю ячейку регистра 17, затем эта единица спускается в нижние ячейки. При превышении выходным сигналом счетчика 11 выходного сигнала блока памяти 15 на выходе компаратора 16 возникает логический ноль, который начинает записываться в регистр 17, начиная с его верхних ячеек. При заполнении счетчика 11 на его выходе появляется импульс, который запускает одновибратор 7, выходной сигнал которого закрывает коммутатор 10, в .результате чего счетчик 11 останавливается. Процесс считывания прерывается, а в регистре 17. остаются записанными логические единищл в Ешжних ячейках.. Число этих ячеек равно числу, находящегося на выходе блока памяти.15. Эти логические единицы возбуждают соответствующие горизонтальные шины 20 матрицы. В точках пересечения данных шин с одной возбужденной вертикальной шиной 21 загораются световые элементы. Номер возбужденной вертикальной Ьшны определяется числом на выходе счетчика 12, т.е. номером считываемой ячейки блока памяти 15. Горящие световые элементы образуют собой светящийся столб, равный по высоте цифровому слову, считываемому из блока памяти 15. Длительность выходного импульса одновибратора 7 значительно больше длительности процесса работы счетчика 11, поэтому глаз человека замечает на экране только постоянный по высоте светящийся столбец. После окончания импульса одновибратора 7 открывается коммутатор 10, запускается счетчик 11, задний фронт импульса на его выходе записывает в счетчик еще одну единицу, при этом на выходе блока памяти 15 появляется число из его следующей ячейки. Процесс считывания повторяется внов Частота считывания, информации из всего блока памяти 15 не должна быть ниже 50 Гц, чтобы изображение на экране матрицы не было мелькающим для глаза человека. Каждый горящий столбец матрицы возбуждается только на 1/п часть периода считывания всей информации из блока памя ти 15. Но из-за инерции глаз челове .oiir видит на экране совокупность горяв rf столбцов, форма которых описывае запоминающий входной сигнал осциллографа. . В режиме записи уровней Vt входны сигналов вход 25 коммутатора 9 уста навливается в положение уровень. При этом коммутатор 9 подключает н свой выход выходной сигнал одного из Biv детекторов 13, номер которого определяется числом на-выходе счетчика 12. В этом случае процесс записи информации аналогичен уже рписанному процессу записи формы сигнала. Отличие состоит только в том что в первую ячейку блока памяти 15 записывается сигнал с выхода первого детектора 13, во вторую ячейку блока памяти 15 записывается сигуал с выхода второго детектора 13и так далее. Так как постоянные .сигналы на выходах детекторов 13 пропорциональны,уровням (действую щим значениям или амплитудам) входных сигналов, то в памяти последовательно за время одного периода опорного сигнала Записываются уровни й-сех И входных сигналов. В режиме нХ индикации на -з.кране видны И светящихся . столбов, высота которых пррпорционсшьна уровням и входных -СИГНсШОВ. в режиме записи фазовых соотношений входных сигналов на вход 26 Фаза коммутатора: подается логическая единица. : При этом коммутатор-9 подключает на свой выход тот входной сигнал осциллографа, номер которого задается числом на выходе счетчика 12. Одновременно сигнал фаза устанавливает на выходе tIAn 14постоянный логический ноль и переводит блок 6 синхронизации в режим, в котором он подает на вход делителя 4 импульсы, частота которых в п. раз меньще частоты данных импульсбв в предыдущих режимах. В этом случае на выходе делителя 4 появляются за время одного периода опорного сигнала только К импульсов. Выбранный входной сигнал осциллографа сравнивается на входах компаратора 2 с нулевым сигналом, при этом на выходе компаратора появляются им-, пульсы. Причем, так как в режиме анализа фаз сигналов все входные сигналы И опорный сигнал должны иметь одинаковые периоды повторения, то в течение длительности, периода опорного сигнала на выходе компаратора 2 имеет место только один перепад из 1 в О. При равенстве фаз выбранного входного и опорного сигнала этот перепад имеет место в середине длительности периода опорно -о сигнала При несовпадении фаз перепад возни- - кает до или после середины периода опорного сигнала, -чем больше разница фаз, тем больше от середины возникает перепад сигн.ала на выходе компаратора 2. В этсм режиме за время длительности периода опорного сигнала на выходе счетчика 11 образуется лишь один возрастающий сигнал, поэтому в-момент в.озникновения перепада на выходе компаратора 2 в блок памяти 15 записывается одно число, величина которого пропорциональна длительности времени, прошедшего от начала перепада опорного. сигнала до момента наступления перепада на выходе компаратора 2. При подключении к следующему входному сигналу осциллографа в следующую ячейку памяти записывается новое число, характеризующее фазу данного входного сигнала, относительно опорного сигнала. При индикации записанной в блоке памяти 15 информации на экране видны п светящихся столбов, каждой столб при этом характеризует фазу одного из выходных сигналов. Причем при равенстве фаз всех входных и опорного сигналов столбы все одинаковые и занимаютпо высоте половину экрана. Если фазы отрицательные, то столбы располагаются по высоте ниже середины экрана, если фазы положительные, то - выше середины экрана. При сдвиге фаз +180 столбы занимают весь экран по высоте. Таким .образом, по сравнению с прототипом предлагаемый осциллограф имеет значительно упрощенный матричный экран и обеспечивает возможность осциллографирования не только форы, но и уровней всех входных сигналов и сдвиг фаз входнйх сигналов относительно опорного сигн .ла.

„

Ш

TffKm

20

J9

I

21

I

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для регистрации аналоговых сигналов | 1980 |

|

SU911577A1 |

| Матричный осциллограф | 1974 |

|

SU473103A1 |

| Устройство для отображения информации на экране электронно-лучевой трубки | 1980 |

|

SU938310A1 |

| Цифровой осциллограф | 1989 |

|

SU1626161A1 |

| Устройство для регистрации информации | 1982 |

|

SU1092537A1 |

| Осциллограф с матричным экраном | 1983 |

|

SU1129529A1 |

| Устройство для регистрации однократныхпРОцЕССОВ | 1978 |

|

SU842936A1 |

| Устройство для отображения информации на экране электронно-лучевой трубки | 1980 |

|

SU930361A1 |

| Устройство для управления считыванием и вводом информации | 1990 |

|

SU1751786A1 |

| Устройство для отображения информации на экране электронно-лучевой трубки | 1985 |

|

SU1354242A1 |

МАТРИЧНЫЙ ОСЦИЛЛОГРАФ,содержащий первый компаратор/ выход которого соединен с первьпи входом триггера, последовательно соединенные первый счетчик, цифро-аналоговый преобразователь и второй компаратор, выход второго счетчика соедй-. иен с входом первого одновибратора, выход которого соединен со вторым входом триггера, блок синхронизации, входы первого компаратора являются первым и вторым входами осциллографа соответственно, вертикальные шины матричной панели которого соединены с выходами дешифратора, вход которого соединен с выходом второго с4етчика, второй одновибратор, вход KQторого соединен с выходом первого счетчика, соедийенным с входом второго счетчика, и детекторы, отличающийся тем, что, с целью упрощения осциллографа и расширения области применения за счет обеспечения возможности осциллографирования уровней входных сигналов и их фазовых соотношений, в него введены последовательно соединенные измеритель периода входного сигнала и делитель частоты, два коммутатс а,. регистр, блок памяти и третий компаратор, вйход которого соединен с информационным входом регистра, тактовый вход которого соединен с выходом второго коммутатора, первый вход которого соединен с выходом делителя частоты, а второй вход О первым выходом блока синхронизации, второй выход которого соединен с лервыгл входом измерителя периода входного фигнала, а третий выход со вторым входом делителя частоты, второй вход измерителя периода входного сигнала соединен с выходом первого компаратора, выход триггера соединен с четвертым входом второго; коммутатора и первым входом блока (Л памяти, второй вход которого соединен с выходом.второго счетчика, третий с: вход - с выходом первого счетчика, четвертый вход - с выходом второго, компаратора, выхоД блока памяти соединен с первым входом третьего компаратора, второй вход которого соединен с выходом первого счетчика,, выход первого коммутатора соединен со вторым входом второго компаратора, выход второго счетчика соединен, с первым входом коммутатора, 00 о ю второй и третий входы которого являются третьим и четвертым входами осциллографа соответственно, четвертый вход первого коммутатора соединен со вторым входом цифро-аналогового преобразователя и входом блока синх ронизации и является пятым входом осциллографа, входы одной группы первого коммутатора соединены с выходами детекторов, входы которых и входы другой группы первого коммутатора являются входа lи группы осциллографа.

Авторы

Даты

1983-05-15—Публикация

1981-05-28—Подача