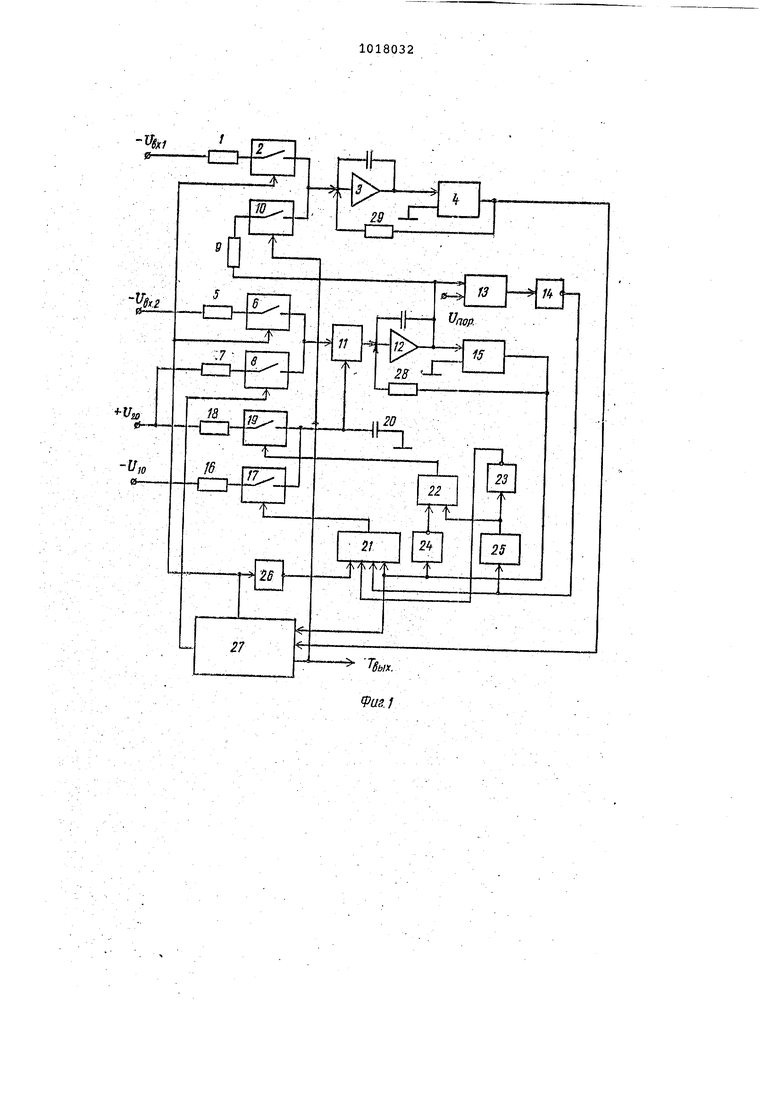

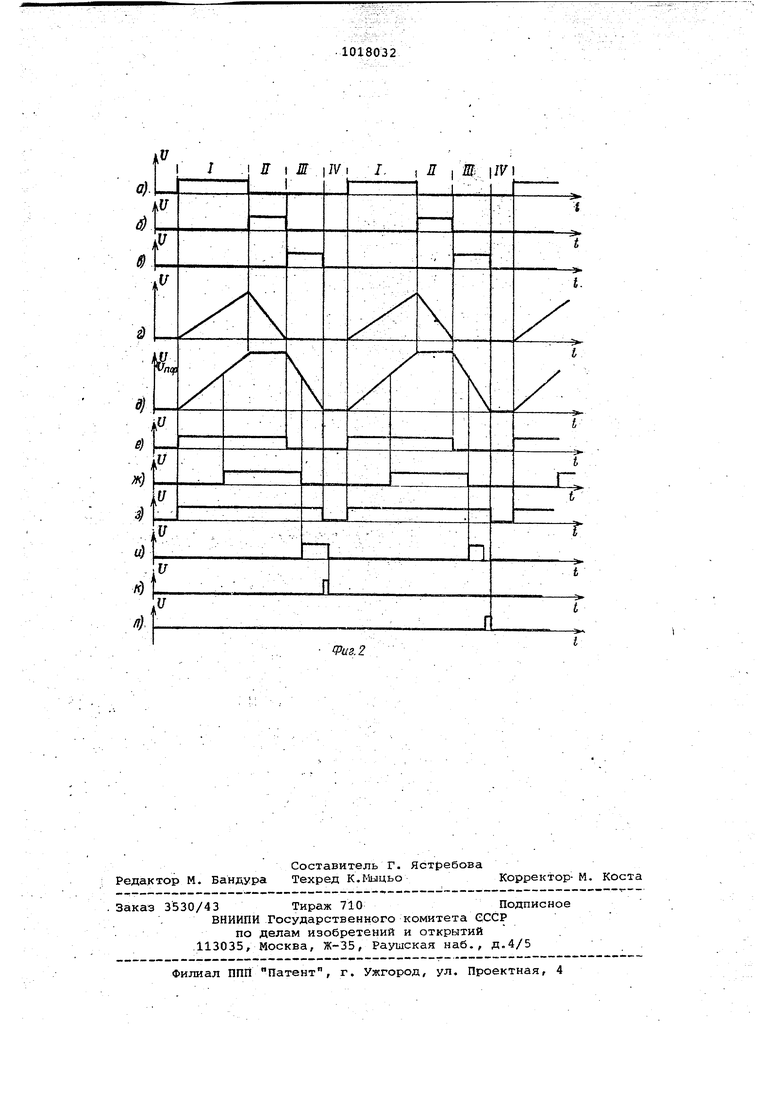

Изобретение относится к аналого.вой вычислительной технике и может быть использовано в измерительных и вычислительных системах для обработки аналоговой информации. Известно устройство для измерения отношения двух напряжений, содержащее преобразователь логарифма отношения двух напряжений в интервал времени, к выходу которого подключены формирователь экспоненциально-падающего напряжения и формирователь образцового интервала времени tl. Недостатком данного устройства я ляется его низкая помехозащищенност обусловленная воздействием помехи на входные напряжения, что приводит .к изменению времени, за которое экс поненциально-падающее напряжение из меняется от первою входного напряжения до второго. Наиболее близким по технической сущности к предлагаемому является устройство для измерения отношения двух напряжений, содержащее последовательно соединенные первый источ ник/входного напряжения, первый резистор, первый ключ, первый интегра тор, первый компаратор, выход которого подключен к блоку управления, также последовательно соединенные . вторсэй источник входного напряжения второй резистор, второй ключ, второ интегратор и третий ключ, четвертый и пятые ключи, подключенные между входом и выходом интеграторов, управляющие входы ключей подключены к выходам блока управления 23. Недостатком известного устройства является низkaя помехозащищен-; ность по второму входному напряжени Цель изобретения - повышение помехозащищенности устройства. Поставленная; цель достигается тем, ЧТОв устройство для измерения отношения двух напряжений, содержащее последовательно соединенные пер вый резистор, первый ключ, первый интегратор, первый нулю-орган и бло управления, первый выход которого подключен к управляю1«им входам перв го и второго ключей, вход второго ключа подключен к второму резистору второй интегратор, третий, четверты и пятый резисторы, третий, четверты и пятый ключи, конденсатор, оДна Обкладка которого подключена к выходу пятого ключа, а вторая - к общей шине, введены усилитель постоян него тока, седьмой и восьмой резисторы, шестой ключ, пороговый элемент, последовательно соединенные первый инвертор, формирователь образцового интервала, второй инвертор и первый Э7 емент И, последовательно соединенные второй нульог ан, третий инвертор и второй эле мент И, а также четвертый инвертор и два источника опорного напряжения, причем выход второго ключа через третий ключ и третий резистор подключен к первому источнику опорного напряжения, через усилитель постоянного тока и второй интегратор подключен к входам второго нуль-органа и порогового элемента, которью, подключены через четвертый резистор и четвертый ключ к входу первого интегратора, управляющий вход четвертого ключа подключен к второму выходу блока управления, третий выход которого подключен к управляющему входу третьего ключа, первый блока управления подключен через четвертый инвертор и второй вход первого элемента И к управляющему входу пятого ключа, вход которого через пятый рез.истор подключен к второму источнику опорного напряжения., .выход его подключен к управляющему входу усилителя постоянного тока, к первой обкладке конденсатора и через последовательно соединенные шестой ключ и шестой резистор к первому источнику опорного напряжения, управляющий вход шестого ключа подключен к выходу второго элемента И, другой вход которого подключен к выходу формирователя образцового интервала, вход которого подключен к третьему входу первого элемента И, четвертый вход кото- , рого подключен к второму входу блока управления и к входу третьего инвертора, при этом седьмой резистор подключен между выходом первого нульоргана и входом первого интегратора, а восьмой резистор подключен .между выходом второго, нуль-органа и входом второго интегратора. На фиг. 1 представлена блок-схе ма устройства для измерения отношения двух напряжений; на фиг. 2 временные диаграммы, поясняющие ра-. боту устройства. Устройство для измерения двух напряжений содержит первый резистор 1, первый ключ 2, первый интегратор 3, первый нуль-орган 4, второй резистор 5, второй ключ б, третий резистор 7, третий ключ 8, четвертый резистор 9, четвертый ключ 10, усилитель 11 постоянного тока, второй интегратор 12, пороговый элемент 13, Iпервыйинвертор 14, второй нуль-орган 15, пятый резистор 16, пятый ключ 17, шестой резистор 18, шестой ключ 19, конденсатор 20, первый и второй элементы И 21 и 22, второй и третий инверторы 23 и 24, формирователь 25 образцового интервала, четвертый инвертор 26, блок 27 управления, седьмой и восьмой резисто{ял 28 и 29. Работа устройства разбита на 4 такта. В первом такте блок 27 управлени включает ключи 2. и 6 на период сетевой помехи TO (см. фиг. 2а). При этом напряжение на интеграторах 3 и 12 растет (см, фиг. 2t и д} и в i. конце первого такта становится равным соответственно RiC% и,. i rQeUg,lL.T первое и второе входные напряжения. Во втором такте блок 27 размыкае ключи 2 .и 6 и замыкает ключ 10 (см. фиг. 2ff). Напряжение на интеграторе 3 начинает падать до нулевого значения (см. фиг. 21), Времй ли .нейного падения напряжения на интеграторе 3 ,,, определяет длительность второго такта и является выхо|1ной величиной устройства, оно оп рёделяется из соотношения иаТбы . (3) где .,R - сопротивления резисторов 1, 5, 9 соответственно, емкость конденсатора и теграторов 3 и 12 соот ветственно Из (3) получаем В третьем такте ключ 10 раз ; ыкаеТся (см. фиг. 2d), клнзч 8 замыкается (фиг. 2-8), и начинается линейгный разряд интегратора 12 до нулевого значения (см. фиг. 2d). В момент, когда напряжение на интеграторе 12 стает равно напряжению ОПОР срабатывает пороговыйэлемен 13(см. фиг. 2) и через инвертор 14запускает формирователь 25 (см, фиг. 2tt). Вели импульс с выхода формирователя 25 закончится раньше чем сработает нуль-орган 15 (котрры срабатывает в тот момент, когда нап ряжение на интеграторе 12 достигает нуля), то элемент И 21 включает клю 17, так как на четьфех входах элемента И 21 в этот момент будут единицы. Время., в течение которого включен ключ 17 (см. .фйг. 2А) - от момента окончания импульса с выхода формирователя: 25 до срабатывания «уль-органа 15. Если импульс с выхода фоЕ 1Ироватбмяя 25 закончится позже, чем сработает нуль-орган 15, то элемент И 22 на время между срабатыванием нуль. органа 15 и окончанием импульса на формирователе 25 включает ключ 19 (см. фиг. 2Ж).. При включении ключа 19 напряжение на конденсаторе 20 за счет тока, протекающего через резистор 18, меняется в одну ёторону, а при включении ключа 17 за счет тока, протекающего через резистор 16, - в другую. Полярность изменения напряжения на конденсаторе 20 в зависимости от устройства усилителя 11 должна быть выработана такой, чтобы это напряжение при заряде или .разряде то-ком через резисторы 16 и 18 способ-; ствовало уменьшению разности во времени между моментом окончания образцового интервала TQJM, и моментом срабатывания нуль-органа 15. После нескольких первых циклов, т.е. в установившемся режиме, коэффициент передачи усилителя 11 будет таким, что время уменьшения напряжения на выходе интегратора 12 от уровня и pop до нуля будет постоянным и равным TQPP. Для установившегося режима можно записатЬ: II UuoTospKv VnOp- ;р.-, где.UOQ- OTiophoe .напряжение; ., -- --- -- -- - коэффициент-передачи усилителя 11. IB четвертом такте все ключи .разомкнуты и выходы нуль-органов 4 (фиг. 26).и 15 (фиг. 25) подключены через резисторы 28 и 29 к входам интеграторов 3 и-12 для удержания выходного напряжения их на нулевом уровне. Из выражения (5) получаем Kv Un6pR7 Сх UooTn -: -ъ «- acposf Подставляя (б) в (2), получаем Ц пор т Л 5 . .- . Подставляя значения из (1) и (7) Б (4), получим выражение для выходного .ин т ервала. Ubx R.sR9Ui.oTo6i . (j...ft о-и v8) втиа -iRTUno Учитывая, что R-i , R, R-,, R osp постоянные величины, которые могут быть постоянными с высокой точностью, получаем, т V . . т.е. выходной интервал времени пропорционален отношению двух входных напряжений и не зависит от емкости интегрирующих конденсаторов,- кото|ж в являются наиболее нестабильными ве-; личиними в устройстве. Кроме того, выходная величина не зависит от периода помехи TQ.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для преобразования физической величины в код | 1987 |

|

SU1481691A1 |

| Устройство для измерения отклонения сопротивления от заданного значения | 1986 |

|

SU1536322A1 |

| Цифровой измеритель температуры | 1988 |

|

SU1560987A1 |

| Аналого-цифровой преобразователь интегральных характеристик электрических величин | 1981 |

|

SU1035790A1 |

| Цифровой измеритель температуры | 1988 |

|

SU1569590A1 |

| Устройство для измерения отношения двух напряжений | 1982 |

|

SU1099287A1 |

| Преобразователь толщины в интервал времени | 1986 |

|

SU1392345A2 |

| Цифровой измеритель температуры | 1985 |

|

SU1303849A1 |

| Интегрирующий аналого-цифровой преобразователь с автоматической коррекцией погрешности | 1984 |

|

SU1334372A1 |

| Электронный измеритель массы | 1990 |

|

SU1753290A1 |

УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ОТНОШЕНИЯ ДВУХ НАПРЯЖЕНИЙ, содержа- . . вдее последовательно.соединенные первый резистор, первый ключ, первый интегратор, первый нуль-Морган и блок управления, первый выход которого подк/по-лен к управляющим входам первого и второго ключей, вход второго ключа подключен к второму резистору, второй интегратор, третий четвертый И: пятый резисторы, третий, четвертый и пятый ключи, конденсатор, одна обкладка которого подключена к , : выходу пя.тогб ключа, г а вторая - к об1дей шине, о т л и ч а ю щ е е с я тем. Что, с целью повышения помехрзащивдейности, введены усилитель по.ст.оянного тока, седьмой и восьмой резисторы, шестой кЛюч, пороговый элемент, последовательно соединенные : первый инвертор,.формирователь образцового интервала, вторрй инвертор и первый элемент и, последовательно соединенные второй нуль-орган, третий инвертор и второй элемент И, а также четвертой инвертор и два источника опорного напряжения, причем выход второго ключа через третий ключ и третий резистор подключен к первому источнику опорного напряжения, через усилитель постояннрго тсэка и второй интегратор подключен к входам второго нуль-органа и порого-. вого элемента, которые прдтслючены через четвертый резистор и че Твертый ключ к входу первого интегратора, ;; управляющий вход четвертого ключа подключен.к второму выходу блока управления, третий выход которого подг ключей к управляющему входу третьек го ключа, первый выход блока управления подключен через .четвертый инв;ер- . тор и второй вход первого.: элемента И:S к управляющему входу пятого; ключа-, W вход которого через пятый pe;SHGTop подключен к второму источнику опорного напряжения, выход его подключен к управляющему входу усилителя постоянного тока, к первой обкла,цкё кон-S денсатора и через последов.ательнб соединенные шестой ключ и шестой резистор к первому источнику опорногонапряжения, управ.ляк)щий вход шестого ключа подключен к выходу второго злел мен Та И, другой вход которрго под- . GO ключе к выходу формирователя об- : разцового интервала, вход котбррго ;: -подключен к третьему входу первого СлЭ 51лемента И, четвертый вхрд кртЬрого подключен к второму-входу бло-IsD ка управления и к входу третьего ин. верхора, при этом седьмой резиртор подключен между выходом первого нульоргана и входом первого Интегратора, а восьмой резистор подключен между / выходом второго нуль-органа и. входом второго интегратора.

Авторы

Даты

1983-05-15—Публикация

1980-08-12—Подача