третий и четвертый токоограничивающие элементы 7-10, вьшолненные в виде резисторов, интегратор 11, нуль-орган 12, цифроаналоговые преобразователи (ЦАП) 13 и 14 калибровки и установки нуля соответственно, блок 1.5 согласования уровней напряжения, блок 16 управления, счетчик 17, вычитающий блок 18, вькодную пшну 19 и входную шину 20 калибровочной константы. Поставленная цель достигается за счет

1

Изобретение относится к измерительной технике и может быть использовано при проектировании измерительных информационных систем и автоматических измерительных приборов.

Цель изобретения - повьшение быстродействия.

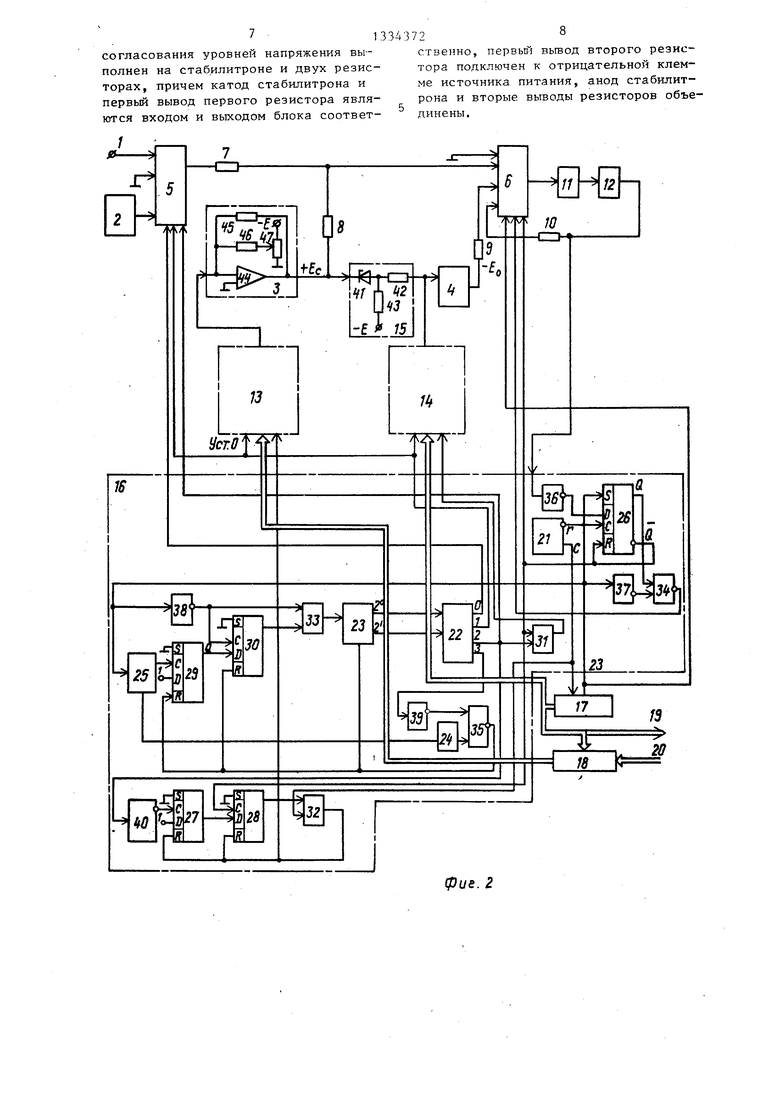

На фиГу1 приведена блок-схема пре- образова 1:еля; на фиг. 2 - один из воз- .можных вариантов реализации; на фиг.3 временная диаграмма его работы.

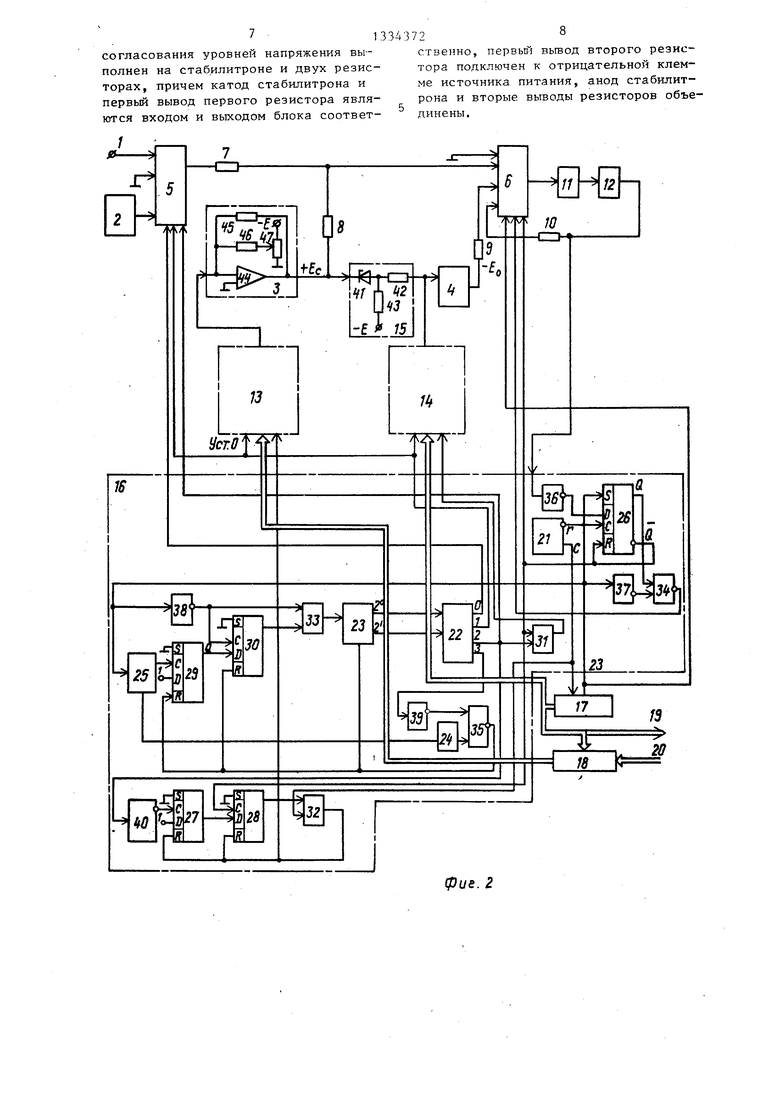

Преобразователь содержит (фиг.1) входную информационную шину 1, источник 2 калибровочного напряжения, источник 3 напряжения смещения Нуля, источник 4 опорного напряжения, первьй и второй коммутаторы 5 и 6, первьй, второй, третий и четвертый токоограничивающие элементы 7-10, выполненные в виде резисторов, интегратор 11, нуль-орган 12, ЦАП 13 и 14 калибровки и установки нуля соответственно, блок .15 согла сования уровней напряжения, блок 16 управленияg счетчик 17, вычитающий блок 18, выходную шину 19 и входную шину 20 калибровочной константы.

Блок 16 управления содержит (фиг.2) генератор 21 тактовых импульсов, дешифратор 22, делитель 23 частоты, блок 24 сброса, счетчик 25 периода коррекции, D-триггеры 26-30, элементы И 31-33, элементы И-НЕ 34 и 35 и ин- верторы 36-40.

. Блок 15 согласования уровней напряжения содержит (фиг.2) стабилитрон 41 и резисторы 42 и 43,

выполняемых автоматически операций установки нуля шкалы преобразователя путем изменения уровня опорного напряжения, калибровки (коррекции наклона характеристики) преобразователя путем изменения уровня выходного напряжения источника смещения нуля и следующей за операцией калибровки установки нуля при помощи блока согласования уровней напряжения указанных источников. 2 з.п. ф-лы, 3 ил.

о

5

Источник 3 напряжения (фиг.2) смещения нуля содержит операционный усилитель 44 и резисторы 45-47.

Преобразователь работает следующим образом.

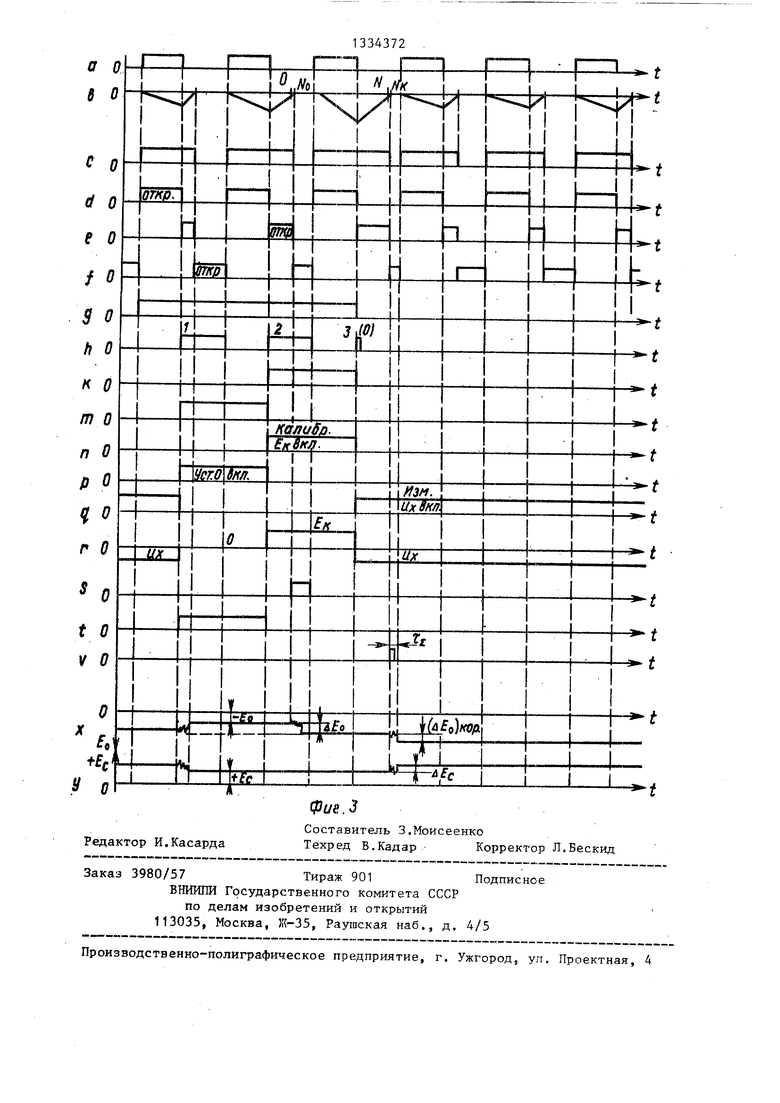

Инициирование процесса автоматической коррекции погрешности АЦП производится по сигналу (фиг.3§), формируемому на вькоде D-триггера 29 блока 16 управления. Период этого сигнала равен промежутку времени между двумя следующими друг за другом процессами автоматической коррекции погрешности. В блоке 16 при этом формируются три последовательных импульса (фиг.ЗЬ).

После воздействия первого импульса установки нуля (фиг.Зр) устанавливав ется нулевой потенциал на выходной шине коммутатора 5 (фиг.Зг). Одновременно начинается формирование сигнала (фиг,3t) для установки ЦАП 13 и 14 (фиг.2) в начальное (нулевое) состояние. При этом выходные сигналы источников 3 и 4 напряжения устанавливаются в начальное состояние: потенциалы + EJ, , -ЕО соответственно.

Затем производится преобразование нулевого входного аналогового сигнала в .соответствующий ему цифровой эквивалент NO (фиг.ЗЬ) в счетчике 17 с учетом знака смещения нуля АЦП, кото- рьй заносится в ЦАП 14 по импульсу, формируемому на выходе элемента И 31 (фиг.3s).

После этого ha выходе источника 4 устанавливается напряжение, измененное на величину ЛЕд, пропорциональную N в соответствии со знаком N,,. При положительном знаке выходной уровень Е источника 4 увеличится по модулю на величину дЕ. При этом скорость изменения выходного сигнала интегратора 11 во втором такте интегрирования увеличивается на величину, компенсирующую смещение N характеристики аналого-цифрового преобразователя.

После окончания первого такта интегрирования при нулевом входном сигнале АЦП на выходе коммутатора 5 устанавливается калибровочный сигнал (фиг.Зп). Смена сос тояния коммутатора 5 происходит при воздействии второго импульса (фиг.ЗЬ). Производится преобразование калибровочного сигнала в соответствующий цифровой эквивалент N (фиг.ЗЬ). Разность , полученная на выходе вычитающего блока 18 (фиг,2), заносится в ЦАП 13 по сигналу с вькода элемента И 32 (фиг.2v). Промежуток времени между моментом срабатьшания триггера 26 и ближайшим следукицим положительным фронтом импульса после срабатьшания триггера, переключающим счетчиком 17 необходим для формирования разности NK,-N, где N - калибровочная точка прибора (константа на входной шине 20), а N результат преобразования калибровочного сигнала. Если, например, (, то на выходе вычитающего блока 18 устанавливается положительное число, которое заносится в ЦАП 13. В Данном случае выходной уровень + Е. источника 3 увеличивается на величину д ЕС, (фиг.ЗУ). Скорость изменения выходного сигнала интегратора 11 в первом такте интегрирования при нулевом входном сигнале увеличивается на величину, компенсирующую мультипликативную погрешность преобразования. При этом нулевое смещение, установленное в цикле коррекции аддитивной погрешности (установка нуля), становится положительным и равным AN. Для автоматической компенсации этого смещения служит блок 15 согласования уровней напряжения, которьш определяет знак и величину изменения выходного напряжения источника 4 в зависимости от изменения выходного напряжения источника 3. Это происходит следующим образом.

В момент времени начала действия импульса записи в ЦАП 13 (фиг.ЗУ) изменение выходного напряжения источника 3 (EJ. на фиг.ЗУ) передается на

выход источника 4 с соответствующим коэффициентом передачи, что приводит к изменению его выходного напряжения на величину (iiE) коррекции (фиг.Зх), компенсирующую смещение uN. Таким образом, введение в преобразователь блока 15, новых связей позволяет осуществить автоматическую коррекцию погрешности за два измерительных цикла АЦП: первый цикл - установка нуля, второй цикл - калибровка с коррекцией установки нуля без использования измерительного цикла.

15

Формула изобретения 1. Интегрируюш й аналого-цифровой преобразователь с автоматической коррекцией погрешности, содержащий цифроаналоговый преобразователь калибровки и цифроаналоговьй преобразователь установки нуля, информационные- входы которых подключены соответственно к выходам вычитающего блока и

счетчика, первый коммутатор, первый информационный вход которого является ВХОДНОЙ информадионной шиной, а второй информационный вход подключен к выходу источника калибровочного нап ряжения, последовательно соединенные второй коммутатор, интегратор и нуль- орган, выход которого соединен с первым входом блока управления, первьй токоограничивающий элемент, вьтолнен- ный в виде резистора, первьй вывод которого подключен к первому информационному входу второго коммутатора, отличающийся тем, что, с целью повьш1ения быстродействия, в него введены последовательно соединенные источник напряжения смещения нуля, блок согласования уровней напряжения и источник опорного напряжения , а также три токрограничива.ющих .элемента, выполненных в виде резистора каждьм, причем первьй управляющий вход первого коммутатора и установочные входы цифроаналогового преобразователя калибровки и цифроаналогового преобразователя установки нуля объединены и подключены к первому выходу блока управления, второй и третий выходы которого соединены с управляющими входами цифроаналогового преобра-

зователя калибровки и цифроаналогового преобразователя установки нуля соответственно, четвертый и пятый выходы подключены к второму и третьему управляющим входам первого коммутато

51334372®

pa, третий информационный вход кото- вторьпуг входами дешифратора, первый рого объединен с вторым информацион- и второй выходы которого являются ным входом второго коммутатора и под- четвертым и первым выходами блока

. ключен к шине нулевого потенциала а управления соответственно, третий вы- выход подключен к второму выводу пер ход через первый инвертор соединен вого резистора, первьй вьшод которого с вторым входом первого элемента И, через второй резистор подключен к вхо- а четвертьй выход является пятым вы- ду блока согласования уровней напря- ходом блока управления и соединен с жения, шестой и седьмой выходы блока ю первым входом второго элемента И и управления соединены соответственно через второй инвертор - с С-входом с первым и вторым управляняцими входа- третьего D-триггера, S- и D-входы коми второго коммутатора, третий инфор- торого подключены к шинам нулевого мационньй вход которого через третий . и единичного потенциалов соответст- резистор подключен к выходу источника 15 венно, а выход соединен с D-входом опорного напряжения, четвертьй инфор- четвертого D-триггера, S-вход которо- мационный вход через четвертый резис- го подключен к шине нулевого потенци- тор подключен к выходу нуль-органа, ала, R-вход объединен с R-входом тре- восьмой выход блока управления подл , тьего D-триггера и подключен к выходу

ключен к счетному входу счетчика, вы- 20 третьего элемента И, который является ход переполнения которого соединен с вторым выходом блока управления, вы- третьим управляюш;им входом второго ход четвертого В триггера подключен коммутатора и с вторым входом блока к первому входу третьего элемента И, управления, а вмходы являются вьрсод- а С-вход объединен с вторым входом ной шиной, преобразователя и соединены 25 второго элемента И, R-входом пятого соответственно с первыми входами вы- D-триггера и подключен .к его инверс- читающего блока, вторые входы которо- ному выходу,- который является седьмым го являются входной шиной калибровоч- выходом блока управления, первый вход ной константы, выходы цифроаналогово- блока управления через третий инвер- го преобразователя калибровки и циф- зО ОР подключен к D-входу пятого. D- роаналогс вого преобразователя уста- триггера, прямой выход которого сое- новки нуля соединены с входами источ- динен с первым входом второго элемен- ника напряжения смещения нуля и исто- та И-НЕ, а С-вход соединен с инверс- чника опорного напряжения соответст- - ным выходом генератора тактовых им- венно. пульсов, прямой выход которого соеди 2. Преобразователь по п.1, о т - «е« вторым входом третьего элемента л и ч а ю щ и и с я тем, что блок . « является восьмым выходом блока управления содержит генератор такто управления, второй вход блока управ- вых импульсов, счетчик периода кор- ления соединен с S-входом пятого D- рекции, делитель частоты, дешифратор. 40 ° счетным входом счетчика пять П-триггеров, три элемента И, два периода коррекции, через четвертьй элемента И-НЕ, пять инверторов и блок инвертор - с вторым входом второго сброса, вьтолненный на резисторе, элемента И-НЕ, а через пятьй инвер- конденсаторе и инверторе, выход кото- - с первым входом первого злемен- рого соединен с вход ом. сброса счетчи- 45 С-входом второго D-тригге- ка периода коррекции, первые вьгооды . Р ькод которого соединен с вторым резистора и конденсатора и вход ин- входом первого элементам, S-вход объ- вертора объединены, а вторые выводы единен с S-входом первого D-триггера резистора и конденсатора подключены « подключен к. шине нулевого потенциа- к шинам единичного и нулевого потен- кп D-вход соединен с выходом пер- циалов соответственно, а первьй вьшод ° В--триггера,. D-вход которого под.резистора подключен к первому входу лючен к шине едини чного потенциала, первого злемента И-НЕ, выход которо- -вход - к выходу счетчика периода го соединен с R-входами первого и коррекции, выход второго элемента второго D-триггеров и входом сброса 55 является шестым выходом блока делителя частоты, счетный вход кото- управления, выход второго элемента И яв- рого соединен с выходом ..первого эле- ляется третьим выход ом блока управления мента И, а первый и второй выходы со- 3, 1реобразовате:7ь по п,1, о т - единены соответственно с первым и личающийся тем, что блок

согласования уровней напряжения выполнен на стабилитроне и двух резисторах, причем катод стабилитрона и первый вывод первого резистора являются входом и выходом блока соответственно, первый вьгаод второго резистора подключен к отрицательной клемме источника питания, анод стабилитрона и вторые выводы резисторов объединены.

фие. 2

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство преобразования сигнала с датчика | 1989 |

|

SU1651364A1 |

| КАЛИБРОВОЧНОЕ УСТРОЙСТВО ДЛЯ УЛЬТРАЗВУКОВОГО РАСХОДОМЕРА | 1995 |

|

RU2082951C1 |

| ОПЕРАТИВНЫЙ КОНТРОЛЛЕР СУММАРНОЙ МОЩНОСТИ НАГРУЗКИ ГРУППЫ ЭНЕРГОПОТРЕБИТЕЛЕЙ | 1998 |

|

RU2145717C1 |

| Устройство для измерения температуры | 1985 |

|

SU1332160A1 |

| Логарифмический аналого-цифровой преобразователь | 1987 |

|

SU1481803A1 |

| Цифроаналоговый преобразователь с автокалибровкой | 1986 |

|

SU1361720A1 |

| Многоканальный цифроаналоговый преобразователь | 1984 |

|

SU1269269A1 |

| УЛЬТРАЗВУКОВОЙ РАСХОДОМЕР | 2002 |

|

RU2210062C1 |

| Цифроаналоговый генератор телевизионного сигнала | 1989 |

|

SU1654978A1 |

| Преобразователь сигнала тензомоста в интервал времени | 1987 |

|

SU1580260A1 |

Изобретение относится к измерительной технике и может быть использовано при проектировании измерительных информационных систем и автоматических, измерительных приборов. Цель изобретения - повьшение быстродействия. Преобразователь содержит входную информационную шину 1, источник 2 калибровочного напряжения, источник 3 напряжения смещения нуля, источник 4 опорного напряжения, первый и второй коммутаторы 5 и 6, первый, второй. i СЛ

| Стенд для гидродинамических исследований движителей типа машущее крыло | 1986 |

|

SU1444628A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Реферативная информация о законченных научно-исследовательских работах в вузах Украинской ССР: Радиоэлектроника, автоматика и связь | |||

| Вьт | |||

| IX, 1976, с | |||

| Веникодробильный станок | 1921 |

|

SU53A1 |

Авторы

Даты

1987-08-30—Публикация

1984-08-27—Подача