Изобретение относится к измерению характеристик случайных процессов и предназначено для определения корреляционной функции текущего стационарного случайного процесса в реальном масштабе времени.

Известен цифровой коррелятор, содержащий компараторы, регистр, блоки умножения,, интеграторы l1.

Однако построенный по принципу знакового коррелятора аналог не обладает добтаточно высокой точностью.Наиболее близким к предлагаемому уст1Х)йству является коррелятор параллельного действия, содержащий входной блок памяти на Ум ячеек, блоков умножения, сумматоров, два аналого-цифровых преобразователя, генератор импульсов. Первым входом устройства является . первый вход первого аналого-цифрового преобразователя (АЦП), выход которого параллельно подключен к первым .входам блоков умножения. К вторым

. входам блоков умножения подключены выходы соответствующих ячеек входного блока памяти. Второй вход устройства последовательно подключен к первому вход)г второго АЦП, первому входу вход ноге блока памяти, второй вход которого объединен с вторыми входами АЦП и подключен к выходу генератора импульсов. Выходы блоков умножения подключены через соответствующие сумматоры к соответствующим выходам устройст- .,

Недостатком известного коррелятора является малое быстродействие.

15

Целью изобретения является увеличение быстродействия.

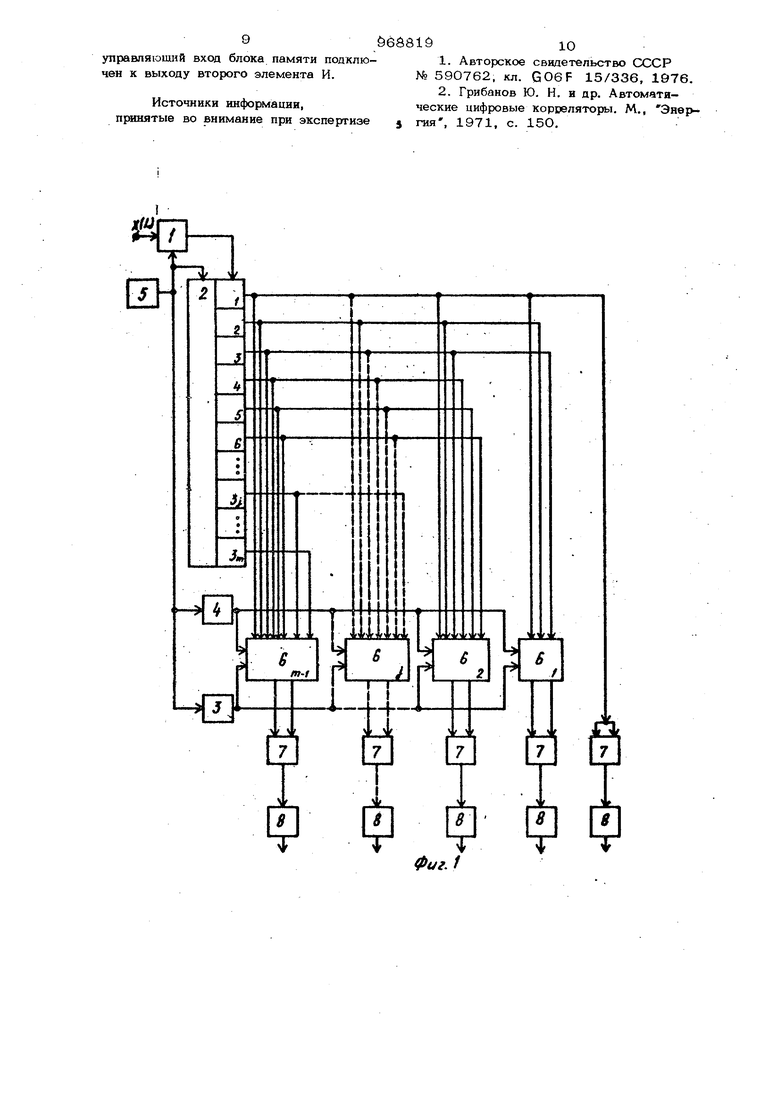

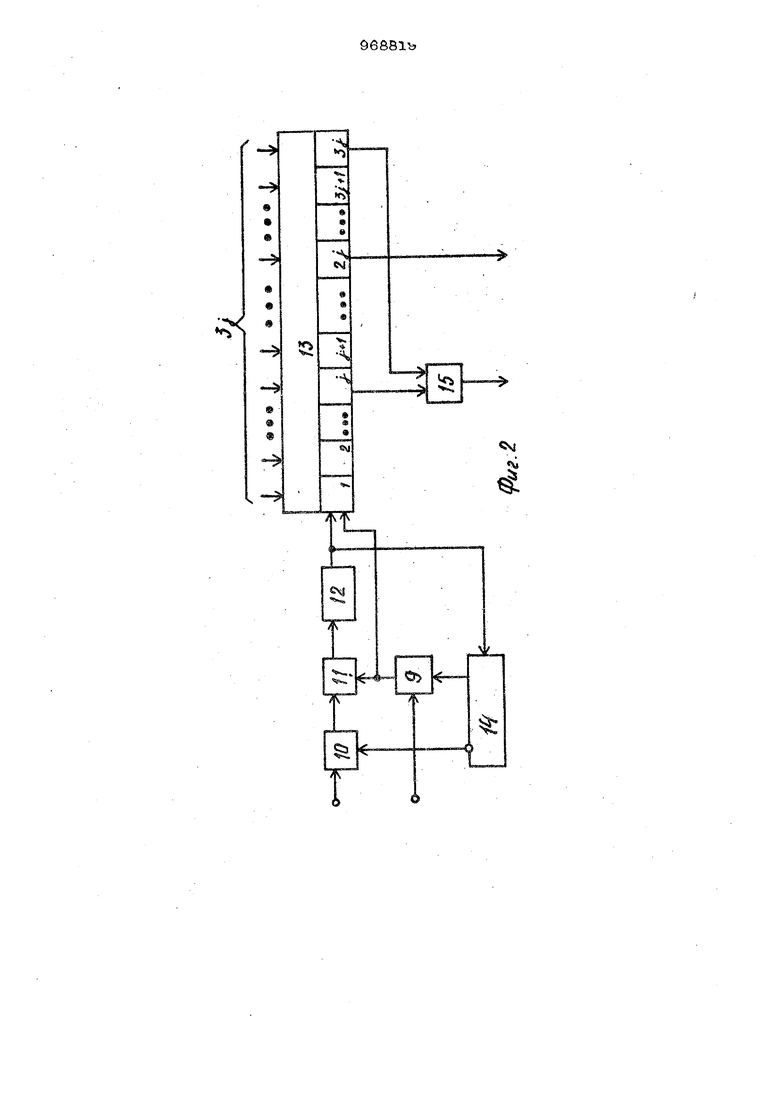

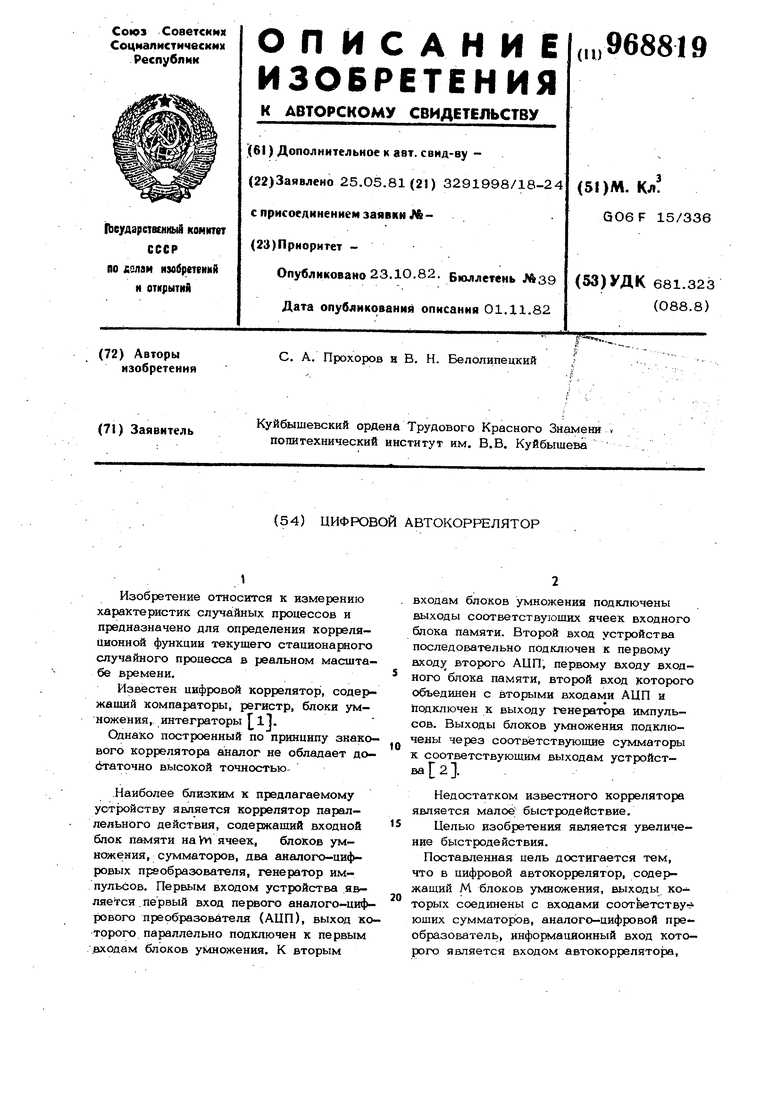

Поставленная цель достигается тем, что в цифровой автокоррелятор, соде1 жащий .М блоков умножения, выходы ко20торых соединены с входами соответствую, юших сумматоров, аналого-цифровой преобразователь, информационный вход которого является входом автокоррелято за. a выход соединен с информационным входом блока памяти, управляюише входы аналого-цифрового преобразователя и блока памяти объединены и подключены к вы ходу генератора импульсов, введены блок формирования сомножителей, делител частоты на два и на три, входы которых объединены и подключены к выходу генератора импульсов, выходы делителей подключены соответственно к первому и второму управляющим входам блоков формирования сомножителей, первый и второй выходы которых подключены соответственно к первому и второму входам соответствующего блока умножения, 3; , 1, 2, ..., М-1 информационных входов каждого блока формирования сомножителей соединены с выходами соответствующих ячеек блока памяти, выход первой на которых соединен с двумя входами первого блока умножения. Кроме того, j -и блок формирования сомножителей содержит элемент ИЛИ, счетчик, триггер, сумматор, блок памяти с 3J -ячейками и два элемента И, входы которого являются соответственно першым и вторым управляющими входами блока формирования сомножителей, выходами ко торого являются соответственно выходы сумматора и 2.J -и ячейки блока памяти, первый и второй выходы триггера подключены к вторым входам соответствующих элементов И, выходы которых соединены с соответствующими входами элемента ИЛИ, выход которого подключен к входу счетчика, выход которого соединен с входом триггера и первым управляющим входом блока памяти, информационные входы которого являются инфсфма- ционным входом блока формирования сомножителей, второй управляющий вход.блоica памяти подключен к выходу второго элемента И. На фиг. 1 представлена структурная электрическая схема цифрового автокоррелятора; на фиг. 2 - структурная схема j -го блока формирования сомножителей; на фиг. 3 - таблица соответствия содержимого входного блока памяти. Вход устройства последовательно подключен к первому входу аналого-цифрового преобразователя 1 и первому входу входного блока 2 памяти, второй вход которого объединен с вторым входом аналого-цифрового преобразователя 1 и делителей 3 и 4 частоть соответственно на два и на три и подключен к выходу 1 нератора 5 импульсов. 3) информацион969 ных входов каждого j-того блока 6 формирования сомножителей ( j 1, 2, ..., М- 1) подключеныК выходам соответствующих ячеек входного блока 2 памяти, начийая с первой. Первый и второй управляющие входы блоков 6 формирования сомножителей соответственно объединеныи подключены к выходам делителей частоты соответственно на два 3 и на три 4. Первый и второй выходы блоков 6 формирования подключены соответственно к первому и второму входам соответствующего блока 7 умножения, начиная с второго блока 7 умножения, которых через соответствующее сумматоры 8 подключены к соответствующим выходам устройства. На фиг. 2 представлена структурная электрическая схема j-того блока 6 формирования сомножителей. Первым и вторым входами j -того блока 6 формирования являются первые входы соответственно первого и второго логических элементов И 9 и 10. Выход второго логического элемента И 1О последовательно подключен к первому входу логического элемента ИЛИ 11, входу счетчика 12, первому управляющему входу буферного блока 13 памяти. Выход первого логического элемента И 9 подключен параллельно к второму входу логического элемента ИЛИ 11 и второму упра1зляющему входу буферного блока 13 памяти. Вторые входы первого и второго логических элементов И 9 и 10 подключены соответственно к прямому и инверсному выходам триггера 14, вход которого соединен с выходом счетчика 12. Выход Lj -той ячейки буферного блока 13 памяти является первым выходом i-того блока 6 формирования, а выход j -той и 3 j -той ячеек подключены соответственно к первому и второму входам сумматора 15, выход которого является вторым выходом j -того блока 6 формирования. Цифровой автокоррелятор работает следуюшим образом. Аналого-цифровой преобразователь 1 осу ществляет дискретизацию во времени входного сигнала по синхроимпульсам генератора 3 импульсов, по которым, кроме того, осуществляется прием дискретизированного сигнала в первую ячейку входного блока 2 памяти и сдвиг содержимого ячеек входного блока 2 памяти. С приходом первого синхроимпульса происходит прием первого дискретизированного сигнала в первую ячейку входного блока 2 памяти.

и начинает работать первый блок 7 умножения сумматор 8,В которых происходит возведение в квадрат поступивших сигналов и накопление их суммы. Цикл работы при этом повторяется с приходом каждого последующего синхроимпульса. В сумматоре 8 накапливается сумма

; еО

Л-

где -тое значение входного процесса, N -объем выборки входного процесса.

С приходом т ретьего синхроимпульса первый раз срабатывает делитель часто- ты на три 4 и nepBbfft €лок 6 формирования сомножителей осуществляет прием сигналов, находящихся в первых трех ячейках входного блока 2 памяти. Цикл работы первого блока 6 формирования

сомножителей повторяется через два синхроимпульса, после чего срабатывает делитель частоты .на два 3, и первый блок 6 формирования осуществляет прием еде- дуюихих сигналов, находящихся в первых трех ячейках входного блока 2 памяти. При этом за два синхроимпульса первый блок 6 формирования формирует пару сомножителей и передает их во второй блок 7 умножения и второй сумматор 8, где накапливается сумма-, соответствующая второй точке корреляционной функции и т. д. до прихода последнего синхроимпульса.

Блоки б формирования сомножителей работают следующим образом. В начальном состоянии триггеры 14 блоков 6 формирования (фиг. 1) находится в нулевом состоянии. Таким образом, разрещая прохождение синхроимпульсов че рзз логический элемент И 1О с делителя частоты на три 4 и запрещая прохождение синхроимпульсов с делителя частоты на два 3 (фиг. 1) через первый логический элемент И 9. С приходом 3 j -того синхроимпульса в и -том блоке 6 формирования срабатывает счетчик 12 с коэффициентом пересчета j и выдает сигнал на первый управляющий вход буферного блока 13 памяти тем самым разрещая прием содержимого первых 3J -ячеек входного блока 2 памяти в буферный блок 13 памяти.

.При этом сигнал с выхода счетчика 12 поступает на вход триггера 14, устанавливая его в единичное состояние, тем самым разрешая прохождение синхроимпульсов с делителя частоты на два 3 (фиг. 1 через первый логический элемент И 9

на второй управля:ощий вход буферного блока 13 памяти и через логические элементы ИЛИ 11 в счетчик 12 с коэффициентом пересчета J . За Фактов, образованных 2J синхроимпульсами, в буферном блоке 13 памяти происходит А сдвигов содержимого ячеек, в сумматоре 15 происходит суммирование, а на первый и второй выходы j -/того блока формирования передается пар сомножителей

,,

-j-H

и .

X

(1)

и ) Таким образом, за 2 j синхроимпульсов в j +1 ом сумматоре 8 (фиг. 1) и на Д +1 -ом выходе устройства накапливается сумма

i/j.,.x.j,-).(3)

Так как цикл работы j -того блока формирования повторяется через 2i , то мо но записать вырам ение для суммы, кото- ;рая накапливается в + 1-ом сумматоре ,

8 за л синхрюимпульсов:

N j

,4 i /i-i KX ig - j.i/iej),.

где N;i можно определить из условия ,lj4-i4-aN J MПри 1 ) имеем

H-.i

(5)

iN,

Можно показать, что (4} является оценкой корреляционной функции в j -9Й точке при умножении на 1/С. 1/N-2-f,

Из (3) можно определить время, необходимое на обработку одного входного

сигнала4- 4.7+5

)

it. -- Для окончания работы устройства требуется (Ы + 2IVV) синхроимпульсов, тогда общее вржмя работы устройства будет равно -т f.

-- CN+-2M)tc.2.,Ы / , - . ч ,л

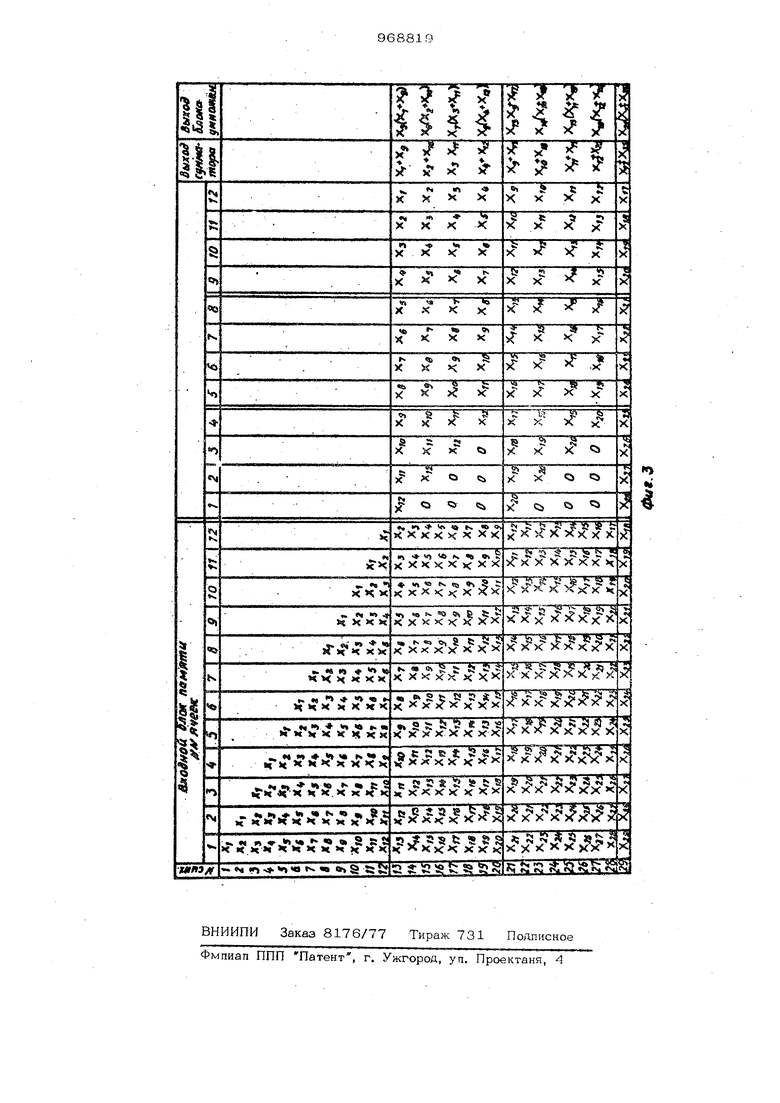

--Т- X лс// Можно показать, что быстродействие предлагаемого устройства выше по ср)ав- неникэ с известным приблизительно в два раза, учитывая, что АЛ Л . Для пояснения работы предлагаемого устройства на фиг. 3 приведена таблица соот1зетствия содержимого входного бло- кга памяти, буфертого блока 13 памяти {фиг. 2)j сумматора 15 (фиг. 2), блока7 умножения (фиг. 1) для 4-той ординаты корреляционной функции, т. е. для j 4 синхроимпульсам генератора 5 импульсов (фиг. 1). Техническая реализация устройства мо- жет быть осушествлена с использованием .элементов цифровой вычислительной техники. Разрядность АЦП 1 определяется заданной точностью оценки корреляционно функции и быстродействием устройства. Входной блок 2 памяти представляет собой набор регистров сдвига. Количество регистров сдвига равно числу разрядов АЦП 1, а разрядность регистров равна числу ординат корреляционной функции -М Делитель частоты на два 3 представляет собой триггер по счетным входам. Делитель частоты на три 4 может быть выпо нен как двухразрядный счетчик с коэффициентом пересчета 3. Блоки 7 умножения, сумматоры 8 (фиг. 1), логические элементы И 9 и 1О ИЛИ 11, счетчик 12, триггер 14, сумматор 15 (фиг. 2), являясь обычными уз лами ЦВТ, могут быть выполнены на интегральных схемах. Первый блок умножения 7 представляет собой квадратор. При чем быстродействие квадратора может быть сделано намного выще быстродейстВИЯ мнол ительного устройства. Поэтому быстродействие первого блока умножения не сказывается на общем быстрюдействии устройства. Буферный блок 13 памяти (фиг. 2) является устройством, аналогичным входному блоку 2 памяти (ф-иг. 1 Использование новых элементов дели- телей частоты на два и на три и блоков формирования, -сомножителей содержащих два логических элемента И, логические элементы ИЛИ, сумматор, триггер, счетчик и буферный блок памяти) позволяет увеличить быстродействие коррелятора параллельного действия за счет сокращения числа операций умножения, что позволяет увеличить частоту опроса АЦП приблизительно вдвое, т. е. расширить частотный диапазон устройства и повысить оперативность корреляционного анализа в реальном масштабе времени. Формула изобретения 1.Цифровой автокореллятор, сбдержаший М блоков умножения, выходы которых соединены с входами соответствующих сумматоров, аналого-цифровой праобразователь, информационный вход которого является входом авторегулятора,, а выход соединен с информационным входом блока памяти, управляющие входы аналого-цифрового преобразователя и блока памяти объединены и подключены к выходу генератора импульсов, отличающийся тем, что, с целью увеличения быстродействие, в автокорреля- тор введены М-1 блок формирования сомножителей, делители частоты на два и на три, входы которых объединены и подключены к выходу генератора импульсов, выходы делителей подключены соответственно к первому и второму управляющим входам блоков формирования сомножителей, первый и второй выходы которых подключены соответственно к первому и второму входам соответству:ощего блока умножения 3 -; ; j 1, 2, ..., М-1 - информационных входов каждого блока формирования сомножителей соединены с выходами соответствующих ячеек блока памяти, ВЫХОД первой из которых соединен с двумя входами первого блока умножения. 2.Автокоррелятор по п. 1, о т л ичающийся тем, что -и блок (|юрмирк вания сомножителей содержит элемент ИЛИ, счетчик, триггер, суммэгтор, блок памяти с 3J ячейками и два И, элемента И, входы которого являются соответственно первым и вторым управляющими входами блока формирования сомножителей, выходами которого являются соответственно выходы сумматора и 2 3 -и ячейки блока памяти, первый и второй выходы триггера подключены к вторым входам соответствующих элементов И, выходы которых соединены с соответствующими входами элемента ИЛИ, выход которого подключен к входу счетчика, выход которого соединен с входом триггера и первым управляющим входом блока памяти, информационные входы которого явля;:)тся информационным входом блока формирования сомножителей, второй

9Й6в81Й10

управляющий вход блока памяти подклю-1. Авторское свидетельство СССР

чен к выходу второго элемента И.

Источники информации, принятые во внимание при экспертизе

№ 590762. кл. GO6F 15/336, 1976.

2. Грибанов Ю. Н. и др. Автоматические цифровые корселяторы. М., Эяер 5 гия, 1971. с. 150.

| название | год | авторы | номер документа |

|---|---|---|---|

| Автокоррелятор | 1989 |

|

SU1617447A1 |

| Цифровой автокоррелятор | 1983 |

|

SU1104529A1 |

| Многоканальный цифровой коррелометр | 1982 |

|

SU1040492A1 |

| Цифровой автокоррелятор | 1982 |

|

SU1020835A1 |

| Цифровой автокоррелятор | 1983 |

|

SU1149277A1 |

| Автокоррелятор | 1990 |

|

SU1833894A1 |

| Оптическое устройство для вычисления корреляционной функции | 1988 |

|

SU1520541A1 |

| Цифровой автокоррелятор | 1985 |

|

SU1287178A1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ КОРРЕЛЯЦИОННОЙ ФУНКЦИИ | 1992 |

|

RU2037198C1 |

| Цифровой коррелятор | 1986 |

|

SU1328825A1 |

Авторы

Даты

1982-10-23—Публикация

1981-05-25—Подача