ИЛИ первого коммутатора объединены и под1шючены к шине нуленого потенциала, выходы одноименных ключей всех коммутаторов объединены и через соответствующие счетчики, кроме первого счетчика, подключены к первым входам соответствующих блоков деления, кроме первого/ выходы одноименных элементов И первой группы всех коммутаторов объединены и через соответствующие сумматоры, кроме первого, подключены

к вторы 1 входам соответствующих блоков деления,, кроме ппрвого, первый вход первого блока деления через первый счетчик подключен к синхронизирующему входу автокоррелятора, второй вход первого блока деления через первый сумматор подюшчен к выходу первого блока умножения, выходы блоков деления являются соответСТВУЮ1ЦИМИ выходами автокоррелятора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой автокоррелятор | 1982 |

|

SU1020835A1 |

| Автокоррелятор | 1989 |

|

SU1617447A1 |

| Коррелятор | 1982 |

|

SU1042030A1 |

| Цифровой автокоррелятор | 1983 |

|

SU1149277A1 |

| Устройство для решения задач планирования экспериментов | 1984 |

|

SU1317450A1 |

| Устройство для вычисления структурной и интервальной функций | 1984 |

|

SU1166135A1 |

| Устройство интерполяции для отображения графической информации | 1988 |

|

SU1525717A1 |

| Статистический анализатор | 1983 |

|

SU1124342A1 |

| Цифровой автокоррелятор | 1981 |

|

SU968819A1 |

| Спектральный анализатор случайных сигналов | 1984 |

|

SU1269048A1 |

-ЦИФРОВОЙ.АВТОКОРРЕЛЯТОР, содержащий (п-1) коммутаторов, первый блок памяти, состоящий из п последовательно соединенных ячеек, вход первой ячейки которого является первым информационным входом автокоррелятора, выход первой ячейки первого блока памяти соединен с первыми входами п блоков умножения, вторые входы которых подключены к выходам соответствующих ячеек первого блока памяти, второй блок памяти, состоящий из h последовательно соединенных ячеек, вход первой ячейки которого является вторым информационным входом автокоррелятора, выход первой ячейки второго блока памяти соединен с первыми .входами (п-1) блоков вычитания, вторые входы которых подключены к выходам соответствующих ячеек второго блока памяти, начиная со второй, m сумматоров, вход первого сут матора подключен к выходу первого блока умножения, а каждый коммутатор содержит дешифратор и первую группу из (т-1) элементов И, причем входы дешифраторов коммутаторов подключены к выходам соответствующих блоков .вычитания, первые входы элементов И первых групп всех коммутаторов объединены и являются синхронизирующими входами автокоррелятора, отличающийся тем, что, с целью повышения точности, в него введены m счетчиков и m блоков деления, а в каждый коммутатор - вторая группа из (т-1) элементов И, (т-1) элементов ИЛИХт-1) элементов НЕ, и (т-1) ключей, информационные входы которых в каждом коммутаторе объединены и подключены к выходу соответствующеi го блока умножения, кроме первого, (Управляющие входы ключей, кроме пер(Л вого ключа, в каждом коммутаторе объединены с вторыми входами одноименных элементов И первой группы того же коммутатора и подключены к выходам соответствующих элементов И второй группы того же коммутатора, первые входы которь& поключены к выходам соответствзтощих элементов ИЛИ того же коммутатора, вторые входы элементов И второй группы в каждом коммутаторе через соответствующие элементы НЕ подключены к соответствующим выходам дешифратора, управляющий вход первого ключа в каждом коммутаторе объединен- с вторым входом первого элемента И первой группы и с первым входом первого элемента ИЛИ и подключен в первом коммутаторе к щине единичного потенциала и к шине нулевого потенциала в остальных тсоммутаторах, вторые входы элементов ИЛИ i-ro коммутатора (где i 2, п-1) подключены к соответствующим выходам дешифратора (i-1)-ro коммутатора, вторые входы элементов

Изобретение относится к измерению характеристик случайных процессов и предназначено для определения оценки корреляционной функции текущего стационарного процесса, представленного неравноотстоящими отсчетами, рев .реальном масштабе времени.

I

Известен цифровой автокоррелятор, содержащий входной блок памяти, состоящий из 3(т-1) последовательно соединенных ячеек, аналого-цифрового преобр1азователя, генератора импульсов, делителя частоты на два и на три, (т-1) блоков формирования, m блоков умножения и m сумматоров, Причем каждый j-й блок формирования содержит блок памяти с 3j ячейками, сумматор, счетчик, триггер, элемент ИЛИ и два элемента И ,

Указанный автокоррелятор вьгчисляет автокорреляционную функцию процёссов с регулярные щагом дискретизации входного процесса и не позволяет вычислять автокорреляцуонную фунК1 ию процессов с нерегулярным шагом дискр тизации.

Наиболее близким по технической сущности и функциональному назначению к изобретению является цифровой коррелятор, содержащий два блока памяти, состоящих последовательно соединенных ячеек каждый, п блоков умножения, (п-1) блоков вычитания, () блоков коммутации, m сумматоров. Первым входом коррелятора является вход первого блока памяти. Выход первой ячейки первого блоки памяти подключен к первьм входам блоков умножения, вторые входы которых соединены с выходами соответствующих

ячеек первого блока памяти. Вход первого сумматора соединен с выходом первого блока умножения. Вторьгм входом коррелятора является вход второго блока памяти, вькоды ячеек которого, кроме первой, подключены к первым входам соответствующих блоков вычитания, вторые входы которых подключены к выходу первой ячейки второго блока памяти. Выходы блоков вычитания подключены к первым входам соот. вет ствующих блоков коммутации, вторые входы которых соединены с выходами соответствующих блоков умножения, кроме первого. Выходы блоков коммутации подключены к входам соответствующих cj MMaTopoB, кроме первого t 2 3.

Однако устройство не учитывает закон, по которому аппроксимирован входн.ой процесс, представленный неравноотстоящими отсчетами, т.е. не

.восстанавливает его. Он обрабатывает

,лишь существенные отсчеты и не обрабатывает промежуточные. Таким образом, возрастает статистическая погрешность определения оценок автокорреляционной функции исходного процесса (при фиксированном времени на.блюдения).

На практике в системах сжатия данных входной процесс чаще всего аппроксимирован полиномами нулевого порядка. Сладо ательно можно определять промежуточные отсчеты входного процесса, тем самым повысить точность оценки автокорреляционной функции.

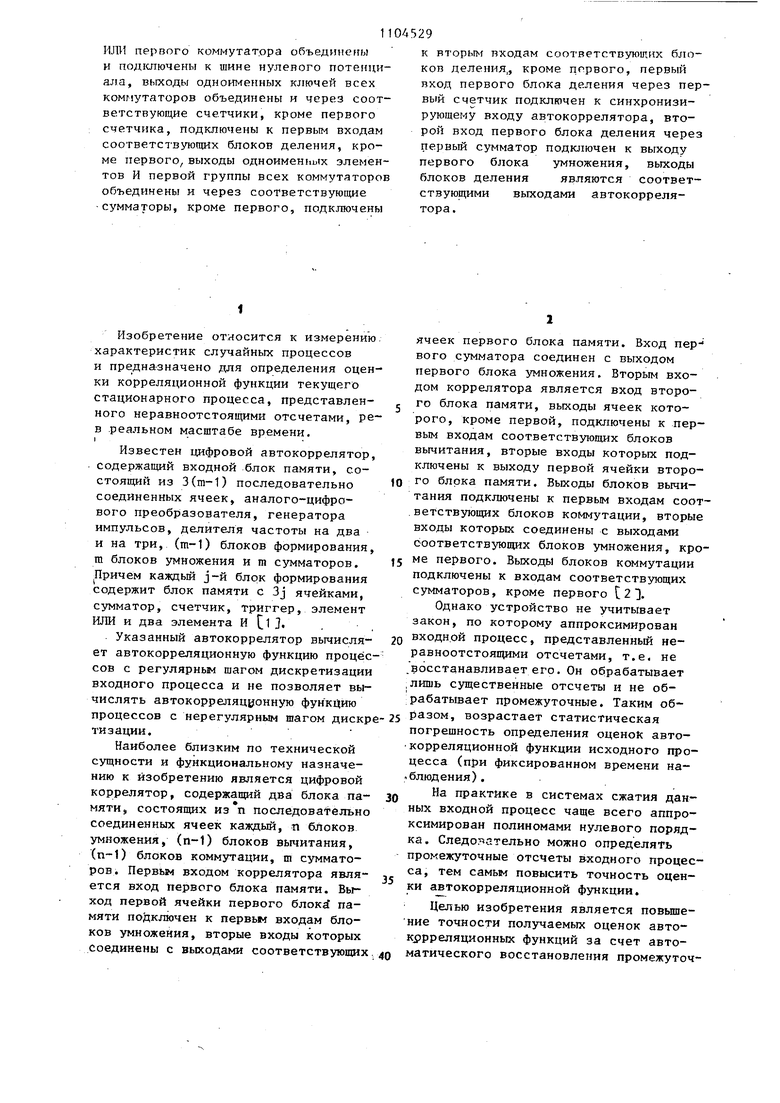

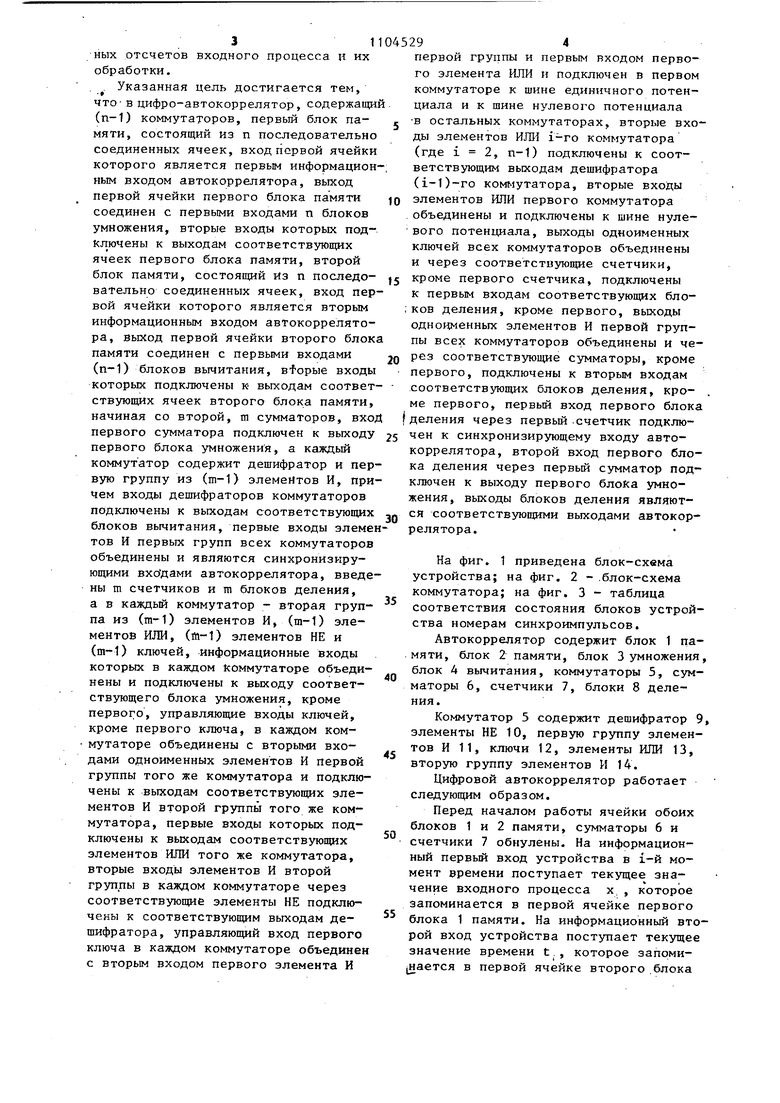

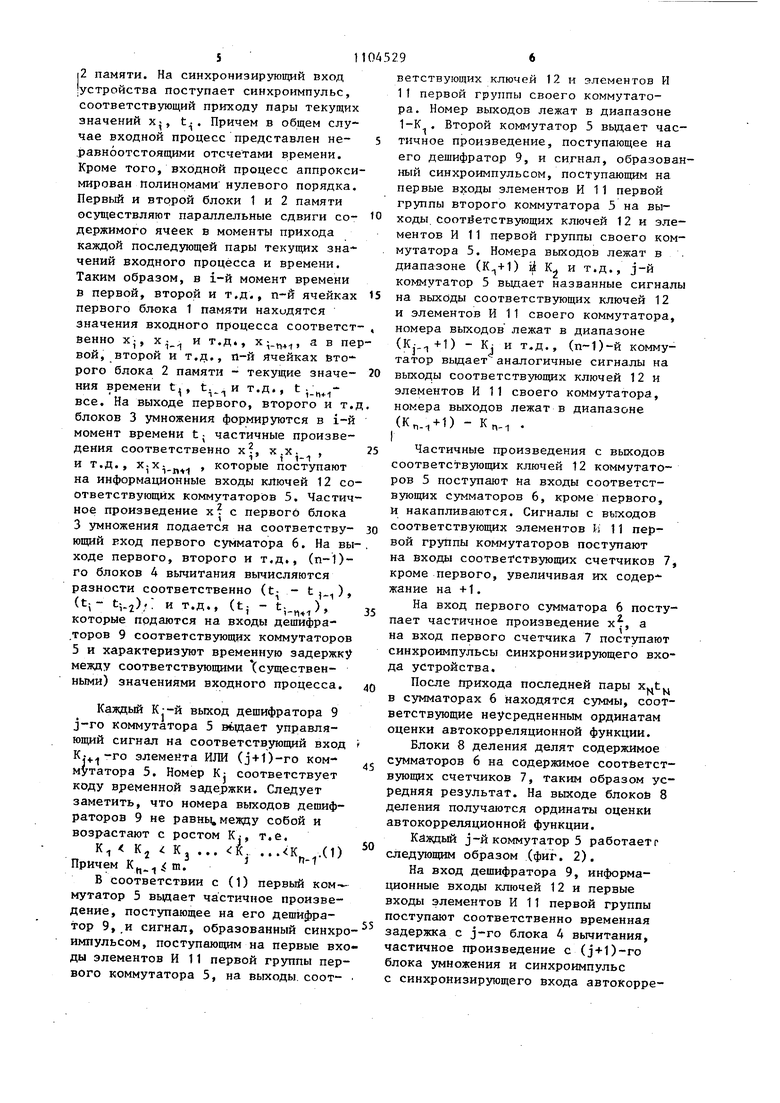

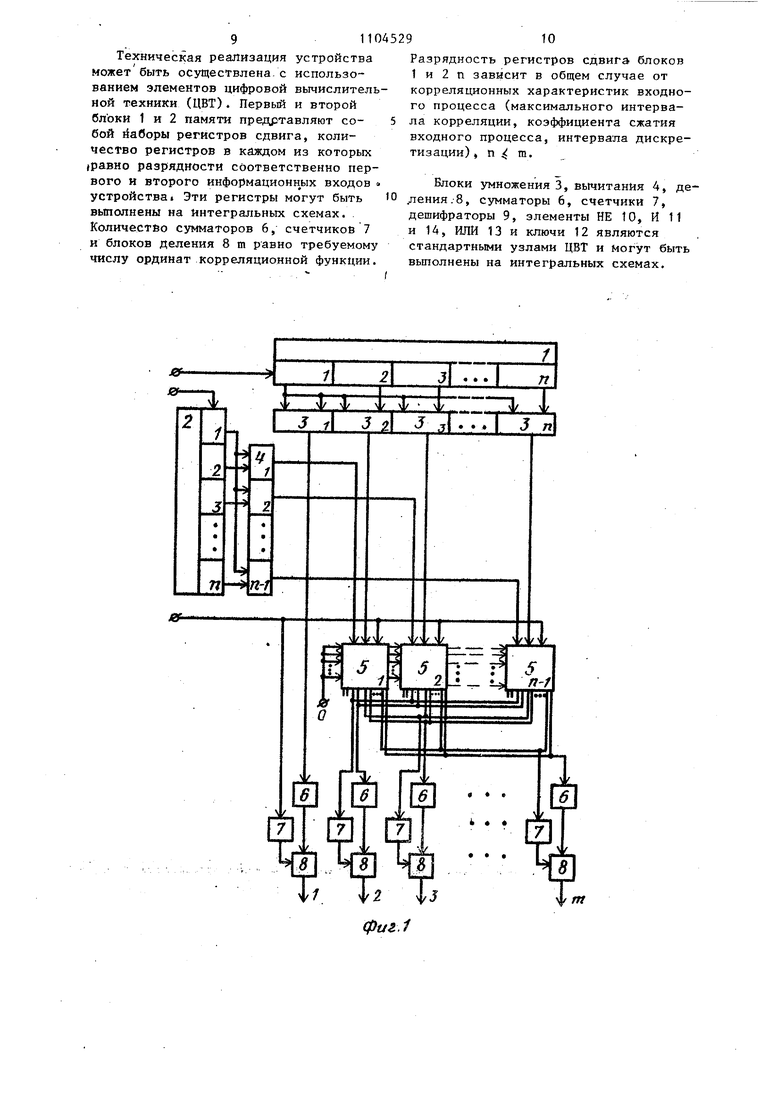

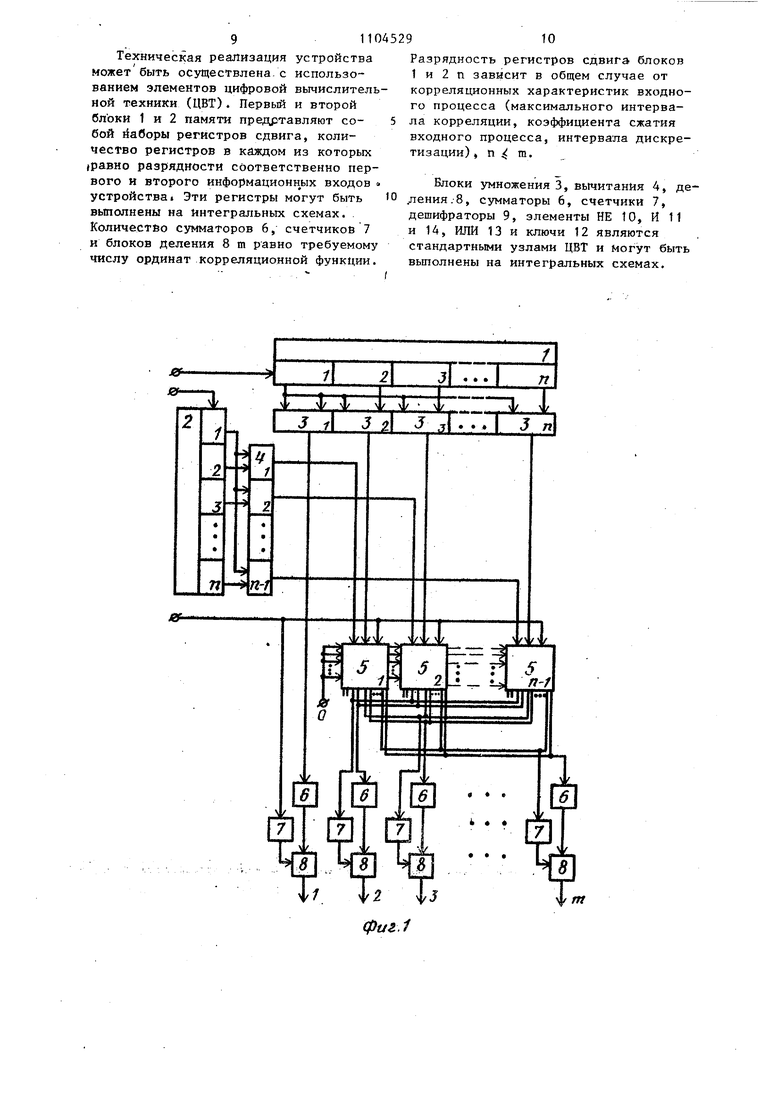

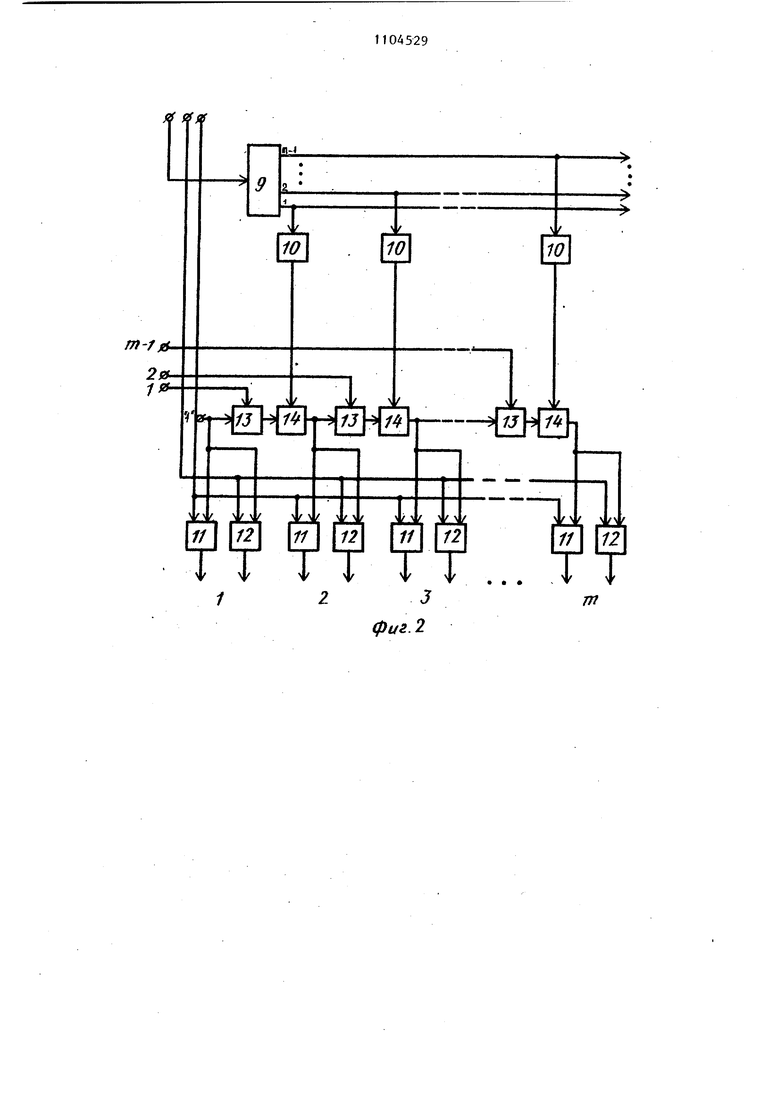

Целью изобретения является повьшение точности получаемьтх оценок авток ррреляционных функций за счет автоматического восстановления промежуточных отсчетов входного процесса и их обработки. . Указанная цель достигается тем, что- в цифро-автокоррелятор, содержащи (п-1) коммутаторов, первый блок памяти, состоящий из п последовательно соединенных ячеек, вход первой ячейки которого является первым информацион ным входом автокоррелятора, выход первой ячейки первого блока памяти соединен с первыми входами п блоков умножения, вторые входы которых подКл ючены к выходам соответствующих ячеек первого блока памяти, второй блок памяти, состоящий из п последовательно соединенных ячеек, вход пер вой ячейки которого является вторым информационным входом автокоррелятора, выход первой ячейки второго блок памяти соединен с первыми входами (п-1) блоков вычитания, вfopыe входы которых подключены к- выходам соответ ствующих ячеек второго блока памяти, начиная со второй, m сумматоров, вхо первого сумматора подключен к выходу первого блока умножения, а каждый коммутатор содержит дешифратор и пер вую группу из {т-1) элементов И, при чем входы дешифраторов коммутаторов подключены к выходам соответствующих блоков вычитания, первые входы элеме тов И первых групп всех коммутаторов объединены и являются синхронизирующими вхсУдами автокоррелятора, введе ны m счетчиков и m блоков деления, а в каждый коммутатор - вторая группа из (т-1) элементов И, (т-1) элементов ИЛИ, (й1-1) элементов НЕ и (т-1) ключей, информационные входы которых в каждом коммутаторе объединены и подключены к выходу соответствующего блока умножения, кроме первого, управляющие входы ключей, кроме первого ключа, в каждом коммутаторе объединены с вторыми входами одноименных элементов И первой группы того же коммутатора и подключены к выходам соответствующих элементов И второй группы того же коммутатора, первые входы которых подключены к выходам соответствующих элементов ИЛИ того же коммутатора, вторые входы элементов И второй группы в каждом коммутаторе через соответствующие элементы НЕ подключены к соответствуюЕ1ИМ выходам дешифратора, управляющий вход первого ключа в каждом коммутаторе объединен с вторым входом первого элемента И первой группы и первьм входом первого элемента ИЛИ и подключен в первом коммутаторе к шине единичного потенциала и к шине нулевого потенциала в остальных коммутаторах, вторые входы элементов ИЛИ i-ro коммутатора (где , п-1) подключены к соответствующим выходам дешифратора (i-l)-ro коммутатора, вторые вхоДы элементов ИЛИ первого коммутатора объединены и подключены к шине нулевого потенциала, выходы одноименных ключей всех коммутаторов объединены и через соответствующие счетчики, кроме первого счетчика, подключены к первым входам соответствуюш сх бло- ков деления, кроме первого, выходы одноименных элементов И первой группы всех коммутаторов объединены и через соответствующие сумматоры, кроме первого, подключены к вторым входам соответствующих блоков деления, кроме первого, первый вход первого блока деления через первый .счетчик подключен к синхронизирующему входу автокоррелятора, второй вход первого блока деления через первый сумматор подключен к выходу первого блока умножения, выходы блоков деления являются соответствующими выходами автокоррелятора. На фиг. 1 приведена блок-схема устройства; на фиг. 2 - .блок-схема коммутатора; на фиг. 3 - таблица соответствия состояния блоков устройства номерам синхроимпульсов. Автокоррелятор содержит блок 1 памяти, блок 2 памяти, блок 3 умножения, блок k вычитания, коммутаторы 5, сумматоры 6, счетчики 7, блоки 8 деления. Коммутатор 5 содержит дешифратор 9, элементы НЕ 10, первую группу элементов И 11, ключи 12, элементы ИЛИ 13, вторую группу элементов И 14. Цифровой автокоррелятор работает следующим образом. Перед началом работы ячейки обоих блоков 1 и 2 памяти, сумматоры 6 и счетчики 7 обнулены. На информационный первый вход устройства в i-й момент времени поступает текущее значение входного процесса х, , которое запоминается в первой ячейке первого блока 1 памяти. На информационный второй вход устройства поступает текущее значение времени t., которое запоми ается в первой ячейке второго .блока

|2 памяти. На синхронизирующий вход устройства поступает синхроимпульс, соответствующий приходу пары текущих Причем в общем слузначений Х: чае входной процесс представлен не.равноотстоящими отсчетами времени. Кроме того, входной процесс аппрокси мирован полиномами нулевого порядка. Первый и второй блоки 1 и 2 памяти осуществляют параллельные сдвиги содержимого ячеек в моменты прихода каждой последующей пары текущих зна- чений входного процесса и времени. Таким образом, а i-й момент времени в первой, второй и т.д., п-й ячейках первого блока 1 памяти находятся значения входного процесса соответст венно х-, х и т.д., к-.,, а в пе вой, второй и т.д., п-й ячейках второго блока 2 памяти - текущие значения времени t, , t. и т.д., t .все. На выходе первого, второго и т. блоков 3 умножения формируются в i-й момент времени t частичные произведения соответственно х и т.д., х-х.,, , которые поступают на информационные входы ключей 12 со ответствующих коммутаторов 5. Частич ное произведение х с первогб блока 3 умножения подается на соответствующий вход первого сумматора 6. На вы ходе первого, второго и т.д., (п-1)го блоков 4 вычитания вычисляются разности соответственно (t- - t )), (t,- t-,.2);: И Т.Д., (t. - t;.), которые подаются на входы дешифра.торов 9 соответствующих коммутаторов 5 и характеризуют временную задержку между соответствующими (существенными) значениями входного процесса. Каждый К--и выход дешифратора 9 j-ro коммутатора 5 вьщает управляющий сигнал на соответствующий вход К.-.-го элемента ИЛИ (j + 1)-ro коммутатора 5. Номер К: соответствует коду временной задержки. Следует заметить, что номера выходов дешифраторов 9 не равнь(, между собой и возрастают с ростом Kj, т.е. К, Kj KJ ... :К. ...К .(1) Причем Kj, m. В соответствии с (1) первый коммутатор 5 вьдает частичное произведение, поступающее на его дешйфратор 9, и сигнал, образованный синхро импульсом, поступающим на первые вхо ды элементов И 11 первой группы первого коммутатора 5, на выходы, соот1104529

ветствующих ключей 12 и элементов И 11 первой группы своего коммутатора. Номер выходов лежат в диапазоне 1-К . Второй коммутатор 5 вьщает частичное произведение, поступающее на его дешифратор 9, и сигнал, образованный синхроимпульсом, поступающим на первые входы элементов И 11 первой группы второго коммутатора 5 на выходы соответствующих ключей 12 и элементов И 11 первой группы своего коммутатора 5. Номера выходов лежат в . диапазоне () и К и т.д., j-й коммутатор 5 выдает названные сигналы на выходы соответствующих ключей 12 и элементов И 11 своего коммутатора, номера выходов лежат в диапазоне (К- +1) - Kj и т.д., (п-1)-й коммутатор вьщает аналогичные сигналы на выходы соответствующих ключей 12 и элементов И 11 своего коммутатора, номера выходов лежат в диапазоне (К,., + 1) - К„., . Частичные произведения с выходов соответствующих ключей 12 коммутаторов 5 поступают на входы соответствующих сумматоров 6, кроме первого, и накапливаются. Сигналы с вьжодов соответствующих элементов И 11 первой группы коммутаторов поступают на входы соответствующих счетчиков 7, кроме первого, увеличивая их содержание на +1. На вход первого сумматора 6 поступает частичное произведение х4, а на вход первого счетчика 7 поступают синхроимпульсы синхронизирующего входа устройства. После прихода последней пары в сумматорах 6 находятся суммы, соответствующие неусредненным ординатам оценки автокорреляционной функции. Блоки 8 деления делят содержимое сумматоров 6 на содержимое соответствующих счетчиков 7, таким образом усредняя результат. На выходе блокой 8 деления получаются ординаты оценки автокорреляционной функции. Каждый j-й коммутатор 5 работаете следующим образом (фиг. 2). На вход дешифратора 9, информационные входы ключей 12 и первые входы элементов И 11 первой группы поступают соответственно временная задержка с j-ro блока 4 вычитания. частичное произведение с (j+1)-ro блока умножения и синхроимпульс с синхронизирующего входа автоКоррелятора. Код временной задержки дешиф рируется дешифратором 9 в единичный сигнал на своем К--м выходе. Кроме того, этот сигнал поступает на К--и элемент НЕ 10 рассматриваемого коммутатора. Таким образом, сигналы на выходах элементов НЕ 10 формируют код, обратный коду, сформированному на выходах дешифратора 9, Во всех разрядах этого обратного кода находятся единичные потенциалы, kpoMe .К--го, где сформирован нулевой потен циал. Сигналы с выходов элементов НЕ 10 поступают на соответствующие входы элементов И 14, тем самым разрешая прохождение сигнала через эти элементы до элемента И 14, на который подается нулевой потенциал с К 1-го элемента НЕ 10. На соответствующие входы элементо ИЛИ 13 j-ro коммутатора 5 подается прямой код с выходом дешифратора 9 (j-l)-ro коммутатора и соответственно с выходов своего дешифратора 9 коммутатора 5. В К- , -м разряде этого кода находится единичный потенциал, во всех остальных - нулевые. Сигнал с К- -го выхода дешифратора 9j-ro коммутатора 5 поступает последовательно на соответствующий вход элемента ИЛИ 13 и соответствующий вход открытого элемента И 14 ()-го ключа 12, на первый вход элемента ИЛИ 13 и вход открытого элемента И 14 (К +2)-го ключа 12 и т.д. до закрытого нулевым сигС К--го элемента НЕ.10 элеменналом14 (К-+1)-го ключа 12. Сигналы та И с выходов элементов И 14 поступают на .управляющие входы соответствующих ключей 12 и в соответствзпощие входы элементов И 11. Таким о.бразом, сигна с К:., -го соответствующего элемента ИЛИ 13 входа j-ro коммутатора 5 открывает ключи 12 и соответствуюш 1е им элементы И 11 с (К + 1)-го до Kj-r I Частичное произведение с второго входа и синхроимпульс с третьего вх да j-ro коммутатора 5 подаются соот ветственно на информационные входы ключей и первые входы элементов И и далее на выходы соответствующих групп выходов указанного блока, номера которых лежат в диапазоне (К;., +1) - К,, т.е. через те ключи и элементы И, которые открыты сигналами соответствующих элементов И. Если на вход первого коммутато ра 5 подается единичный потенцпа.ч, а на управляющие входы группы нулевые потенциалы, то частичное произведение с .второго входа и синхроимпульс с третьего входа этого блока передаются соответственно на выходы первой и второй групп первого коммутатора 5, номера которь(х лежат в диапазоне 1-К. Если на входы каждого последующего коммутатора 5 подается нулевой потенциал, то частичное произведение с выхода соответствующего блока 3 -умножения и синхроимпульс синхронизирующего входа автокоррелятора через соответствующие ключи 12 и элементы И 11 j-ro коммутатора поступают на выходы, номера которых лежат в диапазоне 1-К. Так как на соответствующие входы первого элемента ИЛИ 13, элемента И 11 и управляющий, вход первого ключа 12 первого коммутатора подается единичный потенциал, то сигнал с этого коммутатора передаются на входы с номерами (К.+1) + Kj. Поскольку на соответствующие входы первого элемента ИЛИ 13, первого элемента И 11 и управляющий вход,первого ключа остальных коммутаторов подается нулевой потенциал, то сигналы с выходов J-го коммутатора 5 поступают на выходы с номерами с (К- ., +1)-го по Kj . Для пояснения работы устройства представлена таблица (фиг. 3) соответствия содержимого составляющих блоков устройства синхроимпульсам входного процесса. Из этой таблицы видно, что, кроме существенных отсчетов входного процесса, обрабатываются и промежуточные отсчеты. По результатам сравнительного анализа, по точности предлагаемого устройства и известного, проведенного методом имитационного моделирования, установлено, что среднеквадратическая погрешность вычисления корреляционной функции у предлагаемого устройства меньше, чем у известного. Лучшие метрологические характеристики предлагаемого устройства по сравнению с известным позволят расширить область его применения в различных областях народного хозяйства, что обеспечит большую экономическую эффективность от его использования. Техническая реализация устройства можетбыть осуществлена, с использованием элементов цифровой вычислитель ной техники (ЦВТ). Первьй и второй блоки 1 и 2 памяти предртавляют собой йаборы регистров сдвига, количество регистров в каждом из которых (равно разрядности соответственно первого и второго информационн 1х входов устройства Эти регистры могут быть вьтолнены на интегральных схемах. Количество сумматоров 6, счетчиков 7 и блоков деления 8 m равно требуемому числу ординат корреляционной функции Разрядность регистров сдвига блоков 1 и 2 п зависит в общем случае от корреляционных характеристик входного процесса (максимального интервала корреляции, коэффициента сжатия входного процесса, интервала дискретизации) , п т. . Блоки умножения 3, вычитания 4, деления. 8, сумматоры 6, счетчики 7, дешифраторы 9, элементы НЕ 10, И 11 и 14, ИЛИ 13 и ключи 12 являются стандартными узлами ЦВТ и могут быть выполнены на интегральных схемах.

ff fiH m -ffi.

55 S

V,

«44

гГ

It

tj -«

fe ч

Э «

г н

«S

«91

«в

Нг«Ч

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Цифровой автокоррелятор | 1981 |

|

SU968819A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Авторское свидетельство СССР № 980101, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-07-23—Публикация

1983-03-18—Подача