liSrHR Р 1 2. Усилитель по п. 1, о т л и ч а ю - щ и и с я тем, что распределитель импульсов выполнен на инверторе и цвух синхронных 1)К5-триггерах, причем перм вый вхоц распределителя импульсов подключен к объединенным D и R-входам одного синхронногоВР5-триггера, и через ин10274 вертор - к объединенным входам второгоБЙЗ-триггера, синхровхоцы обоих синхронных ВЯ5-триггеров подключены к второму входу распределителя импульсов, въкоды синхронныхВР5-триггеров соединены с соответствующими выходами распределителя импульсов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Усилитель мощности | 1984 |

|

SU1241414A2 |

| Усилитель мощности | 1985 |

|

SU1314438A1 |

| Усилитель мощности | 1988 |

|

SU1525863A1 |

| Гибридное интегрирующее устройство | 1985 |

|

SU1418768A1 |

| Способ управления транзисторным полумостовым инвертором | 1986 |

|

SU1467711A1 |

| Датчик угловой скорости | 1985 |

|

SU1296949A1 |

| ЦЕЗИЕВЫЙ СТАНДАРТ ЧАСТОТЫ | 1994 |

|

RU2076411C1 |

| Аналого-цифровое интегрирующее устройство | 1985 |

|

SU1275483A1 |

| Устройство для управления преобразователем постоянного напряжения в напряжение заданной формы | 1988 |

|

SU1646026A1 |

| Усилитель класса Д | 1984 |

|

SU1334358A1 |

1. УСИЛИТЕЛЬ МОДНСХЗТИ, I соаержашйй послеаоватепьно включенные источник вхоцного сигнала, сумматоринтегратор, один из входов которого со единен с выходом источника входного сигнала, и дискриминатор, а также генератор тактовых импульсов и выходной каскад, выход которого подключен к другому входу сумматора-интегратора и нагрузке, отличающийся тем, что, с целью уменьшения нелинейных искажений, в него введен распределитель импульсов, первый и второй входы которого соответственно соединены с выходами дискриминатора и генератора тактовых импульсов, а выходы - с входами выходного каскада.

1

Изобретение относится к радиЬгехнике, гае оно может быть использовано, в частности, в усилителях мощности низкой частоты, а также в импульсных регуляторах напряжения постоянного тока.

Известен усилитель мощности, содержащий последовательно включенные ис- точник сигнала, суммато{ -интегратор, один из входов которого соединен с выхоцом источника вжодного сигнала, и цискриминатор, а также генератор тактовых импульсов и выходной каскад, выход ко- торого подключен к аругому входу сумматора-интегратора и нагрузке ClJ .

Однако известнъгй усилитель мощности имеет больщие нелинейные искажения.

Цель изобретения - уменыиение нелинейных искажений.

Указанная цель достигается тем, что а убидитель мощности, содержащий последовательно включенные источники входного сигнала, сумматор-инт г тор, один из входов которого соединен с выходом источника входного сигаала, и аискриминатор, а также генератор тактовых импульсов и выходной каскад, вьрсод которого подключен к другому входу сумматора-ийтегратрра и нагрузке, введен распреаелитель импульсов, первый и второй входы которого соотве- ственяо соединены с выходами дискри миватора в генератора .тактовых импульсов, а выходы - с Bxotf MH выходного сигнала

Крсаде Tofo, распределитель импульсов шыполнен на инверторе и двух синхронныкВЯ5« - иггераХт путчем первый

ERoa распределителя имйульсс подключен к объединенным и К-входам одного синхр шно1Ч ; гг5-три тера, и через инве top к обьеоиненным входам вторснч) SRS триггера, сннхровхоцы обоих синхронных DRS-триггеров подключены к второму входу распреаелителя импульсов, выходы

синхронных ВРЗ риггеров соединены с соответствукиаими выходами распреаелителя импульсов.

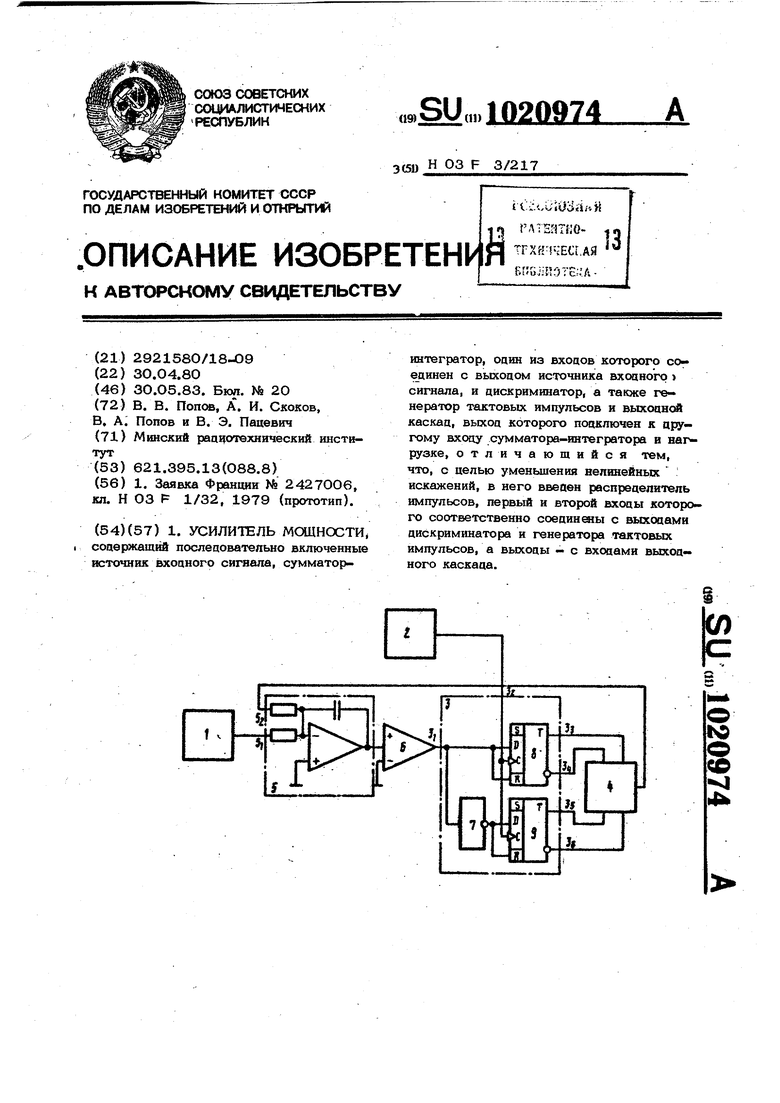

На чертеже представлена структурная схема усилителя мощности;

Усилитель мощности содержит источник 1 входного сигнала, генератор .2 тактовых импульсов, распределитель 3 импульсов с входами 3 и 3« и выходами 3 2 - 3,,. выходной каскад 4 сумматорнннтегратор 5 с входами 5 И дискриминатор 6. Распределитель 3 ипульсов виюлнен на инверторе 7 и двух синхронныхDRS-триггеpax 8 и 9. :

Усилитель, мощности работает следующим образом.

В исходном, состоянии оба синхронных BRS-триггера находятся в состоянии О, что соответствует отсутствию какоголибо (положительного или отрицательного) потенци на выходе выходного каскада 4. На вход 52 сумматора-интегратора 5 поступает нулевой сигаал.

Сумматор-интегратор 5 является основным элементом устройства, в котором осуществляется сравнение плошаав выходнс«го усиленного импульса со значением, занесенным в сумматор-интегратор 5 по входу 5.

Hpis отрицательном выходном сигнале iHa В1 1ходе сумматора-интегратора по .входу 5 накопится некоторый положитель ный потенциал, соответствующий интегралу входного за часть тактового промежутка до тактового импульса. ; На выходе дискриминатора 6 при этсии устанавлиЕваетсй положительный потенциал на выходе инвертора 7 - нулевой потенциал,который по входу R удерживает Триг;гдр в состошии О. С приходом первогЧ) положительного тактового импульса триггер 8 устанавливается в состояние t а тртггер 9 своего состояния не меняет так как на его установочном входе R в

это время присутствует нулевой потенциал с инвертор 7. При этом сигнал с выхода Sj распределителя импульсов 3 усиливается ооиим из плеч выходного каскада 4 и подается на вход 52 сумматогра-интегратора 5. С этого момента начинается сравнение интеграла выходного усиленного момёнта импульса, который может быть любой формъ, с интегралом входного сигнала. Причем, так как вход- ной сигнал интегрируется непрерывно, то в сравнении участвует как |штеграл входного сигнала до тактового импульса (за- несенное ранее в интегратор значение), так и после него. Резисторы и емкость сумматс ра янтёгратора 5 выбраны таким образом, чтобы то прихода следующего тактового импупъса сравнение заканчиш лось, что соответстбует переходу напряжения яа выхсще сумматора-интеграто ра 5 в О. Переход напряжения на выхси сумматора-интегратора 5 в О фиксируется цискрвминатором 6, выходной импульс которого перебрасывает триггер по входу R в состояй О. Формированве вьосооногю импульса заканчивается.

На вхопе 5 2 сумматора-интегратора 5 по обратной связи исчезает попо жительиый потенциал,сравнение интегралов входного и выходного сигналов за ка1(Ч1Е1вается. Так как вкходноб сигнал поаается на 5 | кепрер 1вно, в сумматоре-интеграторе 5 начянается накоплея, значеняя интеграла выходного сигна па на csmKnojaeu тактовом промежутке, jEtacKpaMGBiarop 6 вьшав сигнал переброса {жггера,воз врбш ютс:я в исходное состо янве.Ш Biuxme -3 распреоелигеля 3 импупьсов и на miixcKte выходного каска да 4 до ягдахбда следующего тактового импульса сокр яется яулевой потенциал..

Яри йврехОДе вхосигнала чераз О пЬсяз заве{ шения последнего по

ложительного импульса на выходе выходного каскада 4 в Ьумматоре-интеграторе 5: начинает накапливаться отрицательный потенциал. Это состояние определяется аис криминатором 6, который подает разрешающий положительный потенциал на вход и R-триггера 9 и отрицательный на 1) вход и триггера 8. Поэтому пря подаче на синхровходы обоих1)К5-тригтеров тактового импульса изменит свое со- ето5шие с О на только триггер 9. upsi этом выходной каскад 4 выполнен шкшл образом, что вкянэте ние триггера 9 приводит к формированию отрицательного импульса на его выходе, ill . этом начинается сравнение интеграла отрицательного выходного импульса (лю-

, бой формы) с интегралом попожитель «

ного входного сигнала.

Процесс сравнения идет аналогично как и для отрицательного входного сигнала. При переходе напряжения на выходе сумматора-интегратора 5 через О (конец сравнения интегралов нхсового и ходного сигналов) дискриминатор 6 через инвертор 7 подает отрицательный управлякядий сигнал на } и Р-входы трйхтё- ра 9. Триггер 9 переходит в состоянве О hpcHiecc сравнения закончен. На О вl{ вxoды триггера 8 также поступает ю пульс попожитепьй( полярности и триггер 8 своего состояния О не изменяет. Усилитель мошностя прихоцат в иосодяое состояивй. в следующем такте ПЕ положительном входном сигнале формнрдгется отрицательный импульс на выходного каскада 7.

TEIKMM (разом, ввесюние нового эле- .мента-фаспределитепя импульсов позволят снизить нели&1евные вокаженвя в предлагаемом усвшпеле мошвости.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Пенал | 1929 |

|

SU24270A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1983-05-30—Публикация

1980-04-30—Подача