11

Изобретение относится к радиотехнике и может быть использовано, в частности, в усилителях мощности низкой частоты, а также в импульсных регуляторах и стабилизаторах напря- женин постоянного тока и является дополнительным к основному авт. св. № J020974.

Цель изобретения увеличение выходной мощности.

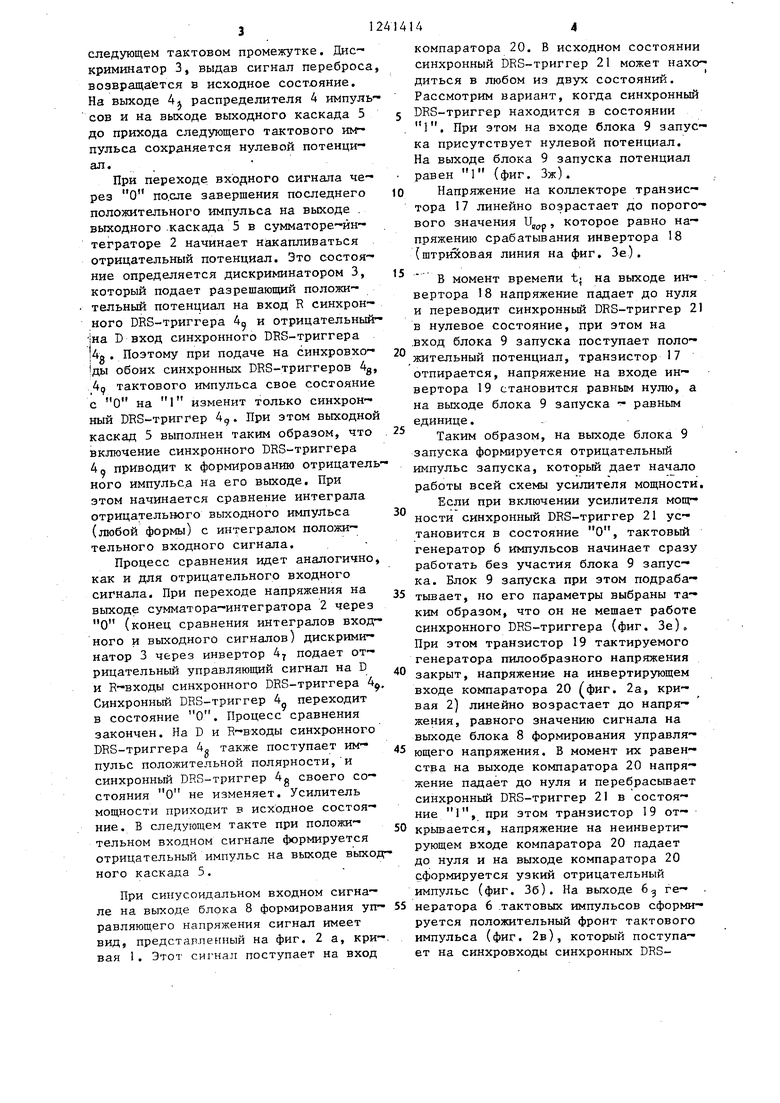

На фиг. 1 представлена структурная схема усилителя мощности; на фиг. 2 - диаграммы напряжений, поясняющие его работу.

Усилитель мощности содержит ис- точник 1 входного сигнала, сумматор- интегратор 2 с входами 2 к 2, дискриминатор 3, распределитель 4 импульсов, со входами 4, и 4, выходами , инвертором 4 и синхронны- ми DRS-триггерами 4д-4,, выходной каскад 5, генератор 6 тактовых, импульсов с управляющим входом 6, входом синхронизации 6 и вьосодом 6 элемент 7 совпадения. Генератор 6 тактовых импульсов содержит блок 8 формирования управляющего напряжения блок 9 запуска и управляющий ждущий генератор 10 с входом 10 и прямым и инверсным выходами Ю, 10 соот- ветственно. Блок 8 формирования управляющего напряжения содержит двух- полупериодный выпрямитель на диодах 11 и 12 и инвертирующем операционном усилителе 13 и элемент сдвига уровня на диоде 14 и резисторах 15 и 16. Блок 9 запуска содержит генератор пилообразного напряжения на транзисторе 17 и инвертор 18. Управляемый ждущий генератор IО содержит такти- руемый генератор пилообразного напряжения на транзисторе 19, компаратор 20, синхронный DRS-триггер 21.

Усилитель мощности работает следующим образом.

В исходном состоянии оба синхрон- - ных DRS-триггера распределителя 4 импульсов находятся в состоянии О, что соответствует отсутствию какого- либо (положительного или отрицатель- кого) потенциала на выходе выходного каскада 5. На вход 2 сумматора-интегратора 2 поступает нулевой сигнал

Сумматор-интегратор 2 .является основным элементом устройства, в котором осуществляется сравнение площади выходного усиленного импульса со

14 .2

значением, занесенным в сумматор-интегратор 2 по входу 2f .

При отрицательном выходном сигнале на выходе с умматора-интегратора 2 по входу 2, накопится некоторый положительный потенциал, соответствующий интегралу входного сигнала за часть тактового промежутка до тактового

импульса. I

На выходе дискриминатора 3 при 3toM устанавливается положительный потенциал, на выходе инвертора 4 - нулевой потенциал, который по входу R удерживает синхронный DRS-триггер- 4р в состояние О. С приходом первого положительного тактового импульса синхронный DRS TpHrrep 4 устанавливается в состояние 1 а синхронный DRS-триггер 4 своего состояния не меняет, так как на его установочном входе К в это время присутствует нулевой потенциал с инвертора 4. . При этом сигнал с выхода 4,, распределителя 4 импульсов усиливается одним из плеч выходного каскада 5 и подается на вход 2 сумматора-интегратора 2. С этого момента начинается сравнение интеграла выходного усиленного момента - импульса, которьй может быть любой формы, с интегралом входного сигнала. Так как входной сигнал интегрируется непрерывно, то в сравнении j/ частвует интеграл входного сигнала до тактового импульса (занесенное ранее в интегратор значение) и после него. Резисторы и емкость сумматора-интегратора 2 выбраны TaKttM образом, чтобы д.о прихода следующего тактового импульса сравнение заканчивалось, что соответствует переходу напряжения на выходе сумматора-интегратора 2 в О. Переход напряжения на выходе сумматора-интегратора 2 в о фиксируется дискриминатором 3, вы:кодной импульс которого перебрасьшает синхронный DRS-триггер 4д по входу KB состояние О. Формирование выходного импульса заканчивается.

На входе 2,, сумматора-интегратора 2 по обратной связи исчезает положительный потенциал, сравнение интегралов входного и выходного сигналов заканчивается. Так как входной сигнал подается на вход 2 сумматора- интегратора 2 непрерывно, то в последнем начинается накопление значе- ня интеграла выходного сигнала на

следующем тактовом промежутке. Дискриминатор 3, выдав сигнал переброса возвращается в исходное состояние. На выкоде 4 распределителя 4 импульсов и на вьтходе выходного каскада 5 до прихода следующего тактового им пульса сохраняется нулевой потенциал.

При переходе; входного сигнала через О по.сле завершения последнего положительного импульса на выходе . выходного .каскада 5 в сумматоре-интеграторе 2 начинает накапливаться отрицательный потенциал. Это состояние определяется дискриминатором 3, который подает разрешающий положительный потенциал на вход R синхронного DRS-триггера 4 и отрицательный- |На D вход синхронного DRS-триггера

8

Поэтому при подаче на синхровхо4а

1ды обоих синхронных DRS-триггеров чд, 4(j тактового импульса свое состояние с о на 1 изменит только синхронный DRS-триггер 4. При этом выходной каскад 5 выполнен таким образом, что включение синхронного DRS-триггера 4о приводит к формированию отрицательного импульс.а на его выходе. При этом начинается сравнение интеграла отрицательного выходного импульса (любой формы) с интегралом положительного входного сигнала.

Процесс сравнения идет аналогично, как и для отрицательного входного сигнала. При переходе напряжения на выходе сумматора-интегратора 2 через О (конец сравнения интегралов входного и выходного сигналов) дискриминатор 3 через инвертор 4 подает отрицательный управляющий сигнал на D и R-входы синхронного DRS-триггера 4 Синхронный DRS-триггер 4 переходит в состояние О. Процесс сравнения закончен. На D и R-входы синхронного DRS-триггера 4g также поступает импульс положительной полярности, и синхронный DRS-триггер 4g своего состояния о не изменяет. Усилитель мощности приходит в исходное состояние. В следующем такте при положительном входном сигнале формируется отрицательный импульс на выходе вькод ного каскада 5.

При синусоидальном входном сигнале на выходе блока 8 формирования уп- равляющего напряжения сигнал имеет вид, предсталленный на фиг. 2 а, кри- вая 1. Этот сигнал поступает на вход

компаратора 20. В исходном состоянии синхронный DRS-триггер 21 может нахо- диться в любом из двух состояний. Рассмотрим вариант, когда синхронный DRS-триггер находится в состоянии 1, При этом на входе блока 9 запуска присутствует нулевой потенциал. На выходе блока 9 запуска потенциал равен 1 (фиг. Зж).

Напряжение на коллекторе транзистора 17 линейно возрастает до порого

вого значения Ц

вор

которое равно напряжению срабатьшания инвертора (штриховая линия на фиг. Зе).

18

5

5

0

0

В момент времени t- на выходе инвертора 18 напряжение падает до нуля и переводит синхронный DRS-триггер 21 в нулевое состояние, при этом на .вход блока 9 запуска поступает положительный потенциал, транзистор 17 отпирается, напряжение на входе инвертора 19 становится равным нулю, а на выходе блока 9 запуска - равным единице.

Таким образом, на выходе блока 9 запуска формируется отрицательный импульс запуска, который дает начало работы всей схемы усилителя мощности.

Если при включении усилителя мощности синхронный DRS-триггер 21 установится в состояние О, тактовый генератор 6 импульсов начинает сразу работать без участия блока 9 запуска. Блок 9 запуска при этом подраба- 5 тывает, но его параметры выбраны таким образом, что он не мешает работе синхронного DRS-триггера (фиг. Зе), При этом транзистор 19 тактируемого генератора пилообразного напряжения закрыт, напряжение на инвертирующем входе компаратора 20 (фиг. 2а, кривая 2) линейно возрастает до напряжения, равного значению сигнала на выходе блока 8 формирования управляющего напряжения. В момент их равенства на выходе компаратора 20 напряжение падает до нуля и перебрасьшает синхронный DRS-триггер 21 в состояние 1, при этом транзистор 19 открывается, напряжение на неинверти- рующем входе компаратора 20 падает до нуля и на выходе компаратора 20 сформируется узкий отрицательный импульс (фиг. Зб). На выходе 6 генератора 6 .тактовых импульсов сформируется положительный фронт тактового импульса (фиг. 2в), который поступает на синхровходы синхронных DRS5

триггеров распределителя А импульсов, на выходе которого сформируется передний фронт выходного широтно модулированного импульса (фиг. 2 з,к) Задний фронт широтно модулированного импульса формируется по моменту равенства площадей входного и выходного сигнала,.По моменту окончаний выходного импульса с одного из выхо- дов 4fl или 4g распределителя 4 импульсов положительный фронт импульса через элемент 7 совпадения поступает .на синхровход синхронного DRS- триггера 21 и устанавливает его в состояние О.

С этого момента начнется формирование следующего тактового импульса, который поступает на вход распре™ делителя 4 импульсов через некоторый промежуток времени, который обратно пропорционален амплитуде входного сигнала. В данном усилителе мощности при всех индексах модуляции невозможно такое состояние, когда тактовый импульс поступает на вход распределителя 4 импульсов ранее, чем закончился предьадущий импульс. ФорМирова ние тактового импульса начинается после окончания формирования выходно го импульса.

Формула изобретения

1.Усилитель мощности по авт. св. № 1020974, отличающийся тем, что, с целью увеличения выходной мощности, выход источника входного сигнала соединен с .управляющим вхо- дом генератора тактовых импульсов, а между выходами распределителя импульсов и входом синхронизации генератора тактовых импульсов введен элемент совпадения,

2.Усилитель по п, , о т л и чающийся тем, что генератор тактовых импульсов содержит блок фор, o s

0 5 о

5

,

мирования управляющего напряжения, вход которого является управляющим входом генератора тактовых импульсов , выход соединен с управляющим входом управляемого ждущего генератора , один выход которого является выходом генератора тактовых импульсов, другой выход соединен с входом блока запуска, выход которого подклю- Ч€1Н К входу запуска уиршв-ляемого ждущего генератора, вход синхронизации которого является входом синхронизации генератора тактовых HI-S пульсов,

3.Усилитель по п. 2, отличающийся тем, что .блок формирования управляющего напряжения содержит последовательно соединенные двухполупериодаый выпрямитель и элемент сдвига уровня, выполненный на диоде и резисторах,

4.Усилитель поп, 2, отличающийся тем, что блок запуска выполнен на последовательно соединенных генераторе пилообразного напряжения и инверторе,

5.Усилитель по п. 2, отличаю, щ и: и с я тем, что управляе- М1)1й ждущий генератор содержит тактируемый генератор пилообразного напряжения, выход которого соединен с первым входом компаратора, второй вход которого является управляющим входом управляемого ждущего генератора, выход соединен с Б-входом синхронного DRS-триггера, синхровход которого является входом синхронизации генера- тора тактовых импульсов, D-вход под- ктаочен к общей шине источника питания, Е-вход - к выходу блока запуска, вход которого соединен с инверсным выходом DRS-триггера, прямой выход которого является выходом генератора тактовых импульсов и соединен с входом тактируемого генератора пилообразного напряжения.

Фиг. 2

| название | год | авторы | номер документа |

|---|---|---|---|

| Усилитель мощности | 1980 |

|

SU1020974A1 |

| ЦЕЗИЕВЫЙ СТАНДАРТ ЧАСТОТЫ | 1994 |

|

RU2076411C1 |

| Датчик угловой скорости | 1985 |

|

SU1296949A1 |

| Аналого-цифровой преобразователь параметров диэлькометрического датчика | 1988 |

|

SU1547063A1 |

| Аналоговое запоминающее устройство | 1979 |

|

SU930387A1 |

| СПОСОБ ОПРЕДЕЛЕНИЯ ОБЪЕМНОГО РАСХОДА ВЕЩЕСТВ С ПОМОЩЬЮ УЛЬТРАЗВУКОВЫХ СИГНАЛОВ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1999 |

|

RU2169906C2 |

| Устройство для управления преобразователем постоянного напряжения в напряжение заданной формы | 1988 |

|

SU1646026A1 |

| Усилитель мощности | 1988 |

|

SU1525863A1 |

| УСТРОЙСТВО ФАЗОВОЙ АВТОПОДСТРОЙКИ ЧАСТОТЫ | 1991 |

|

RU2014740C1 |

| Усилитель мощности | 1985 |

|

SU1314438A1 |

Изобретение относится к радиотехнике и является дополнительным к изобретению по авт. св. № 1020974. Обеспечивается увеличение выходной мощности. Усилитель мощности содержит источник 1 входного сигнала, сумматор-интегратор 2, дискриминатор 3, распределитель импульсов 4, выходной каскад 5, генератор 6 тактовых импульсов и элемент 7 совпадения. Генератор 6 тактовых импульсов включает блок 8 формирования управляющего напряжения, блок 9 запуска и управляемый ждущий генератор 10. В блоке 8 формирования управляющего напряжения диоды 11, 12 и инвертирующий операционный усилитель 13 образуют двух- полупериодный выпрямитель, а диод 14 и резисторы 15, 16 - элемент сдвига. Блок 9 запуска вьтолнен на генераторе пилообразного напряжения (ГПН) и инверторе 18. Управляемый ждущий генератор 1.0 содержит тактируемый . . ГПН, выполненный на транзисторе 19, компаратор 20 и синхронный DRS-триг- гер 21. Сумматор-интегратор 2 является основным злементом усилителя мощности. Он осуществляет сравнение площади выходного усиленного импульса со значением, поступающим с источника 1 входного сигнала. Увеличение выходной мощности достигается за счет введения элемента 7 совпадения и подачи входного сигнала на генератор 6 тактовых импульсов. 4 3.я. ф-лы. 2 ил. с & (Л tc 4 4 Ч)

| Усилитель мощности | 1980 |

|

SU1020974A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1986-06-30—Публикация

1984-05-08—Подача