Изобретение относится к гибридной вычислительной технике и может быть I использовано в аналого-цифровых вы- j числительных системах и устройствах I автоматики для длительного интегрирования аналогового сигнала.

Целью изобретения является повышение точности интегрирования и сокращение аппаратурных затрат.

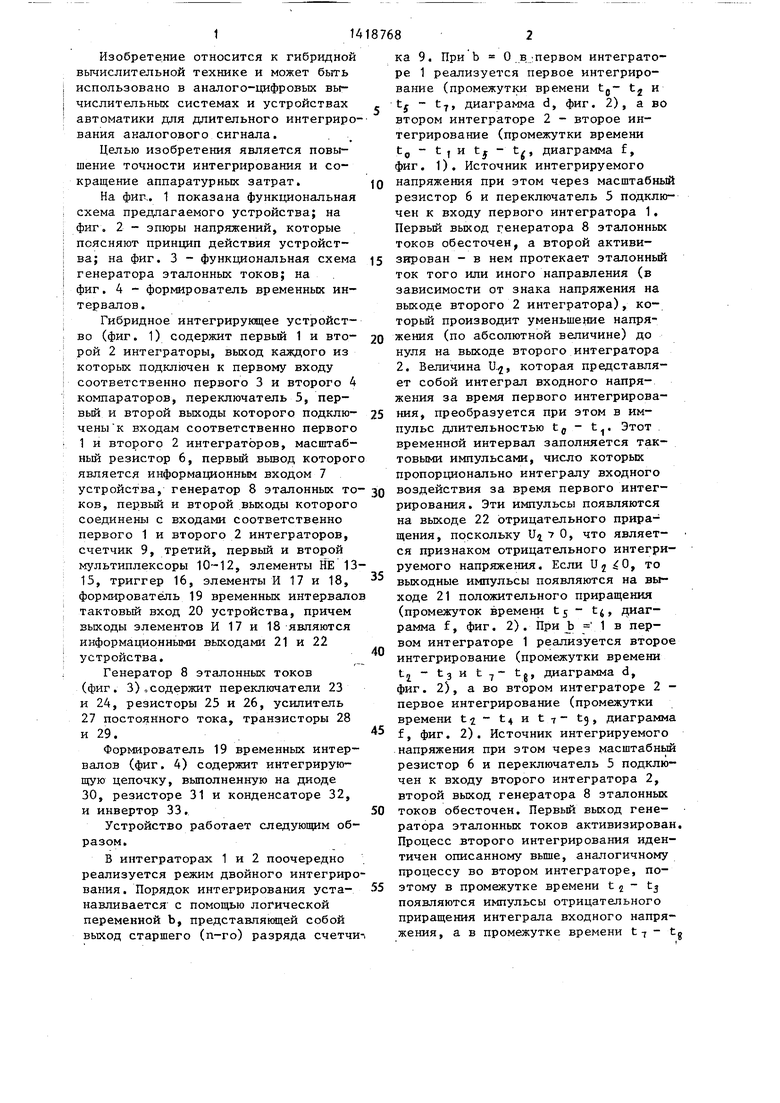

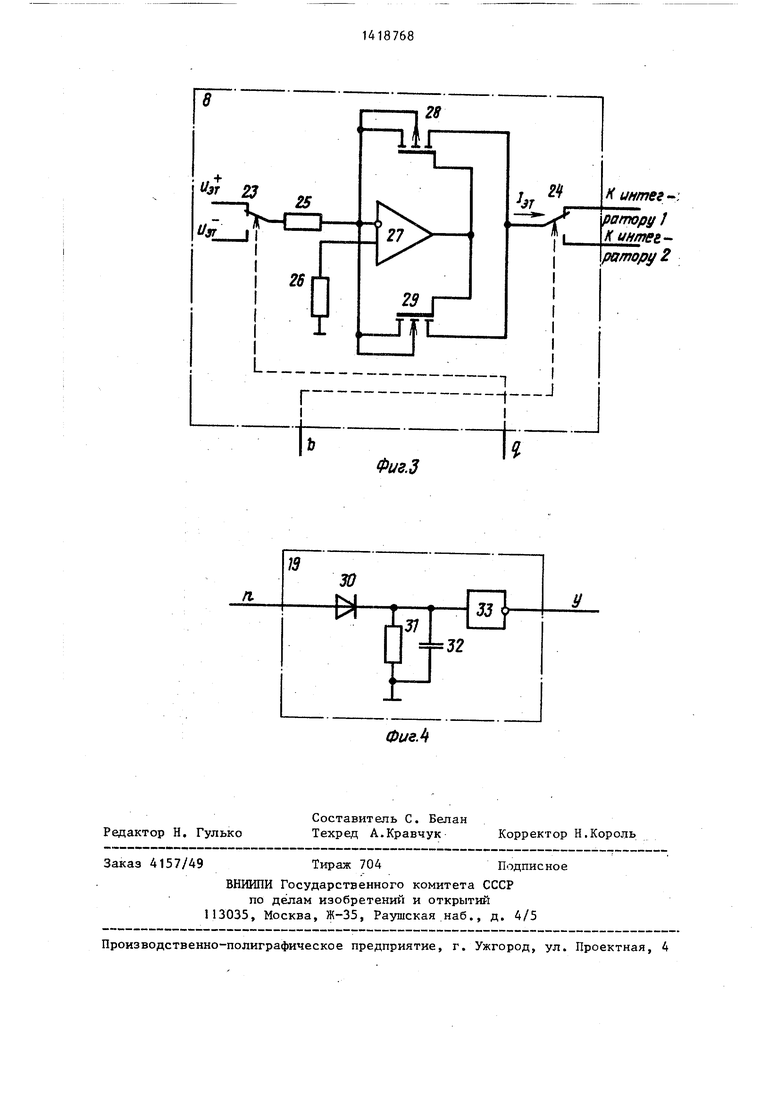

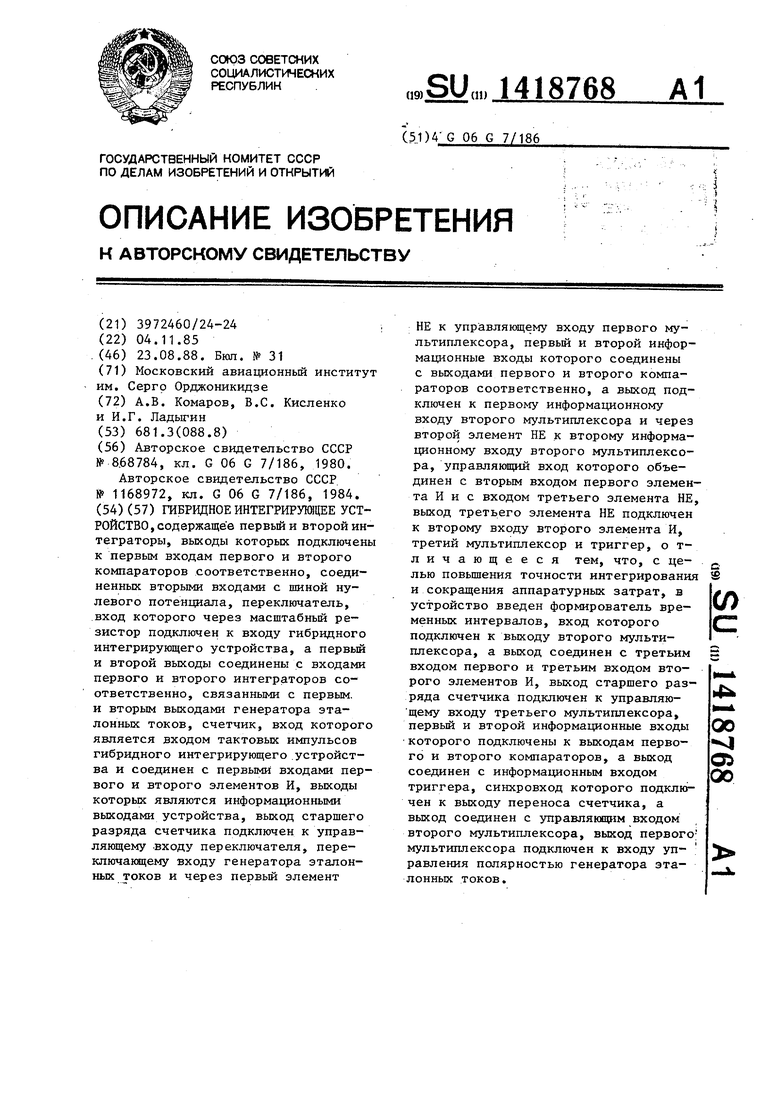

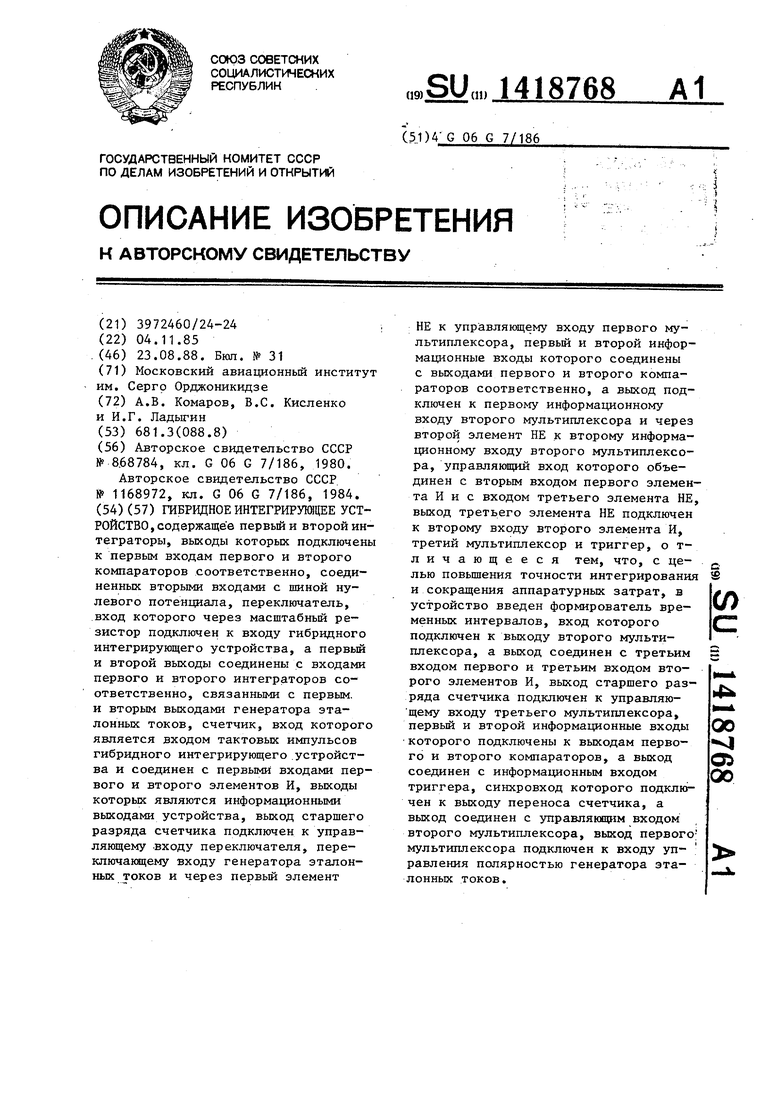

На фиг-.. 1 показана функциональная : схема предлагаемого устройства; на : фиг. 2 - эпюры напряжений, которые поясняют принцип действия устройст- I ва; на фиг. 3 - функциональная схема i генератора эталонных токов; на I фиг. 4 - формирователь временных ин- ; тервалов.

: Гибридное интегрирующее устройст- : во (фиг. 1) содержит первый 1 и вто- ; рой 2 интеграторы, выход каждого из : которых подключен к первому входу I соответственно первого 3 и второго 4 ; компараторов, переключатель 5, пер- вьй и второй выходы которого подклю- : чены к входам соответственно первого 1 и второго 2 интеграторов, масштаб- ньй резистор 6, первьй вьшод которог является информационным входом 7 устройства, генератор 8 эталонных токов, первый и второй выходы которого соединены с входами соответственно первого 1 и второго 2 интеграторов, счетчик 9, третий, первый и второй мультиплексоры 10-12, элементы НЕ 13 15, триггер 16, элементы И 17 и 18, формирователь 19 временных интервало ; тактовый вход 20 устройства, причем выходы элементов И 17 и 18 являются информационными выходами 21 и 22 I устройства,

; Генератор 8 эталонных токов (фиг. 3),содержит переключатели 23 и 24, резисторы 25 и 26, усилитель 27 постоянного тока, транзисторы 28 и 29.

Формирователь 19 временных интервалов (фиг. 4) содержит интегрирующую цепочку, выполненную на диоде 30, резисторе 31 и конденсаторе 32, и инвертор 33,

Устройство работает следующим образом.

В интеграторах 1 и 2 поочередно реализуется режим двойного интегрирования. Порядок интегрирования устанавливается с помощью логической переменной Ь, представляницей собой выход старшего (п-го) разряда счетчи

ка 9. При b О.в,:первом интеграторе 1 реализуется первое интегрирование (промежутки времени tj- t и tj - t-f, диаграмма d, фиг, 2), а во втором интеграторе 2 - второе интегрирование (промежутки времени tp - t , и tj - t/, диаграмма f, фиг, 1), Источник интегрируемого

0 напряжения при этом через масштабный резистор 6 и переключатель 5 подключен к входу первого интегратора 1, Первый выход генератора 8 эталонных токов обесточен, а второй активи5 зирован - в нем протекает эталонный ток того или иного направления (в зависимости от знака напряжения на выходе второго 2 интегратора), ко- торьй производит уменьшение напря0 жения (по абсолютной величине) до нуля на выходе второго интегратора 2, Величина 1)., которая представляет собой интеграл входного напряжения за время первого интегрирова5 ния, преобразуется при этом в импульс длительностью tg - t. Этот временной интервал заполняется тактовыми импульсами, число которых пропорционально интегралу входного

0 воздействия за время первого интегрирования . Эти импульсы появляются на выходе 22 отрицательного приращения, поскольку Uj 7 О, что является признаком отрицательного интегрируемого напряжения. Если Uj 0, то выходные импульсы появляются на выходе 21 положительного приращения (промежуток времени t5 t, диаграмма f, фиг, 2), При J) 1 в первом интеграторе 1 реализуется второе интегрирование (промежутки времени tj - tзи t, диаграмма d, фиг, 2), а во втором интеграторе 2 - первое интегрирование (промежутки времени t4 и t. т - tg, диаграмма

f, фиг, 2), Источник интегрируемого напряжения при этом через масштабньй резистор 6 и переключатель 5 подключен к входу второго интегратора 2, второй выход генератора 8 эталонных

0 токов обесточен. Первый выход генератора эталонных токов активизирован. Процесс второго интегрирования идентичен описанному вьше, аналогичному процессу во втором интеграторе, по5 этому в промежутке времени t - tj появляются импульсы отрицательного приращения интеграла входного напряжения, а в промежутке времени t-j - t

5

0

импульсы положительного приращения интеграла входного напряжения. Анализ принципа действия устройства показывает, что первый 1 и второй 2

интеграторы попеременно интегрируют входное воздействие, что способствует непрерывному интегрированию входного сигнала, и преобразуют приращения интеграла.входного напряжения в последовательности И1 тульсов, числ и знак которых (номер выхода) соответствуют величине приращения интеграла и знаку этого приращения. Для реализации описанного алгоритма работы устройства необходим управляв- мьм генератор 8 эталонных токов (фиг. 3). При g О переключатель 23 находится в верхнем положении, и на выходе генератора 8 эталонных токов формируется эталонный ток положительной полярности (фиг. 3, это направление показано стрелкой) . При g переключатель 23 находится в нижнем положении и на выходе генератора фор мируется эталонный ток отрицательной полярности. Ответвление эталонного тока к соответствующему интегратору осуществляется переключателем 24, причем при Ь О генератор 8 эталонных токов своим выходом подключен к второму интегратору 2, первый выход генератора разомкнут, а при Ь генератор 8 эталонных токов активизированным выходом подключен к первому интегратору 1, второй выход генератора разомкнут. Это позволяет при Ь О направить эталонный ток соответствующего знака в первый интегратор 1. При этом до момента t(t,) (диаграмма f, фиг. 2)происходит уменьшение (по абсолютной величине) до нулевого потенциала выходного напряжения второго интегратора 2. После режима второго интегрирования второй интегратор 2 переводится в режим стабилизации исходной точки входного потенциала, который заключается в принудительном удержании ее около уровня нулевого потенциала. Этот режим реализован подачей на вход интегратора эталонного тока, противоположного по знаку выходного напряжения данного интегратора. При этом на выходе второго интегратора 2 наблюдается пере- :менное напряжение (с постоянной составляющей вблизи уровня нулевого потенциала) , амплитуда и частота кото

10

f5

20

30

255

18768 ,

рого зависят от постоянной времени интегрирования данного интегратора, чувствительности компаратора и времени задержки распространения сигнала в схеме управления переключением направления эталонного тока. В это время в первом интеграторе 1 осуществляется первое интегрирование входного напряжения.

При Ь 1 во втором интеграторе 2 прекращается режим стабилизации и он переходит к первому интегрированию входного напряжения (вход второго интегратора 2 отключается переключателем 24 от генератора 8 эталонных токов и подключаются к информационному входу устройства переключателем 5). Первьй интегратор 1 сначала находится в режиме вто- рого интегрирования (моменты t to. t, - tg, диаграмма d, фиг. .2),

35

40

момент времени йэ, t произво 3

а в

дится в режим стабилизации исходной

точки входного потенциала.

Счетчик 9, мультиплексоры 10-12, элементы НЕ 13-15, триггер 16, элементы И 17 и 18, формирователь 19 временных интервалов предназначены для формирования трех режимов работы интеграторов: первого и второго интегрирования и режима стабилизации исходной точки и временного интервала, заполняемого синхроимпульсами, число и номер выхода которых определяют знак и интеграл входного напряжения.

Работа компараторов 3 и 4 может быть описана следующим уравнением:

,и.

1°

п,

если если

UBX 70;.

Временные диаграммы первого 3 и второго 4 компаратора (п и g соответственно, фиг. 3) поясняют принцип их работы.

Мультиплексор 10 и тригггер 16 предназначены для фиксации знака интегрируемого напряжения.

При Ь 0 происходит первое интегрирование в первом интеграторе 1. Первый компаратор 3 вьщеляет знаковую часть выходного сигнала, которая через мультиплексор 10 транслируется на информационный вход триггера 16.

Принцип работы мультиплексоров заключается в следующем: в случае.

51

когда на управляющем входе X О, на выход мультиплексора подключается I сигнал, поданный на первый информационный вход, когда X 1, на выходе сигнал, поданный на второй информа- ционньй вход. Напряжение, соответствующее знаку входного и интегрирующего напряжения, фиксируется в триггере 16 синхроимпульсом, поступающим с выхода переноса счетчика 9 в конце каждого цикла первого интегрирования При b 1 фиксируется знак интегрируемого во, втором интеграторе 2. Выходной сигнал триггера 16 определяет номер выхода, на котором появляются тактовые импульсы. При отрицательном интегрируемом входном напряжении (т 0) разрешается прохождение тактовых импульсов на второй выход 22 устройства, а при положительном (т 1) - на первый выход 21.

Мультиплексоры 11 и 12, элементы НЕ 14 и 15, формирователь 19 временных интервалов предназначены для формирования временного интервала, длительность которого пропорциональна интегралу входного напряжения. Мультиплексор 11 транслирует на свой выход сигналы, соответствующие режиму второго интегрирования ( длительность которого соответствует интегралу входного напряжения) и режиму стабилизации исходной точки поочередно первого 1 и второго 2 интеграторов.

Элемент НЕ 14 и мультиплексор 12 формируют сигнал, в котором временной интервал, соответствующий второму интегрированию в интеграторах, всегда принимает значение п О (моменты tg - t, t - tj, ts - tf, t.g , диаграмма n, фиг. 2). Когда интегрируется отрицательное входное напряжение, такой сигнал формируется естественным образом и передается на выход третьего мультиплексора 12. В случае пол.ожительного интегрируемого напряжения сигнал g инвертируется и через второй информационный вход третьего мультиплексора 12 транслируется на выход. Управляющий сигнал, учитывающий знак интегрируемого напряжения, снимается с . выхода триггера 16.

Формирователь 19 временных интервалов предназначен для формирования

86

временных ворот, т.е. единичных сигналов разрешения, пропорциональных интегралу от входного сигнала. Входной сигнал п (диаграмма п, фиг.2) состоит из информационного сигнала нулевого потенциала и помехового сигнала. Интегрирующая цепочка формирователя 19 из высокочастотного помехового сигнала формирует единичный сигнал. На вькоде инвертора 33 (элемент НЕ) получают сигнал, в котором информационная часть имеет потенциал логической 1, а помеховая - логи- .

ческого О. Таким образом, сформирован информационный сигнал, который поступает на элементы И 17 и 18 и определяет интервал, в течение которого на выход устройства поступают

тактовые импульсы С учетом знака интегрируемого напряжения.

Режим стабилизации исходной точки заключается в быстром изменении интегрируемого напряжения, при этом

выходное напряжение интеграторов колеблется около порога срабатьшания компаратора, равного нулевому потенциалу. Окончание второго интегриро- : вания сопровождается пересечением выходного напряжения интеграторов

2и 3 через уровень нулевого потенциала. На эту ситуацию компараторы

3и 4 реагируют изменением своего выходного сигнала. Данное изменение сигнала через мультиплексор 11 поступает на управлякиций вход переключателя 23 и меняет полярность эталонного напряжения, которое подается на вход того интегратора, в котором завершено второе интегрирование. В связи с изменением полярности входного сигнала выходное напряжение данного интегратора вновь начнет уменьшаться (по абсолютной величине) к нулевому потенциалу и вновь пересечет

порог срабатьшания компаратора, что вызовет повторное переключение полярности эталонного напряжения.

Преимущество предлагаемого устрой-, ства по сравнению с известным заключается в повьш1ении точностных характеристик интегрирования, полученных за счет устранения температурного и монтажного дрейфа исходного уровня первого интегрирования и сокращения аппаратурных затрат, связанных с изменением режимов работы ряда элементов

Its2l J ,

П1П11111111П11111|{|щц|||П1 /ш|}Ц| II nil III II тип

рЗчй

7U

,

р

| название | год | авторы | номер документа |

|---|---|---|---|

| Гибридное интегрирующее устройство | 1984 |

|

SU1168972A1 |

| Гибридное интегрирующее устройство | 1985 |

|

SU1316008A1 |

| Аналого-цифровое интергрирующее устройство | 1985 |

|

SU1339591A1 |

| Интегрирующее устройство | 1980 |

|

SU924721A1 |

| Способ измерения времени установления выходного сигнала цифроаналоговых преобразователей и устройство для его осуществления | 1987 |

|

SU1494216A1 |

| Интегратор | 1986 |

|

SU1401485A2 |

| Интегратор | 1976 |

|

SU641462A1 |

| Интегратор | 1988 |

|

SU1728871A1 |

| Интегрирующее устройство | 1981 |

|

SU1010616A1 |

| СПОСОБ ИЗМЕРЕНИЯ ПАРАМЕТРОВ ПОЛНОГО СОПРОТИВЛЕНИЯ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1994 |

|

RU2092861C1 |

е

/JL

,

IIIIIIIIIIIIHII IllllllllllUmi

ip d/ tz 3 9 S ts tj tg ty

Фиг. 2

r((i

гг

1Ш1(1111111111Г

-№

Ш1IflllllllllllllllliDlBlllllllllirr f

. n

tj tg ty

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Авторское свидетельство СССР | |||

| Гибридное интегрирующее устройство | 1984 |

|

SU1168972A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-08-23—Публикация

1985-11-04—Подача