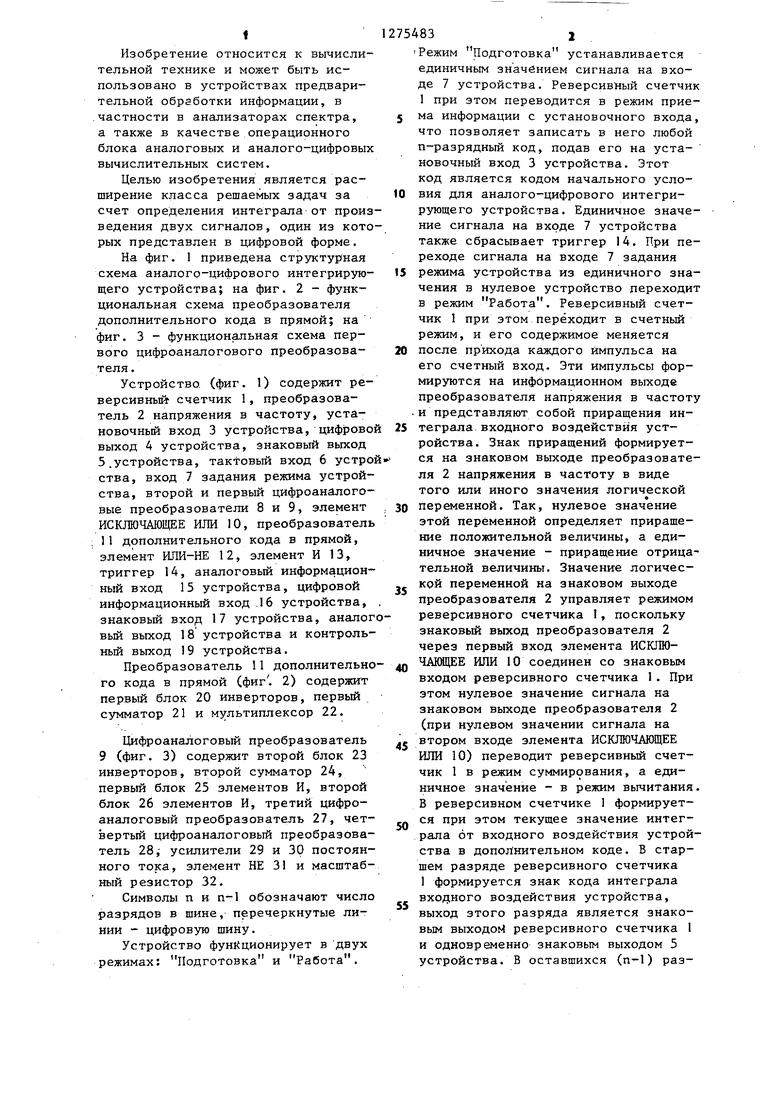

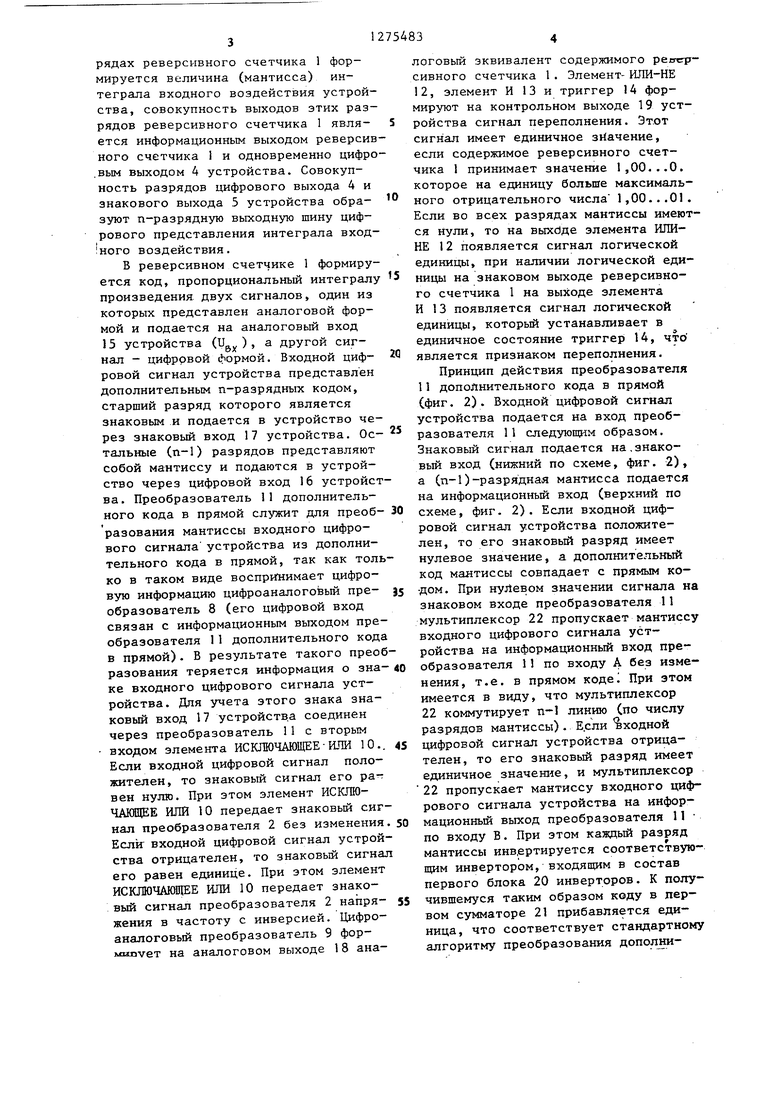

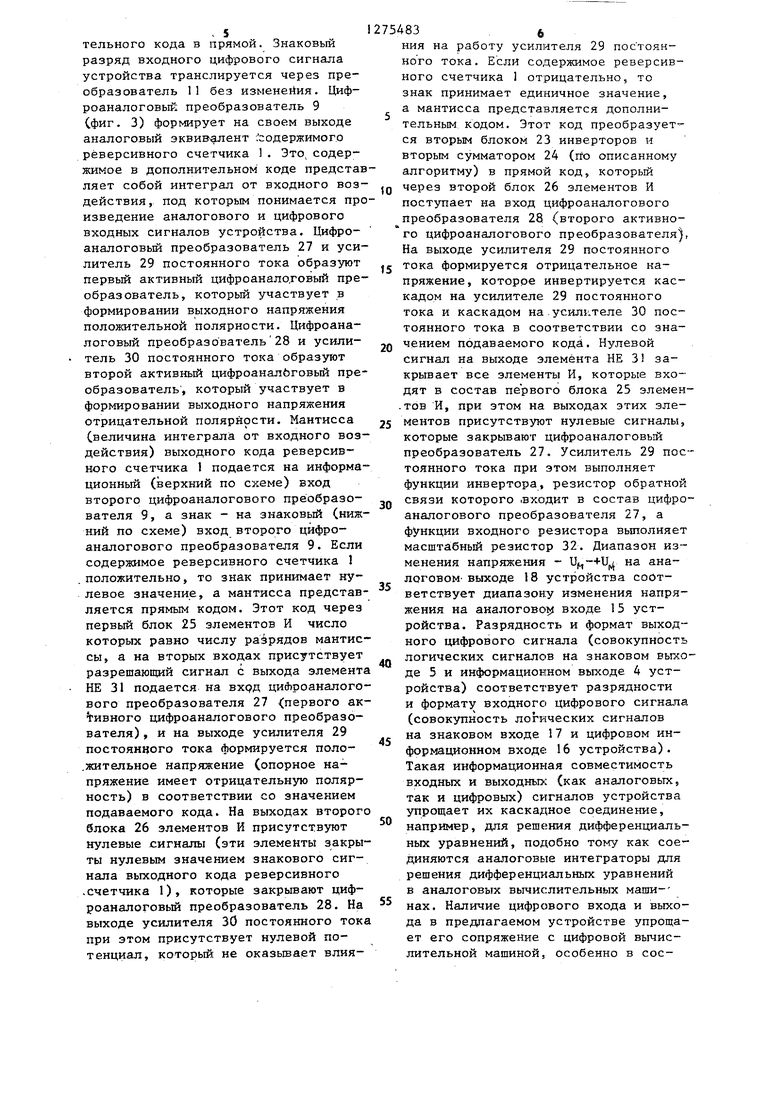

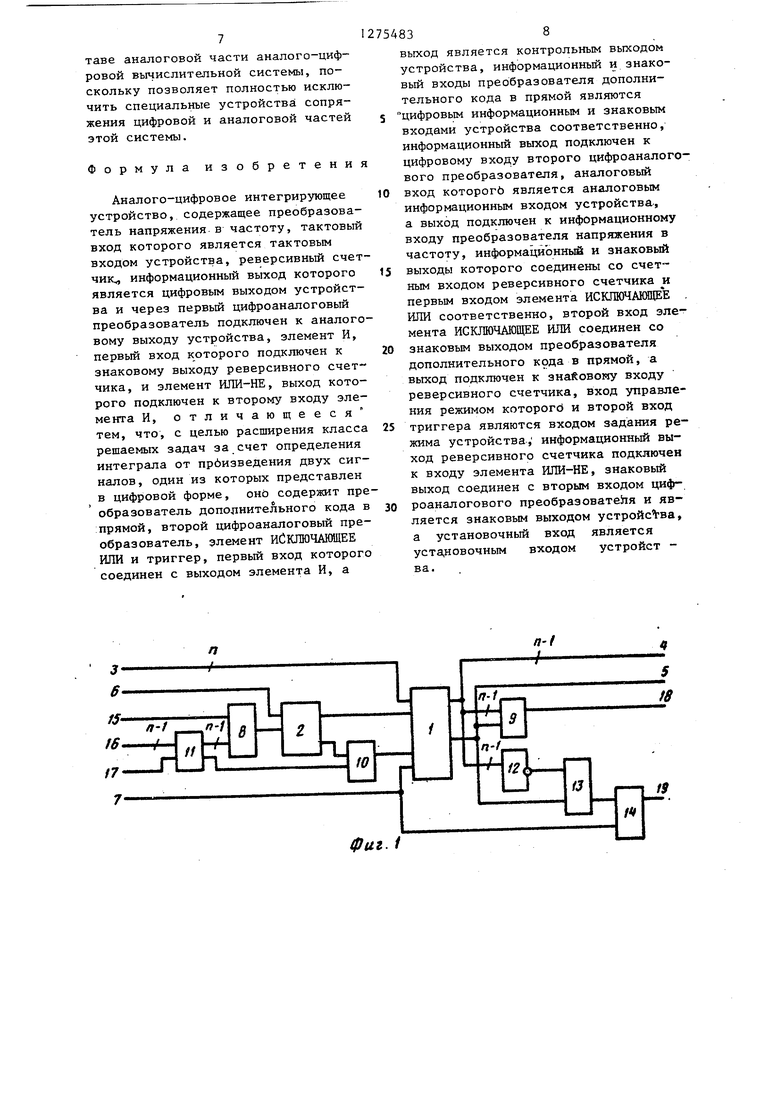

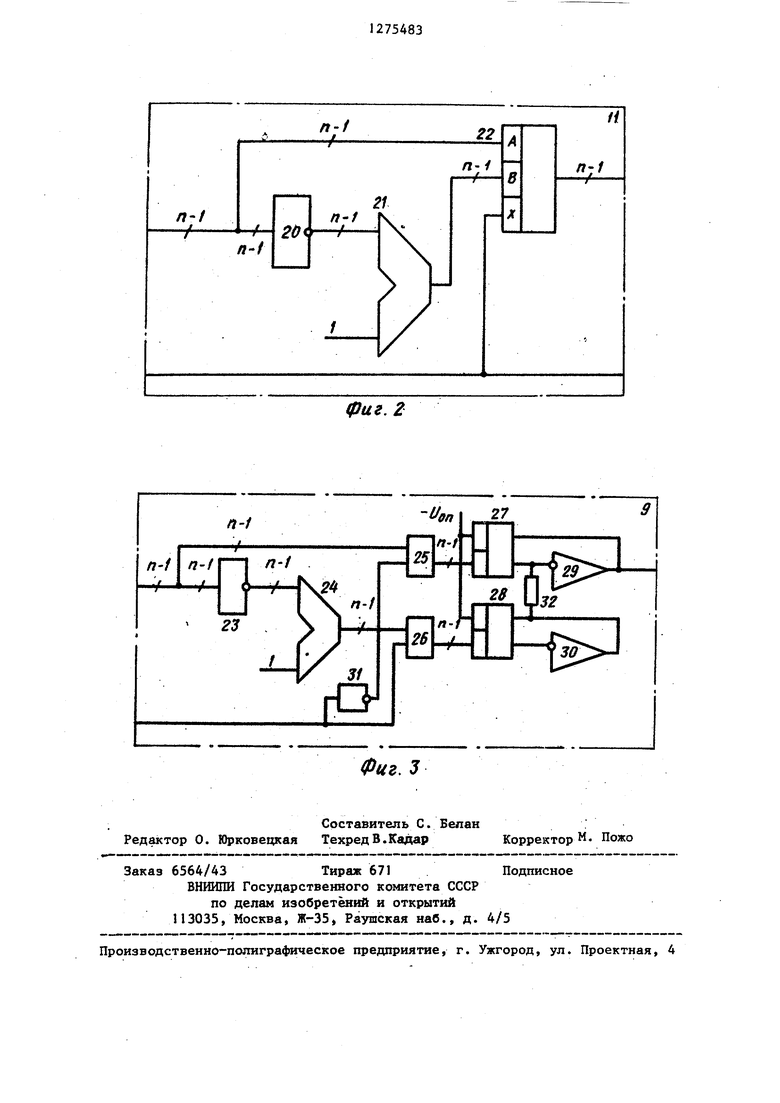

Изобретение относится к вычислительной технике и может быть использовано в устройствах предварительной обработки информации, в ,частности в анализаторах спектра, а также в качестве операционного блока аналоговых и аналого-цифровых вычислительных систем. Целью изобретения является расширение класса решаемых задач за счет определения интеграла от произ ведения двух сигналов, один из кото рых представлен в цифровой форме. На фиг. 1 приведена структурная схема аналого-цифрового интегрирующего устройства; на фиг. 2 - функциональная схема преобразователя дополнительного кода в прямой; на фиг. 3 - функциональная схема первого цифроаналогового преобразователя. Устройство (фиг. 1) содержит реверсивный счетчик 1, преобразователь 2 напряжения в частоту, установочньй вход 3 устройства, )Ово выход 4 устройства, знаковый выход 5 .устройства, тактовьй вход 6 устро ства, вход 7 задания режима устройства, второй и первый цифроаналоговые преобразователи 8 и 9, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 10, преобразователь : 11 дополнительного кода в прямой, элемент ИЛИ-НЕ 12, элемент И 13, триггер 14, аналоговый информационный вход 15 устройства, цифровой информационный вход .16 устройства, знаковый вход 17 устройства, анало вый выход 18 устройства и контроль ный выход 19 устройства. Преобразователь 11 дополнительн го кода в прямой Сфиг. 2) содержит первый блок 20 инверторов, первьА сумматор 21 и мультиплексор 22. Цифроаналоговый преобразователь 9 (фиг. 3) содержит второй блок 23 инверторов, второй сумматор 24, первый блок 25 элементов И, второй блок 26 элементов И, третий цифроаналоговый преобразователь 27, четвертый Цифроаналоговый преобразователь 28,- усилители 29 и 30 постоянного тока, элемент НЕ 3 и масштабный резистор 32. Символы п и п-1 обозначают число разрядов в шине, перечеркнутые линии - цифровую шину. Устройство функционирует в двух режимах: Подготовка и Работа. 832 Режим Подготовка устанавливается единичным значением сигнала на входе 7 устройства. Реверсивный счетчик 1 при этом переводится в режим приема информации с установочного входа, что позволяет записать в него любой п-разрядный код, подав его на установочный вход 3 устройства. Этот код является кодом начального условия для аналого-цифрового интегрирующего устройства. Единичное значение сигнала на входе 7 устройства также сбрасьгоает триггер 14. При переходе сигнала на входе 7 задания режима устройства из единичного значения в нулевое устройство переходит в режим Работа. Реверсивный счетчик 1 при этом переходит в счетный режим, и его содержимое меняется после прихода каждого импульса на его счетный вход. Эти импульсы формируются на информационном выходе преобразователя напряжения в частоту и представляют собой приращения интеграла входного воздействия устройства. Знак приращений формируется на знаковом выходе преобразователя 2 напряжения в частоту в виде того или иного значения логической переменкой. Так, нулевое значение этой переменной определяет прирашение положительной величины, а единичное значение - приращение отрицательной величины. Значение логической переменной на знаковом выходе преобразователя 2 управляет режимом реверсивного счетчика 1, поскольку знаковый выход преобразователя 2 через первый вход элемента ИСКПЮЧМНЦЕЕ ИЛИ 10 соединен со знаковым входом реверсивного счетчика 1. При этом нулевое значение сигнала на знаковом выходе преобразователя 2 (при нулевом значении сигнала на втором входе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 10) переводит реверсивный счетчик 1 в режим суммирования, а единичное значение - в режим вычитания. В реверсивном счетчике 1 формируется при этом текущее значение интеграла от входного воздействия устройства в дополнительном коде. В старшем разряде реверсивного счетчика 1 формируется знак кода интеграла входного воздействия устройства, выход этого разряда является знакоBbw выходом реверсивного счетчика I и одновременно знаковым выходом 5 устройства. В оставшихся (п-1) разрядах реверсивного счетчика 1 формируется величина (мантисса) интеграла входного воздействия устройства, совокупность выходов этих разрядов реверсивного счетчика 1 является информационным выходом реверсив ного счетчика 1 и одновременно цифро .вым выходом 4 устройства. Совокупность разрядов цифрового выхода 4 и знакового выхода 5 устройства образуют п-разрядную выходную шину цифрового представления интеграла входiHoro воздействия. В реверсивном счетчике 1 формируется код, пропорциональный интегралу произведения двух сигналов, один из которых представлен аналоговой формой и подается на аналоговый вход 15 устройства (и„ ), а другой сигнал - ЦИФРОВОЙ формой. Входной цифровой сигнал устройства представлен дополнительным п-разрядных кодом, старший разряд которого является знаковым и подается в устройство через знаковый вход 17 устройства. Ос- тальные (п-1) разрядов представляют собой мантиссу и подаются в устройство через цифровой вход 16 устройст ва. Преобразователь 11 дополнительного кода в прямой служит для преобразования мантиссы входного цифрового сигнала устройства из дополнительного кода в прямой, так как тол ко в таком виде воспринимает цифровую информацию цифроаналоговый преобразователь 8 (его цифровой вход связан с информационным выходом пре образователя 11 дополнительного код в прямой). В результате такого прео разования теряется информация о зна ке входного цифрового сигнала устройства. Для учета этого знака знаковый вход 17 устройства соединен через преобразователь 11 с вторым входом элемента ИСКЛЮЧАЮЩЕЕ-ИЛИ 10. Если входной цифровой сигнал положителен, то знаковый сигнал его ра-т вен нулю. При этом элемент ИСКЛЮЧАЮПЩЕ ИЛИ 10 передает знаковый сиг нал преобразователя 2 без изменения Если входной цифровой сигнал устрой ства отрицателен, то знаковый сигна его равен единице. При этом элемент ИСКЛЮЧАЮиЩЕ ИЛИ 10 передает знаковый сигнал преобразователя 2 напряжения в частоту с инверсией. Цифроаналоговый преобразователь 9 форMMDveT на аналоговом выходе 18 аналоговый эквивалент содержимого реаггрсивного счетчика 1. Элемент- ИЛИ-НЕ 12, элемент И 13 и триггер 14 формируют на контрольном выходе 19 устройства сигнал переполнения. Этот сигнал имеет единичное значение, если содержимое реверсивного счетчика 1 принимает значение 1,00...0. которое на единицу больше максимального отрицательного числа 1,00...01. Если во всех разрядах мантиссы имеются нули, то на выхс)де элемента ИЛИНЕ 12 появляется сигнал логической единицы, при наличии логической единицы на знаковом выходе реверсивного счетчика 1 на выходе элемента И 13 появляется сигнал логической единицы, который устанавливает в единичное состояние триггер 14, что является признаком переполнения. Принцип действия преобразователя 11 дополнительного кода в прямой (фиг. 2). Входной цифровой сигнал устройства подается на вход преобразователя 11 следующим образом. Знаковый сигнал подается на.знаковьш вход (нижний по схеме, фиг. 2), а (п-1)-разрядная мантисса подается на информационный вход (верхний по схеме, фиг. 2). Если входной цифровой сигнал устройства положителен, то его знаковый разряд имеет нулевое значение, а дополнительный код мантиссы совпадает с прямым кодом. При нулевом значении сигнала на знаковом входе преобразователя 11 мультиплексор 22 пропускает мантиссу входного цифрового сигнала устройства на информационный вход преобразователя 11 по входу А без изменения, т.е. в прямом коде При этом имеется в виду, что мультиплексор 22 коммутирует п-1 линию (по числу разрядов мантиссы). Если входной цифровой сигнал устройства отрицателен, то его знаковый разряд имеет единичное значение, и мультиплексор 22 пропускает мантиссу входного цифрового сигнала устройства на информационный выход преобразователя 11 по входу В. При этом каждый разряд мантиссы инв.ертируется соответствующим инвертором, входящим в состав первого блока 20 инверторов. К получившемуся таким образом коду в первом сумматоре 21 прибавляется единица, что соответствует стандартному алгоритму преобразования допол ш 5

тельного кода в прямой. Знаковый

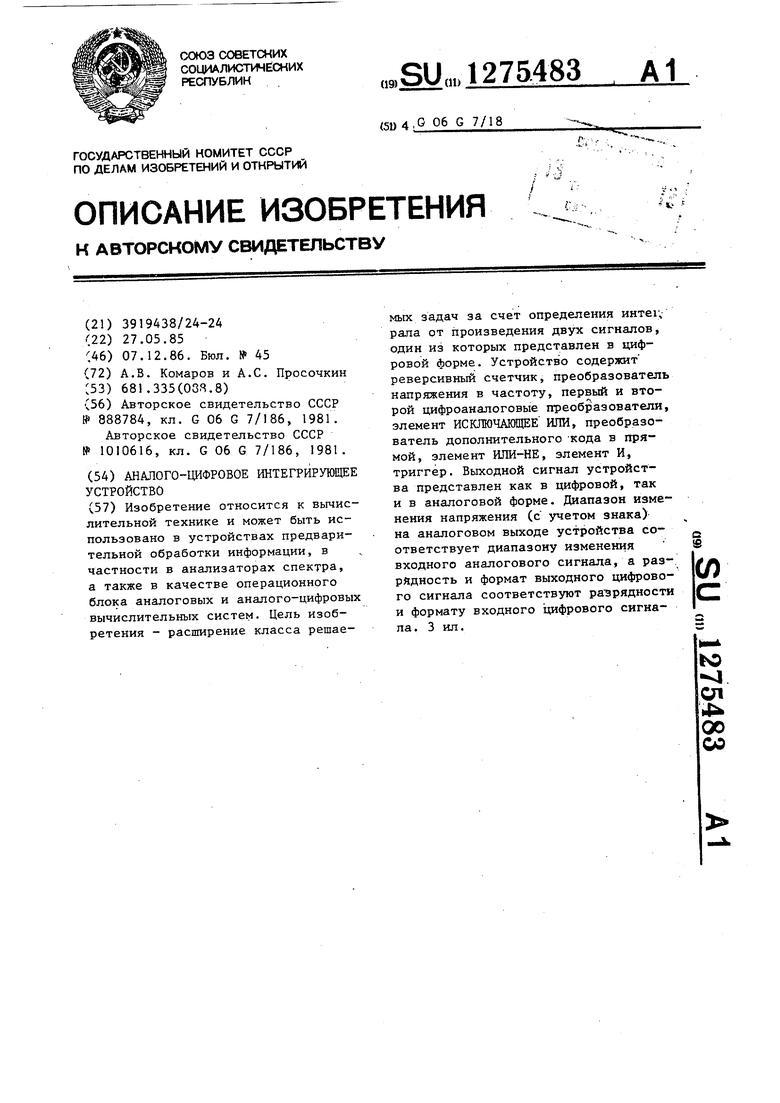

разряд входного цифрового сигнала устройства транслируется через преобразователь 11 без изменейия. Цифроаналоговый преобразователь 9 Сфиг. 3) формирует на своем выходе аналоговый эквивалент содержимого реверсивного счетчика 1. Это, содержимое в дополнительном коде представляет собой интеграл от входного воздействия, под которым понимается произведение аналогового и цифрового входных сигналов устройства. Цифроаналоговый преобразователь 27 и усилитель 29 постоянного тока образуют первый активный цифроанало.говый преобразователь, который участвует в формировании выходного напряжения положительной полярности. Цифроаналоговый преобразователь28 и усилитель 30 постоянного тока образуют второй активный цифроаналЪговый преобразователь, который участвует в формировании выходного напряжения отрицательной полярйости. Мантисса (величина интеграла от входного воздействия) выходного кода реверсивного счетчика 1 подается на информационный (верхний по схеме) вход второго цифроаналогового преобразователя 9, а знак - на знаковьй (нижний по схеме) вход второго цифроаналогового преобразователя 9. Если содержимое реверсивного счетчика 1 .положительно, то знак принимает нулевое значение, а мантисса представляется прямым кодом. Этот код через первьй блок 25 элементов И число которых равно числу разрядов мантиссы, а на вторых входах присутствует разрешающий сигнал t выхода элемента НЕ 31 подается на вхрд циЛроаналогового преобразователя 27 первого ак Гивного цифроаналогового преобразователя) , и на выходе усилителя 29 постоянного тока формируется поло.жительное напряжение (опорное напряжение имеет отрицательную полярность) в соответствии со значением подаваемого кода. На выходах второго блока 26 элементов И присутствуют нулевые сигналы (эти элементы закрыты нулевым значением знакового сигнала выходного кода реверсивного .счетчика 1), которые закрывают цифроаналоговый преобразователь 28. На выходе усилителя 30 постоянного тока при этом присутствует нулевой потенциал, который не оказьшает влия754836

ния на работу усилителя 29 постоянного тока. Если содержимое реверсивного счетчика 1 отрицательно, то знак принимает единичное значение, а мантисса представляется дополнительным, кодом. Этот код преобразует ся вторым блоком 23 инверторов и вторым сумматором 24 (rio описанному алгоритму) в прямой код, который

JQ через второй блок 26 элементов И поступает на вход дифроаналогового преобразователя 28 (второго активного цифроаналогового преобразователя), На выходе усилителя 29 постоянного

5 тока формируется отрицательное напряжение, которое инвертируется каскадом на усилителе 29 постоянного тока и каскадом на усилителе 30 постоянного тока в соответствии со знаQ чением подаваемого кода. Нулевой сигнал на выходе элемента НЕ 3 закрывает все элементы И, которые входят в состав первого блока 25 элемен.тов И, при этом на выходах этих зле5 ментов присутствуют нулевые сигналы, которые закрывают цифроаналоговьгй преобразователь 27. Усилитель 29 постоянного тока при этом выполняет функции инвертора, резистор обратной

Q связи которого входит в состав цифроаналогового преобразователя 27, а функции входного резистора выполняет масштабный резистор 32. Диапазон изменения напряжения - Un,-+Uj на аналоговом-выходе 18 устройства соответствует диапазону изменения напряжения на аналогово входе 15 устройства. Разрядность и формат выходного цифрового сигнала (совокупность логических сигналов на знаковом выходе 5 и информационном выходе 4 устройства) соответствует разрядности и формату входного цифрового сигнала (совокупность логических сигналов на знаковом входе 17 и цифровом информационном входе 16 устройства). Такая информационная совместимость входных и выходньш (как аналоговых, так и цифровых) сигналов устройства упрощает их каскадное соединение, например, для решения дифференциальных уравнений, подобно току как сов диняются аналоговые интеграторы для решения дифференциальных уравнений в аналоговых вычислительных маши-нах. Наличие цифрового входа и выхода в предлагаемом устройстве упрощает его сопряжение с цифровой вычислительной мащиной, особенно в составе аналоговой части аналого-цифровой вычислительной системы, поскольку позволяет полностью исключить специальные устройства сопряжения цифровой и аналоговой частей этой системы.

Формула изобретения

Аналого-цифровое интегрирующее устройство, содержащее преобразователь напряжения в частоту, тактовый вход которого является тактовым входом устройства, реверсивный счетчик информационный выход которого является цифровым выходом устройства и через первый цифроаналоговый преобразователь подключен к аналоговому выходу устройства, элемент И, первый вход которого подключен к знаковому выходу реверсивного счетчика, и элемент ИЛИ-НЕ, выход которого подключен к второму входу элемента И, отличающееся тем, что, с целью расширения класса рещаемых задач за счет определения интеграла от прбизведения двух сигналов, один из которых представлен в цифровой форме, оно содержит преобразователь дополнительного кода в прямой, второй цифроаналоговый преобразователь, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ и триггер, первый вход которого соединен с выходом элемента И, а

выход является контрольным выходом устройства, информационный и знаковый входы преобразователя дополнительного кода в прямой являются цифровьм информационным и знаковым входами устройства соответственно, информационный выход подключен к цифровому входу второго цифроаналогового преобразователя, аналоговый

вход которогЬ является аналоговым информационным входом устройства, а выход подключен к информационному входу преобразователя напряжения в частоту, информационный и знаковый

выходы которого соединены со счетным входом реверсивного счетчика и первым входом элемента ИСЮШНАЮПЩЕ . ИЛИ соответственно, второй вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен со

знаковым выходом преобразователя дополнительного кода в прямой, а выход подключен к знаковому входу реверсивного счетчика, вход управления режимом которогЬ и второй вход

триггера являются входом задания режима устройства, информационный выход реверсивного счетчика подключен к входу элемента ИЛИ-НЕ, знаковьй выход соединен с вторым входом цифроаналогового преобразователя к является знаковым выходом устройс ва, а установочный вход является устдновочным входом устройст ва.

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровое интегрирующее устройство | 1986 |

|

SU1376106A1 |

| Устройство для интегрирования функций | 1984 |

|

SU1242993A1 |

| Устройство для интегрирования функций | 1982 |

|

SU1070570A1 |

| Синхронный фильтр | 1983 |

|

SU1131028A1 |

| Синхронный фильтр | 1985 |

|

SU1317649A2 |

| СЛЕДЯЩИЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1989 |

|

RU2028731C1 |

| Следящий аналого-цифровой преобразова-ТЕль | 1979 |

|

SU828401A1 |

| Параллельно-последовательный п-разрядный аналого-цифровой преобразователь с автоматической коррекцией функции преобразования | 1988 |

|

SU1732471A1 |

| Анализатор спектра | 1977 |

|

SU732759A1 |

| Функциональный преобразователь | 1983 |

|

SU1166147A1 |

Изобретение относится к вычислительной технике и может быть использовано в устройствах предварительной обработки информации, в частности в анализаторах спектра, а также в качестве операционного блока аналоговых и аналого-цифровых вычислительных систем. Цель изобретения - расширение класса решаемых задач за счет определения рала от произведения двух сигналов, один из которых представлен в цифровой форме. Устройство содержит реверсивный счетчик, преобразователь напряжения в частоту, первый и второй цифроаналоговые преобразователи, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, преобразователь дополнительного -кода в прямой, элемент ИЛИ-НЕ, элемент И, триггер. Выходной сигнал устройства представлен как в цифровой, так и в аналоговой форме. Диапазон изменения напряжения (с учетом знака) на аналоговом выходе устройства соi ответствует диапазону изменения входного аналогового сигнала, а раз(Л рядность и формат выходного цифрового сигнала соответствуют разрядности и формату входного цифрового сигнала. 3 ил. IND сд 4 00 Од

a-f

4

| Авторское свидетельство СССР № 888784, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Интегрирующее устройство | 1981 |

|

SU1010616A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-12-07—Публикация

1985-05-27—Подача