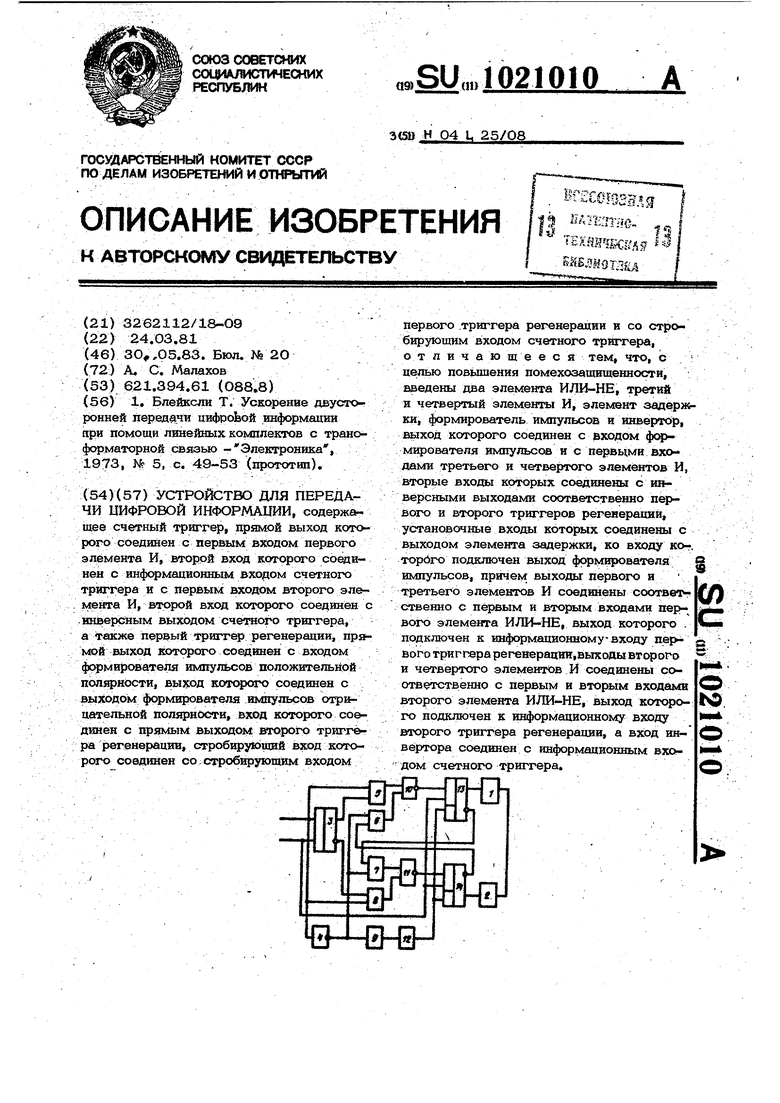

1 Изобретен 1е относится к технике электрической связи и может быть ис ;пользовано для передачи информации по проводным каналам связи, Извесл-но устройство для передачи цифровой инфсэрмации, содержащее счетный триггер, прямой выход которого соединен с первым входом первого элемента И, второй вход которого соединен с информационным входом счетного триггера и с первым входом второго элемента И, второй вход которого соединен с инверсным выходом счетного триггера, а также первый триггер регенерации, прямой выход которого соединен с входом формиро 1ателя импульсов положительной полярности, выход которого соединен с выходом формирователя импульсов отрицательной полярности, вход которого соединен с первым выходом второго триггера регенерации, стробирующий вход которого соединен со стробирующим входом первого триггера регенерации и со стробирующим входом счетнрго триггера Однако известное устройство имеет недостаточную помехозащищенность. Цель изобретения - повышение помехо защищенности. Указанная цель достигается тем, что в устройство для передачи цифровой информации, содержащее счетный триггер, прямой выход которого соединен с первым входом первого элемента И, второй вход которого соединен с информационным входом счетного триггера и с первым входом второго элемегега И, второй вход которого соединен с инверсным выходом счетного триггера, а также первый триггер регенерации, прямой выход которого соединен со входом формирователя импуль-40 го сов положительной полярности, выход которого соединен с выходом формирователя импульсов отрицательной полярности, вход которого соединен с прямым выходом второго триггера регенерации, стробирующий вход которого соединен со стробирующим входом первого триггера регенерации и со стробирз/ющим входом счетного тригх а, введень два элемента ИЛИ-НЕ, третий и четвертый элементы И, элемент задержки, формирователь импульсов и инвертор, выход которого соединен с входом формирователя импуль сов и с первыми входами третьего и четверто:го элементов И вторые входы которых соединены с инверсными выхо дами соответётвенно первого и второго триггеров регенерации, установочные входы которых соединены с выходом эле10мента задеряоси, ко входу которого подключен выход формирователя импульсов, причем выходы первого и третьего эле.ментов И соединены соответственно с первым и вторым входами первого эл&мента ИЛИ-НЕ, выход которого подключен к информационному входу первого триггера регенерации, выходы второго и четвертого элементов И соединены соответственно с первым и вторым входами второго элемента ИЛИ-НЕ, выход которого подключен к информационному входу второго триггера регенерации, а вход инвертора соединен с информацион. ным входом счетного триггера. На чертеже приведена структурная электрическая схема предлагаемого ycTV ройства. Устройство содержит формирователь 1 импульсов положительной полярности, формирователь 2 импульсов отрицательной полярности, счетный триггер 3, инвертор 4,- элементы И 5-8, формирователь 9 импульсов, элементы ИЛИ-НЕ Ю и 11, элемент 12 задержки, триггеры 13 и 14 регенерации. Устройство работает следующим образом. Первая единица исходной двоичной последовательности кодируется импульсом произвольной пол5фности, следующая за ней единица кодируется импульсом противоположной пол яркости, В начале нулевого тактового интервала, следующего за единичным, формируется короткий импульс противоположной полярности. Это достигается тем что отрицательньтй фронт тактовой последовательности, поступающей на стробирующий вход счетнотриггера 3, переводит его в противоположное состояние в Toiyt случае, когда на информационном входе этого трш , гера единица исходной двоичной последовательности. При этом, если счетный триггер 3 устанавливается в единичное состо5шие, на информационный вход первого триггера 13 регенерации поступает сигнал Логический ноль через первый элемент ИЛИ-НЕ 10 и первый элемент И 5, а на информационный вход второго триггера 14 регенерации поступает сигнал Логическая единица через элемент ИЛИ-НЕ и второй элемент И 8. Положительный фронт с робирующёй последовательности устанавливает триггеры 13 и 14 регенера ции в состо5шие, соответствующее сигналам на их информационных входах. Сигнал Логический прямого выхода первого триггера 13 регенерации включает подкроченный к нему форм:1фователь 1 импульсов положительной полярности и на выходе устройства формируется импульс положительной полярности. Если счетный триггер 3 устанавливает ся в нулевое состояние, на информационный вхоа. первого триггера 13 регенерации поступают сигнал Логическая еди ница через первый элемент ИЛИ-НЕ 10 и первый элемент И 5 , а на информационный вход второго триггера 14 регенерации поступает сигнал Логический ноль через второй элемент ИЛИ-НЕ 11 и элемент И 8. Положительный фронт стрсбируюшей лослеаовательности устанавливает трипге ры 13 V. 14 регенерации в состояние, соответствующее сигналам на их информапвощпых входах, ригнал Логический ноль Х5 прямого выхода второго трлггара 14 регенерации включает формирователь 2 импульсов отрща-тельной полярности и на выходе устройства формирует ся импульс отрицательной полярности. Ноль исходной двоичной последователь ности, поступающий аа информацион&лй вход счетного триггера 3, запрещает изменение его состояния при поступлеиии отрицательного фррнта стробирующей Яоследовательностя, а также запирает первый 5 и 8 элементы И Сигнал Логическая единица с выход инвертора 4 отврывает (третий) 6 и (четвертый) 7 элементы И. Через третий элемент И 6 и первый элемент ИЛИ-НЕ 1О на информационный вход первого триггера 13 регенерации поступает сигнал, соответствующий сос тоянию второго триггера регенерации через четвертый элемёЕКГ И 7 и второй эле мент ИЛИ-НЕ 11 поступает, сигнал, соответствующий сосот нш9 пе|Жого триггера 13 регенерации. В. результате пос1010 пе прихода на стробирующий вход тр агге- Р(% 13 и 14 рёгенерашш положительного; фронта стробирующей последовательное ги { состояоаие этих триггеров- изменяется на противоположное и если на предыдущем стробирукпием интер ше, на котором пе редавался символ логической единицы, был включен форм1фователь 1 импульсов положительной пол5фности, то на следукц щем стробирующем интервале, на крто|ррм передается символ Логического нуля, в начале стробнрующего интервала вкпкх . чается формирователь икшульсов отрицательной поляршхзти 2 и наоборот.; Положительный фронт о инвер- ,: тора 4 запускает ф6рм1фОвате1а 9 нмпупьг ссж., ; ..;. ,-. .: : Сформированный этим фсрмирователем импульс через элемент 12 задержки тупает на установочные входы триггеров 13 и 14 регенераций и устанавлиа Т; эти триггеры в единичное состояние. Сигналы Логический ноль с выхода первого и второго триггфов 13 и 14 регенерации включают формирователи им- ;: . пульсов лолозкительной 1 н отрицатель-i ной 2 полярности. Длительность коррек тирующего импульса в начале нулевого ; . интервала дается интервалом времени между положительным строб1фук щей последовательноста и моментом пск тупленйя импульса на установочные входи триггеров 13 и 14. Наличие корректирующего импульса ; позволяет уменадгать величину, искажения длительности единичного и следующего за ним нулевого символа для которызс ; эти искажения максимальны в случае отсутствия импульса коррекции. Такое уменьшение «ежрймвольной интерф еяции позволяет в полтора раза увеличить максимальную дсшуотньлую частоту п юдачи сообщений но той же линии связи.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой широтно-импульсный модулятор | 1988 |

|

SU1647881A2 |

| Устройство для синхронизации блоков памяти | 1986 |

|

SU1439566A1 |

| Цифровой регулятор угловой скорости дугостаторного асинхронного двигателя | 1984 |

|

SU1203481A1 |

| Устройство для контроля одноразрядных блоков памяти | 1988 |

|

SU1640743A1 |

| Устройство для измерения и регулирования соотношения скоростей | 1985 |

|

SU1364993A1 |

| Устройство для ввода информации | 1987 |

|

SU1509914A1 |

| Устройство для ввода информации | 1984 |

|

SU1200274A2 |

| Детектор @ -зубца электрокардиосигнала | 1984 |

|

SU1260004A1 |

| Цифровой широтно-импульсный модулятор | 1987 |

|

SU1478316A1 |

| Аналого-цифровой преобразователь | 2017 |

|

RU2646356C1 |

УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ ЦИФРОВОЙ ИНФОРМАЦИИ, содержащее счетный триггер, прямой выход которого соединен с первым входом первого элемента И, второй вход которого соедииен с инфс мационным входом счетного триггера и с первым входом второго элемента И, второй вход которого соединен с . ищ ерсным выходом счетного триггера, а также первый тригг регенерации, прямой выход которого соединен с входом формирователя импульсов положительной полезности, выход которого соединен с выходом формирователя импульсов отрицательной пол$фнйсти, вход которого соединен с щ)ямым выходом второго триггера регенерации, стробирующий вход которого соединен со стробщзующим входом первого триггера регенерации и со стробирующим входом счетного триггера, от л и ч а ю щ е е с я тем, что, с целью повышения помехозащищенности, введены два элемента ИЛИ-НН, третий и четвертый элементы И, элемент задержки, формирователь импульсов и инвертор, j ixofl которого соединен с входом формирователя импульсов и с первыми вхо дами третьего и четвертого элементов И, вторые входы которых соединены с инверсными выходами соответственно первого и второго триггеров регет ераций, установочные вхо/ц 1 которых соединены с выходом элемента задержки, ко входу ког. торОго подключен выход формирователя S импульсов, причем выходы первого и третьего элементов И соединены соответгиГЛ ственно с первым и вторым входами |ш1м вогчэ элемента ИЛИ-НЕ, выход которого р подключен к информационному входу пер д -. вого триггера рёгенерац|га,выходы второго и четвертого элементов И соединены соответственно с первым и вторым входами второго элемента И ЛИ-НЕ, выход tvD. го подключен к информационному входу второго триггера регенерации, а вход инвертора соединен с информационным входом счетного триггера.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Способ смешанной растительной и животной проклейки бумаги | 1922 |

|

SU49A1 |

Авторы

Даты

1983-05-30—Публикация

1981-03-24—Подача