w

Ј

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля интегральных микросхем оперативной памяти | 1984 |

|

SU1249588A1 |

| Устройство для контроля оперативной памяти | 1991 |

|

SU1833919A1 |

| Логический анализатор | 1985 |

|

SU1283771A1 |

| Устройство для сопряжения между абонентами | 1987 |

|

SU1411759A1 |

| Устройство для контроля блоков памяти | 1985 |

|

SU1251187A1 |

| Устройство для контроля оперативной памяти | 1983 |

|

SU1295455A1 |

| Устройство для диагностического контроля оперативной памяти | 1991 |

|

SU1807525A1 |

| Устройство для выделения кадрового синхронизирующего слова | 1989 |

|

SU1704146A1 |

| Устройство для контроля логических блоков | 1985 |

|

SU1283769A1 |

| Устройство для регистрации результатов контроля | 1985 |

|

SU1406596A1 |

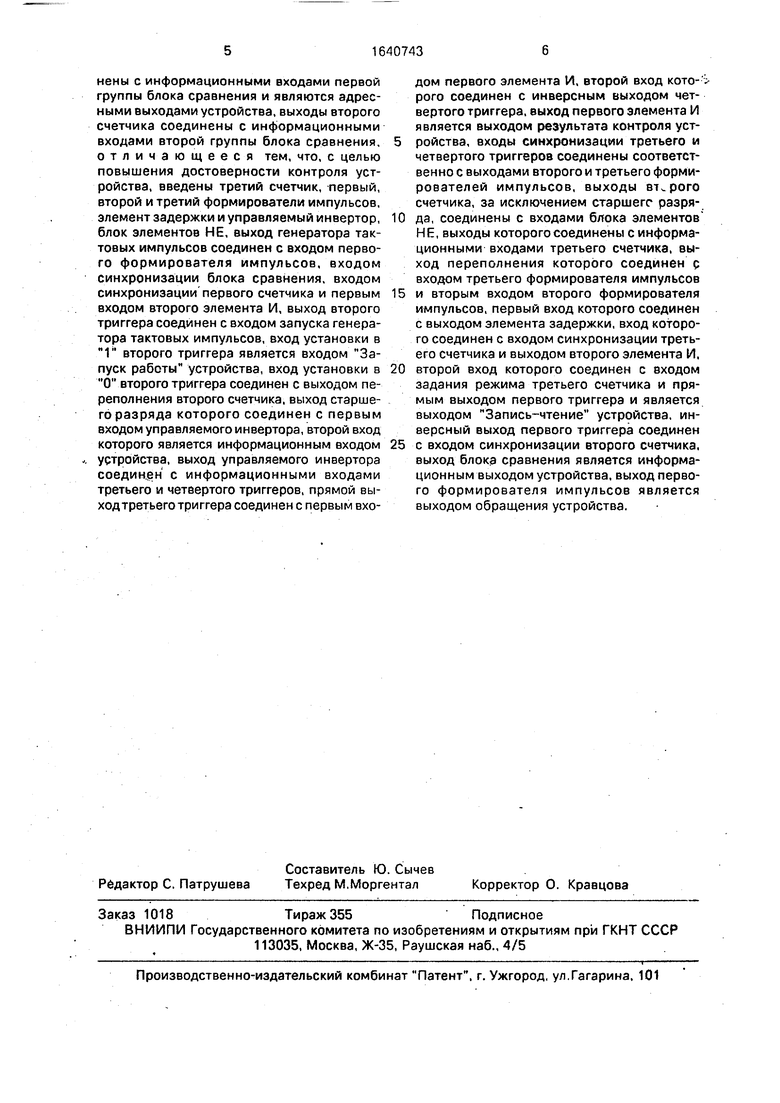

Изобретение относится к автоматике и вычислительной технике и может быть использовано для функционального контроля интегральных микросхем памяти. Цель изобретения - повышение достоверности контроля устройства. Устройство для контроля одноразрядных блоков памяти содержит счетчики 1 - 3, блок 4 сравнения, триггеры 5-8, генератор 9, элементы И 10, 11, управляемый инвертор 12, формирователи 13-15 импульсов, блок элементов НЕ 16, блок 17 индикации, элемент 18 задержки. 1 ил.

а

.N о

2

00

Изобретение относится к автоматике и вычислительной технике и может быть использовано для функционального контроля интегральных микросхем памяти.

Цель изобретения - повышение достоверности контроля устройства.

На чертеже приведена схема устройства для контроля интегральных микросхем памяти.

Устройство содержит первый 1. второй 2 и третий 3 счетчики, блок 4 сравнения, первый 5, второй 6, третий 7 и четвертый 8 триггеры, генератор 9 тактовых импульсов, первый 10 и второй 11 элементы И, управляемый инвертор 12, первый 13, второй 14, третий 15 формирователи импульсов, блок элементов НЕ 16, блок 17 индикации, элемент 18 задержки, вход 19, проверяемая микросхема 20.

Устройство работает следующим образом.

В исходном состоянии счетчики 1-3, триггеры 5, 6, 8 обнулены, а триггер 7 установлен в единицу (цепи установки для упрощения не показаны).

Блок 4 сравнения осуществляет поразрядно сравнение состояния счетчика 1 адреса и счетчика 2 кадров. Результат сравнения записывается в проверяемую микросхему 20 по адресу, определяемому счетчиком 1 адреса.

Работа устройства начинается при подаче на вход 19 запуска устройства единичного импульса. Триггер 6 устанавливается в единицу и разрешает работу генератора 9, импульс с генератора 9 передним фронтом стробирует блок 4 сравнения, единица в счетчик 1 добавляется по его заднему фронту, вследствие чего сначала происходит сравнение состояния счетчика 1 адреса и счетчика 2 кадров, а затем появляется новый адрес.

Так как в начале работы оба счетчика 1 и 2 обнулены, в результате сравнения блок 4 сравнения выдает логическую единицу, которая записывается в испытуемую микросхему 20 по нулевому адресу.

В дальнейшем, по мере поступления импульсов с генератора 9, постоянно имеет место несравнение, и по всем адресам в проверяемую микросхему 20 записываются нули. Импульс переполнения счетчика 1 адреса устанавливает триггер 5 в единицу. По фронту установки в единицу в счетчик 3 записывается инверсное значение счетчика 2 кадров, далее происходит считывание информации по всем адресам со сравнением, через открытый элемент И 11 импульсы поступают на счетный вход счетчика 3. Первым же импульсом счетчик 3

переполняется, формирователь 13 вырабатывает импульс, который фиксирует в триггере 7 единственную единицу, прочитанную по нулевому адресу из испытуемой микросхемы 20 Формирователь 14 импульса не вырабатывает, так как его работу блокирует импульс переполнения со счетчика 3. Элемент 18 задержки задерживает передний фронт импульса генератора 9 чтобы он по0 падал на время действия импульса переполнения со счетчика 3. При дальнейшем поступлении импульсов через элемент И 11 формирователь 14 стробирует на триггере 8 нулевую информацию из испытуемой мик5 росхемы 20.

Блок 17 индикации содержит триггер, который устанавливается в состояние Брак по перепаду из единицы в нуль на входе, и светодиод. Запись информации в

0 триггер 8 продолжается до переполнения счетчика 1 адреса. Сигнал переполнения счетчика 1 устанавливает триггер 5, выполненный как D-триггер со счетным входом, в ноль, в результате чего закрывается эле5 мент И 11, а к содержимому счетчика 2 прибавляется единица. Начинается работа устройства для следующего кадра. Теперь единица записывается в испытуемую микросхему не по нулевому, а по первому адре0 су. Работа устройства для следующих кадров аналогична.

При каждом кадре работы устройства при записи информации по 2N адресам в микросхему 20 записывается одна единица

5 и 2 нулей. Записанная единица фиксируется триггером 7, записанные нули - триггером 8. По исполнении 2 кадров, включающих запись и чтение со сравнением, в (N+1) - М разряде счетчика 2 кадров

0 появляется единица. Под воздействием этой единицы блок 4 сравнения и управляемый инвертор 12 начинают инвертировать информацию, в дальнейшем повторяется цикл работы устройства по проверке микро5 схемы 20 записью и чтением ноля на фоне всех единиц по всем адресам. После окончания всех кадров второго цикла счетчик 2 кадров переполняется, и сигнал переполнения со счетчика 2 устанавливает триггер 6 в

0 ноль. Если за время проверки, составляющее 22N+2 Т, где Т - период генератора 9, не сработал блок 17 индикации, то испытуемая микросхема 20 исправна.

Формула изобретения

5 Устройство для контроля одноразрядных блоков памяти, содержащее генератор тактовых импульсов, первый и второй элемент И, первый, второй, третий и четвертый триггеры, первый и второй счетчики, блок сравнения, выходы первого счетчика соединемы с информационными входами первой группы блока сравнения и являются адресными выходами устройства, выходы второго счетчика соединены с информационными входами второй группы блока сравнения, отличающееся тем, что, с целью повышения достоверности контроля устройства, введены третий счетчик, первый, второй и третий формирователи импульсов, элемент задержки и управляемый инвертор, блок элементов НЕ, выход генератора тактовых импульсов соединен с входом первого формирователя импульсов, входом синхронизации блока сравнения, входом синхронизации первого счетчика и первым входом второго элемента И, выход второго триггера соединен с входом запуска генератора тактовых импульсов, вход установки в 1 второго триггера является входом Запуск работы устройства, вход установки в О второго триггера соединен с выходом переполнения второго счетчика, выход старшего разряда которого соединен с первым входом управляемого инвертора, второй вход которого является информационным входом устройства, выход управляемого инвертора соединен с информационными входами третьего и четвертого триггеров, прямой выход третьего триггера соединен с первым входом первого элемента И, второй вход кото- i рого соединен с инверсным выходом четвертого триггера, выход первого элемента И является выходом результата контроля устройства, входы синхронизации третьего и четвертого триггеров соединены соответственно с выходами второго и третьего форми- рователей импульсов, выходы второго счетчика, за исключением старшего разряда, соединены с входами блока элементов НЕ, выходы которого соединены с информационными входами третьего счетчика, выход переполнения которого соединен с входом третьего формирователя импульсов

и вторым входом второго формирователя импульсов, первый вход которого соединен с выходом элемента задержки, вход которого соединен с входом синхронизации третьего счетчика и выходом второго элемента И.

второй вход которого соединен с входом задания режима третьего счетчика и прямым выходом первого триггера и является выходом Запись-чтение устройства, инверсный выход первого триггера соединен

с входом синхронизации второго счетчика, выход блока сравнения является информационным выходом устройства, выход первого формирователя импульсов является выходом обращения устройства.

| Устройство для контроля интегральных микросхем оперативной памяти | 1984 |

|

SU1249588A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Устройство для контроля оперативных накопителей | 1983 |

|

SU1103292A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1991-04-07—Публикация

1988-08-25—Подача