00 CD СП CD 0

Изобретение относится к вычислительной технике и может быть использовано в блоках синхронизации дискретных устройств.

Целью изобретения является повышение достоверности работы.

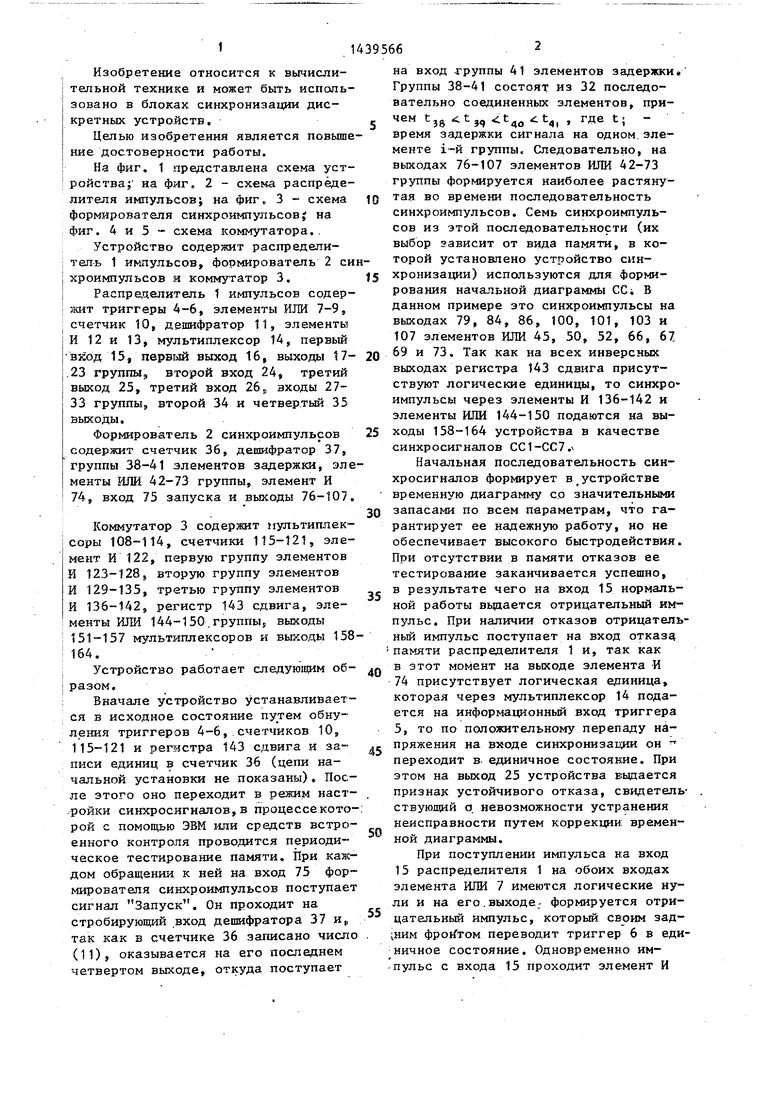

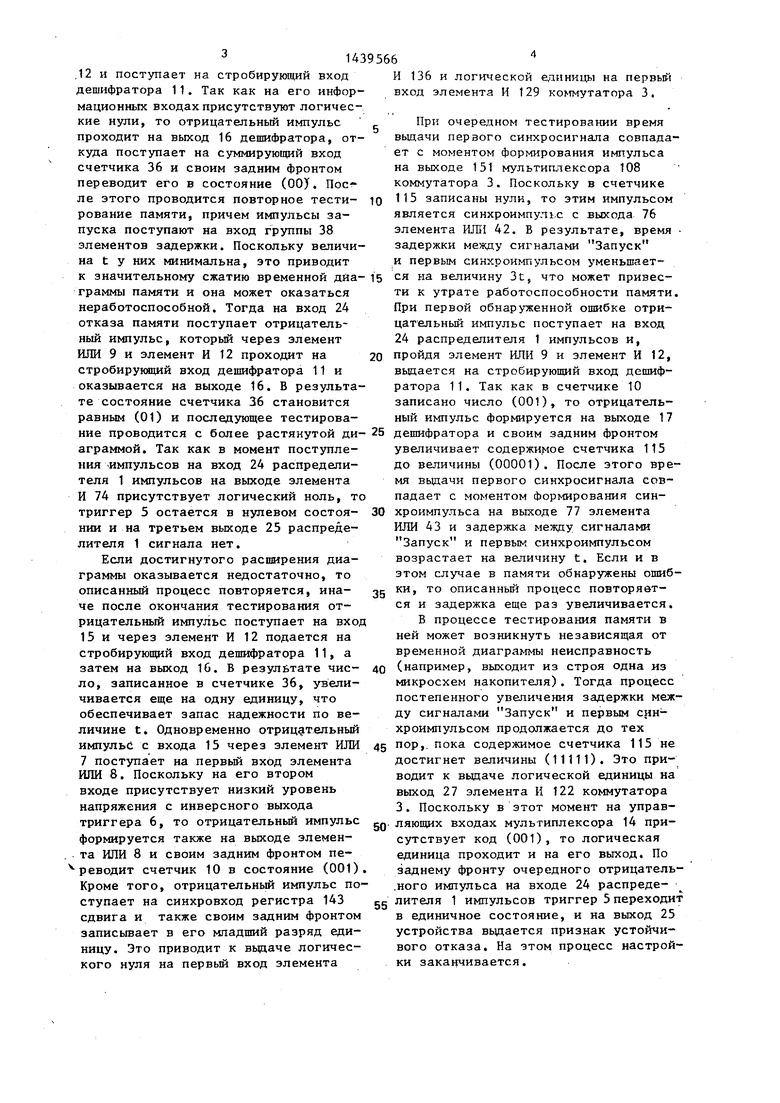

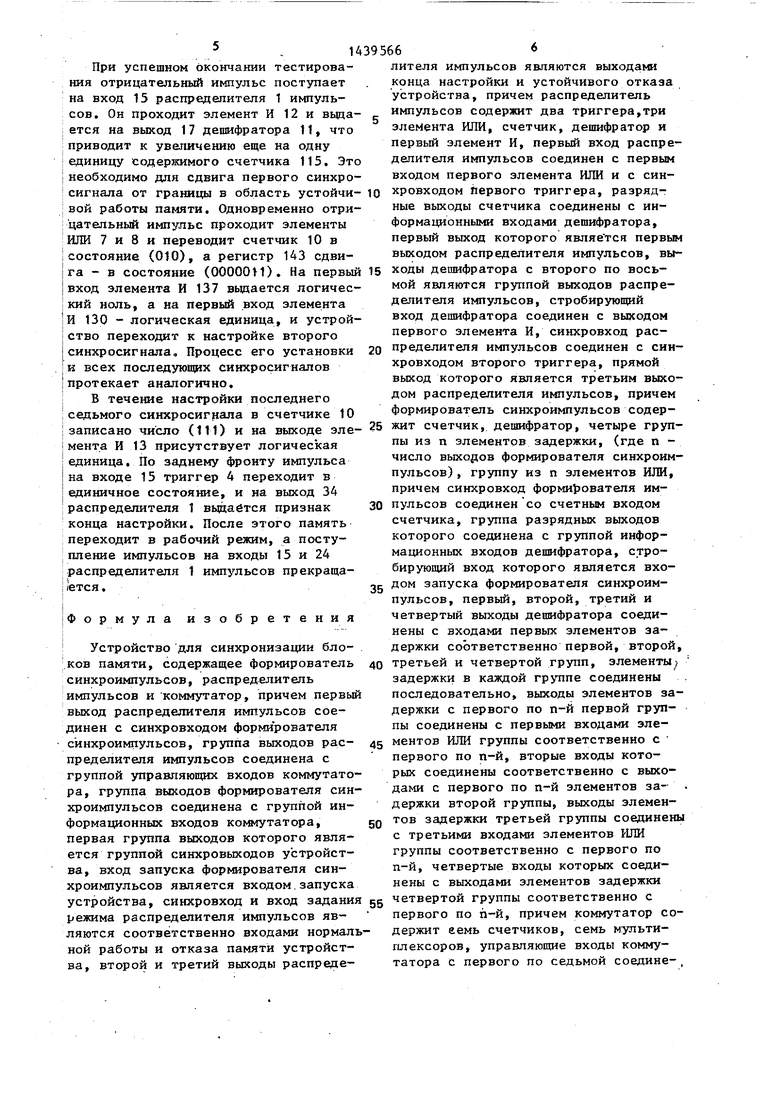

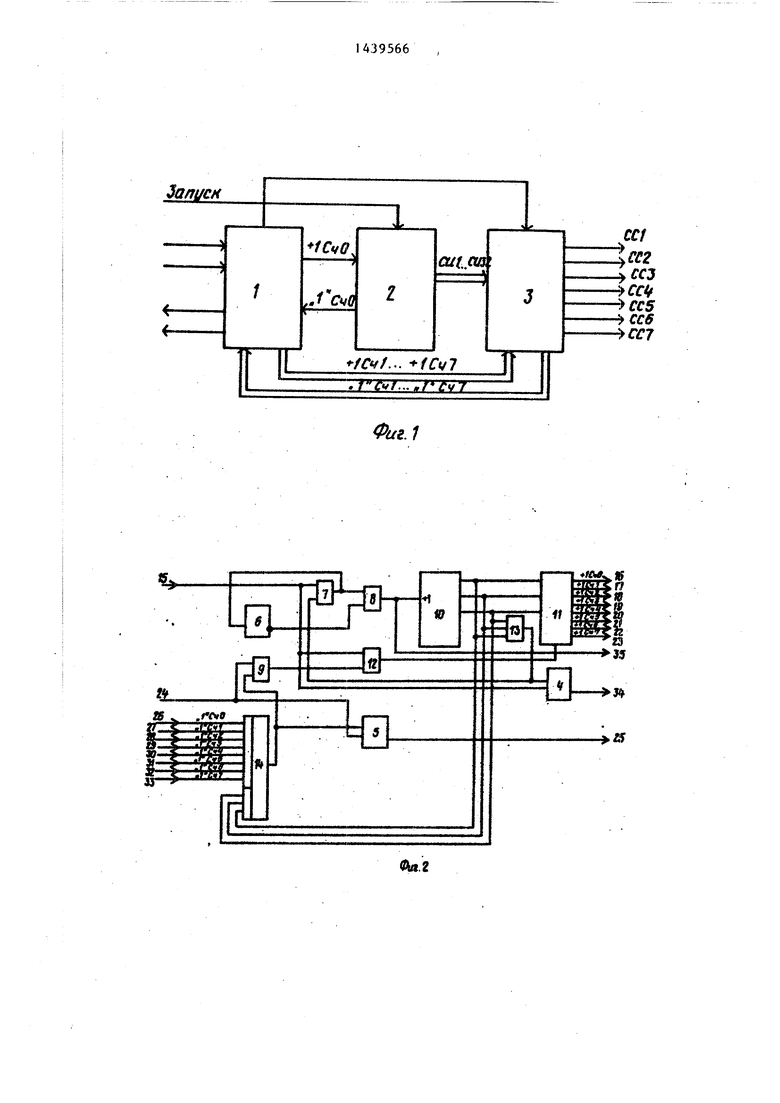

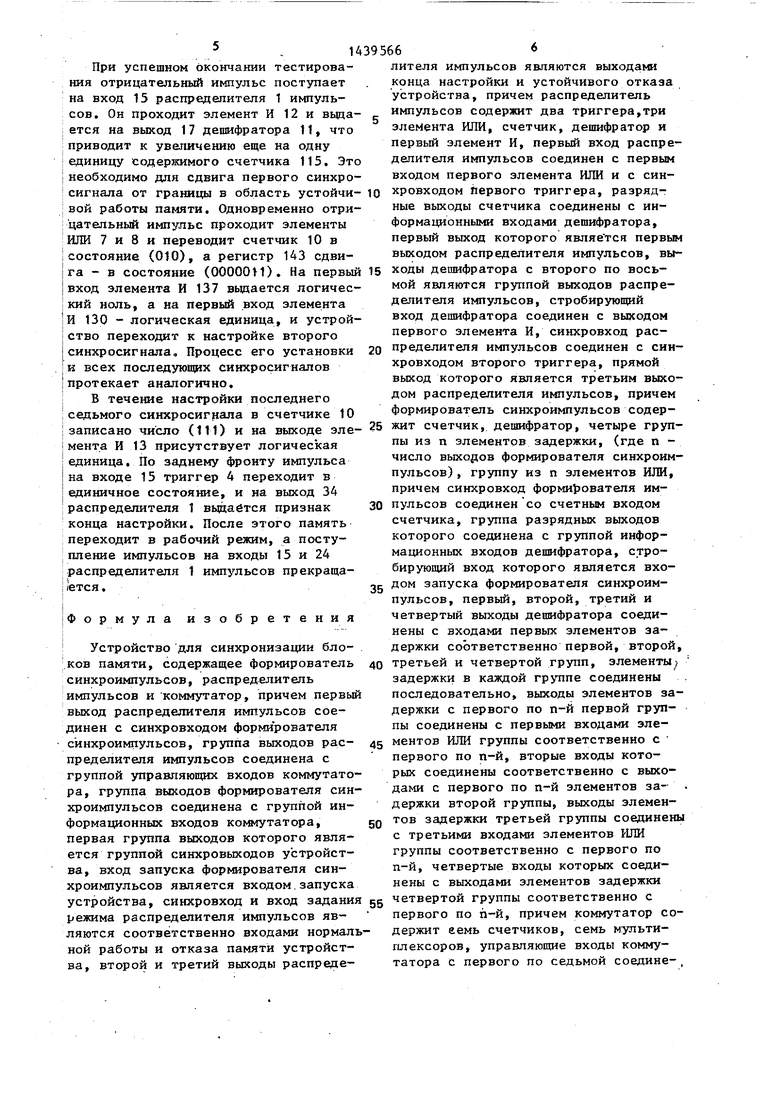

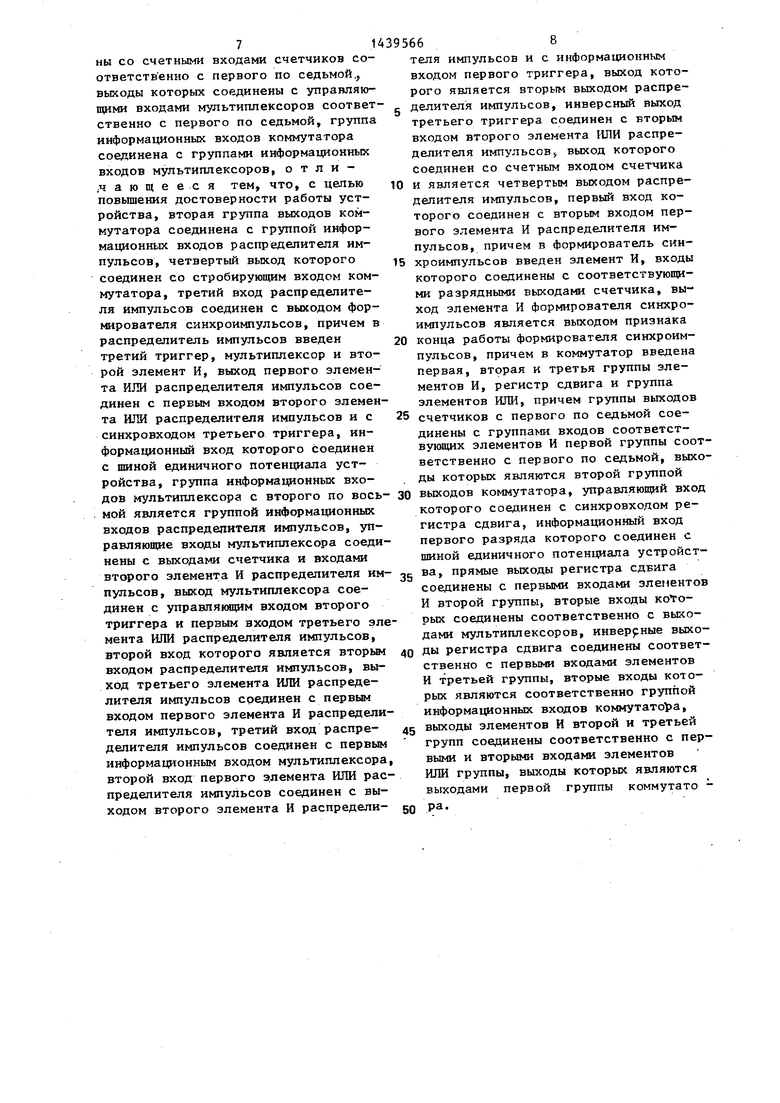

На фиг. 1 представлена схема устройства; на фиг. 2 - схема распределителя импульсовi на фиг 3 - схема формирователя синхроимпульсов на фиг. 4 и 5 - схема коммутатора.,

Устройство содержит распределитель 1 импульсов, формирователь 2 си хроимпульсов и коммутатор 3.

Распре,цвлитель 1 импульсов содержит триггеры 4-6, элементы ИЛИ 7-9, счетчик 10, дешифратор 11, элементы И 12 и 13, мультиплексор 14, первый вкод 15, первг 1й выход 16, выходы 17- .23 группы, второй вход 24, третий выход 25, третий вход 26„ входы 27- 33 группы, второй 34 и четвертый 35 выходы.

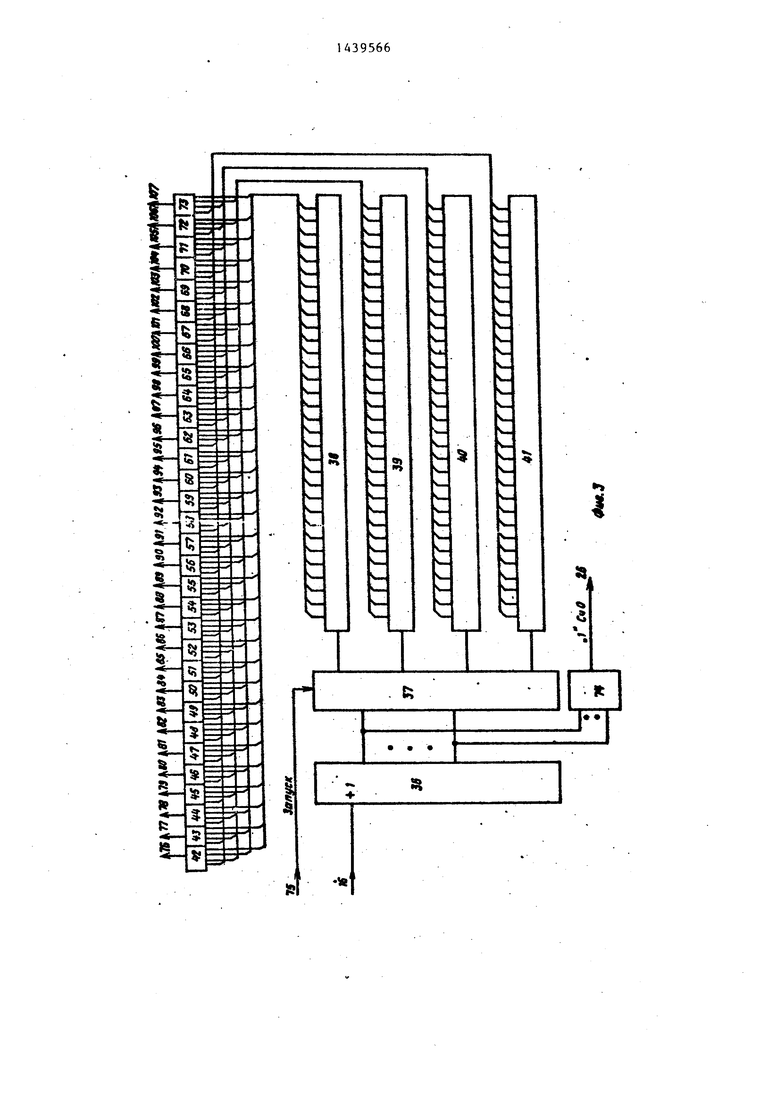

Формирователь 2 синхроимпульсов содержит счетчик 36, дешифратор 37, группы 38-41 элементов задержки, элементы ИЛИ 42-73 группы, элемент И 74, вход 75 запуска и выходы 76-107.

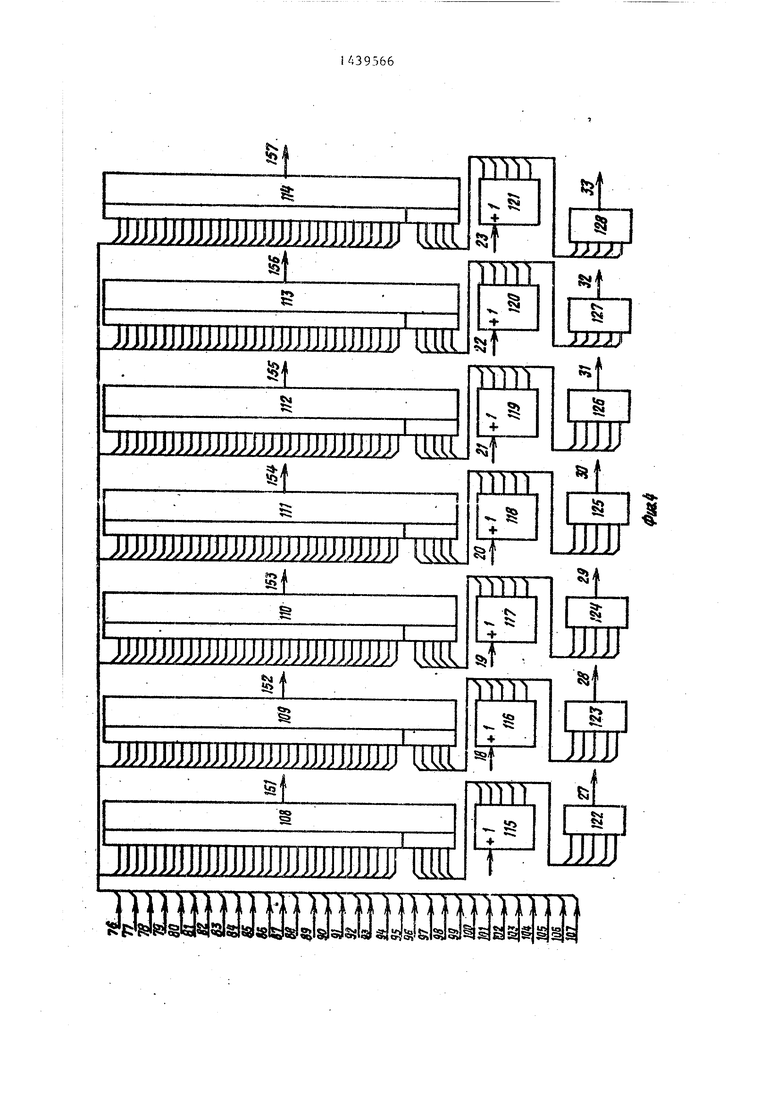

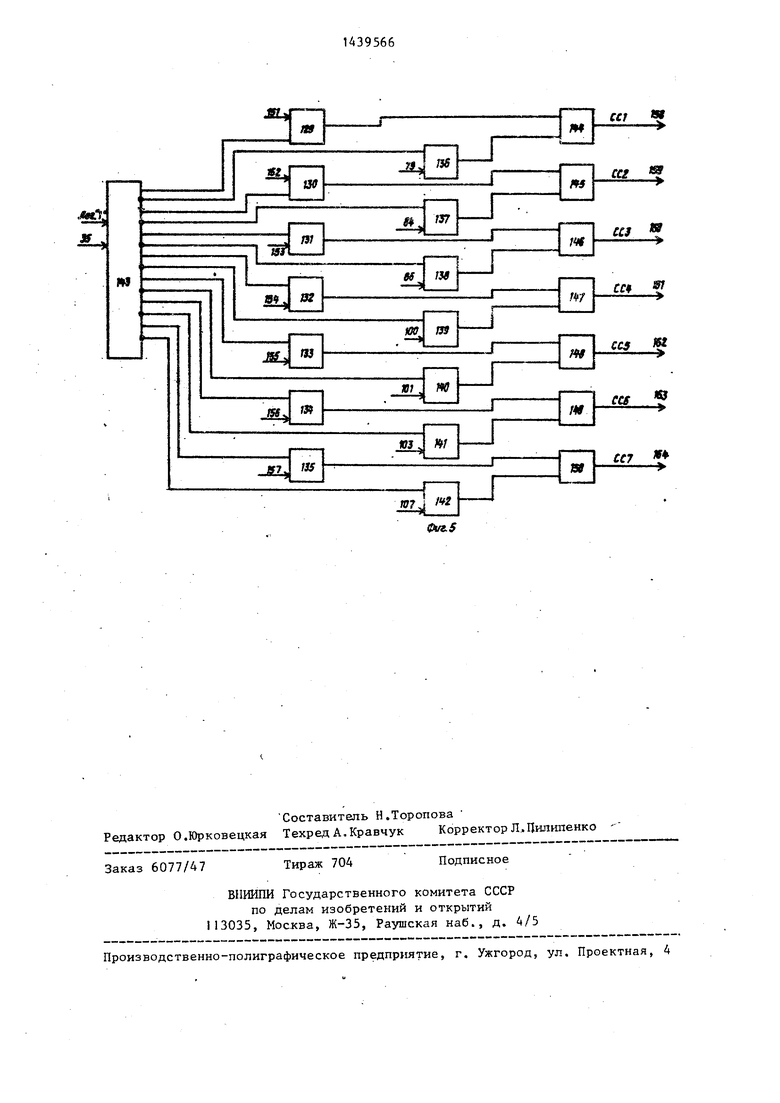

Коммутатор 3 содержит иультиплек- соры 108-114, счетчики 115-121, элемент И 122, первую группу элементов И 123-128, вторую группу элементов И 129-135, третью группу элементов И 136-142, регистр 143 сдвига, элементы ИЛИ 144-150,группы выходы 151-157 мультиплексоров и выходы 158 164.

Устройство работает следую цим образом.

Вначале устройство устанавливается в исходное состояние путем обнуления триггеров 4-6, счетчиков 10, 115-121 и регистра 143 сдвига и записи единиц в счетчик 36 (цепи начальной установки не показаны). После этого оно переходит в режим настройки синхросигналов,в процессекоторой с помощью ЭВМ или средств встроенного контроля проводится периодическое тестирование памяти. При каждом обращении к ней на вход 75 формирователя синхроимпульсов поступает сигнал Запуск, Он проходит на стробирующий вход дешифратора 37 и„ так как в счетчике 36 записано чисхю (11), оказывается на его последнем четвертом выходе, откуда поступает

0

5

0

5

0

5

0

0

5

на вход группы 41 элементов задержки Группы 38-41 состоят из 32 последовательно соединенных элементов, при- чем , , где t; - время задержки сигнала на одном элементе i-й группы. Следовательно, на выходах 76-107 элементов ИЛИ 42-73 группы формируется наиболее растянутая во времени последовательность синхроимпульсов. Семь синхроимпульсов из этой последовательности (их выбор зависит от вида памяти, в которой установлено устройство синхронизации) используются для формирования начальной диаграммы CCi В данном примере это синхроимпульсы на выходах 79, 84, 86, 100, 101, 103 и 107 элементов ИЛИ 45, 50, 52, 66, 67 69 и 73. Так как на всех инверсных выходах регистра 143 сдвига присутствуют логические единицы, то синхроимпульсы через элементы И 136-142 и элементы ШШ 144-150 подаются на выходы 158-164 устройства в качестве синхросигналов СС1-СС7.

Начальная последовательность синхросигналов формирует в устройстве временную диаграмму со значительными запасами по всем параметрам, что гарантирует ее надежную работу, но не обеспечивает высокого быстродействия. При отсутствии в памяти отказов ее тестирование заканчивается успешно, в результате чего на вход 15 нормальной работы вьщается отрицательный импульс. При наличии отказов отрицательный импульс поступает на вход отказа

памяти распределителя 1 и, так как в этот момент на выходе элемента И 74 присутствует логическая единица, которая через мультиплексор 14 подается на информационный вход триггера 5, то по положительному перепаду нй- пряжения на входе синхронизации он переходит в. единичное состояние. При этом на выход 25 устройства выдается признак устойчивого отказа, свидетельствующий о невозможности устранения неисправности путем коррекции временной диаграммы.

При поступлении импульса на вход 15 распределителя 1 на обоих входах элемента ИЛИ 7 имеются логические нули и на его.выходе,- формируется отрицательный импульс, который своим зад;ним переводит триггер 6 в единичное состояние. Одновременно им- пульс с входа 15 проходит элемент И

.12 и поступает на стробирующий вход дешифратора 11. Так как на его информационных входах присутствуют логические нули, то отрицательный импульс проходит на выход 16 дешифратора, откуда поступает на суммирующий вход счетчика 36 и своим задним фронтом переводит его в состояние (ООУ. После этого проводится повторное тестирование памяти, причем импульсы запуска поступают на вход группы 38 элементов задержки. Поскольку величина t у них минимальна, это приводит

И 136 и логической единицы на первый вход элемента И 129 коммутатора 3,

Прк очередном тестировании время вьщачи первого синхросигнала совпадает с моментом формирования импульса на вьиходе 151 мультиплексора 108 коммутатора 3. Поскольку в счетчике 115 записаны нули, то этим импульсом является синхроимпульс с выхода 76 элемента ИЛИ 42. В результате, время задержки между сигналами Запуск и первым синхроимпульсом уменьшает

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для синхронизации памяти | 1984 |

|

SU1247853A1 |

| УСТРОЙСТВО ДЛЯ МНОГОКАНАЛЬНОГО ВОСПРОИЗВЕДЕНИЯ СИГНАЛОВ ЦИФРОВОЙ ИНФОРМАЦИИ С НОСИТЕЛЯ МАГНИТНОЙ ЗАПИСИ | 1992 |

|

RU2018174C1 |

| Устройство для синхронизации вычислительной системы | 1984 |

|

SU1287138A1 |

| Устройство для контроля цифровых узлов | 1990 |

|

SU1756894A1 |

| Устройство для ввода информации | 1982 |

|

SU1048465A1 |

| Устройство для сопряжения вычислительной машины с каналом связи | 1985 |

|

SU1291994A1 |

| Устройство для синхронизации памяти | 1988 |

|

SU1594516A1 |

| Логический анализатор | 1986 |

|

SU1432527A1 |

| Автоматизированная система контроля радиоэлектронных устройств | 1989 |

|

SU1683038A1 |

| Логический анализатор | 1985 |

|

SU1283771A1 |

Изобретение относится к вычислительной технике и может быть использовано в блоках синхронизации дискретных устройств. Отличительной особенностью устройства является то, что устройство позволяет установить индивидуальную для каждого модуля памяти временную диаграмму, отвечающую требованию максимального быстродействия. Более высокая надежность работы достигается за счет сдвига всех синхросигналов от грантов в область устойчивой работы, что исключает сбои при колебаниях температуры и питающих напряжений. Цель изобретения - повышение достоверности работы. Поставленная цепь достигается за счет того, что вторая группа выходов коммутатора соединена с группой входов распределителя импульсов, четвертый выход которого соединен со стробирую- щим входом коммутатора, вход распре- S делителя импульсов соединен с выходом формирователя синхроимпульсов. 5 ил. (Л

к значительному сжатию временной дйа-15 ся на величину 3t, что может привесграммы памяти и она может оказаться неработоспособной. Тогда на вход 24 отказа памяти поступает отрицательный импульс, который через элемент ИЛИ 9 и элемент И 12 проходит на стробируниций вход дешифратора 11 и оказывается на выходе 16. В результате состояние счетчика 36 становится равным (01) и последующее тестирование проводится с более растянутой ди- 25 дешифратора и своим задним фронтом

аграммой. Так как в момент поступления -импульсов на вход 24 распределителя 1 импульсов на выходе элемента И 74 присутствует логический ноль, то триггер 5 остается в нулевом состоянии и на третьем выходе 25 распределителя 1 сигнала нет.

Если достигнутого расширения диаграммы оказывается недостаточно, то описанный процесс повторяется, иначе после окончания тестирования отрицательный импульс поступает на вход 15 и через элемент И 12 подается на стробирующий вход дешифратора 11, а затем на выход 16. В результате число, записанное в счетчике 36, увеличивается еще на одну единицу, что обеспечивает запас надежности по величине t. Одновременно отрицательный импульс с входа 15 через элемент ИЛИ 7 поступает на первый вход элемента ИЛИ 8. Поскольку на его втором входе присутствует низкий уровень напряжения с инверсного выхода триггера 6, то отрицательный импульс формируется также на выходе элемен- та ИЛИ 8 и своим задним фронтом пе- реводит счетчик 10 в состояние (001). Кроме того, отрицательный импульс поступает на синхровход регистра 143 сдвига и также своим задним фронтом записьгоает в его младший разряд единицу. Это приводит к вьдаче логического нуля на первый вход элемента

ти к утрате работоспособности памяти. При первой обнаруженной ошибке отрицательный импульс поступает на вход 24 распредепителя 1 импульсов и, пройдя элемент ИЛИ 9 и элемент И 12, выдается на стробирующий вход дешифратора 11. Так как в счетчике 10 записано число (001), то отрицательный импульс формируется на выходе 17

0

5

0

увеличивает содержимое счетчика 115 до величины (00001). После этого время вьщачи первого синхросигнала совпадает с моментом формирования синхроимпульса на выходе 77 элемента ИЛИ 43 и задержка между сигналами Запуск и первым синхроимпульсом возрастает на величину t. Если и в этом случае в памяти обнаружены ошибки, то описанньй процесс повторяется и задержка еще раз увеличивается. В процессе тестирования памяти в ней может возникнуть независящая от временной диаграммы неисправность (например, выходит из строя одна из микросхем накопителя). Тогда процесс постепенного увеличения задержки между сигналами Запуск и первым синхроимпульсом продолжается до тех пор,. Пока содержимое счетчика 115 не достигнет величины (11111). Это приводит к выдаче логической единицы на выход 27 элемента И 122 коммутатора 3. Поскольку в этот момент на управляющих входах мультиплексора 14 присутствует код (001), то логическая единица проходит и на его выход. По заднему фронту очередного отрицатель- .ного импульса на входе 24 распреде- 5 лителя 1 импульсов триггер 5 переходит в единичное состояние, и на выход 25 устройства вьщается признак устойчивого отказа. На этом процесс настройки заканчивается.

5

0

При успешном окончании тестирования отрицательный импульс поступает на вход 15 распределителя 1 импульсов. Он проходит элемент И 12 и вьща- ; ется на выход 17 дешифратора 11, что ;приводит к увеличению еще на одну единицу содержимого счетчика 115, Это необходимо для сдвига первого синхросигнала от границы в область устойчи- Ю хровходом Первого триггера, разрядвой работы памяти. Одновременно отрицательный импульс проходит элементы ИЛИ 7 и 8 и переводит счетчик 10 в состояние (010), а регистр 143 сдвиные выходы счетчика соединены с информационными входами дешифратора, первый выход которого являе тся первы выходом распределителя импульсов, вы

га - в состояние (0000011). На первый 15 ходы дешифратора с второго по восьвход элемента И 137 выдается логический ноль, а на первый вход элемента И 130 - логическая единица, и устройство переходит к настройке второго синхросигнала. Процесс его установки к всех последующих синхросигналов протекает аналогично.

В течение настройки последнего седьмого синхросигнала в счетчике 10 записано число (111) и на выходе элемента И 13 присутствует логическая единица. По заднему фронту импульса на входе 15 триггер 4 переходит в единичное состояние, и на выход 34

распределителя 1 выдаётся признак конца настройки. После этого память

:переходит в рабочий режим, а посту;пление импульсов на входы 15 и 24 распределителя 1 импульсов прекращаI /ется.

|Формула изобретения

Устройство для синхронизации бло- :ков памяти, содержащее формирователь синхроимпульсов, распределитель импульсов и коммутатор, причем первый выход распределителя импульсов соединен с синхровходом формирователя синхроимпульсов, группа выходов распределителя импульсов соединена с группой управляющих входов коммутатора, группа выходов формирователя синхроимпульсов соединена с группой информационных входов коь 1утатора, первая группа выходов которого является группой синхровыходов устройства, вход запуска формирователя синхроимпульсов является входом.запуска

устройства, синхровход и вход задания 55 четвертой группы соответственно с режима распределителя импульсов яв- первого по п-й, причем коммутатор со- ляются соответственно входами нормальной работы и отказа памяти устройстдержит еемь счетчиков, семь мульти- гшексоров, управляющие входы коммутатора с первого по седьмой соедине- ,

ва, второй и третий выходы распределителя импульсов являются выходами конца настройки и устойчивого отказа устройства, причем распределитель импульсов содержит два триггера,три элемента ИЛИ, счетчик, дешифратор и первый элемент И, первый вход распределителя импульсов соединен с первым входом первого элемента ИЛИ и с синные выходы счетчика соединены с информационными входами дешифратора, первый выход которого являе тся первым выходом распределителя импульсов, вы0

мой являются группой выходов распределителя импульсов, стробирующий вход дешифратора соединен с выходом первого элемента И, синхровход распределителя импульсов соединен с синхровходом второго триггера, прямой выход которого является третьим выходом распределителя импульсов, причем формирователь синхроимпульсов содер5 жит счетчик, дешифратор, четыре группы из п элементов задержки, (где п - число BbKOfioB формирователя синхроимпульсов) , группу из п элементов ИЛИ, причем синхровход форми1)ователя им0 пульсов соединен со счетным входом счетчика, группа разрядных выходов которого соединена с группой информационных входов дешифратора, стробирующий вход которого является вхос дом запуска формирователя синхроимпульсов, первый, второй, третий и четвертый выходы дешифратора соединены с входами первых элементов задержки соответственно первой, второй, третьей и четвертой групп, элементы задержки в каждой соединены последовательно, выходы элементов задержки с первого по п-й первой группы соединены с первыми входами элементов ИЛИ группы соответственно с первого по п-й, вторые входы которых соединены соответственно с выходами с первого по п-й элементов задержки второй группы, выходы элементов задержки третьей группы соединены с третьими входами элементов ИЛИ группы соответственно с первого по п-й, четвертые входы которых соединены с выходами элементов задержки

0

5

0

четвертой группы соответственно с первого по п-й, причем коммутатор со-

держит еемь счетчиков, семь мульти- гшексоров, управляющие входы коммутатора с первого по седьмой соедине- ,

ны со счетными входами счетчиков со- ответственно с первого по седьмой,, выходы которых соединены с управляющими входами мультиплексоров соответственно с первого по седьмой, группа информационных входов коммутатора соединена с группами информационных входов мультиплексоров, о т л и - ;Ч а ю щ е е с я тем, что, с целью повышения достоверности работы устройства, вторая группа выходов коммутатора соединена с группой информационных входов распределителя импульсов, четвертый выход которого соединен со стробирующим входом коммутатора, третий вход распределителя импульсов соединен с выходом формирователя синхроимпульсов, причем в распределитель импульсов введен третий триггер, мультиплексор и второй элемент И, выход первого элемента ИЛИ распределителя импульсов соединен с первым входом второго элемента ИЛИ распределителя импульсов и с синхровходом третьего триггера, информационный вход которого соединен с шиной единичного потенциала устройства, группа информационных входов мультиплексора с второго по вось- 30 вьюодов коммутатора, управляющий вход мой является группой информационных которого соединен с синхровходом регистра сдвига, информационный вход первого разряда которого соединен с

40

входов распределителя импульсов, управляющие входы мультиплексора соединены с выходами счетчика и входами второго элемента И распределителя им- 35 пульсов, выход мультиплексора соединен с управляющим входом второго триггера и первым входом третьего элемента ИЖ распределителя импульсов, второй вход которого является вторым входом распределителя импульсов, выход третьего элемента ИЖ распределителя импульсов соединен с первьо4 входом первого элемента И распределителя импульсов, третий вход распре- депителя импульсов соединен с первым информационным входом мультиплексора, второй вход первого элемента ИЛИ распределителя импульсов соединен с выходом второго элемента И распределишиной единичного потенциала устройства, прямые выходы регистра сдвига соединены с первыми входами элементов И второй группы, вторые входы которых соединены соответственно с выходами мультиплексоров, инверсные выходы регистра сдвига соединены соответственно с первыми входами элементов И третьей группы, вторые входы которых являются соответственно группой информационных входов коммутатоТра, 45 выходы элементов И второй и третьей групп соединены соответственно с первыми и вторыми входами элементов ИЛИ группы, выходы которых являются выходами первой группы коммутато - ра.

50

теля импульсов и с информационным входом первого триггера, выход которого является вторым выходом распределителя импульсов, инверсный выход третьего триггера соединен с вторым входом второго элемента ИЛИ распределителя импу-тьсов выход которого соединен со счетным входом счетчика

и является четвертым выходом распределителя импульсов, первый вход которого соединен с вторым входом первого элемента И распределителя импульсов, причем в формирователь синхроимпульсов введен элемент И, входы которого соединены с соответствующими разрядными вькодами счетчика, выход элемента И формирователя синхроимпульсов является выходом признака

конца работы формирователя синхроимпульсов, причем в коммутатор введена первая, вторая и третья группы элементов И, регистр сдвига и группа элементов ИЛИ, причем группы выходов

счетчиков с первого по седьмой соединены с группами входов соответст- вукмцих элементов И первой группы соответственно с первого по седьмой, выходы которых являются второй группой

шиной единичного потенциала устройства, прямые выходы регистра сдвига соединены с первыми входами элементов И второй группы, вторые входы которых соединены соответственно с выходами мультиплексоров, инверсные выходы регистра сдвига соединены соответственно с первыми входами элементов И третьей группы, вторые входы которых являются соответственно группой информационных входов коммутатоТра, выходы элементов И второй и третьей групп соединены соответственно с первыми и вторыми входами элементов ИЛИ группы, выходы которых являются выходами первой группы коммутато - ра.

| Устройство для синхронизации памяти | 1983 |

|

SU1169017A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Устройство для синхронизации памяти | 1984 |

|

SU1247853A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-11-23—Публикация

1986-03-03—Подача