Изобретение относится к устройствам подсчета импульсных сигналов и может быть использовано в измерительных и вычислительных системах с индикацией результатов.

Известна пересчетная декада, .со держащая счетчик на четырех триггерах, элемент ИЛИ и дешифратор, требующий для своего построения десяти логических элементов ij .

Недостатком этой пересчетной декады является необходимость относи- тельно больших затрат оборудования для их реализации.

Наиболее близкой по технической сущности к предлагаемому устройству является пересчетная дексща, содержащая дешифратор, четыре триггера и элемент ИЛИ, первый вход которого соединен с прямым выходом четвертого триггера, первый и второй управлющий входы которого соединены соответственно с прямым и инверсным выходами третьего триггера, инверсный выход которого соединен с управляющим входом элемента ИЛИ, выход которой соединен с управляющим входом первого триггера, выход которого соединен с первым управляющим входом второго триггера, инверсный выход которого -соединен с вторым управляющим входом третьего триггера, первый вход которого соединен с вторым управляющим входом второго триггера и инверсным выходом четвертого триггера, счетный вход пересченой декады соединен с тактовыми входами всех четырех триггеров, прямые и инверсные выходы которых соединены с входами дешифратора, содержащего десять элементов И, выходы которых соединены с выходами дешифратора, соединенными с.входами элемента индикации, первый вход дешифратора соединен с первыми входами второго, четвертого и шестого элементо И, второй вход с первыми входами третьего, седьмого и восьмого элементов И, третий вход - с первыми входами пятого, шестого и десятого элементов И, четвертый вход с вто-рыми входами седьмого, восьмого и девятого элементов И, пятый вход с первым входом первого элемента и вторыми входами четвертого и десятого элементов И, шестой вход - с вторлм входом третьего, с первым вхдом девятого и третьим входом восьмого Ълементоб и, седьмой вход - с вторыми входами nefiBoro, второго и пятого элементов И, восьмой вход-с третьими входами третьего седьмого и девятого элементов И 2.

Недостатком этой пересчетной декады является- относительная сложность ее, наличие элемента ИЛИ, и значительного количества внутренних связей между триггерами.

Цель изобретения - упрощение пересчетной декады, т.е. уменьшение числа логических элементов и количества внутренних соединений. Поставленная цель достигается

тем, что в пересчетной декаде, содержащей дешифратор и четыре триггера, тактовые входы которых соединены со счетным входом пересчетной декады. Прямой выход первого триггера

0 соединен с первым управляющим входом второго триггера, инверсный выход которого соединен с вторым управляющим входом третьего триггера, инверсный выход которого соединен

5 с вторым управляющим входом четвертого триггера, инверсный выход которого соединен с вторым управляющим входом второго триггера, прямые и инверсные выходы триггеров соединеБЫ с входами дешифратора, содержащёго десять элементов И, выходы которых соединены с выходами дешифратора первый вход которого соединен с первыми входами второго и шестого элет ментов И, второй вход дешифратора соединен с первыми входами третьего, седьмого и восьмого элементов И, третий вход дешифратора соединен с первым входом десятого и с вторым входом шестого элементов И, четвертый вход дешифратора соединен с вторымк входами седьмого, восьмого и с первым входом девятого элемента И, пятый вход дешифратора соединен с первым входом четвертого и вторым

5 входомпервого элемента И, шестой вход дешифратора соединен с вторыми входами третьего и девятого элементов И, седьмой вход дешифратора .соединен с вторым входом пятого элеп мента И, восьмой вход дешифратора соединен с третьими входами третьего и девятого элементов И, инверсный выход первого триггера соединен с первым, управляющим входом третьего триггера, прямой выход которого соединен с первыми управляющим входом первого триггера, второй управляющий вход которого соединен с вторым управляющим входом вторЬго триггера, первый и второй управляющие входы

0 четвертого триггера соединены между собой, а первый вход дешифратора соединен с первым входом пятопо элемента И, третий вход дешифратора соединен с первым входом первого элемента и, пятый вход дешифратора соединен с вторым входом второго элемента И, шестой вход дешифратора соединен с третьим входом седьмого элемента И, седьмой вход дешифратод ра соединен с вторыми входад-ш четвертого и десятого элементов И, восьмой вход дешифратора соединен с третьим входом восьмого элемента И.

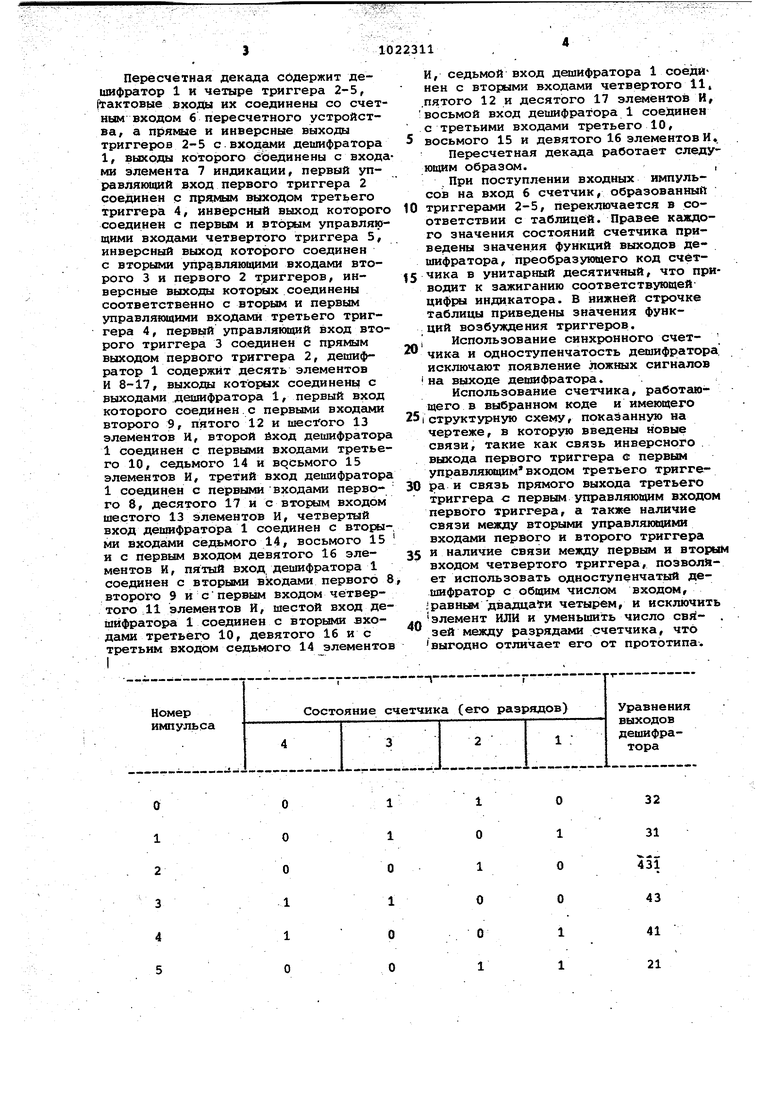

Структурная схема пересчетной 5 декады приведен на чертеже.

Пересчетная декада содержит дешифратор 1 и четыре триггера 2-5, ргактовые входы их соединены со счетным входом 6 пересчетного устройства, а прямые и инверсные выходы триггеров 2-5 с входами дешифратора 1, выхода которого соединены с входами элемента 7 индикации, первый управлякиций вход первого триггера 2 соединен с прямым выходом третьего триггера 4, инверсный выход которого соединен с первым и вторым управляющими входами четвертого триггера 5, инверсный выход которого соединен с вторыми управляющими входами второго 3 и первого 2 т;риггеров, инверсные выхода которых соединены соответственно с вторым и первым управлякицими входг ми третьего триггера 4, первый управлякнций вход второго триггера 3 соединен с прямым выходом первого триггера 2, дешифратор 1 содержит десять элементов И 8-17, выходи которых соединены с выходами дешифратора 1, первый вход которого соединен с первыми входами второго 9, пятого 12 и шестого 13 элементов И, второй ёход дешифратора 1 соединен с первыми входами третьего 10, седьмого 14 и восьмого 15 элементов И, третий вход дешифратора 1 соединен с первыми входами первого 8, десятого 17 и с вторым входом шестого 13 элементов И, четвертый вход дещифратора 1 соединен с вторыми входами седьмого 14, восьмого 15 и с первым входом девятого 16 элементов И, пятый вход дешифратора 1 соединен с вторыми входс1ми первого 8 второго 9 КСпервым входом четвертого Д1 элементов И, шестой вход дешифратора 1 соединен с вторыми входами третьего 10, девятого 16 и с третьим входом седьмого 14 элементов

И, седьмой вход детаифратора 1 соедйнен с вторыми входами четвертого 11. .пятого 12 и десятого 17 элетлентов И, восьмой вход дешифратора 1 сое)|инен с третьими входами третьего 10, восьмого 15 и девятого 16 элементов И. Пересчетная декада работает следующим образом.I

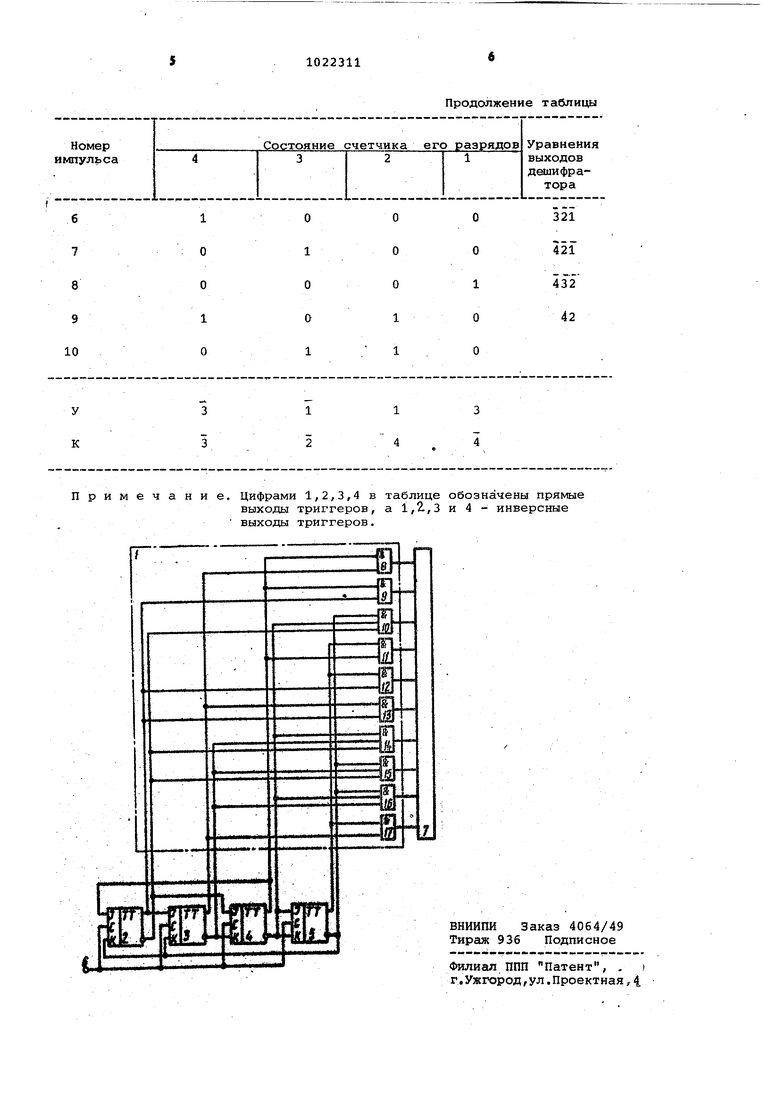

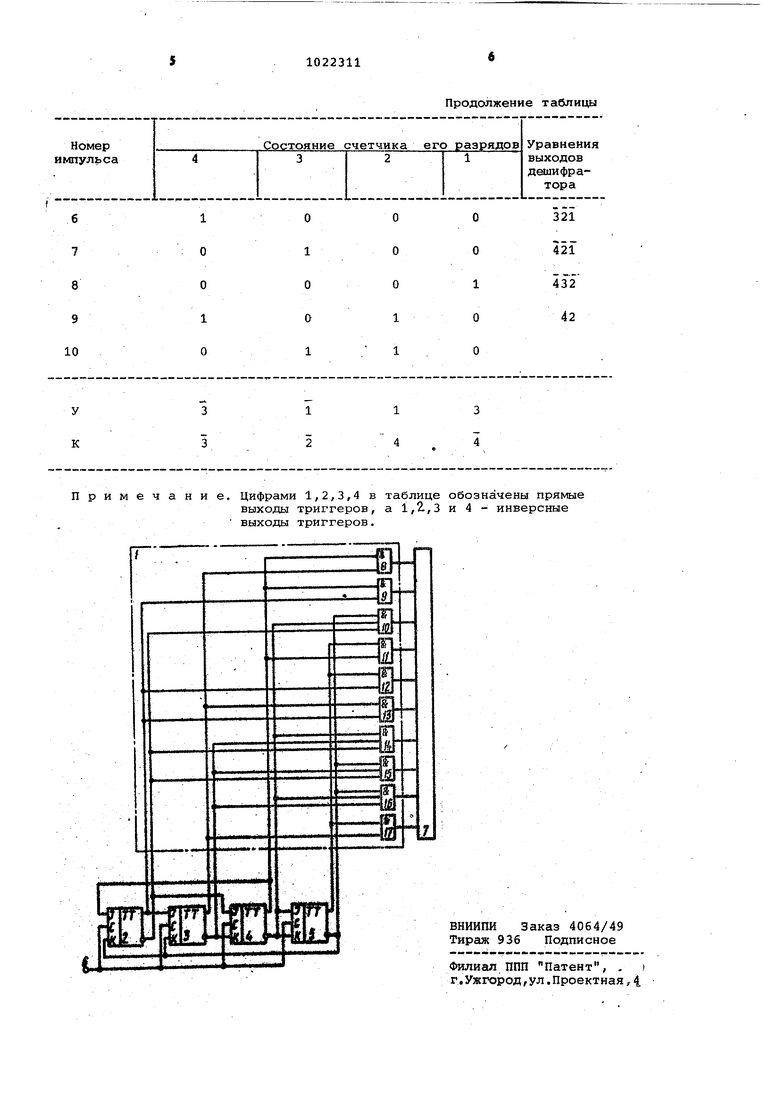

При поступлении входных импульсов на вход 6 счетчик, образованный

0 триггерами 2-5, переключается в соответствии с таблицей. Правее кгикдого значения состояний счетчика приведены значения функций выходов дешифратора, преобразующего код счёт5 ика в унитарный десятичный, что приводит к зажиганию соответствующей цифры индикатора. В нижней строчке таблицы приведены значения функций возбуждения триггеров.

Использование синхронного счет0чика и одноступенчатость дешифратора, исключают появление ложных сигналов на выходе дешифратора.

Использование счетчика, работающего в выбранном коде и имеющего

5iструктурную схему, показанную на чертеже, в которую введены новые связи, такие как связь инверсного выхода первого триггера с первым управляющим входом третьего триггера и связь прямого выхода третьего триггера с первым управляющим входом первого триггера, а также наличие связи между вторыми управляющими входами первого и второго триггера

5 и наличие связи между первым и вторым входом четвертого триггера, позволйет использовать одноступенчатый дешифратор с общим числом входом, jpaBHbB t двадцаги четырем, и исключить

„элемент ИЛИ и уменьшить число свй- . 3ей между разрядами счетчика, что выгодно отличает его от прототипа-.

| название | год | авторы | номер документа |

|---|---|---|---|

| Пересчетная декада | 1981 |

|

SU982199A1 |

| Пересчетная декада | 1983 |

|

SU1112574A1 |

| Пересчетная декада | 1982 |

|

SU1064478A1 |

| Десятичное счетно-индикаторное устройство | 1982 |

|

SU1078628A1 |

| Реверсивная счетная декада | 1988 |

|

SU1554141A1 |

| Десятичный счетчик с индикацией | 1983 |

|

SU1156254A1 |

| Счетчик импульсов с цифровой индикацией | 1984 |

|

SU1231602A1 |

| Реверсивное пересчетное устройство | 1982 |

|

SU1115240A1 |

| Счетчик импульсов с цифровой индикацией | 1987 |

|

SU1478325A1 |

| Счетчик импульсов с цифровой индикацией | 1986 |

|

SU1336230A1 |

ПЕРЕСЧЕТНАЯ ДЕКАДА, содержащая дешифратор и четыре триггера, тактовые входы которых соединены с входом пересчетной декады, прямой выход первого триггера соединен с первым управляющим:входом триггера, инверсный выход которого соединен с вторым управляющим входом третьего триггера, инверсный выход которого соединен с ВТОЕЯЛМ управляющим входола четвертого триггера, инверсный выход которого соединен с вторым управляющим входом второго триггера, прямые и инверсные выходы триггеров соединены с входами дешифратора, содержащего десять элементов И, выходы KOTOE JX соединены с выходами диаифратора, первый вход которого соединен с первыми входами второго и шестого элементов И, второй вход дешифратора соединен с первыми входами третьего, седьмого и восьмого элементов И, тре;тий вход дешифратора соединен с пер- ; вым входом десятого и с входом шестого элементов И, четвертый вход деишфратора соединен с вторыми входами седьмого, восьмого и с первым входом девятого элементов И, пятый вход дешифратора соединен с первым входом четвертого и вторым входом первого элементов И, шестой вход дешифратора соединен с вторыми входами третьего -и девятого элементов И, седьмой вход дешифратора соединен с вторым входом пятого элемента И, восьмой вход дешифратора соединен с третьими входами третьего и девятого элементов И, отличаю-щ а я с я тем, что, с целью упрощения пересчетной декады, инверсный выход первого триггера соединен с перi вым управлякицим входом третьего триггера, прямой выход которого соеди(Л нен с первым управлякищм входом первого триггера, второй управлякзщий С вход которого соединен с вторым управляющим входом второго триггера, первый и второй управляюцще входы четвертого триггера соединены между собой, а рервый вход дешифратора соединен с первым входом пятого элемента И, третий вход дешифратора соto ьэ единен, с первым входом первого элемента И, пятый вход дешифратора соединен с вторым входом второго со элемента И, шестой вход дешифратора соединен с третьим входом седьмого элемента И, седьмой вход дешифратора соединен с вторыми входами четвертого и десятого элементов И, вось- мой вход дешифратора соединен с .третьим входом восьмого элемента И.

О О

О 1 2 3 4 5

о 1 1 о

t о 1 о о 1

о 1 о о 1 1

32 31 431 43 41 21 Примечание. Цифрами 1,2,3,4 в выходы триггеров, выходы триггеров.

Продолжение таблицы таблице обозначены прямые а 1,2.,3 и 4 - инверсные

Авторы

Даты

1983-06-07—Публикация

1982-01-21—Подача