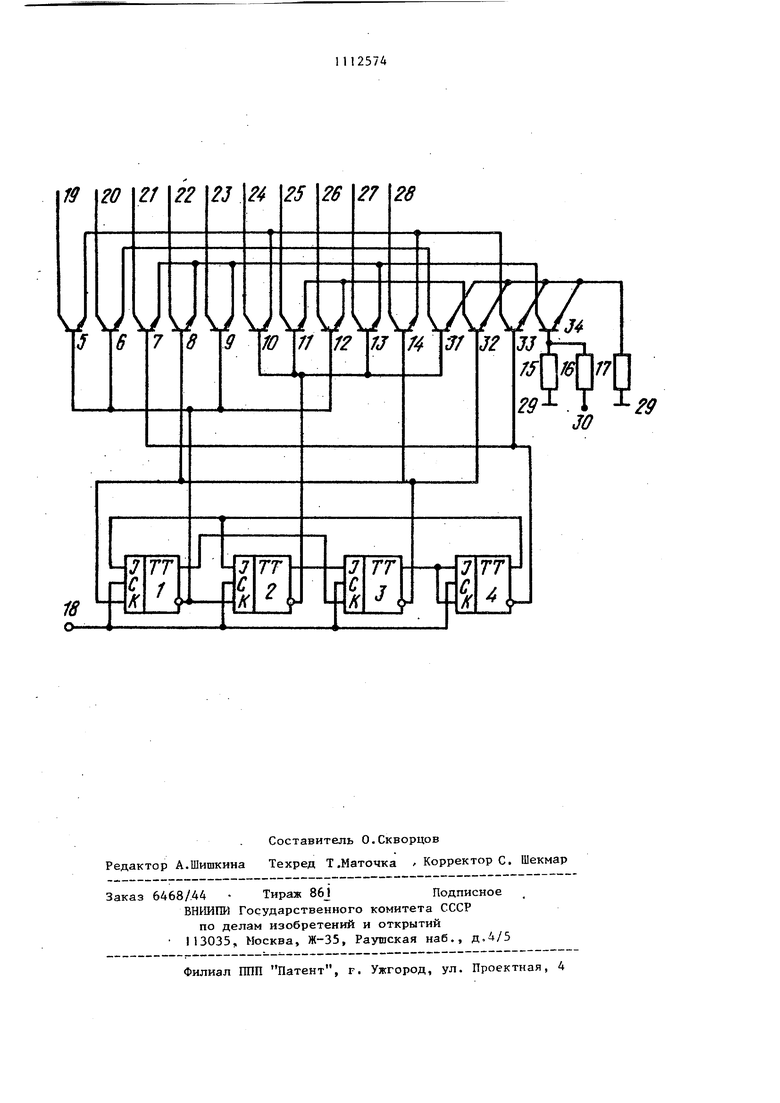

Изобретение относится к устройствам для подсчета импульсных сигналов с индикацией суммарного числа импулЬ сов, поступающих на вход, и может быть использовано в измерительной и вычислительной аппаратуре. Известны пересчетные декады, содержащие четыре триггера, десять транзисторных ключей и резисторную матрицу из пятнадцати резисторов, пять из которых первыми входами подключены к полюсу источника смещения, а вторые входы пяти резисторов соеди нены, с соответствующими базами, объединенными попарно, десяти транзисторных ключей, эмиттеры которых объединены в две группы и каждая группа подключена к соответствующему выходу первого триггера, который с другими тремя триггерами объединен в десятичный счетчик, к выходам кото рого подключены соответствующие вход резисторного дешифратора, содержащег десять резисторов, а выходы резистор ного дешифратора соединены с соответ ствующими базами транзисторных ключей l . Недостатком этого устройства является относительно низкая функцио нальная надежность. Наиболее близкой к изобретению является пересчетная декада, содержа щая четыре I-К-триггера, десять транзисторов и три резистора, счетный вход декады соединен с тактовыми входами J -К-триггеров, прямой выход первого I -К-триггера соединен с К-входом третьего J -К-триггера, 7-вход которого соединен с прямым выходом второго Т -К-триггера,прямой выход третьего J -К-триггера соединен с 1 -входом четвертого J-К-триггера, коллекторы транзисторов соединены с соответствующими выходными шинами, а первые выводы первого, второго и третьего резисторов соединены соответственно с общей шиной, шиной питания и общей щиной 2J. Недостатком известного устройства является относительно низкая функцио нальная надежность, что связано с необходимостью использования для дешифрации резисторов и относительно большим током, необходимым для управления транзисторами. Целью изобретения является повьше ние функциональной надежности. Поставленная цель достигается тем, что в пересчетную декаду, содер жащую четыре 3-К-триггера, десять транзисторов и три резистора, и в которой счетный вход декады соединен с тактовыми входами Ц - К-триггеров, прямой выход первого 1-К-триггера соединен с К-входом третьего Т-Ктриггера, Т -вход которого соединен с прямым выходом второго J -К-триггера, прямой выход третьего J -К-триггера соединен с J -входом четвертого Т -К-триггера, коллекторы транзисторов - с соответствующими выходными шинами, а первые выводы первого, второго и третьего резисторов - соответственно с общей шиной, шиной питания и обшей шиной, введены четыре дополнительных транзистора, J -вход первого J -К-триггера соединен с 3-входом второго Т -К-триггера и прямым выходом четвертого 3 -К-триггера, инверсный выход первого J -К-триггера соединен с К-входом второго J -Ктриггера и базами первого, второго, пятого и восьмого транзисторов, инверсный выход второго Т -К-триггера соединен с базами шестого, седьмого и девятого транзисторов, а также с базой первого дополнительного транзистора, коллектор которого соединен с эмиттером второго транзистора, инверсный выход третьего Т -Ктриггера соединен с базами четвертого и десятого транзисторов, а также с базой второго дополнительного тран-зистора, коллектор которого соединен С коллектором седьмого и восьмого транзисторов, инверсный выход четвертого J -К-триггера соединен с базами третьего транзистора и третьего дополнительного транзистора, коллектор которого соединен с эмиттерами первого, шестого и десятого транзисторов, К-вход четвертого 7 -К-триггера соединен с Т-входом этого J -К-триггера, а К-вход первого J -К-триггера - с инверсным выходом третьего Т - К-триггера, эмиттеры третьего, четвертого пятого и девятого транзисторов соединены с коллектором четвертого дополнительного транзистора, база которого соединена с вторыми выводами первого и второго резисторов, а эмиттер четвертого дополнительного транзистора соединен с эмиттерами первого, второго и третьего дополнительных транзисторов и вторым Б, (ВОДОМ третьего резистора. На чертеже показана структурная схема пересчетной декады. Пересчетная декада содержит четы ре 3 -К-триггера 1-4, десять, транзисторов 5-14 и три резистора 15 - 17. Счетный вход 18 декады соединен с тактовыми входами Т-Ктриггеров 1-4, прямой выход первого J -К-триггера I - с К-входом третье го J -К-триггера 3,Т -вход которого соединен с прямым выходом второго I-К-триггера 2, прямой выход третьего I -К-триггера 3-е I-входом четвертого J -К-триггера 4 коллекторы транзисторов 5-14 - с соответствующими выходными шинами 19-28, а первые выводы первого 15, второго 16 и третьего 17 резисторов соответственно с общей шиной 29, шиной 30 питания и общей шиной 29. Пересчетная декада также содержит четыре дополнительных транзистора 31-34, J -вход первого -К-трип-ера I соединен с J -входом второго J -Ктриггера 2 и прямым выходом четвертого 3 -К-триггера 4, инверсный выход первого J -К-триггера 1- с Квходом второго 3 -К-триггера 2 и ба ми первого 5, второго 6, пятого 9 и восьмого 13 транзисторов, инверсный выход второго J -К-триггера 2-е базами шестого 10, седьмого II и девятого 13 транзисторов, а также с базой первого дополнительного транзистора 31, коллектор которого соед нен с эмиттером второго транзистора 6. Инверсный выход третьего -Ктриггера 3 соединен с базами чотвер того 8 и десятого 14 транзисторов, также с базой второго дополнительно транзистора 32, коллектор которого соединен с коллектором седьмого I1 и восьмого 12 транзисторов, Инверс. ный выход четвертого J -К-триггера 4 соединен с базами третьего транзистора 7 и третьего дополнительног транзистора 33, коллектор которого соединен с эмиттерами первого 5, шестого 10 и десятого 14 транзистор К-вход четвертого J -К-триггера 4 с 7 -входом этого J -К-триггера, а К-вход первого 3 -К-триггера 1 - с инверсным выходом третьего J-К-триг

гера 3, эмиттеры третьего 7, четвертого 8, пятого 9 и девятого 13 транзисторов соединены с коллектором четвертого дополнительного транзистора 34, база которого соединена с вторыми выводами первого I5 и второго I6 резисторов, а эмиттер четвертого дополнительного транзистора 34 соедиваются разомкнутыми.

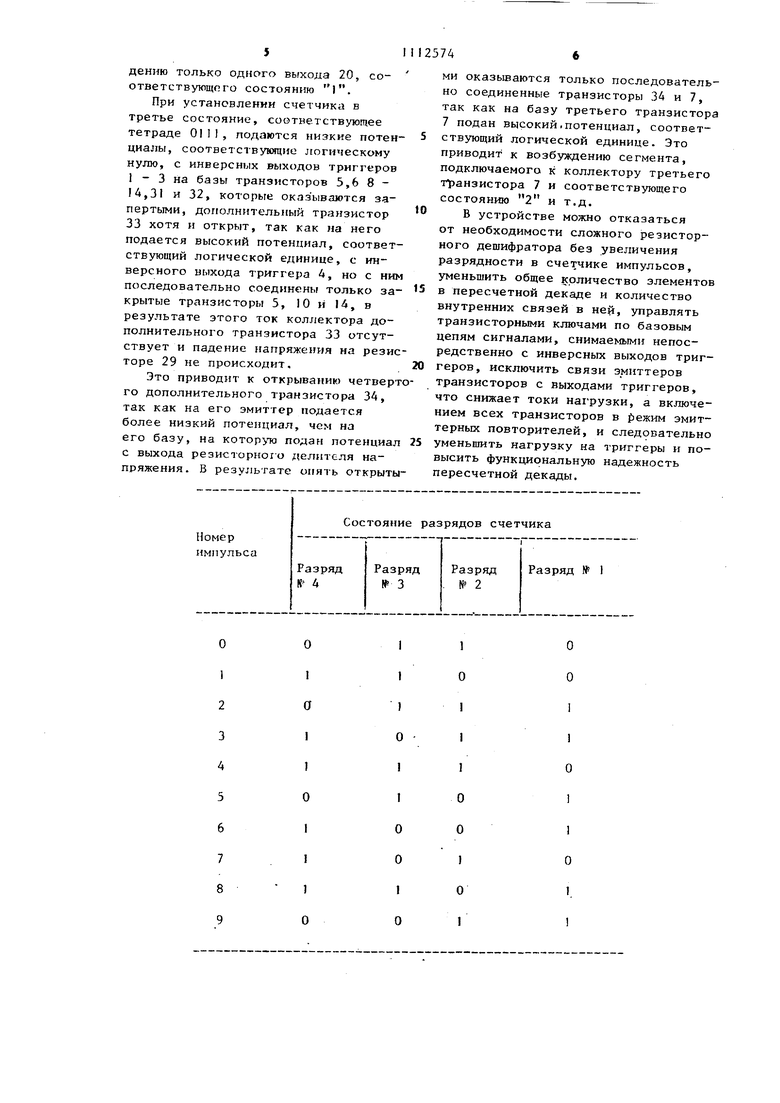

При установлении счетчика в следующее состояние, соответствующее тетраде 1100, последовательно вклк ченными и открытыми оказьшаются опять только два транзистора - второй 6 и первый дополнительный 31 транзисторы, что приводит, к возб жнен с эмиттерами первого 31,второго 32 и третьего 33 дополнительньгх транзисторов и вторым выводом третьего резистора 17. Пересчетная декада работает следующим образом. При поступлении входных импульсов на вход 18 декады счетчик, образованный триггерами 1-4,переключается в соответствии с данными, приведенными в таблице. При установлении счетчика, например, в нулевое состояние, которое соответствует коду 0110, высокий потенциал с инверсного выхода триггера I, соответствующий логической единице, подается на базы первого 5, второго 6, пятого 9 и восьмого 12 транзисторов, открывая их. Одновременно подается высокий потенциал с инверсного выхода триггера 4 на базы третьего 7 и третьего дополнительного 33 транзисторов, открывая их. В результате этого последовательно соединенными и открытыми оказываются только два транзистора, первый 5 и третий дополнительный 33 транзисторы, через которые может пройти ток от источника питания, питающего индикаторный элемент, соответс вующий нулевому состоянию декады. При прохождении тока через открытые транзисторы 5 и 33 на резисторе 29 происходит падение напряжения, величина которого больше, чем напряжение, соответствующее логическому нулю, подаваемое на базы транзисторов 31, 32 и 34, соответственно с инверсных выходов триггеров 2 и 3 и с выхода делителя напряжения, собранного на резисторах 15 и 16, что приводит к запиранию остальных транзисторов В - 11 и 13 и дополнительных транзисторов 31,32 и 34, последовательно с которыми соединены транзисторы 6-14. Транзисторы 6,7,9 и 12 хотя и открыты, но они последовательно соединены с закрытыми дополнительными транзисторами 31,32 и 34, в результате этого цепи питания индикаторных элементов 20-28 оказыдению только одного выхода 20, соответствующпго состоянию 1. При установлении счетчика в третье состояние, соответствующее тетраде 0111, подаются низкие потен циалы, соответствующие логическому нулю, с инверсных выходов триггеров 1 - 3 на базы транзисторов 5,6 8 14,31 и 32, которые оказываются запертыми, дополнительный транзистор 33 хотя и открыт, так как на него подается высокий потенциал, соответ ствующий логической единице, с инверсного выхода триггера 4, но с ни последовательно соединены только за крытые транзисторы 5, 10 и 14, в результате этого ток коллектора дополнительного транзистора 33 отсутствует и падение напряжения на рези торе 29 не происходит, Это приводит к открыванию четвер го дополнительного транзистора 34, так как на его эмиттер подается более низкий потенциал, чем на его базу, на которую подан потенциа с выхода резисторного делителя напряжения. В результате опять открыт ми оказываются только последовательно соединенные транзисторы 34 и 7, так как на базу третьего транзистора 7 подан высокий.потенциал, соответствующий логической единице. Это приводит к возбуждению сегмента, подключаемого к коллектору третьего тт анзистора 7 и соответствующего состоянию 2 и т.д. В устройстве можно отказаться от необходимости сложного резисторного дешифратора без увеличения разрядности в счетчике импульсов, уменьшить общее количество элементов в пересчетной декаде и количество внутренних связей в ней, управлять транзисторными ключами по базовым цепям сигналами, снимаемыми непосредственно с инверсных выходов триггеров, исключить связи эмиттеров транзисторов с выходами триггеров, что снижает токи нагрузки, а включением всех транзисторов в f)eжим эмиттерных повторителей, и следовательно уменьшить нагрузку на триггеры и повысить функциональную надежность пересчетной декады.

| название | год | авторы | номер документа |

|---|---|---|---|

| Пересчетная декада | 1982 |

|

SU1064478A1 |

| Десятичное счетно-индикаторное устройство | 1982 |

|

SU1078628A1 |

| Десятичный счетчик с индикацией | 1983 |

|

SU1156254A1 |

| JK-триггер | 1989 |

|

SU1713091A1 |

| Триггер | 1983 |

|

SU1150732A2 |

| Пересчетная декада | 1981 |

|

SU982199A1 |

| Пересчетная декада | 1982 |

|

SU1022311A1 |

| ТРАНЗИСТОРНЫЙ КЛЮЧ | 2002 |

|

RU2233022C1 |

| СХЕМА ЗАЩИТЫ КЛЮЧЕВОГО ТРАНЗИСТОРА | 2003 |

|

RU2245602C1 |

| Устройство для синхронизации воспроизведения цифровой магнитной записи | 1986 |

|

SU1337918A1 |

ПЕРЕСЧЕТНАЯ ДЕКАДА, содержащая четыре 3-К-триггера, десять транзисторов и три резистора, счетный вход декады соединен с тактовыми входами J -К-триггеров, прямой выход первого J -К-триггера соединен с К-входом третьего J -К-триггера, 3 -вход которого соединен с прямым выходом второго J -К-триггера, прямой выход третьего J -К-триггера соединен с 3 -входом четвертого J -К-триггера, коллекторы транзисторов - с соответствующими выходными шинами, а первые выводы первого, второго и третьего резисторов - соответственно с общей шиной, шиной питания и общей шиной, о т л и ч а ю щ а ЯС я тем, что, с целью повышения функциональной надежности, в нее введены четыре дополнительных транзистора, -вход первого I-К-триггера соединен с J-входом второго Т-К-триггера и прямым выходом четвертого 5 -К-триггера, инверсный выход первого J -К-триггера соединен с К-входом второго Т-К-триггера, и базами первого, второго,пятого и восьмого транзисторов, инверсный выход второго Т -К-триггера соединен с базами шестого, седьмого и девятого транзисторов, а также с базой первого дополнительного транзистора, коллектор которого сое 1нен с эмиттером второго транзистО а, инверсный выход третьего 1 -К-триггера соединен с базами четвертого и десятого транзисторов, а также с базой второгодополнительного транзистора, коллектор которого соединен с коллектором i седьмого и восьмого транзисторов, инверсный выход четвертого J -Ктриггера соединен с базами третьего транзистора и третьего дополнительного транзистора, коллектор которого соединен с эмиттерами первого, шестого и десятого транзисторов, К-вход четвертого J-К-триггера соединен с Т -входом этого Т -К-триггера, а К-вход первого 3 -К-триггера - с инверсным выходом третьего J -Кto сл триггера, эмиттеры третьего, четвертого, пятого и девятого транзисторов соединены с коллекторомчетвертого 1 дополнительного транзистора, база . которого соединена с вторыми выводами первого и второго резисторов, а эмиттер четвертого дополнительного транзистора - с эмиттерами первого, второго и третьего дополнительных транзисторов и вторым выводом третье го резистора.

О 1

а I

I

о 1 1

J о

о о 1

1 о

1

1

о 1

I

о

о

о 1

)

о

1

| КТычино К.К.Пересчетные декады, М | |||

| , Энергия, 1976 | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Тычино К.К, Тычино Н.К.Многофункциональные цифровые измерительные приборы | |||

| М., Радио и связь, 1981(прототип). | |||

Авторы

Даты

1984-09-07—Публикация

1983-06-01—Подача